# RB/1 Review

December 1968 Volume 29 No. 4

#### RADIO CORPORATION OF AMERICA

DAVID SARNOFF, Chairman of the Board ELMER W. ENGSTROM, Chairman of the Executive Committee of the Board ROBERT W. SARNOFF, President and Chief Executive Officer

GEORGE E. MORRIS, Secretary

ERNEST B. GORIN, Vice-President and Treasurer

RCA RESEARCH AND ENGINEERING J. HILLIER, Vice-President

RCA LABORATORIES W. M. WEBSTER, Staff Vice-President

RCA REVIEW

C. C. FOSTER, Manager R. F. CIAFONE, Administrator

#### PRINTED IN U.S.A.

RCA REVIEW, published quarterly in March. June, September, and December by RCA Research and Engineering, Radio Cotporation of America, Princeton, New Jersey 08540. Entered as second class matter July 3, 1950 under the Act of March 3, 1879. Second-class postage paid at Princeton, New Jersey, and at additional mailing offices. Subscription price in the United States and Canada one year \$4.00, two years \$7.00, three years \$9.00; in other countries, one year \$4.40, two years \$7.80, three years \$10.20. Single copies up to five years old \$2.00. Fot copies more than five years old, contact Walter J. Johnson, Inc., 111 Fifth Ave., New York, N. Y. 10003.

## RCA REVIEW

#### a technical journal

Published quarterly by

#### RCA RESEARCH AND ENGINEERING

in cooperation with all subsidiaries and divisions of

#### RADIO CORPORATION OF AMERICA

| VOLUME 29                                 | December 1968                                                                                        | NUMBI         | er 4 |

|-------------------------------------------|------------------------------------------------------------------------------------------------------|---------------|------|

|                                           | CONTENTS                                                                                             |               |      |

|                                           |                                                                                                      |               | PAGE |

| New Process Technolo                      | ogies for Microelectronics—Forew<br>J. A. AMICK and N. E. WOLFF                                      | ord           | 473  |

| Isolation Techniques f                    | or Fabricating Integrated Circuits                                                                   |               |      |

| I. Laminate Sul                           | J. A. AMICK and A. W. FISHER                                                                         |               | 475  |

| A                                         | fill Techniques and Decal Air Isola<br>. I. STOLLER and W. H. SCHILP, JR.                            |               | 485  |

| Relationship Between<br>circuit and the I | the Performance of a Linear Am<br>solation Technique Used in Its Cor<br>A. I. STOLLER                | istruction    | 507  |

|                                           | al Vapor Deposition of Oxide and O<br>WERNER KERN                                                    |               | 525  |

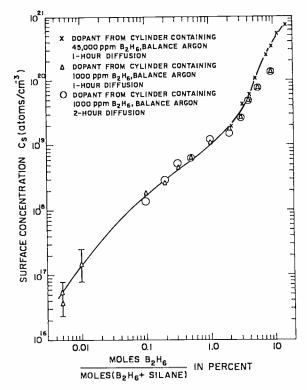

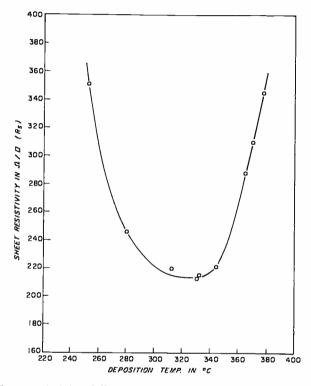

| Layers Deposited                          | tics and Applications of Doped Sid from Silane (SiH <sub>4</sub> ), J. A. AMICK, H. HYMAN, and J. H. | Scott, Jr.    | 533  |

| Diffusion Characterist                    | Lics of Doped Silicon Dioxide Lay<br>Hydrides<br>A. W. FISHER and J. A. AMICK                        | ers Deposited | 549  |

| A Technique for Meas                      | uring Etch Rates of Dielectric Film<br>WERNER KERN                                                   | ns            | 557  |

| DC Sputtering with R                      | F-Induced Substrate Bias<br>. L. VOSSEN and J. J. O'NEILL, JR.                                       |               | 566  |

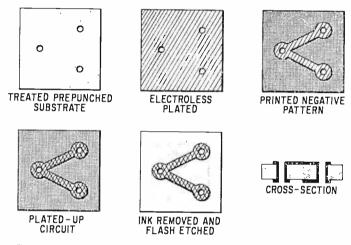

| Additive Processing T                     | Cechniques for Printed-Circuit Boa<br>RYAN, T. E. MCCURDY, and N. E. WO                              | JTL.E.        | 582  |

| Calculation of the E<br>Measurements M    | lectrical Parameters of Transisto<br>lade on Packaged Units<br>A. I. STOLLER                         | r Chips from  | 600  |

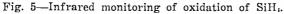

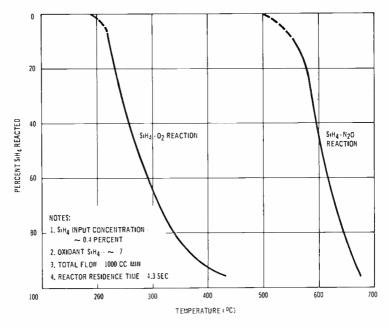

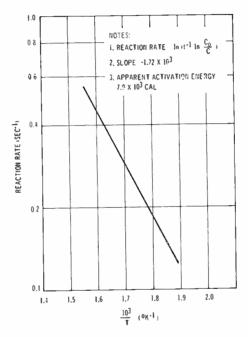

|                                           | of Silane<br>K. STRATER                                                                              |               | 618  |

|                                           | annel Enhancement MOS Triodes<br>P. DELIVORIAS                                                       |               | 630  |

| RCA Technical Pape                        | ers                                                                                                  |               | 640  |

| Anthors                                   |                                                                                                      |               | 644  |

| Index, Volume 29 (1                       | 968)                                                                                                 |               | 649  |

© 1969 by Radio Corporation of America All rights reserved.

### RCA REVIEW

#### BOARD OF EDITORS

Chairman

J. A. RAJCHMAN RCA Laboratories

E. D. BECKEN RC.4 Communications, Inc.

G. H. BROWN RCA Patents and Licensing

A. L. CONRAD RCA Education Systems

A. N. GOLDSMITH Honorary Vice President, RCA

G. B. HERZOG RC.4 Laboratorics

J. HILLIER RCA Research and Engineering

R. S. HOLMES RCA Research and Engineering

E. C. HUGHES RC.4 Electronic Components

E. O. JOHNSON RCA Electronic Components

II. W. LEVERENZ RCA Patents and Licensing H. R. LEWIS RCA Laboratorics

G. F. MAEDEL RCA Institutes, Inc.

I., S. NERGAARD RC.4 Laboratories

II. F. OLSON RC.4 Laboratories

K. H. POWERS RCA Laboratorics

P. RAPPAPORT RC.4 Laboratorics

F. D. Rost RC.1 Laboratories

I., A. SHOTLIFF RCA International Licensing

> T. O. STANLEY RC.4 Laboratorics

> W. M. WEBSTER RC.1 Laboratories

> > A. 1

Secretary C. C. Foster RCA Research and Engineering

#### REPUBLICATION AND TRANSLATION

Original papers published herein may be referenced or abstracted without further authorization provided proper notation concerning authors and source is included. All rights of republication, including translation inteforeign languages, are reserved by RCA Review. Requests for republication and translation privileges should be addressed to *The Manager*.

#### NEW PROCESS TECHNOLOGIES FOR MICROELECTRONICS

#### Foreword

Innovation and technological change are hallmarks of the electronics industry, especially in the fabrication of solid-state devices. Although silicon transistors today do not differ significantly in concept from those of a decade ago, striking advances have been made in their performance and reliability. In particular, the ability to prepare solidstate devices with high yields has steadily improved, leading to the fabrication of multitransistor silicon chip circuits of the "mediumscale integration" (MSI) and "large-scale integration" (LSI) variety. These increases in yield can be traced back directly to refinements and invention in the *processing* of semiconductor devices and their interconnections.

With the advent of additional new processing methods, still further increases in the yield, reliability, performance, and sophistication of solid-state arrays can be anticipated. Furthermore, as the techniques and concepts used in manufacturing transistors are introduced into other areas of electronic device fabrication, greatly improved electronic systems at significantly lower cost will become available. To investigate new processes potentially useful in electronic applications, the Process Research and Development Laboratory was set up at RCA's David Sarnoff Research Center in 1963. Ten of the papers in this issue of the RCA Review are based on the results of investigations carried out in that laboratory.

The first seven papers describe processes useful for fabricating improved silicon integrated circuits. The processing techniques employed are hot-pressing, chemical vapor deposition, and etching; the technologies involved are, respectively, dielectric isolation for monolithic circuits, more controllable diffusion sources, and the characterization of glass layers on a silicon substrate.

The next three papers deal with the interconnection of silicon chips into arrays, with or without additional passive components. Here the processing techniques include rf sputtering, electroless and electrodeposition of metals, offset printing, and hot-pressing.

The last two papers in this issue, both dealing with improved methods for fabricating semiconductor devices, are contributions from the Electronic Components devision of RCA. Chemical vapor deposition is the processing technique common to the two papers, the first being a study of a particular process and the second illustrating an application of the technique.

The processes described in these twelve papers are based on chemistry, physics, metallurgy, ceramics technology, and computer programming. Just as for other issues of the RCA Review devoted to a single topic, i.e., the series of papers on "Epitaxial Growth" published in December 1963, the advances described here represent an interweaving of a variety of disciplines to effect a desired result. They thus illustrate once again the power of an interdisciplinary approach to research and the benefits to be gained by providing an environment in which scientists of different backgrounds can interact cooperatively and fruitfully.

> N. E. WOLFF J. A. AMICK Process Research and Development Laboratory

PRINCETON, N.J.

#### ISOLATION TECHNIQUES FOR FABRICATING INTEGRATED CIRCUITS

...

#### I. LAMINATE SUBSTRATES

#### By

#### J. A. AMICK AND A. W. FISHER

RCA Laboratories Princeton, N. J.

Summary—Substrates comprising silicon regions separated from one another by a silicon dioxide or ceramic dielectric can readily be prepared by lamination in a hot press. The preparation of these substrates is described in detail and their properties are discussed briefly. These substrates are potentially useful for the fabrication of diode arrays or for arrays of MOS field-effect transistors.

#### INTRODUCTION

HE FABRICATION of monolithic integrated circuits containing arrays of individual devices requires that the devices be electrically isolated from one another prior to metallization. Conventionally, this isolation is accomplished by forming "bathtub" junctions surrounding each device. When these junctions are reverse biased, the depletion layer serves as an insulator region. Improvements can be made in the electrical performance of arrays if the depletion layers are replaced by a true dielectric material. If this dielectric is sufficiently refractory, chemically inert, and a good enough match to silicon in thermal expansion, the isolated substrate can be processed in the same way as convential monolithic silicon substrates.

A variety of techniques have been successfully used to fabricate isolated arrays. One involves the lamination of slices of silicon under high temperature and pressure, using a high-melting-point dielectric as a cement. The substrates derived from this process are designated "laminate substrates."

#### EXPERIMENTAL

The processing sequence employed in the preparation of laminate substrates is similar to that described by Naymik.' Ideally, however,

<sup>&</sup>lt;sup>1</sup> D. A. Naymik, "Silicon Mosaic for Integrated Devices," *IEEE Trans.* on *Electron Devices*, Vol. ED-12, p. 497, Sept. 1965.

a higher-temperature, higher-resistivity dielectric than the germanium-silicon oxide used by Naymik would be required, especially if the finished substrates are to undergo standard silicon processing, such as diffusion. Cave has found<sup>2</sup> that steam-grown silicon oxide layers, about 2 microns thick, serve as a satisfactory bonding medium if the oxidized wafers are pressed together at about 1250°C for perhaps 10 minutes at 2000 psi. If the pressing is conducted in vacuum, gas inclusions are minimized and a stack of wafers can be joined together into a rugged, monolithic block of material. On slicing through this block, wafers of silicon bars are obtained, each bar being electrically separated from, and bonded to, its neighbors by a thin, coherent silicon dioxide strip.

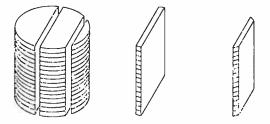

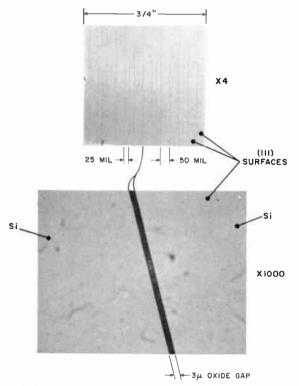

Fig. 1—Laminated block prepared from circular wafers and slices cut from this block.

#### Materials and Processing

Conventional (111) criented silicon wafers were originally used in the preparation of laminated blocks. These nearly circular wafers have two principal disadvantages, however. Perhaps the most serious is the varying size of the slices that can be cut from such a block (Figure 1). Although all slices have one dimension in common (corresponding to the height of the block), the second dimension depends on whether the slice is cut from the edge or from the center of the block. Furthermore, in a crystal, the sets of (111) planes do not lie at right angles to one another. Therefore, it is not possible to cut perpendicularly through a (111) plane and end up with a newly exposed surface that also has (111) orientation. Since many factory processing steps have been designed for (111) oriented wafers, it was desirable to retain this orientation in the final substrate. If (100) oriented surfaces are desired, the crystal symmetry simplifies the preparation of substrates by this method.

<sup>&</sup>lt;sup>2</sup> E. F. Cave, U. S. Patent 3,290,760 issued December 13, 1966; c.f. also J. A. Amick, U. S. Patent 3,354,354 issued November 31, 1967,

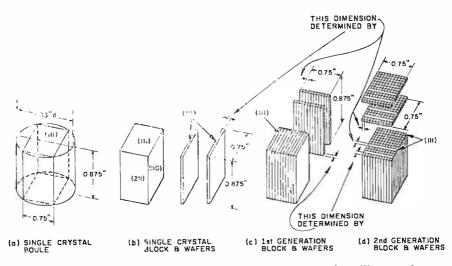

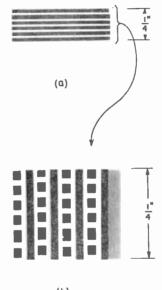

Both these disadvantages can be overcome by using rectangular wafers of silicon of appropriate orientation as starting materials. As shown in Figure 2a, a rectangular block  $0.75 \times 0.875$  inch is first cut from a silicon boule. The orientations of the sides of this block are not critical, but the faces can conveniently be made (211) and (110) planes. The block is now sliced parallel to one of these two planes to give wafers  $0.75 \times 0.875$  inch in area and having any desired thick-

Fig. 2-Preparation of laminate substrates from rectangular silicon wafers.

ness. The ends of these slices are (111) planes (Figure 2b). Using oxidized wafers cut from several blocks, one can assemble a stack 0.75 inch high (Figure 2c). Following lamination and slicing, one then obtains "first-generation" substrates all identical in size, namely  $0.75 \times 0.875 \times$  whatever thickness is chosen for the slice (Figure 2c). Since the two major dimensions for these first-generation slices are the same as for original slices, a "second-generation" block can be prepared from any combination of silicon slices and first-generation wafers. On slicing the second-generation block, one obtains substrates that are all the same size and in which each exposed silicon area is a (111) plane (Figure 2d).

The dimensions of the original block cut from the silicon boule are not critical. For the silicon boules normally available, i.e., 1.125 inches in diameter, a  $0.75 \times 0.75$  inch (111) face is about as large as can be cut without rounding the edges of the block. By making the third dimension of the block longer (or shorter) than the other two, the (111) end of the slices can readily be identified. When single-crystal slices and first-generation slices are assembled into a stack, it is then easy to remember how the stack should be sliced to give (111)-surface substrates.

For some applications, dielectric layers thicker than can be obtained with thermal oxides are desired. For this purpose, wafers of a suitable thermal-expansion-matching ceramic, such as Pyroceram<sup>†</sup> 9606, can be employed. This material is available in the recrystallized form and can be cut into suitably shaped wafers and polished. Again, thermal oxide, grown in steam, forms a satisfactory cement for bonding a silicon wafer to a Pyroceram wafer.

Composite substrates, either of silicon and silicon dioxide, or those including Pyroceram regions, can be satisfactorily polished with Lustrox,\* an alkaline zirconium oxide slurry. Following polishing, very smooth surfaces are obtained in which the silicon regions have minimal work damage. Step-height differences, going from the Pyroceram to the silicon are less than 1 micron following Lustrox polishing.

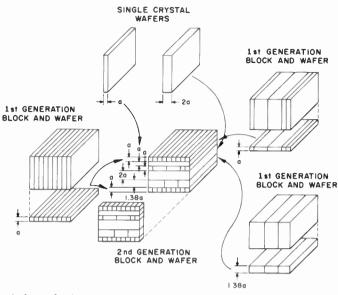

#### Substrate Arrangement

Since each layer included in the preparation of a laminate can be a silicon wafer of different resistivity or resistivity type or a Pyroceram wafer, and since the thickness of all wafers is optional, a wide variety of first-generation (har) substrates is possible. If slices from several different first-generation blocks are incorporated into a second-generation block, along with a variety of single-crystal silicon slices, almost any desired geometrical arrangement of silicon regions and Pyroceram regions can be obtained, with any desired resistivity and resistivity type for the silicon in any location. The dimensions of a given region are determined by (a) the thickness of the original wafer and (b) the thickness of the first-generation slice used to prepare the block (Figure 3). The only limitation, then, is that all areas must be either square or rectangular in outline. However, it is not necessary that any two adjacent areas be the same size.

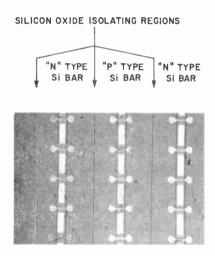

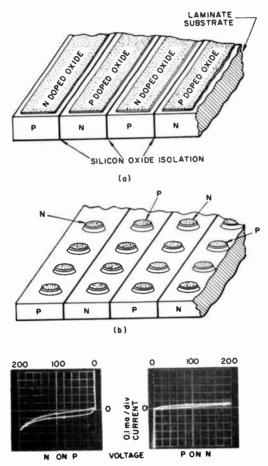

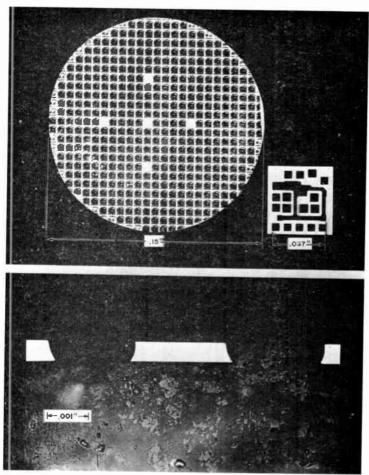

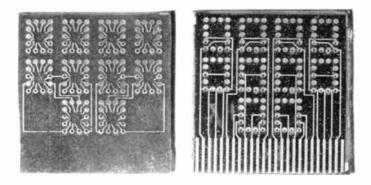

Typical examples of laminate substrates prepared as described above can be seen in Figures 4 and 5. Figure 4 shows a simple silicon-silicondioxide laminate constructed of p-type and n-type wafers, some 0.025 and some 0.050 inch thick. The resultant isolated-bar configuration is suitable for forming ladder arrays of complementary MOS transis-

<sup>†</sup> Corning Glass Works, Corning, New York.

<sup>\*</sup> Tizon Chemical Corp., Flemington, N. J.

Fig. 3—A hypothetical "second-generation" substrate and its components.

tors (Figure 6). In Figure 5, a laminate including Pyroceram regions and silicon bars is seen at the top. Below, a second-generation laminate containing bars and blocks of silicon in a Pyroceram matrix is shown. The wafer in Figure 5a, viewed end-on, forms one row of silicon and Pyroceram blocks for the substrate of Figure 5b.

(b)

Fig. 5-Substrates composed of silicon and matching-coefficient Pyroceram. Top, "first-generation" substrate; bottom, "second-generation" substrate.

#### Electrical Properties of Diodes Formed in Laminate Substrates

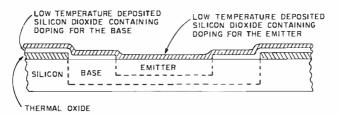

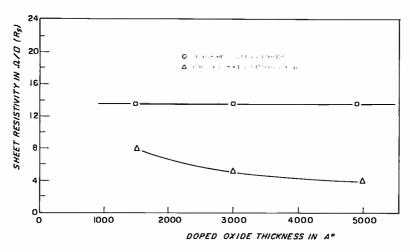

The preparation of complementary diode arrays in laminate substrates has been carried out using doped-oxide diffusion sources deposited as described by Fisher and Amick.<sup>3</sup> Both mesa- and planar-type diodes have been formed successfully.

An array of mesa devices is shown schematically in Figure 7. These were prepared on laminate substrates comprised of nominally 15-ohm-cm n- and p-type bars. Stripes of doped oxide suitable for emitter diffusions were deposited over appropriate silicon regions

<sup>&</sup>lt;sup>3</sup> A. W. Fisher and J. A. Amick, "Diffusion Characteristics of Doped Silicon Dioxide Layers Deposited from Premixed Hydrides," *RCA Review*, Vol. 29, p. 549, Dec. 1968.

through metal masks (Figure 7a). A diffusion step at 1200°C for 1 hour was then carried out, after which mesas were defined with hydrofluoric-nitric acid (Figure 7b). For this step, 0.01-inch-diameter mesas were defined with black wax. Individual diodes were probed to determine their electrical characteristics. As can be seen in Figure 7c, the voltage breakdown for both n-on-p and p-on-n diodes was in excess of 200 volts, while the reverse saturation currents were below 0.1 ma.

- .020<sup>H</sup>-

Fig. 6—MOS transistor arrays fabricated on a silicon/silicon dioxide laminate Rectangular areas are source-drains, dumbbell-shaped areas are gates.

Arrays of complementary planar diodes have been prepared on 1-ohm-cm n- and p-type silicon-Pyroceram laminates. For these devices, a 0.5-micron thermal-oxide layer was first grown over the silicon surfaces. Openings 0.030 inch in diameter were then etched into this oxide above the p-type silicon regions only. A doped oxide containing phosphorus appropriate for base-level doping was next deposited over the entire surface. Openings 0.030 inch in diameter in the double-oxide layer were then formed above n-type regions and a doped-oxide source containing boron, appropriate for base-level doping, was deposited over the entire surface. A single diffusion, serving to drive in both n- and p-type dopants, was carried out at 1200°C for 2 hours, after which contacts were opened. Reversebreakdown voltages for both types of diode were in the neighborhood

#### RCA REVIEW

of 60 to 70 volts, with the reverse saturation current below 1 mA at a few volts, but with a somewhat rounded reverse characteristic at higher reverse biases. Junction depths were 3 microns, as expected.

#### (c)

When emitters were formed in these base-level doped regions, the current gains for the resultant transistors were found to be low, apparently because of a decreased minority-carrier lifetime in the base region compared with that in the original single-crystal silicon wafers from which the laminate substrates were prepared. This lowered lifetime can probably be attributed to the high dislocation density arising from plastic-flow during the hot pressing step, as described subsequently. It is therefore concluded that until a method of reducing the dislocation density in these substrates is devised, they will not be useful for forming arrays of bipolar devices, but should be satisfactory for preparing diode arrays or arrays of MOS transistors (Figure 6). Junction characteristics and transconductances for arrays of MOS transistors are normal, i.e., comparable to arrays formed in singlecrystal substrates.

#### DISCUSSION

Because of the freedom to include silicon regions of almost any resistivity and type in almost any desired location, laminate substrates have certain advantages for the fabrication of complementary integrated circuits. Long rectangular regions can be provided for MOS ladder arrays, and small square areas can be provided for the preparation of individual diodes, diffused resistors, and the like. For diode arrays it is possible to form the cathode contact on either face of the wafer as desired. Passive components could be prepared in silicon regions by diffusion techniques or could be formed by deposition on insulating Pyroceram regions as desired.

An additional advantage of this freedom is the ability to provide feed-throughs in almost any desired location. Since the silicon regions extend completely through the substrate, contact can easily be made to the front and the back face of any region. A  $0.015 \times 0.015 \times 0.015$ inch silicon cube of 0.005-ohm-cm resistivity introduces a series resistance of only about 0.15 ohm. It may therefore be desirable to use both faces of the wafer to form circuits, with feed-throughs provided at suitable locations. Crossovers can conveniently be obtained by tying together two feed-throughs on the back surface by any suitable interconnection technique, such as evaporation of a metal through a mask.

The substrates prepared by the lamination process are mechanically rugged and can be handled and processed very much like single-crystal silicon. Both the thermally grown silicon dioxide and the Pyroceram withstand treatment in an oxidizing atmosphere at the temperatures required for diffusion into the silicon. The laminate substrates prepared in this work have been cycled several times from room temperature to 1200°C and back to room temperature with no cracking or mechanical deterioration.

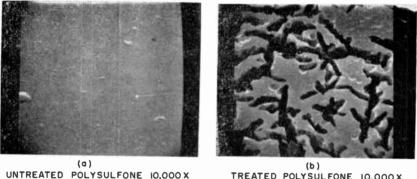

The hot-pressing step does introduce dislocations into the silicon, which deforms plastically at the pressing temperature and pressure. Following Sirtl<sup>4</sup> etching, dislocation densities of as much as  $5 \times 10^6$

<sup>&</sup>lt;sup>4</sup> E. Sirtl and A. Adler, "Chromsäure-Flussäure als spezifisches System Zür Ätzgrubenentwicklung auf Silizium," Z. Metallkde, Vol. 52, p. 529, 1961.

cm<sup>-2</sup> are observed both for laminates of silicon and silicon dioxide and for laminates incorporating Pyroceram.

Resistivity measurements made with a four-point probe reveal that changes in resistivity during lamination are negligible, both for lightly doped and for heavily doped starting material.

In the lamination process, the Pyroceram is sometimes partially reduced chemically. It can easily be restored by a thermal oxidation of the final substrate in steam at 1050° for a few hours. Since the first step in conventional device processing is the growth of an oxide layer on the silicon areas, this reoxidation of the Pyroceram would take place during normal processing. In any event, the resistivity of the partially reduced Pyroceram is extremely high and will probably not interfere with any circuitry fabricated in the substrates even if it is not reoxidized.

During lamination and subsequent high-temperature processing, impurities may diffuse from the Pyroceram into the silicon. In particular, p-type contamination, probably due to aluminum, can be found at depths of a few microns from the Pyroceram-silicon interface. Since the smallest silicon areas that can be made practically in these substrates are about  $250 \times 250$  microns, this diffusion should not cause a problem as long as the outer 25-micron periphery of any silicon region is not included in the active device area. In certain applications, the use of a barrier layer, e.g., silicon nitride or aluminum oxide, may be desirable to minimize the diffusion of impurities into the silicon.

#### CONCLUSIONS

Laminate substrates can readily be prepared in a variety of configurations using silicon, thermally grown oxide layers, and suitable ceramics such as Pyroceram 9606. The substrates can undergo conventional silicon device processing with no deterioration of their mechanical properties. The dislocation density in the final substrates is high and, until ways of lowering the dislocation density can be devised, their usefulness will be limited to the fabrication of MOS devices and diodes. These substrates are especially suitable for applications that require unusually high voltage isolation between devices and for configurations of device arrays beyond the size limitations of single-crystal silicon wafers.

#### ACKNOWLEDGEMENT

We would like to thank E. F. Cave for valuable discussions, as well as N. E. Wolff, who also critically read the manuscript.

#### ISOLATION TECHNIQUES FOR FABRICATING INTEGRATED CIRCUITS

# II. DIELECTRIC REFILL TECHNIQUES AND DECAL AIR ISOLATION

#### Вү

#### A. I. STOLLER AND W. H. SCHLIP, JR.

RCA Laboratories Princeton, N. J.

Summary—Three techniques are described for preparing silicon integrated circuits in which the individual components are separated from one another by a true dielectric rather than the p-n junctions that are presently used. Two of these techniques begin with wafers in which devices have already been formed, while the third involves a new type of isolating substrate capable of undergoing diffusion steps. In all cases the devices are precisely located with respect to one another and are essentially coplanar, so that interconnections can be formed in a single operation.

#### INTRODUCTION

NTEGRATED CIRCUITS have found widespread use in computers and other applications where low voltages and low frequencies are encountered. These are mostly digital applications, although there has been some analog usage where present-day performance of integrated circuits can meet the requirements of the circuit.

Circuits made from discrete semiconductor devices can presently operate at frequencies greater than 1 GHz. Integrated circuits, however, are generally limited to operating frequencies in the 50 to 100 MHz range, due to parasitic capacitances between neighboring components and between components and the substrate. These are associated with the reverse-biased p-n isolation junctions that are normally used for electrically isolating the components from one another. Also, the maximum potential difference that can be supported between devices is limited to the reverse-breakdown potential of the isolation junction (in the range of 40–50 volts). Isolation junctions also have substantial leakage currents and poor radiation resistance.

For these reasons, it is apparent that a better method of isolation must be used if integrated circuits are to be employed for more demanding applications, such as microwave and radar circuits. Even for present applications, such as digital computer circuits, there is a performance advantage to be gained if circuits and systems were designed for, and used, dielectrically isolated integrated circuits.

A common approach to isolation (employed in some commercially made circuits) is based on the use of a thin layer (2-4 microns) of SiO<sub>2</sub> to provide isolation, and a polycrystalline silicon refill to provide useful circuits for certain applications. It does not, however, provide as good an isolation impedance at higher frequencies as does a true dielectric.

Therefore, isolation techniques based on the use of dielectrics such as glass and ceramics have been devised. Several of the methods and processes used for the purpose are described in this paper.

#### APPROACHES TO DIELECTRIC ISOLATION

There are three possible stages in the processing of a silicon integrated circuit at which device isolation could be accomplished:

- (1) before the device diffusions are carried out;

- (2) after the device diffusions are completed, but before metallization and interconnection;

- (3) after the devices are metallized and interconnected.

Associated with each of these options are restrictions on the temperature that may be used in the isolation process and a requirement that the substrate be able to withstand the temperatures subsequently used in completing the device or circuit.

If isolation is provided before the device diffusions, temperatures as high as 1200-1300 °C can be used to achieve isolation, since the only limitations are the melting point of the silicon and the degree to which defects are introduced into the structure of the silicon. Once isolated, however, the substrate must withstand diffusion temperatures of 1100-1200 °C for appreciable periods of time.

If the diffusions are first completed conventionally in a singlecrystal wafer, then the isolation process must be carried out at a temperature that will not affect diffusion profiles in the devices. For silicon devices, this means that the isolation temperature should not exceed 900–950°C. After isolation of diffused devices is completed, the only processing that remains to be done is the metallizing for interconnections. This is accomplished at temperatures well below 900°C. This technique provides the advantage of being able to carry out all the diffusion steps in single-crystal silicon wafers, thereby avoiding

- . - .

any processing problems or contamination that the insulating substrate might introduce.

The third option is the isolation of devices that have been completely fabricated, metallized, and interconnected. The maximum allowable isolation temperature in this case depends on the type of metal that is used. Aluminum, which is the most common metal presently used for silicon semiconductor devices, does not withstand processing at temperatures beyond 450–500°C. This is a severe restriction, since glasses that soften below this temperature usually have high thermal expansion coefficients and contain ions that degrade the dielectric characteristics. However, if a more refractory metal such as tungsten<sup>1</sup> is used, this temperature restriction is relaxed and suitable glasses are available. An example of the latter isolation method, known as the "Decal" process, appears to be the most attractive from both a technical and an economic standpoint and is described later.

There are several possible variations of these methods, and the selection of an isolation scheme must be based on the many electrical and physical requirements of the particular circuit involved.

#### DIELECTRIC MATERIALS SUITABLE FOR ISOLATION

Two types of materials are used as the insulating dielectric in the isolation methods described here—a glass and a glass-ceramic composite.

Where the isolation is provided after the device diffusions are completed, the requirements for the dielectric include (1) a good thermal expansion match with the semiconductor and (2) good dielectric properties at high frequencies. It is not necessary, however, for the final composite substrate to withstand high-temperature diffusion conditions after the isolation is carried out. Glasses that meet these requirements and that can be processed below 900°C are readily available. Corning #7070 glass\*, the glass discussed here, has a softening point of about 715°C.

Glass-ceramic compositions were devised for substrates that must undergo diffusion after the isolation step. Such a requirement places certain constraints on the dielectric material in the substrate.

(1) It must closely match the thermal coefficient of expansion of silicon.

<sup>&#</sup>x27;A. I. Stoller, J. A. Amick, and N. E. Wolff, "Getting the Most Out of Circuits with Dielectric Isolation," *Electronics*, p. 97, March 20, 1967.

<sup>\*</sup> Corning Glass Works, Corning, New York.

- (2) It must be processable at temperatures and pressures that do not introduce excessive dislocations in the silicon and do not change the impurity profile of epitaxial layers. It is, in general, desirable to use temperatures that do not exceed 1300°C, and pressures that do not exceed 1000-2000 psi.

- (3) The dielectric substrate must withstand the device diffusion and processing conditions without degradation or dimensional change. This normally requires exposure to temperatures of 1100°C or greater for several hours.

- (4) It must remain a low-loss dielectric at GHz frequencies.

- (5) It should have a high dielectric strength.

Although some glasses come close to meeting these requirements, none were found that have the proper thermal expansion and that also withstand the diffusion conditions without deformation. Crystalline ceramics, on the other hand, can have satisfactory expansion and mechanical properties. They do not deform or flow readily, however, and cannot be pressed and molded into an intricate shape. A substrate meeting all these requirements can be made by using a suitable combination of a glass and a crystalline ceramic material. The starting compositions are prepared as an intimate mixture of finely powdered materials. The glass provides a deformable phase that permits molding around intricate silicon shapes, leaving essentially no voids. The crystalline ceramic phase provides a skeletal structure that prevents distortion of the substrate at temperatures that would be too high for the glass alone. In addition, a partial crystallization of the glass is encouraged to take place slowly as the substrate is prepared and heat treated. In this way, the substrate material is relatively fluid during pressing, but is much more refractory when completed.

It is possible to obtain a similar glass-ceramic body by using only a devitrifying type of glass that can be pressed into a silicon structure and subsequently devitrified. There is, however, a small volume expansion of the substrate as the devitrification takes place. This causes the silicon to crack if the glass is devitrified to the extent required. On the other hand, if about one half of the volume of the starting composition is crystalline, the overall volume change, due to the partial devitrification of the glass, is so small that it does not cause cracking. The major constitutents of these materials are:

(1) A glass having a high softening point, and a thermal expansion coefficient closely matching that of silicon (about 31 to  $36 \times 10^{-7}$  cm/cm°C). A suitable glass for this purpose is a calcium

alumino-silicate glass, such as Corning #1715, which has a softening point of 1070 °C.

(2) A crystalline ceramic material having a high melting point (>1200°C) and a thermal expansion coefficient closely matching that of silicon. Many materials undoubtedly could be used. Two material that have been found satisfactory are mullite (3Al<sub>2</sub>O<sub>3</sub> • 2SiO<sub>2</sub>) and cordierite (2MgO • 2Al<sub>2</sub>O<sub>3</sub> • 5SiO<sub>2</sub>).

The glass and the ceramic are ball-milled together in distilled water for about 15 hours to give an average particle size of 1 to 5 microns. Typically, the material is hot pressed into the structure to be isolated at temperatures between 1100°C and 1200°C at 1000 to 2000 psi for 10-15 minutes in order to obtain a dense substrate. The temperature may then be held in this range for an additional period of time to afford partial crystallization of the glass. It is desirable to carry out this crystallization before the device processing is started. In this way, any resulting dimensional change is completed before the precessing is begun, and problems of mask misregistration are avoided.

It is possible to influence the rate of crystallization by the use of certain additives. Titanium dioxide  $(TiO_2)$  provides nucleation sites and tends to acclerate the devitrification process. It was found that additions of 3 to 5% by weight of  $TiO_2$  cause such rapid devitrification that the substrate loses its fluidity before it can be pressed to a suitable density. The addition of a few tenths of a percent of  $TiO_2$ , however, is beneficial. In this case, the devitrification of the glass is accelerated, but not to an objectionable degree.

Another additive that can be used to control the devitrification process and subsequent crystal structure is MgO. The rate of crystal growth is reduced by the presence of MgO, thereby allowing some compositions that would otherwise be too viscous for pressing to be pressed to a high density. This permits the addition of more of the crystalline material in the starting composition, which minimizes dimensional changes during the heating cycle.

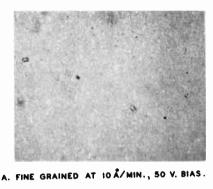

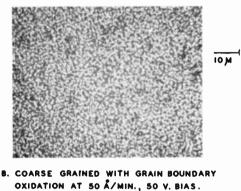

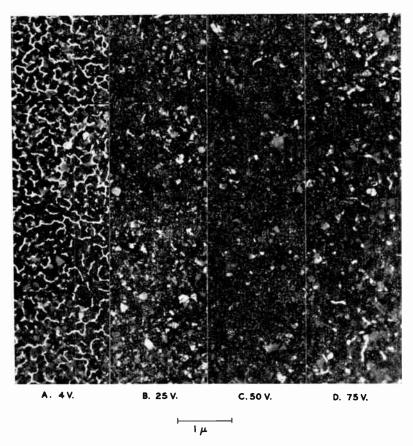

MgO and TiO<sub>2</sub> can also be used together in a composition in order to obtain a better microstructure. In this way, a uniform, fine-grained substrate is obtained that has controllable devitrification characteristics. An MgO addition of 3% by weight and TiO<sub>2</sub> addition of 0.3%by weight has been found satisfactory, although a systematic variation of these quantities has not been made.

Substrate compositions of Corning #1715 glass and mullite were heat treated at various temperatures after they were pressed and the resulting crystal phases were studied by x-ray diffraction. These studies showed that the glass crystallizes to form phases of crystalline  $SiO_2$  and a low-symmetry alumino-silicate. In the absence of additives it was found that the rate of devitrification becomes significant at temperatures of 1100°C and higher.

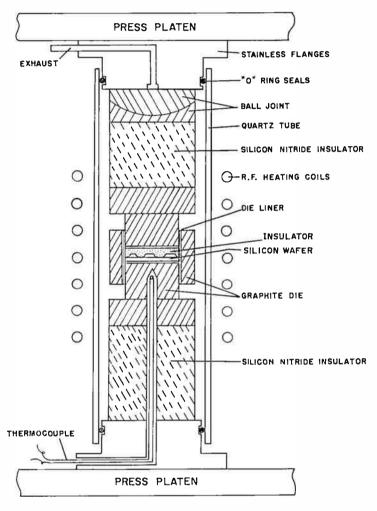

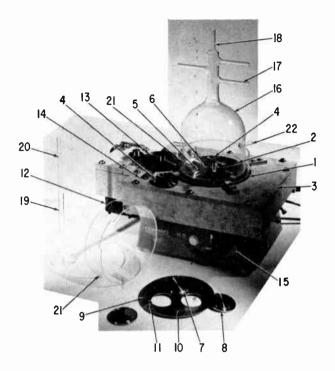

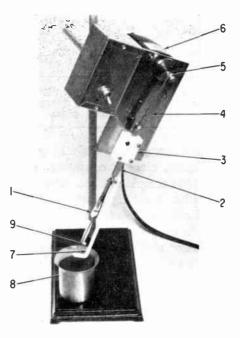

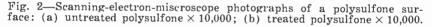

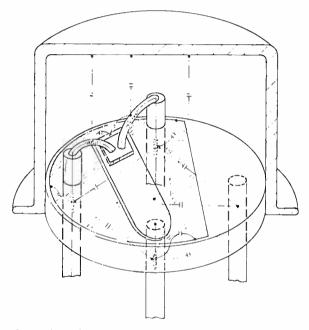

#### HOT PRESSING APPARATUS USED IN PREPARING SUBSTRATES

All the isolation methods described in this paper employ hot pressing. A special apparatus was designed to allow the insulator component of the substrate to be molded and bonded to the silicon regions under heat and pressure in a vacuum or a controlled atmosphere. In this aparatus (Figure 1), a graphite die serves as both a pressing chamber and as a susceptor for rf heating of the sample. A graphite ball joint compensates for any non-parallel surfaces in the assembly. Polycrystalline silicon nitride blocks are ideal as spacers, since they are chemically inert, have a low thermal conductivity and high compressive strength, and are resistent to cracking or spalling.

For pressing the glass-ceramic material, a die liner of 0.005-inchthick graphite is used in a split-collar die. This facilitates removal of the finished sample, and if there is any sticking of the ceramic to the graphite, the liner can be sacrificed and removed by lapping or by oxidation.

For isolation techniques in which a simple glass is used, die faces of pyrolitic<sup>\*\*</sup> graphite are used, since there is no tendency for the glass to adhere to this material. In all cases, a thermocouple penetrates well into the die in order to sense the temperature as close to the wafer as possible. This thermocouple controls the output of the rf generator to maintain a constant, pre-set temperature.

"O" ring seals allow for relative motion of the press platens while maintaining the controlled atmosphere or vacuum in the pressing chamber.

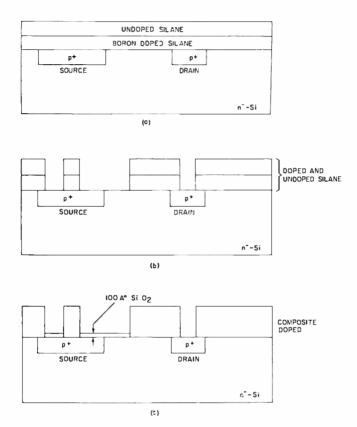

#### ISOLATION BEFORE DEVICE FABRICATION

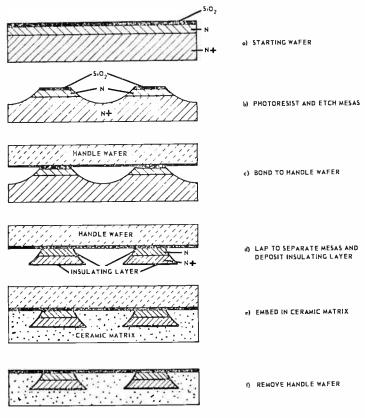

The glass-ceramic material described previously can be used to fabricate isolated integrated circuits by a method known as the "handle-wafer" technique.<sup>2</sup> The process can be divided into three major

<sup>\*</sup> Metallurgical Products Department, General Electric Company, Detroit, Michigan.

<sup>&</sup>lt;sup>2</sup>D. Kenny, U.S. Patent #3,332, 137, Method of Isolating Chips of a Wafer of Semiconductor Material.

steps: (A) preparation of the handle wafer structure, (B) glass-ceramic wafer preparation (isolation), and (C) fabrication of the devices.

Fig. 1—Hot-pressing apparatus.

#### A. Preparation of the Handle-Wafer Structure

The preparation of the handle-wafer structure involves the bonding together of two wafers, one of which will be referred to as the mesa wafer and the other the handle wafer.

The mesa wafer is the wafer in which the devices will ultimately

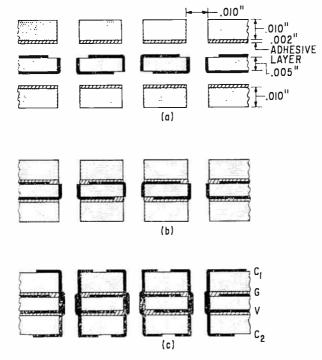

be fabricated and may be of any desired type, resistivity, and epitaxial structure. First, about 1.5 microns of  $SiO_2$  are thermally grown or deposited (and densified) on the surface (Figure 2a). The isolation pattern is then defined in photoresist on the surface, and the  $SiO_2$  layer

Fig. 2—Processing steps for making the ceramic-isolated integrated-circuit wafer.

is etched to this pattern with buffered HF. The photoresist is removed and the wafer is put into an  $IIF-HNO_3$  etchant to form mesas about 0.001 inch high (Figure 2b).

The handle wafer holds the mesas in their proper relative position during the isolation step. To prepare it, silicon wafers are polished flat and parallel and their thicknesses are accurately measured and recorded. These wafers are thermally oxidized to form about one micron of  $SiO_2$  on the surface. The handle and mesa wafers are then placed in the graphite die of the hot pressing apparatus described earlier. They are heated to 1200°C in a nominal vacuum and simultaneously pressed at 2000 psi for two minutes. The pressure is then released, the rf unit turned off, and the die allowed to cool. The wafers, which are shown schematically in Figure 2c, are then removed. Many wafers could be pressed simultaneously by stacking in the same die several sets of handle wafers and mesa wafers, the sets being separated by disks of carbon.

The backs of the mesa wafers are then lapped or ground off to separate the mesas (Figure 2d). Since the glass-ceramic would be readily attacked by the hydrofluoric acid used in subsequent processing, leaving a pitted surface on the ceramic substrate, an insulating layer of a material that is not attacked by HF is deposited over the wafer on the mesa side (Figure 2d). Two such materials are vapordeposited silicon nitride and aluminum oxide. Alternatively, a thick layer (about 3 microns) of SiO<sub>2</sub> can be deposited over the back of the mesa array. This layer is not removed in subsequent etching steps, and provides protection for the underlying ceramic substrates.

#### B. Glass-Ceramic Wafer Preparation (Isolation)

The region around the mesas is filled with dry glass-ceramic powder. The pressing apparatus is set up as shown in Figure 1. For a standard 1.25-inch-diameter wafer, each gram of the glass-ceramic powder forms about 0.020-inch of finished substrate thickness.

The rf heater is turned on and the die is heated. When the temperature reaches about 1000 °C, pressure is applied and slowly increased to 2000 psi. The pressure is held constant for 15 minutes with the temperature at 1175 °C to allow the glass-ceramic to densify. It is imperative that the die be heated rapidly, or the glass in the mixture will devitrify during heating, viscosity will increase, and the structure will not be completely filled. It has been found that, for satisfactory results, the maximum temperature should be reached in two minutes or less. The rf power is then reduced and the die is allowed to cool. When it cools to 1100 °C, the pressure is released and the die is further cooled to 860° C, where it is held for 15 minutes for annealing. At this time, further nucleation of crystallites in the glass also takes place.

The die is cooled, and the wafer (shown in Figure 2e) is removed. The handle, having served its purpose, is removed (Figure 2f) by heating the wafer in a tube furnace at 1000° with 5000 cm<sup>3</sup>/min of anhydrous HCl and 100 cm<sup>3</sup>/min of H<sub>2</sub> flowing through it. This removes the silicon of the handle wafer at a rate of about 0.002 inch per minute and since  $SiO_2$  is not attacked by HCl, the underlying silicon mesas are not etched.

The wafer is now put into hydrofluoric acid until the SiO<sub>2</sub> layer that had served to bond the mesa wafer to the handle wafer is removed. The wafer is cleaned by standard methods and the silicon is reoxidized to provide a layer that is suitable for device processing. For this oxidation, it has been found that two hours at 1050°C in steam, followed by one hour at 1100°C in O<sub>2</sub> and an hour at 1150°C in O<sub>2</sub> forms about 8000 Å of SiO<sub>2</sub> and, at the same time, completes the devitrification of the glass-ceramic insulator.

It has been found that the purity of the readily available commercial materials is adequate for preparing this substrate wafer. The substrate materials used can cause a slight p-type doping if they are in contact with silicon after prolonged heating at high temperatures. This is generally of no concern, however, since the substrate material is not in the junction region of the devices, and since a diffusion barrier such as an SiO<sub>2</sub> layer is interposed between the ceramic and the silicon.

#### C. Fabrication of the Devices

The composite wafer is now ready to undergo the fabrication of integrated circuits or other devices by standard planar techniques. There is, however, one important deviation from standard integratedcircuit processing procedures. The long isolation deposition and diffusion required to obtain the isolation in a standard monolithic wafer, typically a 16-hour heating cycle, is not required in glass-ceramic refill wafers.

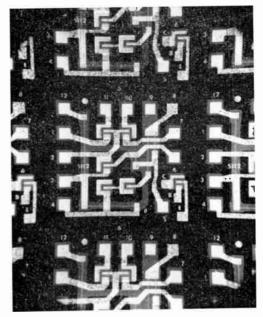

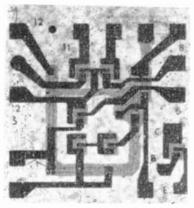

Figure 3 shows a ceramic isolated CA-3005 rf-mixer substrate wafer, with a detailed inset of one circuit. The bottom half of the picture shows a cross section of the substrate. The silicon is seen to be "keyed" into the substrate as a result of the processing sequence. A completed, processed circuit chip is shown in Figure. 4.

#### ISOLATION AFTER DEVICE FABRICATION

The same handle-wafer technique used for the glass-ceramic isolation technique described above can also be used, with a few modifications, to isolate diffused devices in a glass matrix.

(1) An isolation pattern is defined in the SiO<sub>2</sub> layer on a silicon device wafer that has the diffusion steps completed but lacks metalliza-

Fig. 3-Top: Composite substrate wafer; inset shows detail of circuit. (silicon dark)

1

Bottom: Cross-section through isolated wafer. (silicon light)

tion (Figure 5a). The isolation pattern is etched in this wafer to produce mesas that are about 0.001 inch high (Figure 5b).

- (2) A thin layer of glass (0.5 2 microns thick) is vapor-deposited or rf-sputtered onto another flat, (100) oriented silicon wafer that is subsequently used as a temporary handle to hold the devices in their proper location during isolation. This glass layer serves as a bonding medium.

- (3) The device wafer is bonded to the handle wafer, as shown in Figure 5c, by hot pressing. It has been found that 2 microns of sputtered Corning #7059 glass forms a good bond when pressed at 950°C for two minutes at 1000 psi.

#### RCA REVIEW

- (4) The back of the device wafer is lapped away so that device mesas remain bonded to the handle in proper registry (Figure 5d). At this point, the device mesas are only 0.0005 to 0.001 inch high.

- (5) A glass that softens at about 700 to 750°C such as Corning #7070 is pressed into the back of the array, as shown in Figure 5e, at a few hundred psi. This is carried out in the rf-heated graphite die described above.

Fig. 4—Isolated circuit after diffusions and metallization have been completed.

- (6) The handle can be removed (Figure 5f) by dissolving it in a hot 25% KOH solution. Etching stops when the layer of glass is reached, thereby protecting the underlying circuit from being attacked.

- (7) The glass layer that had been used to bond the handle wafer to the device wafer is etched away, leaving only the original silicon dioxide layer on the wafer. When #7059 glass is used, it can be preferentially etched away from the silicon dioxide layer with a 25% hydrofluoric acid solution.

- (8) The contact areas in the silicon dioxide layer are opened and the metal interconnect pattern is applied.

Fig. 5—Processing steps for making the glass-isolated integrated-circuit wafer.

Fig. 6—RF-mixer circuit isolated by the handle wafer method using a glass refill.

A photograph of an rf-mixer circuit chip isolated in this way and interconnected with an aluminum metallization pattern is shown in Figure 6.

#### ISOLATION AFTER METALLIZATION

The scheme of isolation that we have named the "Decal" method is perhaps simpler and more versatile than the two methods previ-

Fig. 7-Steps in the fabrication of the "Decal" structure.

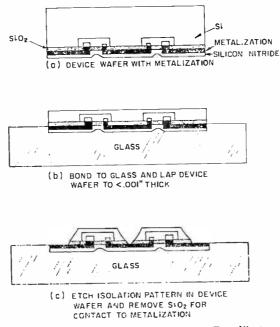

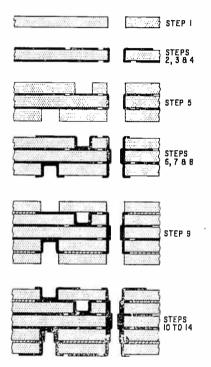

ously described. Here, the devices are completely fabricated on the single-crystal wafer (Figure 7a), including all metallization and interconnection (single or multi-layer). When isolation is accomplished by the Decal method the isolation diffusion step in the monolithic process is, of course, omitted. The dielectric isolation is then carried out according to the following steps.

(1) The metallized device surface of the wafer is bonded to an insulating substrate. For a tungsten-metallized wafer, a layer of silicon nitride is first deposited over the device wafer to provide an improved barrier layer. The wafer is then bonded directly to a glass substrate, such as Corning #7070, at 700 to 800°C under a few hundred psi of pressure.

#### ISOLATION TECHNIQUES

(2) The back of the device wafer is lapped so that only 0.0005-0.001 inch of silicon (containing the devices) remains bonded (face down) to the glass (Figure 7b). The back of the silicon is polished and a layer of chromium (about 5000 A thick) is evaporated over the back of the wafer.

(3) The mirror image of the isolation pattern, similar to that used for diffusion isolation in monolithic circuits, is defined in photoresist. The registration of this mask can be accomplished by etching a part of the silicon wafer away at the edges, leaving some of the metallization pattern exposed for registration.

Fig. 8—An RF mixer circuit isolated by the "Decal" process. Left, looking through the glass, and, right. looking at the back of the circuit.

(4) The chromium is etched with HCl or potassium ferricyanide to form a resistant etch mask for the silicon. A solution of 10% concentrated hydrofluoric acid and 90% concentrated nitric acid is used to etch the silicon into the desired isolation pattern. Thus the silicon is divided into discrete regions, each containing an active or passive component. or a group of components (Figure 7c). The metallization pattern is covered with the SiO<sub>2</sub> layer that was originally on the silicon wafer, since this oxide is not dissolved by the etch used for the silicon.

(5) Openings are etched through the  $SiO_2$  layer in the areas where contact is to be made to the metallization pattern.

(6) If contact is to be made to the resulting circuits by ultrasonic or thermocompression bonding, it is necessary to deposit a layer of aluminum or other ductile metal over the tungsten bonding pads. If a solder contact to the bonding pads is desired, then nickel or other solderable metal is deposited in the bonding-pad areas. These steps are necessary because refractory metals such as tungsten do not bond readily by conventional techniques.

Top and bottom views of an rf-mixer integrated circuit isolated by the Decal method are shown in Figure 8. The metallization pattern on this circuit is tungsten. PROPERTIES OF DIELECTRIC SUBSTRATE MATERIALS

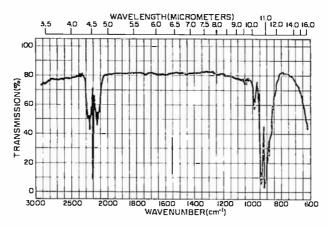

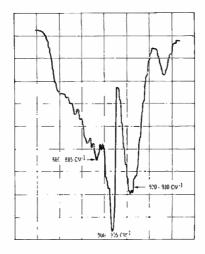

#### Electrical Characteristics of the Glass-Ceramic Refill

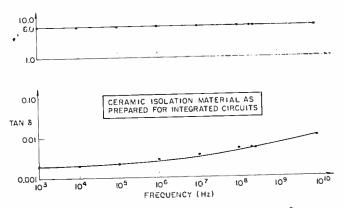

Electrodes were attached to both sides of a piece of a glass-ceramic substrate that was prepared from a 60% #1715 glass-40% mullite composition. The dielectric characteristics versus frequency were measured on a capacitance bridge at frequencies up to 250 MHz. A piece of the same substrate material was measured at 9 GHz in a microwave cavity. The results of these measurements, shown in Fig-

Fig. 9-Dielectric constant and loss tangent versus frequency.

ure 9, demonstrate that the substrate behaves as a low-loss dielectric over the frequency range covered. The relative dielectric constant is about 6, while the loss tangent rises from 0.003 to 0.01 over this frequency range.

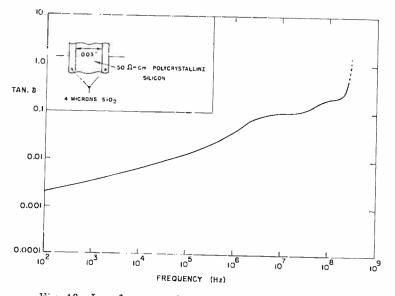

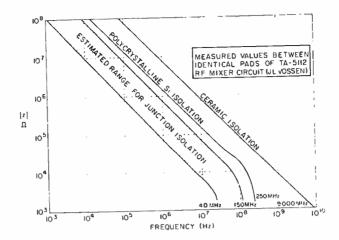

In order to compare the glass and ceramic dielectrics with the commonly used polycrystalline silicon/SiO<sub>2</sub> isolation material, polycrystalline silicon wafers having a 4-micron coating of SiO<sub>2</sub> on each side were measured. Wafer thicknesses of 0.003, 0.006, 0.013 and 0.024 inch were used. They all had resistivities of about 50 ohm-cm, which is typical for this type of isolation material. Since essentially all of the field appears in the SiO<sub>2</sub>, it is not possible to calculate a dielectric constant for such a composite independent of its thickness. However, for a 0.003 inch thickness (which is a typical isolation spacing in an integrated circuit), the effective dielectric constant is 48. This figure increases linearly with thickness. The low-frequency loss tangent was found to be about 0.001 for the polycrystalline silicon isolation material, but increased steadily with frequency as shown in Figure 10. In the vicinity of 250 MHz, the losses increase so rapidly that the material is no longer useful as an isolation medium.

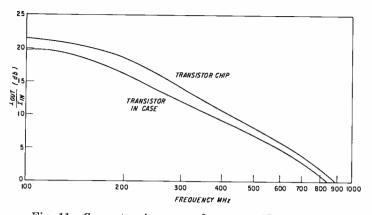

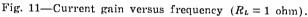

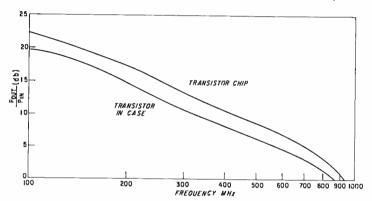

These measurements were confirmed by measuring the isolation impedance between identical silicon pads on CA 3005 rf-mixer-circuit pellets having both ceramic isolation and polycrystalline-silicon isolation. These results are shown in Figure 11. In this figure, an area

Fig. 10-Low-frequency loss tangent versus frequency.

corresponding to the estimated performance for a p-n junction isolation is indicated by shading. This estimate is based on the known frequency limitations of integrated circuits, and the data of Maxwell et al,<sup>3</sup> which show that the parasitic capacitance of a p-n junction is 10 times as great as it is for polycrystalline silicon/SiO<sub>2</sub> isolation.

Maxwell et al also found that the leakage current is reduced by a factor of  $10^7$  when polycrystalline silicon SiO<sub>2</sub> isolation is used in place of p-n junction isolation. In the case of ceramic isolation, one would expect another order of magnitude improvement due to the increased thickness of the dielectric.

The breakdown voltage of a 0.003-inch-thick sample of the glassceramic substrate was found to be in excess of 6000 volts. A sample

<sup>&</sup>lt;sup>3</sup> D. A. Maxwell, R. B. Beeson, and D. F. Allison, "The Minimization of Parasitics in Integrated Circuits by Dielectric Isolation," *IEEE Trans. on Electron Devices*, Vol. ED-12, p. 20, Jan. 1965.

Fig. 11—Isolation impedance versus frequency for various types of isolation.

of polycrystalline silicon 0.003-inch thick having 4 microns of  $SiO_2$ on each side was found to have a breakdown voltage of 1500 volts. This is in agreement with the results of Schnable et al<sup>4</sup> who found a breakdown strength of 200 volts/micron for SiO<sub>2</sub> isolation layers.

Table I summarizes the relative electrical characteristics of the three types of isolation that have been discussed. It should be noted that the breakdown voltage for both p-n junction isolation and  $Si/SiO_2$  isolation is independent of the spacing between regions, while the breakdown voltage between regions in a ceramic-isolated structure can be made larger by increasing the space between devices. It may ultimately be limited by surface leakage.

| Table I                                            |                  |                 |         |  |  |  |

|----------------------------------------------------|------------------|-----------------|---------|--|--|--|

|                                                    | p-n junction     | poly Si<br>SiO: | Ceramic |  |  |  |

| Parasitic Capacitance (Relative)                   | 80               | 10              | 1       |  |  |  |

| Leakage Current (Relative)                         | 108              | 10              | 1       |  |  |  |

| Voltage Breakdown for 0.003 inch Spacin<br>(Volts) | <sup>1g</sup> 50 | 1500            | 6000    |  |  |  |

| Maximum Usable Frequency (MHz)                     | 150              | 250             | >9000   |  |  |  |

<sup>4</sup>G. L. Schnable, A. F. McKelvey, and J. A. Hastings, "A Chemical Technique for Preparing Oxide-Isolated Silicon Wafers for Microcircuits," *Electrochemical Technology*, Vol. 4, p. 57, Jan.-Feb. 1966.

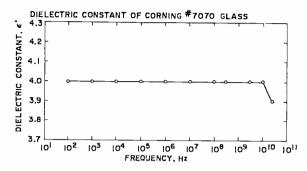

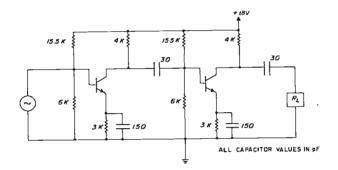

#### Electrical Characteristics of the Glass Refill

The dielectric properties of the Corning #7070 borosilicate glass used as an isolation medium have been reported by von Hippel.<sup>5</sup> The properties compare favorably with those of the glass-ceramic material measurements reported above. Figures 12 and 13 show the dielectric constant  $\epsilon'$  and the dissipation factor, tan  $\delta$ , versus frequency as reported by von Hippel.

#### Electrical Characteristics of Decal Isolation

In the case of the Decal structure, the dielectric between the devices is a composite of air and Corning #7070 glass. For practical purposes, air is a perfect dielectric with  $\epsilon' = 1$  and  $\tan \delta = 0$  from dc to at least 10<sup>10</sup> Hz.

For air, glass, or glass-ceramic isolation, then, the performance as a dielectric is excellent from dc to the GHz region.

Fig. 13-Dissipation factor as a function of frequency between 20°-25°C.

<sup>&</sup>lt;sup>5</sup> A. R. Von Hippel, Tables of Dielectric Materials in *Dielectric Materials and Applications*, p. 291, John Wiley & Sons, Inc., N.Y., 1954.

#### ELECTRICAL PERFORMANCE OF DIELECTRICALLY ISOLATED CIRCUITS

As described above, operative rf-mixer circuits of the type shown in Figure 4 were prepared using glass-ceramic refill, glass refill, and Decal air isolation. As references, the same circuit was also constructed in p-n junction and polycrystalline silicon refill form. Although the circuit was not designed specifically for dielectric isolation, a modest improvement in the performance of the dielectrically isolated versions at high frequencies was obtained. Quantitative measurements have been made only for the glass-ceramic refill, the p-n junction and the polycrystalline refill circuits. For these versions the useful frequency range, defined as the frequency at which the real part of the forward transfer admittance  $(g_{21})$  falls to 1 mmho is

| standard p-n junction  | isolation | 200 | MHz |

|------------------------|-----------|-----|-----|

| polycrystalline refill |           | 280 | MHz |

| glass-ceramic refill   |           | 300 | MHz |

The performance of the glass refill and the Decal air-isolated circuits should be comparable to that of the glass-ceramic refill circuits. Improved test vehicles are currently being designed and fabricated by these various isolation techniques so that a more detailed evaluation can be obtained. From even this preliminary data, however, it is clear that true dielectric isolation will afford a substantial improvement in performance at high frequencies, compared with conventional p-n junction or polycrystalline refill isolation.

#### DISCUSSION

The handle-wafer method with either glass-ceramic or an all-glass dielectric refill is suitable for tightly packed, small-geometry arrays of randomly shaped devices, since the isolation grooves need only be 10-20 microns deep. The isolated array of devices is planar, thereby providing a surface on which passive components and the metallization can readily be fabricated.

This process also affords the possibility of providing isolated silicon areas of different types and resistivities. This can be done by bonding and lapping the back off one mesa wafer and then bonding a second mesa wafer to the same handle and lapping the back off it.

The Decal structure (with its possible variations) provides a very simple and versatile approach to isolation, as well as opening attractive possibilities for low-cost packaging methods. The isolated units may be scribed, broken apart, mounted, and wire bonded in the same way that monolithic circuits are presently handled. Alternatively, the circuit pellets can be inverted and bonded directly to a circuit board or an inexpensive header that needs no hermetic sealing.

Large arrays can also be prepared by this process by letting an entire wafer or a substantial part of a wafer serve as a single, interconnected circuit. Outboard components can be readily connected into the circuit, since direct access to any lead in the circuit area can be provided.

The Decal process also offers the possibility of making a structure having a very low thermal resistance; the junctions are only 10-20 microns from the back of the silicon regions. In a conventional chip, the heat must be transferred through about 125 microns of silicon before it reaches the heat sink. Thus the thermal resistance between the junctions and a heat sink could be made lower for a Decal circuit than for its conventional counterpart.

It is possible to utilize the isolated circuits that have been described here in several ways. If large arrays are required, the circuits can be interconnected by a metallization pattern on the wafer. Alternatively, the wafers can be scribed and broken into circuit chips and then mounted and bonded in the same way that conventional circuit chips are handled.

It is also possible to leave space on the wafer for the fabrication of thin-film passive components that can be connected into the circuit when the devices are metallized. Since the dielectric portion of the wafer can be made larger than the silicon wafer, the passive components may be fabricated on the peripheral areas without using valuable silicon area in the center. Because of the general coplanarity of all components, one-shot interconnections can still be made.

Often it is desirable to use strip-line techniques in the interconnection of high-frequency circuits. In such cases, the dielectric could be brought to the required thickness by abrasion. The dielectric could then be coated with metal by evaporation or other suitable deposition methods to give controlled-impedance circuitry.

## CONCLUSIONS

Three methods of providing dielectric isolation for silicon integrated circuits have been described.

In addition to the electrical benefits of dielectric isolation (i.e., extended frequency range, higher voltage breakdown and improved radiation resistance), new circuit configurations and packaging techniques are also made possible. Space can be made available for depositing passive components side by side with the semiconductor devices. It is feasible to provide precision microstrip lines and ground planes and to operate a large number of devices in parallel (to get high power at high frequencies) without the need for fabricating such interconnecting elements externally. This is particularly useful for solid-state microwave applications.

When isolating Dccal circuits, it is possible to provide access to bonding pads anywhere on the wafer area. Bonding is not restricted to the periphery. The process results in a flip-type circuit package than can be batch fabricated and that can further be packaged into a low-cost conventional lead package without the need for wire bonding.

## ACKNOWLEDGMENTS

The authors wish to acknowledge, and express their appreciation for, the many contributions to this work made by their colleagues. In particular, they are indebted to J. Vossen and T. Walsh for the dielectric measurements, to B. Tilley for the high-frequency circuit measurements, to F. Duigon for the fabrication of the device wafers, to J. Shaw for the tungsten metallization, and to W. Kern and R. Heim for their technical assistance concerning the glassing techniques. Also, the authors wish to thank J. Amick and N. E. Wolff for their guidance, support, and constructive review of the manuscript.

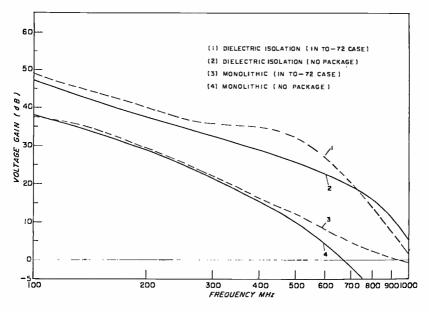

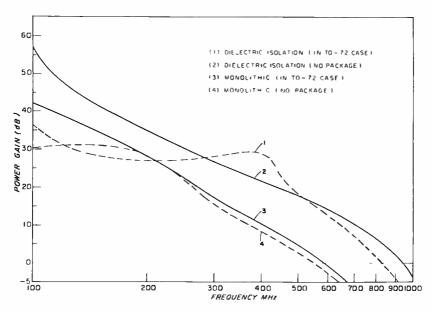

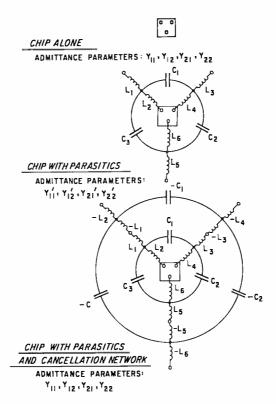

## RELATIONSHIP BETWEEN THE PERFORMANCE OF A LINEAR AMPLIFIER MICROCIRCUIT AND THE ISOLATION TECHNIQUE USED IN ITS CONSTRUCTION

## By

## A. I. STOLLER

**RCA Laboratories** Princeton, N. J.

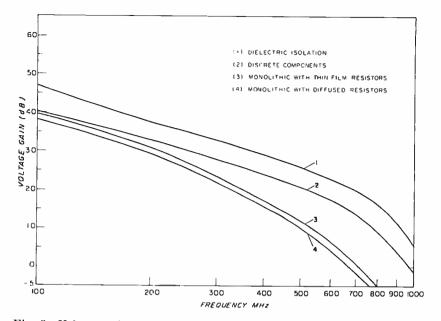

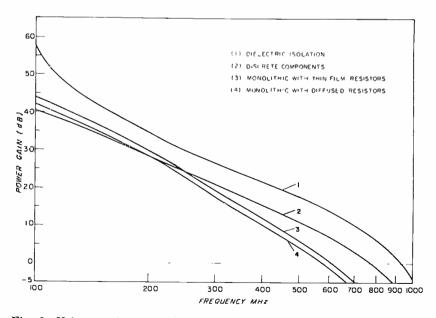

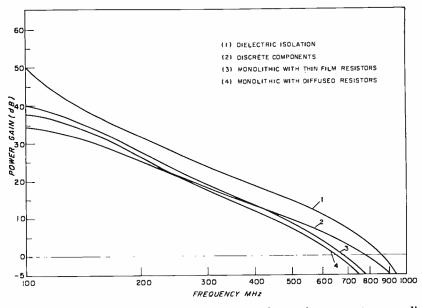

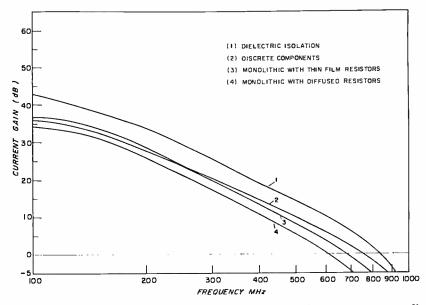

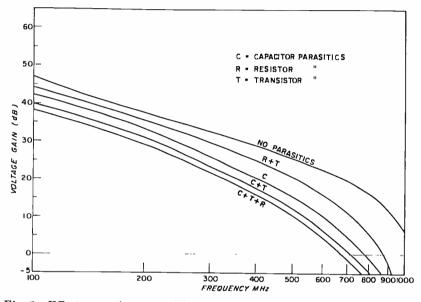

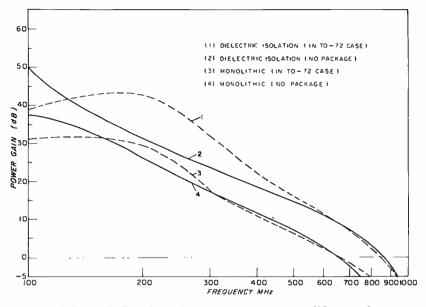

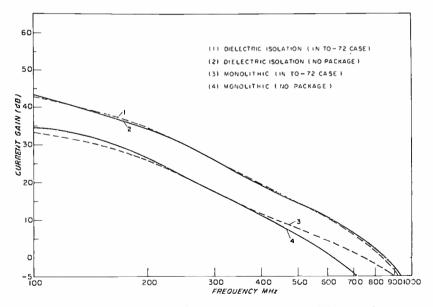

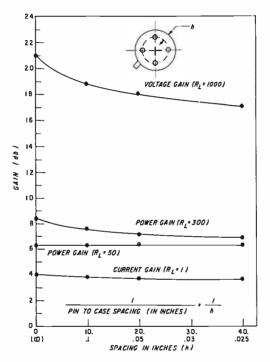

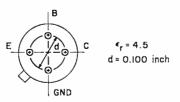

Summary—The high-frequency-performance curves for a linear integrated circuit prepared in a cariety of configurations employing dielectric or junction isolated components were evaluated. The response of the circuit, a 2-stage linear amplifier, is eastly improved in the 0.1 to 1 GHz range by use of a dielectrically isolated structure rather than the standard monolithic structure. A small improvement over the standard monolithic structure is also obtained if thin-film resistors rather than diffused resistors are employed in an otherwise monolithic integrated circuit.

Because of transistor package parasitics, the circuit assembled from discrete components is inferior to its dielectrically isolated counterpart, although it gives better performance than the monolithic version. This analysis has shown, however, that mounting an integrated-circuit chip in a standard package may lead to improved performance in some frequency ranges, since the series lead inductance of the package tends to compensate for the capacitive input impedance of the chip.

#### INTRODUCTION

N THE PAST few years a great deal of work has been carried out<sup>1,9</sup> on techniques for providing dielectric isolation for integrated circuits. The principle motivation for this work is the desire to

<sup>1</sup> A. I. Stoller, J. A. Amick, and N. E. Wolff, "Getting the Most Out of Circuits with Dielectric Isolation," *Electronics*, Vol. 40, p. 97, March 20,

<sup>2</sup> A. I. Stoller and N. E. Wolff, "Isolation Techniques for Integrated Circuits," Proc. 2nd Int. Cong. on Microelectronics, p. 269, R. Oldenbourg, Munich, Germany, 1967.

<sup>3</sup> D. McWilliams, C. Fa, G. Larchian, and O. Maxwell, "A New Di-ter Circuits," Proc. 2nd Circuits, "A New Di-

<sup>3</sup> D. McWilliams, C. Fa, G. Larchian, and O. Maxwell, "A New Di-e'ectric Isolation Technique for High Quality Silicon Integrated Circuits,"

Jour. Electrochem. Soc., Vol. 111, p. 153C, July 1964. <sup>4</sup> T. V. Sikina, B. D. Joyce, N. P. Formigoni, C. C. Roe, and F. Schlies-ing, "A Novel Oxide Isolation Process," Int. Electron Devices Meeting, Washington, D. C., Oct. 20-22, 1965.

T. H. Ramsey and T. Smith, "A Process for Ceramic Dielectric Isola-tion for Integrated Circuits," Int. Electron Devices Meeting, Washington,

tion for integrated Circuits," Int. Electron Devices Meeting, Washington,

D. C., p. 14, Oct. 26-28, 1966.

B. L. Frescura, R. Rusert, and J. Schroeder, "Mesa Isolation—and Isolation Technique for Integrated Circuits," Int. Electron Devices Meeting,

Washington, D. C., p. 13, Oct. 26-28, 1966.

<sup>\*</sup> M. P. Lepselter, "Beam-Lead Scaled-Junction Technology," Bell Laboratories Record, Vol. 44, p. 298, Oct/Nov, 1966.

<sup>\*</sup> D. A. Naumik, "Silicon Magnic for Integrated Davices," IEEE Trans.

<sup>a</sup>D. A. Maxwell and R. H. Beeson, "The Minimization of Parasitics in Integrated Circuits by Dielectric Isolation," *IEEE Trans.* on Electron Devices, Vol. ED-12, p. 497 (Correspondence) Sept. 1965. <sup>a</sup>D. A. Maxwell and R. H. Beeson, "The Minimization of Parasitics in Integrated Circuits by Dielectric Isolation," *IEEE Trans. on Electron De*vices, Vol. ED-12(1), p. 20, Jan. 1965.

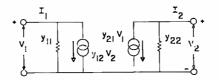

eliminate the parasitic capacitances associated with the p-n junctions used to isolate components in conventional monolithic integrated circuits. The performance of a circuit can be considerably improved, especially at high frequencies, if these parasitic capacitances are eliminated. This paper presents a quantitative evaluation of the relative performance of integrated circuits employing several different methods of isolation.

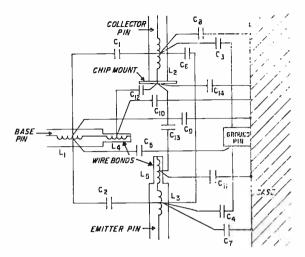

#### CIRCUIT DESIGN

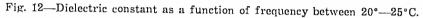

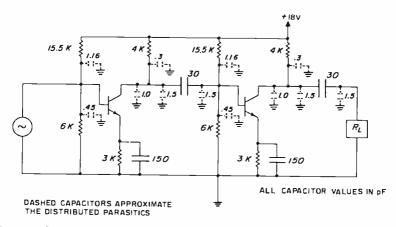

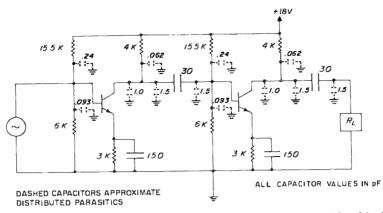

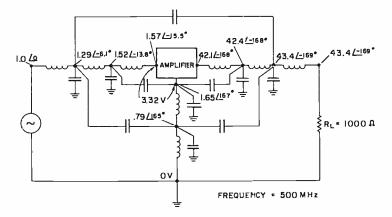

The circuit chosen for the analysis is a 2-stage, common-emitter *RC*-coupled, wide-band amplifier. This uncomplicated type of circuit

Fig. 1-Two-stage amplifier in dielectric isolation configuration.

was selected so that the performance curves could be readily interpreted. The design is such that the circuit can actually be fabricated in integrated form if desired. Also, in choosing a circuit vehicle for evaluating the effects of isolation parasitic capacitance, it is necessary to use transistors capable of performing at high frequencies. The dielectrically isolated form of the circuit is shown in Figure 1.

This circuit is not intended for any particular application, nor is it suggested that the design is optimum. It is intended only to represent a realistic linear circuit comprised of transistors, resistors, and capacitors. The significant aspect of the computations is the *relative* performance of several different forms of this circuit, rather than the absolute performance.

## CIRCUIT ELEMENTS

## Transistors

The transistor type selected for the circuit is the 2N2857 rf tran-

sistor, which has a gain-bandwidth product  $(f_T)$  of 1 GHz. Since it is a silicon, n-p-n epitaxial planar device, it could be fabricated as an integrated-circuit component. No equivalent-circuit model for the transistor was devised; instead the more realistic, frequency-dependent yparameters of the device were used directly in the computer simulation. Columns (A) in Table I give the parameters for the transistors in a standard metal package as shown in the published data sheets.<sup>10</sup> Columns (B) represent the parameters for the transistor in the chip form. The y-parameters for the transistor chip were estimated by correcting the values given in the published data sheet for the package parasitics using the technique described in Reference (11).

The y-parameters are given in the data sheet for the biasing conditions of 1.5 mA of collector current  $(I_{tr})$  which the biasing networks of the 2-stage amplifier were designed to provide.

## Signal Source

The input signal is assumed to be from a small-signal voltage source having zero internal impedance. This eliminates any variations in gain arising from variations in the mismatch of the source to the circuit impedance as the circuit is modified. Such variations would arbitrarily mask the effects of the parasitics, since the source impedance of a real circuit could, in principle, be matched to the input impedance of the amplifier. Subsequent calculations were carried out using finite source impedances. These indicate that the conclusions arrived at by using the zero-impedance source are also valid for finiteimpedance sources.

## **Bias** Network

Resistor values much greater than the maximum of 15,500 ohms used here would give rise to inordinately high parasitics and occupy an impractically large area if they were fabricated in a monolithic integrated form and therefore were avoided.

## **Emitter-Bypass Capacitors**

The value of 150 pF used for the emitter-bypass capacitors pro-

<sup>&</sup>lt;sup>10</sup> File No. 61 (9-66) RCA Semiconductor Products Databook, Electronic Components, Harrison, N. J.

<sup>&</sup>quot;A. I. Stoller, "Calculation of the Electrical Parameters of Transistor Chips from Measurements Made on Packaged Devices," *RCA Review*, Vol. 29, p. 600, Dec. 1968.

| December |

|----------|

| 1968     |

Table I- y-Parameters: Columns A Give Values in Package as Shown in Published Data Sheets; Columns B Give Values for the Chip (All Values Are in Millimhos).

|                    |      | y    | 11   |      |       | V  | /12      |          | <i>Yn</i> |    |         |     |       |          |      |              |

|--------------------|------|------|------|------|-------|----|----------|----------|-----------|----|---------|-----|-------|----------|------|--------------|

| Frequency<br>(MHz) | 9    | 7.1  | b    | 11   | $g_1$ | :  | b        | 12       | g.        | a  | b       | ei  | $g_z$ | <u> </u> | b_#  | <del>.</del> |

|                    | A    | В    | Λ    | В    | A     | В  | A        | В        | A         | B  | _A      | B   | _A    | B        | A    | B            |

| 100                | 1.0  | .64  | 5.0  | 4.2  | 0     | 0  | — .3     | <u> </u> | 46        | 48 | —18     | -14 | .1    | .1       | 1.0  | 0            |

| 200                | 2.5  | 1.8  | 7.0  | 5.6  | 0     | 0  | 9. —     | <u> </u> | 40        | 46 | 27      | -20 | .2    | !        | 1.8  | 0            |

| 300                | 6.5  | 5.2  | 9.0  | 8.0  | 0     | 0  | 1.4      | <u> </u> | 32        | 43 | 32      | -22 | .3    | .9       | 2.5  | 0            |

| 400                | 10.0 | 7.7  | 10.5 | 10.4 | 0     | 0  | -1.8     | .8 —     | 25        | 38 |         | -22 | .4    | 1.0      | 4.0  | 0            |

| 500                | 13.5 | 9.7  | 12.0 | 13.1 | 0     | 0  | 2.3      | -1.0     | 19        | 35 | 36      | -22 | .5    | 1.3      | 5.5  | .3           |

| 600                | 15.5 | 10.0 | 13.5 | 14.3 |       | 0  | 2.7      | -1.0     | 13        | 28 | <b></b> | -20 | 6.    | 1.4      | 6.5  | .4           |

| 700                | 18.0 | 10.3 | 15.0 | 15.3 | .3    | 0  | 3.0      | -1.0     | 8         | 22 | -32     |     | .8    | 1.4      | 8.2  | • (          |

| 800                | 20.0 | 9.8  | 17.0 | 15.6 | 35    | 0  | 3.3      | 1.0      | 4         | 16 | -29     | -16 | 1.0   | 1.4      | 9.5  | .9           |

| 900                | 22.0 | 8.8  | 19.0 | 15.2 | 4     | 16 | -3.6     | -1.0     | 3         | 11 | 25      |     | 1.2   | 1.4      | 11.0 | 1.3          |

| 1000               | 23.0 | 7.9  | 21.0 | 14.0 | 5     | 26 | <u> </u> | 1.0      | 2         | 7  | 20      | 8_  | 1 1.4 | 1.3      | 12.3 | $_{1.5}$ _   |

vides a 10.8-ohm bypass at 100 MHz, the lowest frequency used in the analysis. Lower values of bypass capacitance were found to result in input impedances having a large negative real component at the lower frequencies, which could lead to instability in the amplifier. Since one side of each of the bypass capacitors is grounded, any parasitic capacitances from the bottom electrodes to the substrate would be short circuited and would not affect the response of the amplifier. Also, the voltages across these capacitors are low and of constant polarity. These noncritical requirements for the bypass capacitors can readily be met in an integrated circuit by using standard integrated capacitor structures, such as diffused junction capacitors, diffused MOS capacitors, or thin-film capacitors.

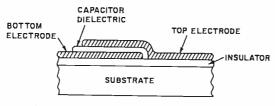

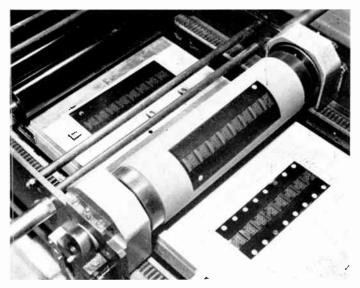

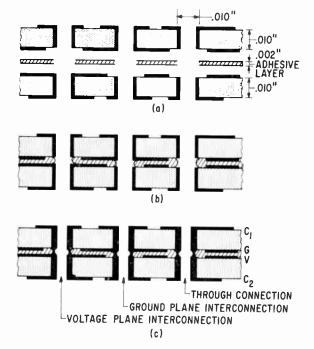

Fig. 2-Thin-film capacitance structure.

## **Coupling** Capacitors

The requirements on the coupling capacitors are more restrictive than the requirements on the bypass capacitors. They should be lowloss capacitors capable of supporting the supply voltage, in this case 18 volts. Also, parasitic capacitances to the substrate must be kept small in order to avoid a shunting of the signal to ground at high frequencies. These requirements can be satisfied by a thin-film capacitance structure such as that shown in Figure 2.

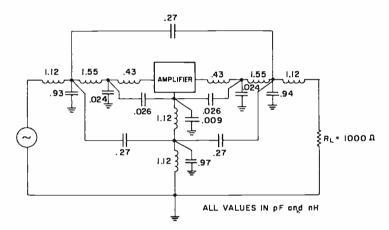

## CIRCUIT MODELS ANALYZED

The basic amplifier shown in Figure 1 was analyzed using the circuit analysis program compiled by Ressler,<sup>12</sup> assuming the various constructions described in the following paragraphs. The appropriate parasities for each assumed construction technique were included in the computer program.

<sup>&</sup>quot; D. G. Ressler, private communication.

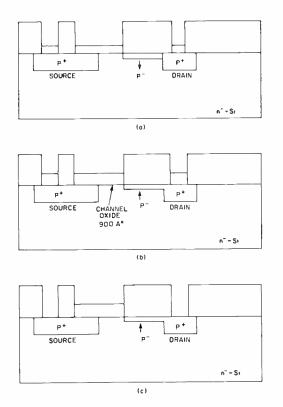

## **Dielectrically Isolated Circuit**

The dielectrically isolated model assumes that the circuit elements are completely isolated from each other and spaced and interconnected as if on a monolithic integrated-circuit chip. The Decal<sup>1,2</sup> or Air-Isolated Monolith  $(AIM)^{**}$  types of integrated circuit structures (in which the elements are essentially air isolated from each other) closely approximate the condition of ideal isolation. A discussion of the various types of dielectric isolation is beyond the scope of this paper, but can be found elsewhere.<sup>1:9</sup> For this analysis, the circuit of Figure 1 was used with no parasitics added. The transistor y-parameters for the chip (B columns of Table I) were used.

## Discrete Transistor Circuit

The circuit of Figure 1 was re-analyzed, but this time the transistor y-parameters in the conventional hermetic package (A columns of Table I) were used. The purpose of this calculation is to determine the effect that the transistor package parasitics have on the circuit if packaged transistors are used in conjunction with an ideal thin-film passive network. Additional stray capacitances and inductances that are not taken into consideration here would be present in the interconnections of a discrete-component circuit. Therefore this model represents the most optimistic result possible for a discrete-component version of the amplifier.

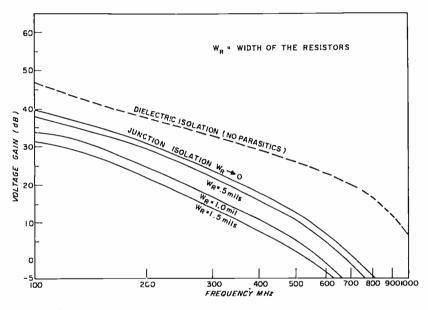

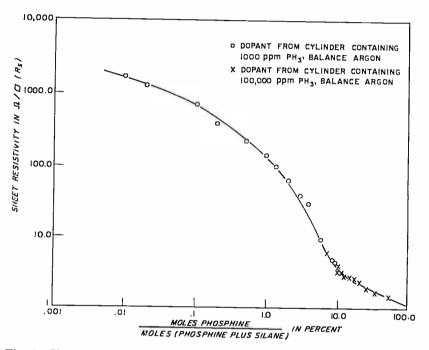

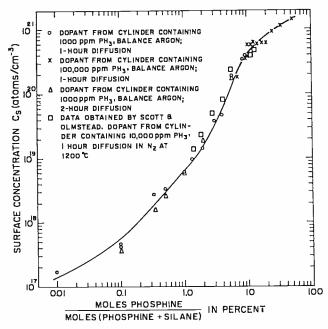

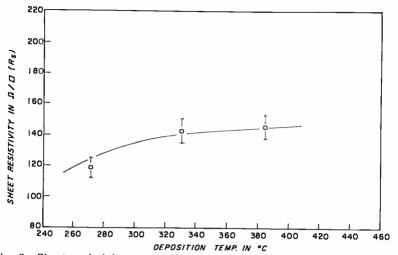

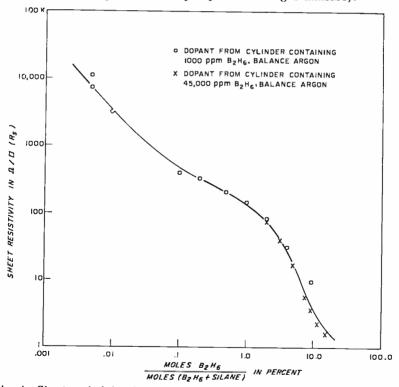

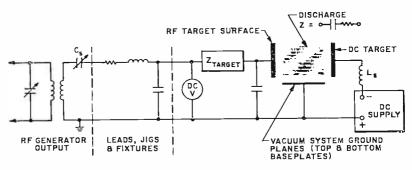

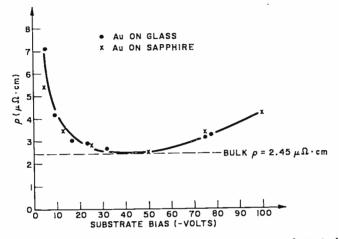

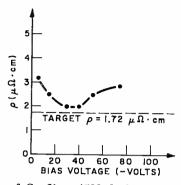

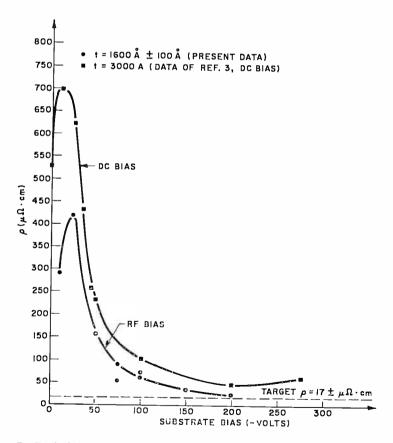

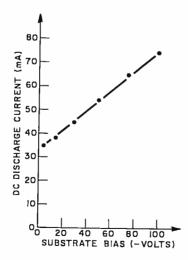

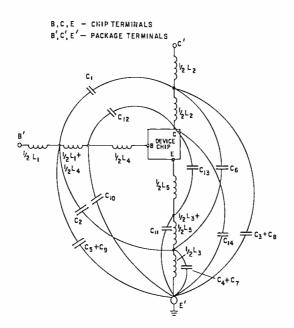

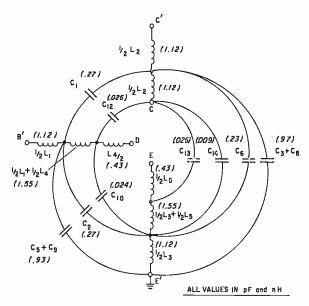

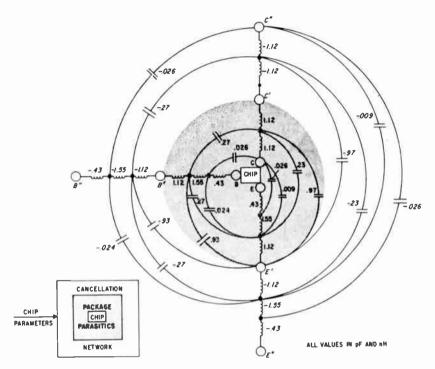

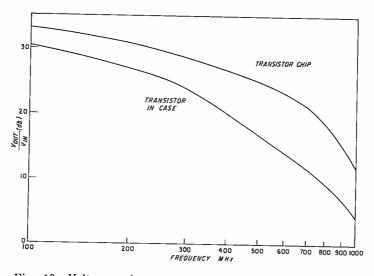

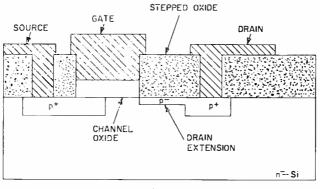

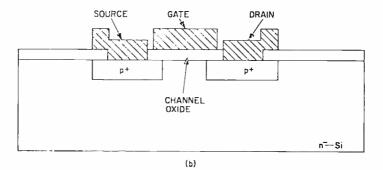

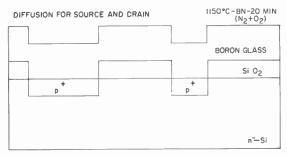

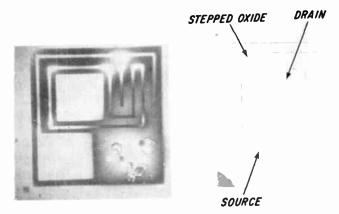

## Monolithic Integrated Circuit with Diffused Resistors