# RB/I Review

**March 1976**

Volume 37 No. 1

RCARCI 37(1) 1-156(1976)

RCA Review, published quarterly in March, June, September and December by RCA Research and Engineering, RCA Corporation, Princeton, New Jersey 08540. Entered as second class matter July 3, 1950 under the Act of March 3, 1879. Second-class postage paid at Princeton, New Jersey, and at additional mailing offices. Effective Jan. 1, 1971, subscription rates as follows: United States and Canada: one year \$6.00, two years \$10.50, three years \$13.50; in other countries, one year \$54.0, two years \$11.30, three years \$14.70. Single copies (except for special issues) up to five years old \$3.00. Ň

A technical journal published quarterly by RCA Research and Engineering in cooperation with the subsidiaries and divisions of RCA.

## Contents

- 3 CVD Glass Films for Passivation of Silicon Devices: Preparation, Composition, and Stress Properties Werner Kern, G. L. Schnable, and A. W. Fisher

- 55 Densification of Vapor-Deposited Phosphosilicate Glass Films Werner Kern

- 78 Analysis of Glass Passivation Layers on Integrated-Circuit Pellets by Precision Etching Werner Kern

- 107 Contact Resistance of Metal-Silicon System at Microwave Frequencies Y. S. Chiang, E. J. Denlinger, and C. P. Wen

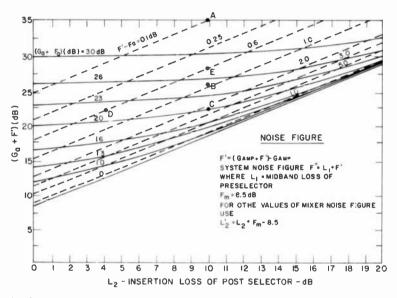

- 119 Noise Performance Factors in Television Tuners Stewart M. Perlow

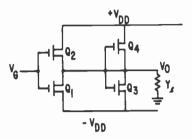

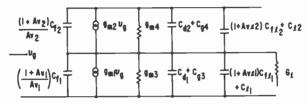

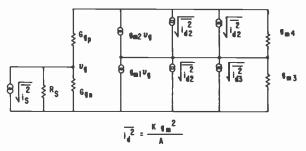

- 136 A COS/MOS Linear Amplifier Stage S. T. Hsu

- 149 Technical Papers

- 150 Patents

- 154 Authors

#### **RCA Corporation**

A. L. Conrad President and Chief Executive Officer

#### **Editorial Advisory Board**

# Chairman, J. A. Rajchman RCA Laboratories

A. A. Ahmed Solid State Division

- E. D. Becken RCA Global Communications

- D. M. Cottler Government and Commercial Systems

- N. L. Gordon RCA Laboratories

- G. C. Hennessy RCA Laboratories

- G. B. Herzog RCA Laboratories

- J. Hillier RCA Research and Engineering

- E. O. Johnson RCA Research Laboratories, Inc., Tokyo

- C. H. Lane Picture Tube Division

- D. S. McCoy Consumer Electronics

- K. H. Powers RCA Laboratories

- R. E. Quinn RCA Laboratories

- P. Rappaport RCA Laboratories

- J. H. Scott, Jr. RCA Laboratories

- L. A. Shotliff International Licensing

- T. O. Stanley, RCA Laboratories

- F. Sterzer RCA Laboratories

- J. J. Tietjen RCA Laboratories

- W. M. Webster RCA Laboratories

Secretary, Charles C. Foster RCA Laboratories

Editor Ralph F. Ciafone

#### Associate Editors

- W. A. Chisholm RCA Limited (Canada)

- D. R. Higgs Missile and Surface Radar Division

- W. A. Howard National Broadcasting Company

- **C. Hoyt** Consumer Electronics

- E. McElwee Solid-State Division

- J. C. Phillips RCA Research and Engineering

- M. G. Pietz Government and Commercial Systems

- C. W. Sall RCA Laboratories

- I. M. Seideman Astro-Electronics Division

- W. S. Sepich Commercial Communicatons Systems Division

- J. E. Steoger RCA Service Company

© RCA Corporation 1976 All Rights Reserved Printed in USA

# CVD Glass Films for Passivation of Silicon Devices: Preparation, Composition, and Stress Properties\*

Werner Kern, G. L. Schnable, and A. W. Fisher

RCA Laboratories, Princeton, N.J. 08540

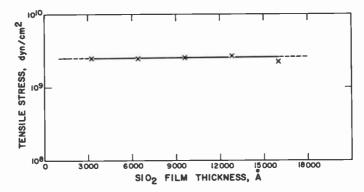

Abstract-Results of studies are described for successful glass passivation, by chemical vapor deposition (CVD), of metallized silicon planar integrated circuits. The effects of various process conditions for low-temperature (350° to 450°C) CVD of phosphosilicate glass layers by oxidation of silane plus phosphine were systematically correlated with the chemical composition and intrinsic stress properties of deposited films. A practical method has been developed and applied for measuring stress in CVD films deposited on silicon wafers; it requires no special fixtures during deposition and is thus applicable for any type of deposition system. A correlation has been demonstrated between intrinsic stress in deposited films and susceptibility to cracking during deposition or during subsequent exposure to thermal stress conditions, particularly at processing temperatures higher than the deposition temperature. Low phosphorus content in deposited films was correlated with excessive intrinsic tensile stress leading to crack formation. CVD conditions were established for attaining low stress films, and a new technique was devised for achieving further reduction in intrinsic tensile stress of CVD films based on the introduction of water vapor in the reaction chamber during film formation. Finally, the causes of structural defects in CVD glass layer are critically reviewed, and some experimental results on photolithographically induced defects are presented.

#### 1. Introduction

The terms "glassing" and "glass passivation" are commonly used to denote the process in which a glass-like, amorphous, inorganic dielectric layer is formed over the surface of a completed microcircuit wafer

<sup>\*</sup> This work was in part supported by the Air Force Materials Laboratory, Wright-Patterson Air Force Base, Ohio, under Contract No. F33615-74-C-5146. Portions of this paper were presented verbally at NAECON '75, and an extended summary was included in the proceedings volume.

for the purpose of protection against the ambient. The sequence for glass passivation consists of deposition of the dielectric layer over the entire surface of the device wafer with completed metallization patterns, followed by photolithographic delineation to remove glass from the central region of bonding pads and from scribe line areas. Typical deposited films are 0.5 to 2  $\mu$ m thick.

The majority of modern integrated circuits (IC's) are metallized with aluminum. A compatible glass passivation process must therefore be performed under conditions where the maximum processing temperature is below the Al-Si eutectic temperature (577°C) to avoid alloying or metallization melting problems. Similar considerations hold for metallization systems involving gold. Chemical vapor deposition (CVD) of dielectric films at low temperature (300° to 500°C) is ideally suited to fulfill these requirements. Reactive sputtering, rf sputtering, and plasma deposition techniques can also be used for depositing dielectric layers, but their use is generally limited to certain applications and to devices that are not degraded by these treatments.

Glassing of microcircuit wafers was originally used to provide a mechanical protection against scratches of the soft aluminum interconnect lines. Vitreous silicon dioxide (SiO<sub>2</sub>) prepared by CVD was first applied as the passivating glass, and is still being used by a number of IC manufacturers. However, to provide effective protection, an SiO<sub>2</sub> film thickness incompatible with the aluminum metallization is required, and cracking of the oxide film will generally result, with consequent problems of device reliability. Device manufacturers who have recognized these shortcomings have substituted more compatible lower-stress films of binary silicate glasses, especially phosphosilicate glass (PSG) films, for the more highly stressed SiO<sub>2</sub> layers.

Intrinsic stress in passivation films is a major factor in determining whether cracks occur in glass over metallization on IC's. Since cracks in the passivation glass can result in substantially lower IC reliability, a detailed knowledge of the effect of CVD deposition conditions on room-temperature stress of CVD films of SiO<sub>2</sub> and PSG on silicon wafer substrates would be of great value.

This paper presents a thorough survey of the subject matter and, in addition, provides new experimental data on the effects of systematic variations in deposition conditions on the film deposition rate, thickness uniformity, chemical composition, and intrinsic stress. The experimental results are examined in relation to data available in the literature. New results, therefore, are presented in the section to which they relate, rather than being grouped under a general discussion. In addition, the effects of post-deposition storage and densification treatments on film stress are examined. Here, again, new experimental results are presented on the origin of localized structural defects in the glass layers. Analytical methods suitable for process control are also briefly outlined.

A large portion of this paper is contained in a report recently prepared by us on IC passivation by CVD techniques.<sup>1</sup> Several related papers should also be mentioned for reference: a summary of the effects of critical factors in the CVD of SiO<sub>2</sub> and PSG;<sup>2</sup> a survey of CVD reactor systems;<sup>2,3</sup> a discussion of functions, applications, and benefits of CVD passivation overcoatings;<sup>3</sup> studies on glass densification;<sup>4</sup> electrical properties of dielectric films;<sup>5</sup> new methods for defect detection;<sup>6</sup> and selective etching analysis of passivation films.<sup>7,8</sup> Finally, a comprehensive, recently published survey paper<sup>9</sup> reviews the entire field of silicon device passivation and may serve as a source of general background material in the present work.

# 2. General Considerations Pertaining to CVD Processing and Stress Measurements

# 2.1 Basic CVD Hydride Reactions

The basic process for depositing  $SiO_2$  films from silane and oxygen at low temperatures (250° to 550°C) was reported in 1967.<sup>10</sup> The exact details of this thermally activated, surface-catalyzed, heterogeneous branching-chain reaction are complex.<sup>11</sup> The overall reaction can be expressed as

$$\operatorname{SiH}_4(g) + 2\operatorname{O}_2(g) \to \operatorname{SiO}_2(g) + 2\operatorname{H}_2\operatorname{O}(g),$$

[1]

but under some circumstances it may proceed as

$$\operatorname{SiH}_4(\mathbf{g}) + \operatorname{O}_2(\mathbf{g}) \to \operatorname{SiO}_2(\mathbf{s}) + 2\operatorname{H}_2(\mathbf{g}).$$

[2]

The reaction favored depends strongly on deposition temperature and silane concentration,<sup>10-14</sup> and probably also on the oxygen-tohydride ratio and variations in reactor geometry.

Phosphorus can be incorporated into the oxide layers as an oxide of phosphorus by the reaction of phosphine with oxygen,

$$2PH_3(g) + 4O_2(g) \rightarrow P_2O_5(s) + 3H_2O(g).$$

[3]

Co-oxidation with silane leads to phosphosilicate glasses.<sup>14-19</sup>

The preparation, properties, and applications of  $SiO_2$  and PSG films synthesized from the hydrides and oxygen have been described extensively in the literature<sup>10,12-32,68,69</sup> and will be further referred to.

Specific effects of CVD parameters on the reaction chemistry are discussed in Section 4 of this paper.

# 2.2 Summary of Critical Factors in CVD

The exact conditions used in the CVD process for  $SiO_2$  and PSG films can critically affect important film properties. Primary CVD parameters that affect deposited film properties, and must therefore be carefully optimized and controlled, include the following, listed in their approximate order of importance:

(1) Substrate temperature of deposition

(2) Oxygen-to-hydride ratio

(3) Hydride flow rate

(4) Silane-to-phosphine ratio

(5) Nitrogen flow rate

(6) Geometry of reaction chamber and gas inlet/outlet configurations

(7) Wall temperature of reaction chamber or gas disperser

(8) Impurities in CVD system and gases

(9) Gas additives

(10) Nature and cleanliness of substrate surface

(11) Geometry and topography of substrate

(12) Type of CVD reactor system

The effects of these factors on the film deposition rate, the thickness uniformity, the chemical composition (in the case of PSG), and the intrinsic stress are discussed and illustrated with experimental results in Sections 4 and 5.

# 2.3 Compatibility of Deposition Temperature with Metallization

The theoretical maximum temperature that can be used in processing devices metallized with aluminum is limited by the melting point of the eutectic formed between silicon and aluminum (577°C). In practice, however, the maximum temperature during glass deposition is held below 500°C because solid-state reactions between aluminum and silicon (or SiO<sub>2</sub>) begin to exert degrading effects in many sensitive devices at approximately 500°C. Some reaction of aluminum with SiO<sub>2</sub> or PSG can be detected in certain devices at temperatures as low as 400°C, forming a thin intermediate layer of aluminosilicate, but normally this presents no serious problems if proper etching techniques are used in delineation of the glass layer to expose the bonding pads and scribe lines.

PSG overcoats have also been used over gold-metallized silicon devices.<sup>33</sup> In this application the temperature of glass deposition must be kept below 350°C to avoid problems of eutectic formation between silicon and gold (373°C).

An up-to-date bibliography of many other related aspects of metallization materials for silicon devices became available recently.<sup>34</sup>

# 2.4 Layer Combinations

Combinations of PSG and SiO<sub>2</sub> layers can offer certain advantages over any one single layer. Structures consisting of SiO<sub>2</sub> over PSG, or of SiO<sub>2</sub>/PSG/SiO<sub>2</sub>, can be readily prepared by CVD techniques, often in one continuous operation, simply by regulating the hydride input in the gas stream.<sup>17</sup> A thin (1000-Å) CVD SiO<sub>2</sub> top layer over the phosphosilicate main layer of 0.6- to 1.5- $\mu$ m thickness is desirable for improved photoresist adherence and consequently improved pattern etching definition, unless organo-silane adhesion-promoting agents are used. The composition of PSG layers used in the semiconductor industry is generally in the range of 2 to 5 wt % P (or 2 to 5 mol % P<sub>2</sub>O<sub>5</sub>).

# 2.5 Survey of Stress Measurement Methods

A variety of techniques for measuring stress in thin films are described in the literature.<sup>1,35,36</sup> X-ray and electron-diffraction analyses have been used to measure changes in lattice spacing and hence permit calculation of stress in films. However, more commonly, stress is calculated by optically measuring the deformation of a substrate, usually in the form of a beam, or a circular disc. In the beam-bending method, stress is calculated by determining the radius of curvature of the beam. Several methods for measuring the radius of curvature of a cantilevered beam have been reported.<sup>35</sup>

For a circular disc, the stress is calculated by measuring the displacement of the center of the circular disc in relationship to its edges. This can be accomplished by several methods: counting interference fringes between the disc and an optical flat, laser interferometry, holography, changes in location of the focal point, profiling the substrate with a light section microscope, or profiling the substrate by scanning with an optical microscope and measuring the change in focus from center to edge.<sup>35,66</sup>

# 2.6 Published Information on Stress in CVD Films

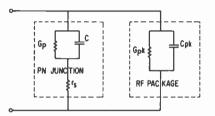

The literature contains some information on stress in CVD  $SiO_2$  and PSG films.<sup>1,9,26,37-42,66</sup> Comparisons are sometimes difficult to make

because of the substantial differences in deposition systems and conditions. Generally, published data are based on room-temperature measurements. SiO<sub>2</sub> films have been reported to be in tension as deposited.<sup>37</sup> Because silicon has a higher coefficient of thermal expansion than silicon dioxide, the residual stress in low-temperature CVD SiO<sub>2</sub> films on silicon at room temperature is somewhat lower than the intrinsic stress of films as deposited, but the films are still in considerable tension.<sup>37,42</sup>

PSG films are in lower stress (at room temperature) than SiO<sub>2</sub> films deposited at the same conditions.<sup>26,37</sup> In general, however, residual stress at room temperature remains tensile.<sup>26,41</sup>

Some information is available on the effect of deposition rate<sup>38,40</sup> and silane/oxygen ratio<sup>38</sup> on CVD SiO<sub>2</sub> stress, and of phosphorus concentration on stress in CVD PSG.<sup>26,40</sup> Stress reduction in CVD films exposed to room air has been reported.<sup>40,66</sup>

Deposited SiO<sub>2</sub> or PSG films, when heated above the deposition temperature, are put in additional tension, particularly in regions over the edges of delineated aluminum films. Accordingly, there is some correlation between the intrinsic tensile stress in deposited films and the temperature increment above deposition temperature that can be attained before cracks begin to form.<sup>26,37</sup> In general, the lower the intrinsic stress in films, the thicker the CVD layer can be before severe cracking begins to occur.<sup>18,26</sup>

The relationship of device reliability and defects in deposited glass layers caused by intrinsic tensile stress and other properties of the glass/metallization system has been examined in recent papers.<sup>1,9,26,43</sup>

#### 3. Experimental

#### 3.1 Gases, Equipment, and Methods Used in CVD Studies

In most of the experiments reported here, semiconductor-grade 3.3 vol % SiH<sub>4</sub> and electronic-grade 1.0 vol % PH<sub>3</sub>, both in ultrahigh-purity N<sub>2</sub>, were used. Several premixed hydride compositions in nitrogen were also used in which the ratios of SiH<sub>4</sub>:PH<sub>3</sub> were 6:1, 12:1, 23:1, and 60:1. The oxidant was O<sub>2</sub> of 99.9% purity, and the diluent was N<sub>2</sub> of 99.998% purity, both filtered through submicron filters.

Unless otherwise noted, we used a single-rotation vertical CVD reactor with a glass deposition chamber, described in a previous paper.<sup>3</sup> The hydrides with N<sub>2</sub> were introduced through the center inlet at the top of the chamber after having passed through a terminal submicron large-area filter. The O<sub>2</sub> was added to this gas stream before it entered the deposition chamber. Surface temperatures were measured with bimetallic- and thermocouple-type surface thermometers. Other details on deposition technology were similar to those reported in previous papers.<sup>3,17,19</sup>

NOU I ILIVIO

A variety of substrate materials were used for film deposition, but most of the work reported in this section was carried out with polished and chemically cleaned (100)-oriented single-crystal silicon slices of 5-cm diameter and 0.3-mm thickness.

Film thicknesses were measured by interferometric and profilometric techniques. The PSG composition was routinely analyzed by etch-rate measurements after densification of the films,<sup>7</sup> and by x-ray fluorescence methods; both techniques were calibrated by wet chemical analysis.

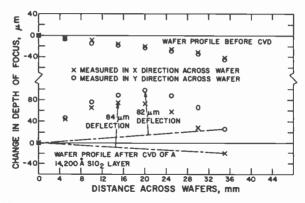

# 3.2 Methods Used for Stress Measurements

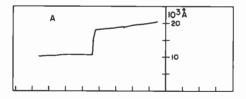

For the work described in this paper, the stress was determined by depositing films onto circular silicon wafers. Measurements of disc deflection were done at room temperature by three methods: (1) use of an optical flat and calculation of deflection by counting interference fringes;<sup>44</sup> (2) determination of the focal point by reflecting a collimated light off the surface of the wafer;<sup>38</sup> and (3) focusing an optical microscope on one wafer edge and moving the sample transversely from one edge to the other through the center of the wafer to measure the change in focus at various points. In this last method, measurements were made in both x- and y-directions at 5-mm intervals. The micrometer on the focusing dial was zeroed at the edge of the wafer. Upward and downward movement of the microscope stage was recorded as positive and negative, respectively. From this information, a plot of the wafer profile was constructed, from which deflection was determined.

Initially, all three methods were used to measure flatness of the substrate before CVD of the films. However, only method (3) was used in the latter part of the investigation, since it gave the best results. Corrections in the final graphical profile were made if deviations from flatness occurred in the starting substrate. Typical plots of change of focus versus distance across wafers are shown in the next Section.

Stress in the CVD films was calculated from the experimental data and the equation derived by Glang et al,<sup>36</sup>

$$\sigma = \left(\frac{\delta}{r^2}\right) \left(\frac{E}{3(1-\nu)}\right) \left(\frac{t_s^2}{t_f}\right),\tag{4}$$

where

$\sigma = \text{stress (dynes/cm}^2),$

$\delta$  = deflection of disc (cm),

$\nu$  = Poisson's ratio for substrate,

E = Young's modulus of substrate,

$t_f = \text{film thickness (cm)},$

$t'_s$  = substrate thickness (cm), and

r = radius of disc (cm).

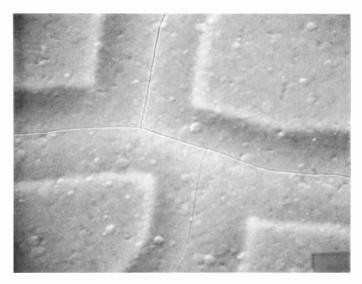

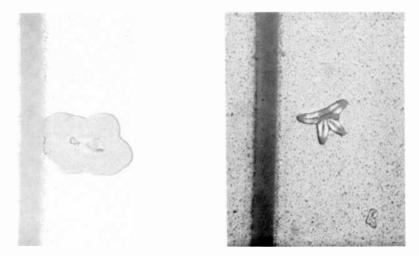

We also employed a convenient test based on step-wise heating of overcoat-passivated aluminum-metallized IC device wafers to relatively high temperatures (500° to 550°C) for typically 20 minutes per heating cycle to bring out latent stresses or weaknesses in the glass. These will increase in number with increasing temperature and give a realistic picture, suitable for statistical evaluation, of the potential stress levels and the specific location and distribution of excessive stress regions. This approach is akin to step-stress accelerated lifetesting and constitutes a useful, practical test method, particularly in conjunction with aluminum marker-etching<sup>45</sup> to enhance the detection sensitivity of localized structural defects. especially microcracks. in the glass overcoating. The largest areas of undelineated aluminum within a circuit, such as those over large capacitors in linear bipolar IC's, are particularly sensitive to the onset of crack formation as a function of heat-treatment temperature. These areas are also most suitable for estimating the crack density, or for counting the number of cracks for quantitative statistical computations. This method of stress testing is by no means a substitute for the direct numerical measurement of film stress by the methods described above. It should be used in conjunction with them because it gives directly observable and realistic information not obtainable otherwise. The method is particularly useful for relative comparison of residual net stress in overcoat layer compositions and deposition conditions used for identical substrate IC wafers. Relatively small stress differences of overcoatings can be pictorially documented and compared by counting or estimating the density of microcracks for identical sample areas. Apart from overcoating parameters, the test is sample dependent; it is quite sensitive to the exact conditions of the substrate. The incidence of microcracks is a function of the thickness, area, and pattern geometry of the metallization, the taper angle and edge of the delineated metal lines, the prior annealing and alloying treatments, and the topography of the underlying oxide steps and via holes.

The use of unpatterned, planar aluminum films on oxidized planar silicon wafers for the test described above can provide additional valuable information on the stress behavior of CVD films. Similar testing of the same films on polished silicon wafers as substrate is a further worthwhile variation of this test that we have used successfully.

# 4. Results and Discussion of CVD Studies

All of the critical factors in CVD of  $SiO_2$  and PSG films listed in Section 2.2 have been investigated, and will be discussed in the order listed.

# 4.1 Effects of Temperature and Oxygen-to-Hydride Ratio

The effects of substrate temperature of deposition and O<sub>2</sub>:hydride ratio are closely interrelated and are therefore best considered in the same context for both  $SiO_2$  and PSG films. The effects on the deposition rate of  $SiO_2$  and PSG are similar, and the composition of PSG is strongly dependent on both of these parameters.

We have previously shown<sup>10</sup> that  $SiH_4$  diluted with N<sub>2</sub> begins to form SiO<sub>2</sub> films at a temperature of about 240°C if the O<sub>2</sub>:SiH<sub>4</sub> mole ratio is in the range of 3:1. The rate of film growth at constant SiH<sub>4</sub> input increases rapidly as the substrate temperature is increased to 310°C. Further temperature increase to 450°C results in a very gradual increase in deposition rate. To attain a linear increase in the maximum deposition rate with temperature, the O<sub>2</sub>:SiH<sub>4</sub> ratio must be increased as the temperature is increased. For example, at 475°C, an  $O_2$ :SiH<sub>4</sub> ratio of at least 14:1 is required to achieve this. Larger ratios of up to 33:1 have no effect, but ratios beyond this limit inhibit the reaction, leading to decreased rates of film growth. Thus, a plateau region exists at this temperature that is insensitive to the O<sub>2</sub>:SiH<sub>4</sub> ratio. Temperatures lower than 475°C require progressively smaller  $O_2$ :SiH<sub>4</sub> ratios to attain the plateau of maximum SiO<sub>2</sub> deposition rate. At the same time the extent of the plateau region narrows as the temperature is decreased. These observations have since been confirmed by several other workers<sup>13,14,22,31,32,46,68,69</sup> and were found to hold qualitatively, even though different reactor geometries were used. The unusual reduction in  $SiO_2$  deposition rate at high  $O_2:SiH_4$ ratios has been explained by retardation theory where O2 acts as the retardant by being adsorbed on the substrate surface.<sup>14</sup>

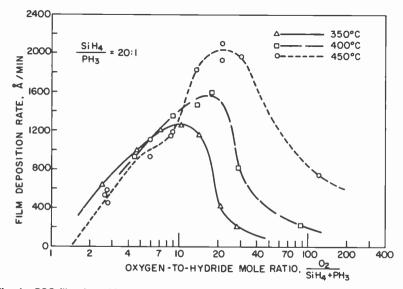

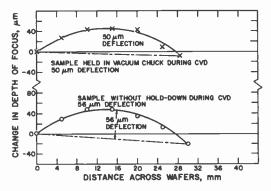

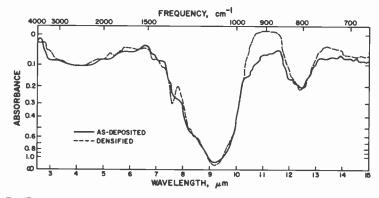

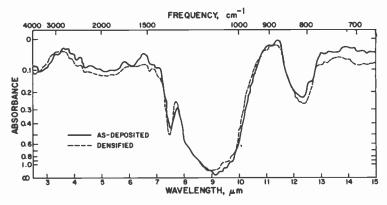

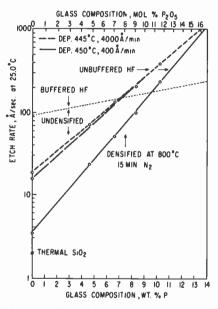

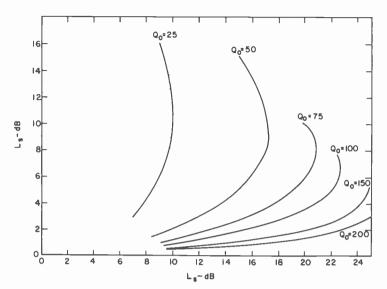

The corresponding observations for PSG formation by co-oxidation of  $SiH_4 + PH_3$  with  $O_2$  are essentially analogous to those discussed for  $SiO_2$ .<sup>1,2,14,16,29</sup> Fig. 1 shows plots of typical data we obtained studying the effect of  $O_2$ :hydride mole ratio on the deposition rate of PSG at 350°, 400°, and 450°C. The  $SiH_4$ :PH<sub>3</sub> mole ratio was fixed at an intermediate value of 20:1, and the total gas flow rate was held constant at 11 liters per minute. The rate of PSG film deposition clearly depends on both the O<sub>2</sub>:hydride ratio and the substrate temperature during deposition. The maximum deposition rate obtainable at a given temperature is a function of the O<sub>2</sub>:hydride ratio. As the temperature is increased, the maximum deposition rate increases, but requires progressively larger O<sub>2</sub>:hydride ratios to be attained. The semi-log plot in Fig. 1 indicates, furthermore, that the ratio range of the maximum region widens with increasing temperature.

Fig. 1—PSG film deposition rate versus oxygen/hydride mole ratio for three deposition temperatures. Total gas flow rate was 11 liters/min.

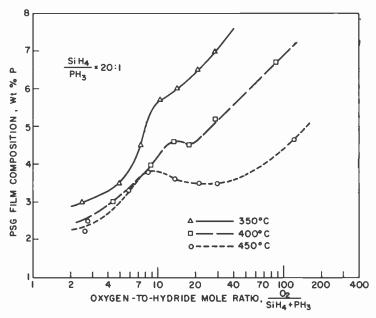

Fig. 2 depicts the effects of O<sub>2</sub>:hydride ratio and temperature on the composition of PSG films for the same samples and CVD conditions from which the deposition-rate results in Fig. 1 were obtained. The phosphorus concentrations in the glass films generally increase with both increasing O<sub>2</sub>:hydride ratio and with decreasing temperature. The phosphorus content in the PSG films deposited at 450°C is less critically dependent on the ratio than in the films deposited at lower temperature, making the higher temperature considerably more desirable from a practical point of view, especially since the level-concentration range occurs within the O<sub>2</sub>:hydride ratio range of

GLASS FILINIS

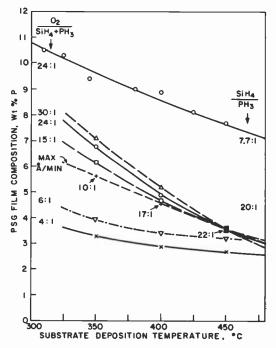

The effects of substrate deposition temperature for fixed  $O_2$ :hydride ratios are illustrated more directly in Figs. 3 and 4; they were both derived from Figs. 1 and 2.

Fig. 2—PSG film composition versus oxygen/hydride mole ratio for three deposition temperatures. Total gas flow rate was 11 liters/min.

Fig. 3 shows the PSG film deposition rate at  $350^{\circ}$ ,  $400^{\circ}$ , and  $450^{\circ}$ C as a function of selected O<sub>2</sub>:hydride ratios (4:1, 6:1, 10:1, 24:1, and 30:1) and also for the ratios corresponding to the maximum deposition rate for each of the three temperatures. The curves exhibit negative slopes for the low ratios and change to positive slopes for the higher ratios. The curves indicate that the deposition rates at all three temperatures are similar for any one ratio in the lower range of 4:1 to 10:1 (not drawn for clarity) but differ increasingly as the ratio is increased. Again, the least dependence is noted at  $450^{\circ}$ C, where deposition rates at all high ratios (15:1, 24:1, and 30:1) are close to that at 22:1, corresponding to the maximum deposition rate.

Fig. 4 shows the PSG phosphorus concentration as a function of the same  $O_2$ :hydride ratio values selected for Fig. 3, again for all three

temperatures. Also included in this figure is a plot showing the temperature effect for a lower SiH<sub>4</sub>:PH<sub>3</sub> mole ratio (7.7:1) over an extended temperature interval (310° to 450°C); the O<sub>2</sub>:hydride ratio was held constant at 24:1. The difference between the slope of this curve and the 24:1 curve for the higher SiH<sub>4</sub>:PH<sub>3</sub> ratio (20:1) indicates some dependence of the temperature effect on the hydride ratio. The family of curves for the 20:1 SiH<sub>4</sub>:PH<sub>3</sub> ratio series shows

Fig. 3—PSG film deposition rate versus deposition temperature for selected oxygen/ hydride mole ratios at a SiH<sub>4</sub>/PH<sub>3</sub> mole ratio of 20:1. The top curve, marked Max Å/min, corresponds to ratios yielding maximum deposition rates. All values were taken from Fig. 1.

that the effect of temperature on PSG composition becomes progressively less as the O<sub>2</sub>:hydride ratio is decreased, similar to the effect on deposition rate. Again, the curves for the higher ratios converge at  $450^{\circ}$ C, demonstrating minimum dependence. The curve corresponding to the O<sub>2</sub>:hydride mole ratios of maximum deposition rate is a straight line. An immediate practical consequence of the temperature effect is the need for isothermal surface conditions of the substrate wafer. Good thermal contact of the wafer with the heated substrate plate is essential to effect good heat transfer and to avoid thermal variations in the wafer surface. Poor contact may arise if the wafers are warped (possibly due to improper annealing after diffusion), if wafers overlap on positioning, or if excessive quantities of CVD glass are allowed to accumulate on the substrate plate causing a decrease in the surface temperature.

Fig. 4—PSG film composition versus deposition temperature for selected oxygen/hydride mole ratios. The family of lower curves was plotted from values taken from Fig. 2. The curve marked Max. Å/min corresponds to ratios yielding maximum deposition rates. The top curve shows temperature effect on composition for a silane/phosphine ratio of 7.7:1 at constant oxygen/hydride ratio of 24:1.

The results we have presented here agree very well with data reported in the literature cited in this section, even though different CVD reactor systems and conditions were used.

#### 4.2 Effects of Hydride Flow Rate

The quantity of SiH<sub>4</sub> or of SiH<sub>4</sub> + PH<sub>3</sub> introduced into the reaction chamber per unit time at a constant substrate temperature and O<sub>2</sub>: hydride ratio determines the rate of film deposition, which follows a linear function up to some saturation level limited by the size and geometry of the reaction chamber. In other words, the film thickness increases proportionally with the hydride input and the time period of deposition, independent of the film thickness up to many micrometers, at which point decreased thermal conductance may become noticeable. Hydride input quantities for the reactor system we used to obtain the data in Figs. 1 and 2, for example, were 670 cm<sup>3</sup>/min of 3.3% SiH<sub>4</sub> and 110 cm<sup>3</sup>/min of 1.0% PH<sub>3</sub>. The PSG film composition is affected only slightly by very large variations in the film-deposition rate, so that this effect can be disregarded in practical applications.

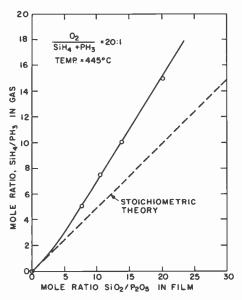

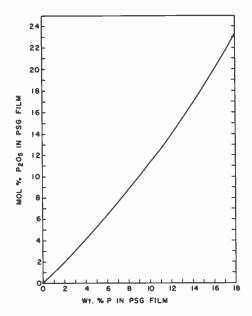

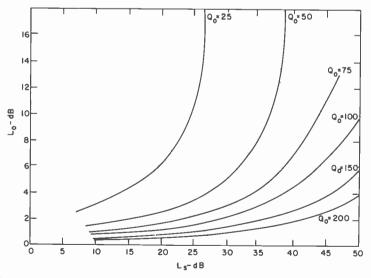

## 4.3 Effects of Silane-to-Phosphine Ratio

The SiH<sub>4</sub>:PH<sub>3</sub> ratio under otherwise constant CVD conditions determines the composition of the resulting PSG. The relationship of the mole ratio of SiH<sub>4</sub>:PH<sub>3</sub> in the gas and of SiO<sub>2</sub>:P<sub>2</sub>O<sub>5</sub> in the resulting glass is nearly linear,<sup>1,2,26,29</sup> as shown in Fig. 5, for a deposition temperature of 445°C. A plot of the same data in terms of mol % PH<sub>3</sub> in SiH<sub>4</sub> + PH<sub>3</sub> versus mol % P<sub>2</sub>O<sub>5</sub> in SiO<sub>2</sub> - P<sub>2</sub>O<sub>5</sub> in the resulting PSG is presented in Fig. 6. It shows a linear relationship up to about 10 mol % P<sub>2</sub>O<sub>5</sub>, followed by a less than linear increase in P<sub>2</sub>O<sub>5</sub> beyond this point. Recent data reported in the literature<sup>29</sup> agree within approximately 10% with our curve shown in Fig. 6. Lower temperatures of deposition at constant SiH<sub>4</sub>:PH<sub>3</sub> ratio increase the mol % P<sub>2</sub>O<sub>5</sub> in the PSG if the O<sub>2</sub>:hydride ratio is adjusted for the plateau region of maximum deposition rate for each temperature, in agreement with the data shown in Fig. 4 and with literature data.<sup>29</sup>

The relationship depicted in Figs. 5 and 6 indicates that the PSG resulting from the oxidation under the conditions stated contains more phosphorus than would be expected from stoichiometry, since two moles of PH<sub>3</sub> form one mole of P<sub>2</sub>O<sub>5</sub>. Fig. 6 indicates that up to about 10 mol % P<sub>2</sub>O<sub>5</sub> the conversion efficiency of PH<sub>3</sub> to P<sub>2</sub>O<sub>5</sub> at 445°C is 1.4 times greater than that of SiH<sub>4</sub> to SiO<sub>2</sub>. At lower temperatures it is still greater. Stated differently, the conversion efficiency of SiH<sub>4</sub> to SiO<sub>2</sub> during co-oxidation of SiH<sub>4</sub> + PH<sub>3</sub> is lower than that of PH<sub>3</sub> alone. Apart from kinetic<sup>14</sup> and thermodynamic<sup>27</sup> differences in the oxidation of the two hydrides, the previously mentioned retardation of SiH<sub>4</sub> oxidation by oxygen is almost certainly responsible for

at least part of the observed effect. Hence, higher than expected phosphorus concentrations in the PSG result. In addition, PH<sub>3</sub> appears to have a retarding effect on SiH<sub>4</sub> oxidation, since our work as well as literature data<sup>30,32</sup> indicates that the film deposition rate is depressed by small additions of PH<sub>3</sub>. We have obtained similar results of retardation with diborane in the co-oxidation of SiH<sub>4</sub> + B<sub>2</sub>H<sub>6</sub> to deposit borosilicates.

Fig. 5—Mole ratio SiO<sub>2</sub>/P<sub>2</sub>O<sub>5</sub> in PSG film versus mole ratio SiH<sub>4</sub>/PH<sub>3</sub> of the hydride gas mixture at a substrate deposition temperature of 445°C and an oxygen/hydride ratio of 20:1. The dashed line indicates relationship for stoichiometric reaction. Total gas flow rate was 8 liters/min. Film deposition rate was 4000 Å/min. Film analysis based on wet chemical method.

Incorrect  $SiH_4$ :PH<sub>3</sub> ratios can lead to several problems in the glass. A PSG with low phosphorus content may result in inadequate gettering of externally introduced contaminants such as sodium ions; it may also cause cracking of the glass because of excessive stress. Too high a concentration of phosphorus, on the other hand, may result in current leakage across the surface or in a hygroscopic glass, which may cause metal corrosion problems.

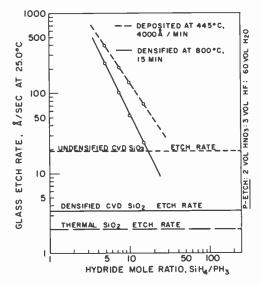

In adjusting the hydride ratio for otherwise fixed conditions, it is convenient to use a plot of etch rate values of the films as a direct function of the  $SiH_4$ :PH<sub>3</sub> ratio.<sup>1,7</sup>

#### 4.4 Effects of Nitrogen Flow Rate

The function of the diluent nitrogen is threefold: (1) to dilute the reactive gases to a sufficiently low concentration to prevent spontaneous combustion when combined with the oxygen and, in some systems, to afford premixing; (2) to force the reactive gas mixture over the heated substrate surface; and (3) to create gas-flow conditions in the reaction chamber that result in good film uniformity across a maximum area of the substrate plate. Too low a nitrogen flow rate

Fig. 6—Composition of PSG films versus composition of hydride gas mixture. Samples and CVD conditions are the same as those defined in Fig. 5. Also shown are PSG composition in terms of wt % P and hydride composition in terms of mole ratio.

can severely depress the deposition rate of both  $SiO_2$  and PSG films and lead to gross nonuniformities in film thickness across the wafers. Excessive nitrogen flow decreases the residence time for the gases at the substrate surface and causes the plate temperature to drop due to cooling, thus leading to nonuniform deposits that, in the case of PSG, contain more phosphorus than obtained under normal conditions (because of the decreased temperature as indicated in Figs. 3 and 4). A suitable flow rate for our reaction chamber (described in Refs. [1] and [3]) is in the range of 7 to 11 liters of total N<sub>2</sub> (including hydride diluent N<sub>2</sub>) per minute, the correct quantity being determined by the attainment of good film-thickness uniformity under the specific CVD conditions used.

Silane, despite its reactivity at high concentrations with oxygen, can be conveniently premixed for production applications with oxygen and nitrogen at sufficiently high dilutions in both oxygen and nitrogen (i.e., 0.5% SiH<sub>4</sub>, 2.5% O<sub>2</sub>, 97% N<sub>2</sub> by volume), forming a mixture that is inert until heated above  $200^{\circ}C.^{13,27}$

# 4.5 Effects of Reactor Geometry

The shape and dimensions of the reaction chamber and the gas inlet/ outlet configuration are very critical with respect to thickness uniformity of the film deposits because they affect the flow dynamics of the gas stream. We have constructed and tested many reaction chambers and found that small differences can cause gross effects, particularly in single-rotation reactors, where a lesser degree of averaging is attainable than in planetary units. The type of bell jar described in Refs. [1] and [3] has given particularly good results despite its deceptive simplicity.

#### 4.6 Effects of Reaction Chamber Wall Temperature

The reactor wall, if hot, acts as a substrate for both glassy and powdery gas-phase reaction products. Cooling the reactor parts that are not intended for heating the substrate results in a decrease of these undesirable coatings and also suppresses homogeneous gas phase nucleation, which is the cause of the powdery deposits, while at the same time promoting desirable heterogeneous reactions leading to glassy films. As a consequence, cleaner film deposits form and the deposition rate tends to increase for the same reactant input. This means, in effect, that the yield of glassy product can increase considerably, since the input of expensive reactants can be reduced to attain the same deposition rate obtained with a hot-wall reactor. The composition, in the case of PSG films, can be slightly affected by this change, requiring some readjustment of the SiH<sub>4</sub>:PH<sub>3</sub> ratio.

#### 4.7 Effects of Impurities in CVD System and Gases

The surface-catalyzed free-radical reaction mechanism underlying CVD of oxide and glass films is quite sensitive to particulate contaminants in the gas phase. Particles in the gas stream (mainly colloidal oxides formed by premature reaction) can cause microbubbles, pinholes, and other localized structural defects in the glass layer. A number of authors have pointed out the relationship between pinholes in dielectric films and particulate impurities in CVD systems and gases.<sup>1,2,3,9,45,46,69</sup> It is therefore imperative to suppress the formation of particulate impurities effectively and to remove as much as possible of the impurities that still form by use of large-area high-capacity submicron filters in the gas lines positioned as close to the site of film deposition as practicable. Frequent blasting out of the CVD system and the gas lines with pressurized nitrogen to dislodge and remove particles is very convenient and effective. In addition, periodic cleaning of the CVD reactor and the gas tubing system should be carried out.

Another type of impurity in CVD films arises from chemical contaminants in the gases used. Silicon dioxide films deposited from semiconductor-grade silane and oxygen are known to contain some sodium that may deleteriously affect MOS devices.<sup>1,26</sup> In the present work, atomic absorption analysis was used to assess the concentration of alkali impurities and copper in typical SiO<sub>2</sub> and PSG films of 1 to 2  $\mu$ m thickness that were prepared at 300° and 450°C in the rotary CVD reactor at deposition rates ranging from 300 to 2000 Å/min. The impurity contents in parts per million by weight ranged as follows: Na 2–6, K 1–3, and Cu 0.6–1.4. Fortunately, PSG passivation layers of proper composition are capable of gettering alkali contaminants to the extent that device instability problems due to this cause should not arise with typical device structures.

## 4.8 Effects of Gas Additives

Additives to the CVD reaction were investigated for the purpose of either lowering intrinsic stress in the glass films or for suppressing homogeneous gas phase nucleation.

Stress in SiO<sub>2</sub> and PSG was successfully lowered by adding water vapor to the gas stream entering the deposition chamber. Quantitative details of these experiments are discussed in Sections 5.7 and 5.8. We found that the deposition rate of SiO<sub>2</sub> films is not markedly affected by the addition of water vapor, in agreement with previously reported observations.<sup>1,31,68</sup> We also found that neither the deposition rate nor the composition and uniformity of PSG films is noticeably influenced by introducing water vapor during CVD. Additions of azeotropic hydrochloric acid (20% HCl) vapor instead of water vapor for the purpose of possible impurity gettering also did not affect deposition rate, uniformity, composition of PSG films, or the aluminum metallization of IC wafers being glass coated.

ILAUG I ILIVIO

As already noted, most of the particular contaminants present in CVD systems are caused by homogeneous gas phase nucleation (manifested as white fog and powdery wall deposits) that can be minimized to some extent by the techniques noted. Complete but selective suppression of the homogeneous reaction by addition of a specific inhibiting agent (such as a free-radical scavenger) to the gas mixture during CVD would be highly desirable to improve the quality of the glass layers. Ethylene has been reported to act as a selective suppressant of homogeneous gas phase nucleation in the oxidation of silane to SiO<sub>2</sub>;<sup>31</sup> however, selective inhibition is effective only at very low O<sub>2</sub>:SiH<sub>4</sub> ratios<sup>47</sup> (such as 1.5:1) where formation of colloidal oxide is extreme.<sup>10</sup> Because of the decreased rates of film growth, these conditions are not normally usable for film deposition. Experiments conducted in our laboratory using a rotary reactor, O<sub>2</sub>:SiH<sub>4</sub> ratios of 6:1 and 15:1, deposition temperatures of 350° and 450°C, total gas flow rate of 11 liters/min, and ethylene additions yielding C<sub>2</sub>H<sub>4</sub>:SiH<sub>4</sub> ratios ranging from 0.3:1 to 100:1 showed the following. Ratios of C<sub>2</sub>H<sub>4</sub>: SiH<sub>4</sub> of less than 1:1 did not markedly affect the deposition rates of either the vitreous  $SiO_2$  (1100 Å/min) on the silicon substrates or that of the powder on the reactor wall. Higher ratios caused a rapid, but nonselective depression of the deposition rates for both products. For example, a ratio of 5:1 led to a 11-fold decrease in the film deposition rate. Ratios of 14:1 to 100:1 completely prevented any reaction.

Results obtained with PSG at a substrate temperature of  $450^{\circ}$ C and at O<sub>2</sub>:hydride ratios of 8:1 and 20:1 showed that the film deposition rate is also suppressed nonselectively, but more severely than in the case of SiO<sub>2</sub>. A C<sub>2</sub>H<sub>4</sub>:hydride ratio of only 5:1 completely inhibited reaction.

Similar results of nonselective inhibition of  $SiO_2$  and PSG formation were also obtained with styrene and several other selected compounds.

# 4.9 Effects of Substrate Surface

The composition of the substrate material and the physical and chemical nature of adsorbed contaminants on the substrate surface affect the growth rate and the quality of CVD oxide and glass films

| Table 1—Effects of Substrate Impurities on the Microscopic Appearance of CVD SiO, and PSG Films (Defects Observed by White Light, Monochromatic Light, or Nomarski Differential Interference Contrast)             | s on the Microscopic<br>c Light, or Nomarski D                                                                                                                  | Appearance of CVD SiO <sub>2</sub> al<br>ifferential Interference Cont                      | nd PSG Films (Defec<br>rast)                 | ts Observed         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|----------------------------------------------|---------------------|

|                                                                                                                                                                                                                    | Polished Si                                                                                                                                                     | Polished Si Substrate Wafer                                                                 | Evaporated Al Film on SiO <sub>2</sub>       | m on SiO2           |

| Contaminant<br>Added to Substrate                                                                                                                                                                                  | SiO <sub>2</sub>                                                                                                                                                | PSG                                                                                         | SiO <sub>2</sub>                             | PSG                 |

| <i>Control</i><br>No contaminants added                                                                                                                                                                            | (H)                                                                                                                                                             | No defects                                                                                  | (H)                                          | (H)                 |

| Particulates<br>Si crystal dust<br>Al,O, powder, 0.05 µm particles<br>PSG dust, CVD wall deposit                                                                                                                   | H<br>H (Fig. 7E)<br>H (Fig. 7A)                                                                                                                                 | H<br>H<br>B,E,H                                                                             | Е,Н,Р<br>Е,Н,Р<br>Е,Н                        | E,H<br>E,H,K<br>E,H |

| Organics<br>Apiezon<br>Photoresist<br>Trichloroethylene                                                                                                                                                            | C,H,K,T<br>D,S<br>C,H,S,T                                                                                                                                       | B,S<br>D,H,K,S                                                                              | $\substack{B,D \ (Fig. 7B) \\ H, K, P \\ H}$ | B<br>C<br>E,H       |

| <i>Chemicals</i><br>HF, poorly H <sub>1</sub> O rinsed<br>HF + HNO <sub>3</sub> , poorly H <sub>2</sub> O rinsed<br>H <sub>3</sub> PO <sub>4</sub> , poorly H <sub>2</sub> O rinsed                                | H,K,S,T<br>H,S<br>C,S                                                                                                                                           | P<br>H<br>D,K,P,S (Fig. 7F)                                                                 | С,Н<br>Н<br>Н, <b>Р</b>                      | E,P,K               |

| <i>Mixed</i><br>Tap water<br>Fingerprints                                                                                                                                                                          | D,S,Y (Fig. 7C)<br>Y (Fig. 7D)                                                                                                                                  | S,Y<br>Y                                                                                    | d'H                                          | Ч,Р<br>Ү            |

| Code of Defects: B - Bubbles or blisters<br>C - Cloudy, hazy<br>D - Dots or micropinholes<br>E - Elongated interference fringe<br>H - Halos of interference fringes<br>( ) indicates small number of defects only. | Bubbles or blisters<br>Cloudy, hazy<br>Dots or micropinholes<br>Elongated interference fringe patterns<br>Halos of interference fringes<br>ber of defects only. | K - Streaks<br>P - Pits or depressions<br>S - Stains<br>T - Thin spot areas<br>Y - Crystals |                                              |                     |

22 RCA Review • Vol. 37 • March 1976

synthesized from the hydrides.<sup>1-3,10,15,17,19,22,67,70</sup> This is in part due to the free-radical reaction mechanism underlying this type of hydride oxidization, which is sensitive to chemical trace impurities on the substrate surface that can act as growth catalysts or inhibitors.

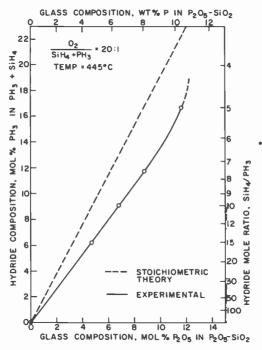

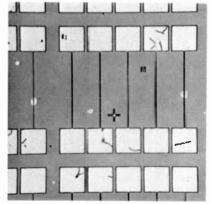

Effects of usually nondescript substrate impurities on CVD SiO<sub>2</sub> films have been reported by several investigators.<sup>1,10,22,43,45,46,48</sup> In general, defects such as pinholes, pits, thin spots, blisters, microbubbles, cloudiness, and local variations in film thickness can result. To examine under controlled conditions the effects of specific substrate impurities on the microscopic appearance of CVD SiO<sub>2</sub> and PSG films, selected representative physical and chemical materials were placed randomly on certain areas of clean substrates, which were then overcoated under typical CVD conditions at 450°C. The substrates consisted of polished and chemically cleaned (100)-oriented silicon wafers and of 5000 Å-thick unpatterned aluminum films vacuum evaporated over thermally oxidized polished silicon wafers. Samples without additives served as uncontaminated controls. Particulate impurities, sprinkled over the substrates, were silicon crystal dust from scribing with a diamond, aluminum oxide powder ( $\gamma$ -Al<sub>2</sub>O<sub>3</sub>, cubic) of 0.05-µm-diameter particles, and PSG power from CVD reactor wall deposit. Organic contaminants, applied to the substrate from solution and allowed to dry, included Apiezon Hard Wax W (J. G. Biddle Co.), KTFR photoresist (Eastman Kodak Co.), and electronic grade trichloroethylene. Reactive chemical agents were oxide etch (49% HF solution), silicon etch (49% HF-70% HNO<sub>3</sub> 1:1 mixture), and aluminum etch (85% H<sub>3</sub>PO<sub>4</sub>-H<sub>2</sub>O-70% HNO<sub>3</sub> 40:10:4 mixture). In this series the substrates were immersed in the reagents and rinsed briefly with a small amount of distilled water. Additional sample impurities were tap water allowed to dry on the substrates and fingerprints leaving NaCl and greasy impurities. The results of microscopic examination of the samples after CVD are summarized in Table 1. Photomicrographs of several typical defects observed are presented in Fig. 7.

# 4.10 Effects of Geometry and Topography of Substrate

The relief geometry of the structure and the topography of the substrate surface determine to a significant extent the quality of the CVD glass overcoat, apparently due to localized disturbances in the gas flow pattern.

The layer integrity and conformity over steep steps and sharp edges are particularly severely affected by these factors, and can give rise to serious reliability problems, as is evident by analysis of glass-

- Fig. 7—Photomicrographs showing typical effects of surface contaminants on the microscopic appearance of CVD overcoatings defined in Table 1. Magnifications are for photo sizes shown here:

- A-SiO<sub>2</sub> over PSG particles on Si (monochromatic light, X93)

- B-SiO<sub>2</sub> over wax residue on AI (white light, X180)

- C-SiO<sub>2</sub> over tap water residue on Si (Nomarski differential interference contrast,  $\times$  230)

- D-SiO<sub>2</sub> over NaCl crystals from fingerprints on Si (white light, X180)

- E-SiO<sub>2</sub> over  $\gamma$ -Al<sub>2</sub>O<sub>3</sub> particles on Si (monochromatic light, X93)

- F-PSG over H<sub>3</sub>PO<sub>4</sub> residue on Si (monochromatic light, X230)

passivation device failure modes.<sup>1,43,45,49,50</sup> We have previously shown<sup>49</sup> that the quality of step coverage can be controlled and improved to a limited extent by optimizing the CVD conditions (mainly by reducing the total gas flow rate), although tapering of the structure prior to overcoating should be done whenever possible because it is more effective.

New results indicate that the chemical composition of an overcoating material can have a marked influence on the step coverage. Layers of 0, 2, 3, and 4 wt % phosphorus PSG of 1.1 to 1.2-µm thickness were deposited on wafers of two types of aluminum-metallized IC's (planar linear bipolar and MOS IC's). Deposition was carried out at 450°C in a rotary reactor at a rate of 2000 Å/min. We found, by special etching techniques,<sup>6</sup> that 2 to 4 wt % phosphorus PSG affords a substantially better conformal edge coverage over aluminum patterns than does SiO<sub>2</sub> (0% P). The difference between 0 and 2 wt % phosphorus is remarkable, and is definitely due to the overcoat material since the conditions of CVD were kept exactly analogous, and the effect occurred on both types of IC's, even though the aluminum thickness and edge contour are not exactly the same.

Surface roughness of the substrate is another factor that determines the quality of CVD layer deposits. A typical case is that of evaporated aluminum films, especially after alloying treatments with silicon, which leads to the formation of hillocks, spikes, and grainyness that tend to give rise to increased pinhole formation in the overcoating.<sup>1,48</sup>

# 4.11 Effects of CVD Reactor Systems

A considerable variety of CVD reactor systems for preparing  $SiO_2$ and PSG passivating overcoatings is now available. We have categorized and described the design, operation, and capability of CVD equipment, which varies from relatively simple to sophisticated automated reactors.<sup>1–3</sup> We have conducted a limited number of experiments with several of these types of reactor systems, including several commercially available continuous processing units,\* to examine whether the experimental results presented in this section are applicable to other systems as well. We found that they not only agree in principle, but that they frequently relate on a semiquantitative basis, despite the remarkable differences in geometry and system operation.

<sup>\*</sup> Typical units and their manufacturers are as follows: Rotox-60, Unicorp. Incorporated, 625 North Pastoria Dr., Sunnyvale, CA 94086; AMS-2000 Continuous Silox Reactor, Applied Materials Technology, Inc., 2999 San Ysidro Way, Santa Clara, CA 95051; PWS Model 2000 Vapor Deposition System, Pacific Western Systems, Inc., 855 Maude Avenue, Mountain View, CA 94040.

Nevertheless, the performance of each reactor must be carefully examined and adjusted to attain conditions for producing films of specified properties.

# 5. Studies of Film Stress

## 5.1 Evaluation of Substrates Used for Stress Measurements

Initially, 65-µm-thick, flat, circular (111)-oriented silicon wafers were used as a substrate to measure the stress of deposited films. During the CVD process the wafers deformed because of the thermal gradients across them, as well as from the strain that was being introduced from the depositing layer. (The magnitude of the deformation of these thin silicon test wafers is, of course, much greater than that which occurs on the considerably thicker integrated-circuit wafers.) Deformation of the substrate during CVD can cause errors in the stress measurements; it is therefore important that the substrates remain relatively flat during film deposition. To maintain the flatness. a fixture was designed to hold the substrates down by vacuum. The fixture consisted of an aluminum block 57 mm in diameter and 18 mm in height, with a 6.3-mm stainless-steel tube leading to a cavity in the center of the block: 0.3-mm holes were drilled through the top of the block to the cavity, in a circular area 35 mm in diameter. A vacuum line was connected to the fixture, and wafers placed over the holes in the top surface were held firmly in place.

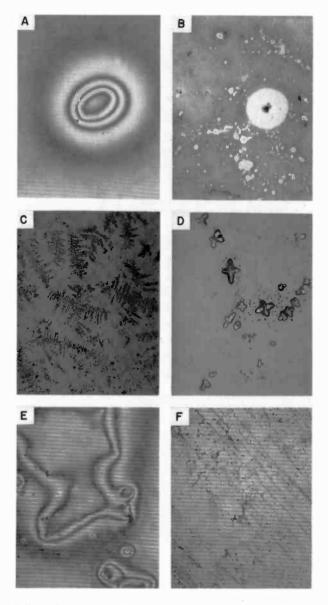

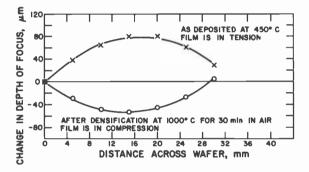

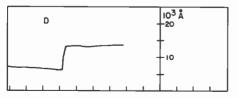

While the vacuum hold-down fixture worked satisfactorily, it could not be used with some types of CVD reactors. Furthermore, the  $65-\mu$ m wafers proved to be too fragile for easy handling in a large number of tests. Accordingly, tests were carried out to determine what wafer thickness could be used that would not be excessively fragile and still give good results. It was found that wafers about 140  $\mu$ m thick and 39 mm in diameter were sturdy enough so that excessive breakage did not occur. Because of the increased thickness, it became unnecessary to use the vacuum hold-down fixture. Stress measured on samples held fast during deposition was not appreciably different from that of wafers not held at all, and uniform CVD film thicknesses resulted. Profiles for two wafers, one with and one without hold-down, are shown in Fig. 8.

The term  $E/(1 - \nu)$  in the stress equation (Eq. [4]) was calculated for the silicon substrates used for film deposition. This was accomplished by thermally oxidizing the wafers in steam at 1100°C, removing the oxide from one side in aqueous HF, and measuring the deflection. Since the stress value of thermally grown SiO<sub>2</sub> has been published,<sup>51</sup> this value was substituted into the stress equation, and  $E/(1 - \nu)$  was calculated. The calculated value of  $1.9 \times 10^{12}$  dynes/cm<sup>2</sup> for (111)-oriented silicon is close to Glang's value of  $2.3 \times 10^{12}$  dynes/cm<sup>2</sup>.

However, for (100)-oriented silicon, the value of  $E/(1 - \nu)$  was found to be  $1.3 \times 10^{12}$  dynes/cm<sup>2</sup>. This difference between (111) and (100) silicon was also confirmed by stress experiments, which showed that wafers of equal thickness with equal CVD oxide thicknesses deflected by different amounts, with larger deflection occurring on (100)-oriented silicon wafers.

Fig. 8-Profiles of two silicon substrates following CVD of a 1-µm-thick layer of SiO<sub>2</sub>.

In the process of making stress measurements in CVD dielectric layers, some unexplained variations in measured stress were observed. Experiments revealed that some substrate wafers deflected more easily than others, thus indicating larger stress value than actually were present in the CVD layer. Variations in the depth of microcracks caused by lapping and polishing of the silicon substrate are probably the main cause for the difference between wafers. In an effort to eliminate these variations, an apparatus was set up to measure wafer deflection by placing the silicon substrates onto an O-ring support, and then applying a partial vacuum to the holder, thus causing the wafer to bow. A differential pressure of 14.7 Torr was used, since this deflected the substrates about the same amount as a CVD SiO<sub>2</sub> film of 1 µm thickness. Each wafer used for stress measurements was checked, and only wafers that showed equal amounts of deflection for both sides and equal amounts of deflection from wafer to wafer for a given pressure were used for stress measurements of deposited films.

Fig. 9—Wafer profiles before and after CVD of a 1.4- $\mu$ m-thick SiO<sub>2</sub> layer.

For all stress data presented in this report, (111)-oriented silicon substrate wafers were used, and Glang's value<sup>36</sup> for  $E/(1 - \nu)$  was used in the calculations. Typical plots of change of focus versus distance across a wafer before and after coating are shown in Fig. 9 to illustrate the measurement method.

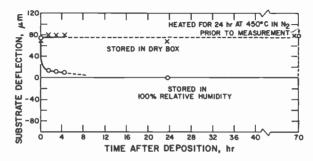

#### 5.2 Effect of Storage on Stress

Stress in CVD SiO<sub>2</sub> films decreases with time, the amount of decrease being dependent upon the storage ambient. Wafers having a CVD SiO<sub>2</sub> layer are essentially relieved of their stress in about four hours if stored in 100% relative humidity at room temperature, whereas films prepared under the same deposition conditions showed little change in stress when stored in a dry box for 70 hours (Fig. 10). Wafers with oxide layers whose stress had been relieved by storing in 100% rela-

28 RCA Review • Vol. 37 • March 1976

tive humidity went back into tensile stress when the sample was returned to the dry ambient. These results indicate that for undensified, encapsulated  $SiO_2$  layers, the stress will vary depending on ambient conditions.

# 5.3 Effect of Deposition Rate on Stress

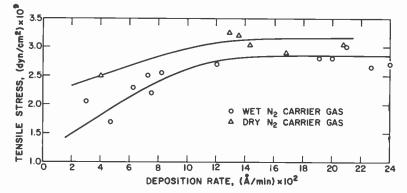

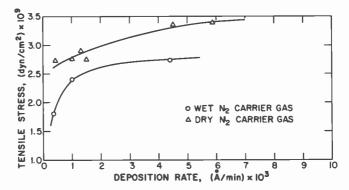

SiO<sub>2</sub> films deposited at 350°C at a deposition rate of 400 Å/min had a tensile stress of  $2.5 \times 10^9$  dynes/cm<sup>2</sup>. At a deposition rate of 1400 Å/min the stress increased to about  $3.1 \times 10^9$  dynes/cm<sup>2</sup>. Measurements of SiO<sub>2</sub> films deposited at 450°C and at a very high rate (5000 Å/min) showed a tensile stress of about  $3.4 \times 10^9$  dynes/cm<sup>2</sup>, as compared with  $2.7 \times 10^9$  dynes/cm<sup>2</sup> for films deposited at 1000 Å/min.

Stress as a function of film deposition rate for PSG layers deposited at 400°C and containing 3.6 wt % phosphorus was measured in the range of 1250 to 5000 Å/min with the O<sub>2</sub>:hydride ratio held constant at 11.4:1. Stress was  $2.3 \times 10^9$  to  $2.4 \times 10^9$  dynes/cm<sup>2</sup> for all samples prepared in this range.

# 5.4 Effect of Deposition Temperature on Stress

Stress as a function of deposition temperature was measured in the range of 340° to 450°C. The average stress for five samples of CVD SiO<sub>2</sub> films on silicon prepared at 340°C was  $3.1 \times 10^9$  dynes/cm<sup>2</sup>. Film average stress for five samples prepared at 400°C was also  $3.1 \times 10^9$  dynes/cm<sup>2</sup>. Samples prepared at 450°C averaged  $2.7 \times 10^9$  dynes/cm<sup>2</sup>. The etch rate tends to decrease with increasing deposition temperature. Experimental conditions and evaluation data for these and similar tests are presented in Table 2.

# 5.5 Stress as a Function of Oxygen-to-Hydride Ratio

Stress as a function of  $O_2$ :SiH<sub>4</sub> ratio was measured for SiO<sub>2</sub> films deposited at 450°C, and little difference was observed in the stress of the deposited film when the  $O_2$ :SiH<sub>4</sub> ratio was varied between 3:1 and 36:1, as shown in Table 3. Low  $O_2$ :SiH<sub>4</sub> ratios have been reported<sup>38</sup> to produce lower stress CVD SiO<sub>2</sub> films at 400°C.

We have found that the stress in CVD PSG overcoatings can be strongly influenced by the O<sub>2</sub>:hydride ratio. In these experiments the deposition temperature was lowered to typically 400°C with deposition rates of approximately 2500 Å/min. PSG films of 15,000 to 19,000 Å thickness and containing 9–12 mol % P<sub>2</sub>O<sub>5</sub> were deposited over IC wafers. Induced stress crack testing at 530°C showed no

| Sample<br>No.*                                                                            | Film<br>Thickness<br>(Å)                       | Deposition<br>Rate<br>(A/min)                           | Etch Rate <sup>†</sup><br>(A/sec) | Stress<br>(dynes/cm²)                                                                                            |  |

|-------------------------------------------------------------------------------------------|------------------------------------------------|---------------------------------------------------------|-----------------------------------|------------------------------------------------------------------------------------------------------------------|--|

| Deposit                                                                                   | ed at 340°C; 109                               | % SiH, in Ar at                                         | a Flow Rate of                    | 375 cm <sup>3</sup> /min                                                                                         |  |

| 1                                                                                         | 10,970                                         | 1,100                                                   |                                   | $2.7 \times 10^{\circ}$                                                                                          |  |

| 1<br>2<br>3<br>4<br>5                                                                     | 11,200                                         | 1,120                                                   | 17.8                              | $3.1 \times 10^{\circ}$                                                                                          |  |

| 3                                                                                         | 14,000                                         | 1,400                                                   |                                   | $3.2 \times 10^{\circ}$                                                                                          |  |

| 4                                                                                         | 11,570                                         | 1,160                                                   | 17.2                              | $3.2 \times 10^{\circ}$                                                                                          |  |

| 5                                                                                         | 9,540                                          | 950                                                     | 18.9                              | $3.4 \times 10^{\circ}$                                                                                          |  |

| Deposited at 400°C; 10% SiH <sub>4</sub> in Ar at a Flow Rate of 325 cm <sup>3</sup> /min |                                                |                                                         |                                   |                                                                                                                  |  |

| 6                                                                                         | 12,620                                         | 1,260                                                   | 17.0                              | 3.6 × 10°                                                                                                        |  |

| Ž                                                                                         | 17,600                                         | 1,760                                                   | 16.6                              | $2.9 \times 10^{9}$                                                                                              |  |

| ċ                                                                                         | 10000                                          |                                                         |                                   |                                                                                                                  |  |

| 8                                                                                         | 13.800                                         | 1,380                                                   |                                   | $3.3 \times 10^{9}$                                                                                              |  |

| 8                                                                                         | $13,800 \\ 14,100$                             | $1,380 \\ 1.410$                                        | 17.5                              | $3.3 \times 10^{\circ}$<br>$3.0 \times 10^{\circ}$                                                               |  |

| 6<br>7<br>8<br>9<br>10                                                                    | 13,800<br>14,100<br>12,380                     | 1,380<br>1,410<br>1,240                                 | 17.5                              |                                                                                                                  |  |

| 10                                                                                        | 14,100                                         | 1,410<br>1,240                                          |                                   | 3.0 × 10°<br>3.3 × 10°                                                                                           |  |

| 10<br>Deposi                                                                              | 14,100<br>12,380<br>ted at 450°C; 10           | 1,410<br>1,240<br>0% SiH <sub>4</sub> in Ar at          |                                   | 3.0 × 10°<br>3.3 × 10°                                                                                           |  |

| 10<br>Deposi                                                                              | 14,100<br>12,380<br>ted at 450°C; 10<br>11,140 | 1,410<br>1,240<br>0% SiH <sub>4</sub> in Ar at<br>1,110 |                                   | 3.0 × 10°<br>3.3 × 10°                                                                                           |  |

| 10<br>Deposi                                                                              | 14,100<br>12,380<br>ted at 450°C; 10           | 1,410<br>1,240<br>0% SiH <sub>4</sub> in Ar at          |                                   | $3.0 \times 10^{\circ}$<br>$3.3 \times 10^{\circ}$<br>$233 \text{ cm}^{3}/\text{min}$<br>$2.8 \times 10^{\circ}$ |  |

Table 2—Relationship of Stress in CVD SiO<sub>2</sub> Films and Deposition Temperature (N<sub>2</sub> diluent flow rate: 6000 cm<sup>3</sup>/min; O<sub>2</sub> flow rate: 687 cm<sup>3</sup>/ min; deposition time: 10 min)

\*Samples were prepared on different dates. †P-etch at 25.0°C.

cracks in films deposited with  $O_2$ :hydride ratios of 10:1 and lower, some cracks at a ratio of 20:1, and a very high density of cracks at a ratio of 40:1.

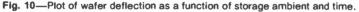

## 5.6 Stress as a Function of Glass Composition

A number of investigators<sup>1,9,18,26,50,52</sup> have reported lower stress for PSG layers compared to  $SiO_2$ , and that the stress tends to decrease as

| Table                                                                                     | 3-Relationship of Stress in CVD SiO <sub>2</sub> Films and O <sub>2</sub> /SiH <sub>4</sub> Ratio (De- |  |  |  |

|-------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|--|--|--|

| position temperature: 450°C; N <sub>2</sub> flow rate: 6 liters/min; 10% SiH <sub>4</sub> |                                                                                                        |  |  |  |

|                                                                                           | in Ar at a flow rate of 190 cm³/min)                                                                   |  |  |  |

| O2:SiH<br>(Ratio) | O, Flow<br>Rate<br>(cm³/min) | Oxide<br>Thickness<br>(A) | Deposition<br>Rate<br>(A/min) | Tensile<br>Stress<br>(dynes/cm²) |

|-------------------|------------------------------|---------------------------|-------------------------------|----------------------------------|

| 36:1              | 687                          | 12,600                    | 1,260                         | $2.9 \times 10^{9}$              |

| 14:1              | 263                          | 14,200                    | 1,420                         | $2.8 \times 10^{9}$              |

| 3:1               | 60                           | 11,900                    | 1,190                         | $3.2 \times 10^{9}$              |

the phosphorus concentration in the glass is increased. In agreement with this, our experiments have shown that as the phosphorus content in a CVD PSG layer increases from 0 to 8.5 wt %, the room temperature stress decreases. Stress for pure SiO<sub>2</sub> films deposited at 450°C at 10,000 Å/min averages  $3.1 \times 10^9$  dynes/cm<sup>2</sup>, for the PWS 2000 continuous reactor. As one increases the phosphorus content to 8.5 wt % and maintains the film deposition rate at 10,000 Å/min (450°C), the tensile stress at room temperature is reduced to essentially zero. However, upon densification at 1000°C, the layer went into a compressive stress of  $1.3 \times 10^9$  dynes/cm<sup>2</sup>. Results thus show that room-temperature stress in CVD films can be reduced to nearly zero by increasing the phosphorus content; however, excessively high concentrations of phosphorus can lead to electrochemical attack of

Fig. 11—Room temperature tensile stress versus wt % phosphorus for films deposited at 450°C at a rate of 1 μm/min. Deposition of these films was carried out in a continuous processing reactor (PWS-2000).

the aluminum.<sup>1,52,53</sup> The relationship of phosphorus content in 1- $\mu$ m-thick PSG films deposited at 450°C and the room-temperature tensile stress is shown graphically in Fig. 11.

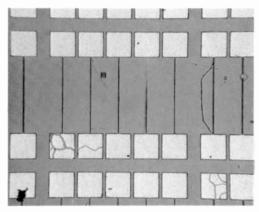

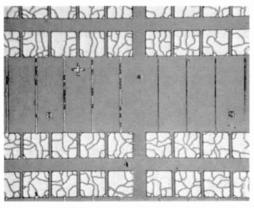

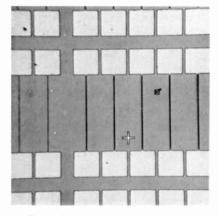

Layers of SiO<sub>2</sub> and of 2, 3, and 4 wt % phosphorus PSG were deposited on IC device wafers and examined for stress cracks. CVD processing was carried out in the rotary reactor under the usual conditions at 450°C, and the layer thicknesses ranged from 1.1 to  $1.2 \ \mu m$ . Both linear bipolar IC's (CA3747) with large aluminum-metallized capacitor areas and CMOS IC's (CD4017A) were chosen for these tests. The overcoat layers were delineated by photolithography and chemical etching to open the aluminum bond-pad areas and the grid lines. Microscopic examination showed that the highly stressed  $SiO_2$ layer had cracked along the edges and in the interior of the large aluminum-metallized areas. Additional cracks formed along the entire edge of the circuit over the dense oxide. The glass layers containing 2, 3, or 4 wt % phosphorus exhibited no cracks, thus demonstrating that the incorporation of a relatively small amount of phosphorus in the glass can have a very large effect on preventing glass cracking.

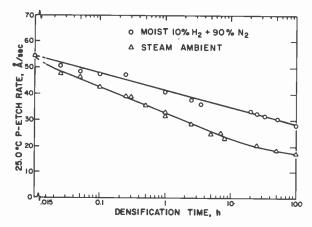

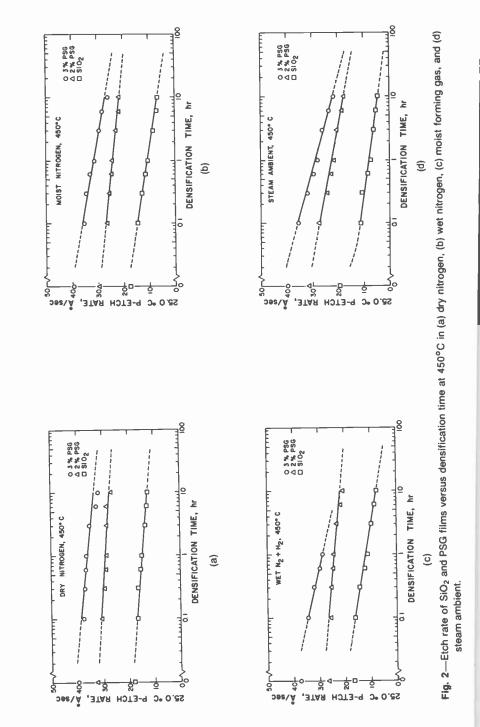

5.7 Effect on Stress of Intentionally Introduced Water Vapor During CVD of SiO\_2 and PSG Films

It has been demonstrated that substantial degrees of densification of CVD films can be achieved by prolonged heat treatments at 450°C in ambients containing water vapor.<sup>2,4</sup> To attempt to lower the tensile stress directly in the as-deposited layers,  $H_2O$  vapor was intentionally added into the CVD reaction chamber at a deposition temperature of 450°C.

Since  $H_2O$  is one of the reaction products when SiH<sub>4</sub> is oxidized, it was necessary to substantially increase the  $H_2O$  content to observe an effect. This was easily accomplished by passing the main N<sub>2</sub> carrier

| Substrate<br>Deposition<br>Temperature<br>(°C) | Water Vapor<br>Content (factor<br>increase over that<br>present from<br>chemical reaction) | Deposition<br>Rate (A/min) | Stress<br>(dynes/cm?)   |

|------------------------------------------------|--------------------------------------------------------------------------------------------|----------------------------|-------------------------|

| 350                                            | 0                                                                                          | 1750                       | 3.2 × 10°               |

|                                                | 4.2                                                                                        | 1750                       | 2.8 × 10°               |

|                                                | 0                                                                                          | 500                        | 2.5 x 10°               |

|                                                | 6.7                                                                                        | 500                        | $2.2 \times 10^{\circ}$ |

| 450                                            | 0                                                                                          | 1000                       | 2.8 x 10°               |

|                                                | 9.2                                                                                        | 1000                       | 2.4 × 10°               |

|                                                | 0                                                                                          | 350                        | $2.7 \times 10^{\circ}$ |

|                                                | 14.5                                                                                       | 350                        | $1.7 \times 10^{\circ}$ |

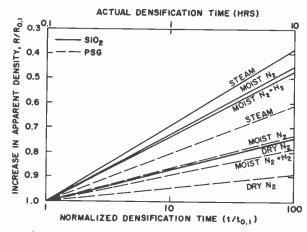

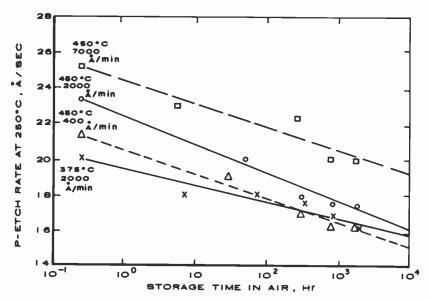

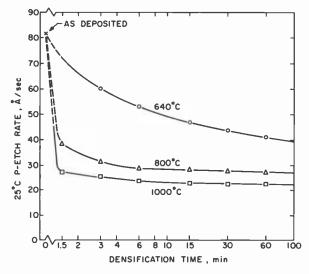

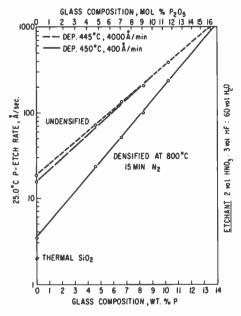

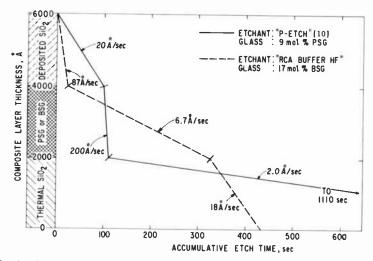

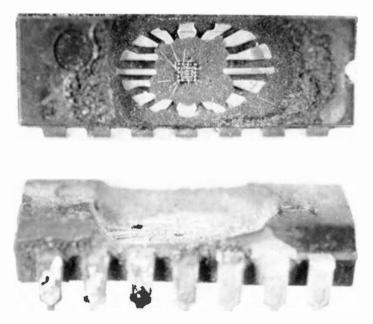

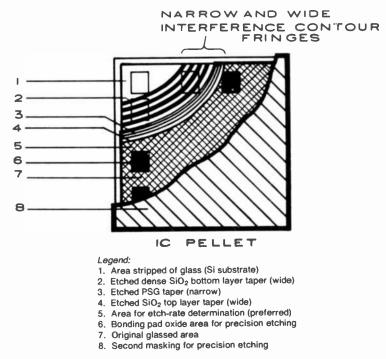

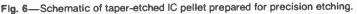

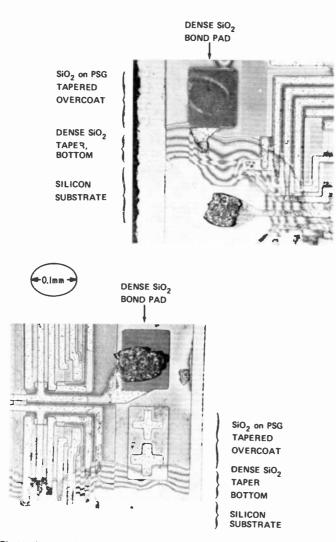

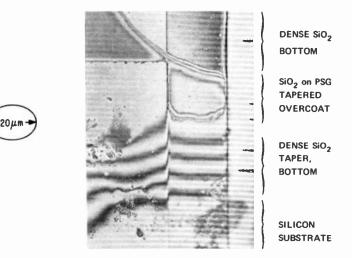

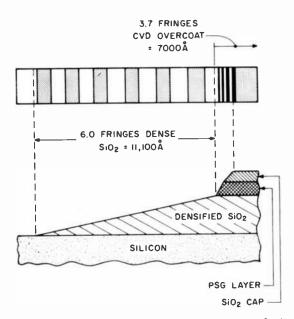

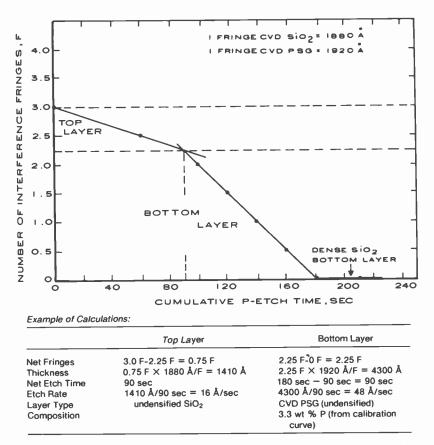

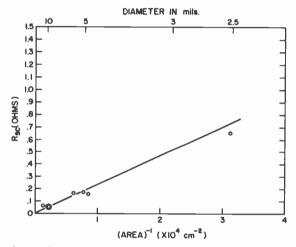

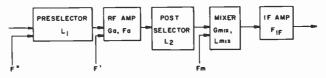

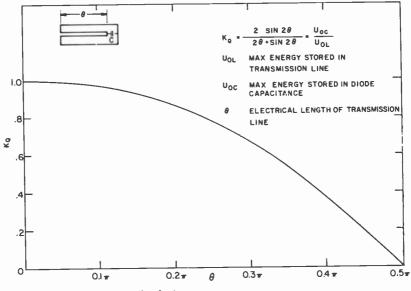

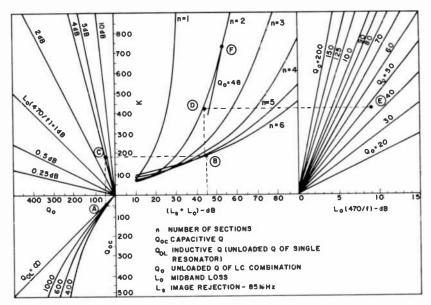

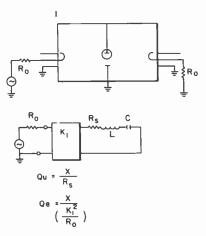

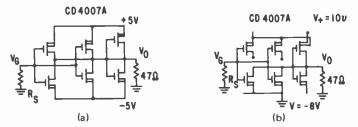

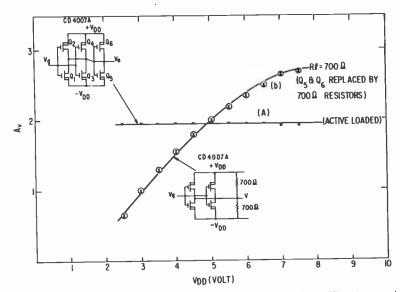

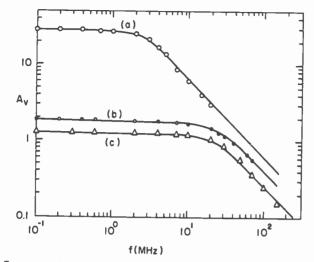

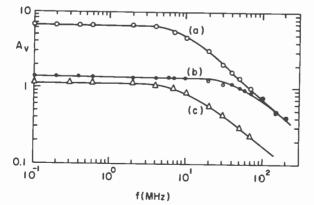

Table 4-SiO<sub>2</sub> Films Deposited on Silicon in Dry and Wet Nitrogen