# Electronic Vol. 6, No components & applications

198

## Electronic components & applications

Volume 6, No. 4

1984

Editors Ian L. A. Crick Michael J. Prescott

Design and production Cees J. M. Gladdines Bernard W. van Reenen Jacob Romeijn Michael J. Rose

*Design consultant* Theo Kentie

Not so long ago the solid-state imager was regarded as little more than a curiosity, something for the research labs to play with, but no real competition for the tv camera tube. In just a few short years, however, those early imagers have grown into something really big. Already we find two-dimensional imagers, such the NXA1010/1020 frame-transfer sensors featured in this issue, replacing vidicons in CCTV and home video systems, and it won't be long before they hit the broadcasting market in the latest ENG tv cameras. But their real future ties in areas where camera tubes have hardly penetrated, such as character-recognition systems and home security systems, and in the more distant future, videophones, robot-vision systems and electronic still-picture cameras. With such a bright future, the solid-state imager is certainly worth keeping an eye on.

## Contents

| Disk controller supports both rigid and floppy drives Guy Thomsen                                                   | 194        |

|---------------------------------------------------------------------------------------------------------------------|------------|

| Liquid-crystal displays for automotive applications<br>E. Loward and P. Streit                                      | 202        |

| An integrated approach to CD players<br>Part 1: The optical pickup<br>Part 2: The decoding electronics<br>J. Nijhof | 209<br>216 |

| The frame-transfer sensor – an attractive alternative to the tv camera tube <i>U. Feddern and S. Zur Verth</i>      | 223        |

| DMA Interface for 68000 systems<br>Guy Thomsen and Bart Vernooij                                                    | 230        |

| Interfacing HCMOS with other logic families J. P. Exalto                                                            | 239        |

| High-voltage rectifier stacks for diode-split transformer Graham Hine                                               | 246        |

| Abstracts                                                                                                           | 253        |

| Authors                                                                                                             | 256        |

All information in Electronic Components and Applications is published in good faith, but the publishers assume no liability for any consequence of its use; its publication these not imply a licence under any patent. Specifications and availability of goods mentioned in it are subject to change without notice.

## Disk controller supports both rigid and floppy drives

#### **GUY THOMSEN**

Many designers are developing systems that use hard disks for on-line mass storage and some other medium to back up the disks. Because it's compact, portable and inexpensive, the floppy disk has been a popular back-up choice, but until now, its use has meant that you had to develop two separate controllers – one for each drive type.

Using a new 2-chip set, however, you can design a single controller to service both rigid and floppy disks. The two ICs are the SCN68454, an intelligent multiple-disk controller (IMDC). and the SCB68459, a phase-locked loop for the disk drives (DPLL). You can use the pair of chips to control as many as four rigid or floppy disks in any combination. The ICs can work with any drive that has a Shugart SA850, SA1000 or Seagate ST506 interface. (For more details on the controller and phase-locked loop, see panel).

If you want to employ these chips, though, the controller will affect your overall system design, especially its memory usage and the software drivers that control data transfers. On the other hand, adding the hardware to your system is an easy process, and once you understand the hardware, the controller's operation and its effect on your software becomes clear. So it's best to begin with a hardware implementation that can serve as a model for understanding the controller's unique way of operating.

#### SIMPLE CONTROLLER HARDWARE

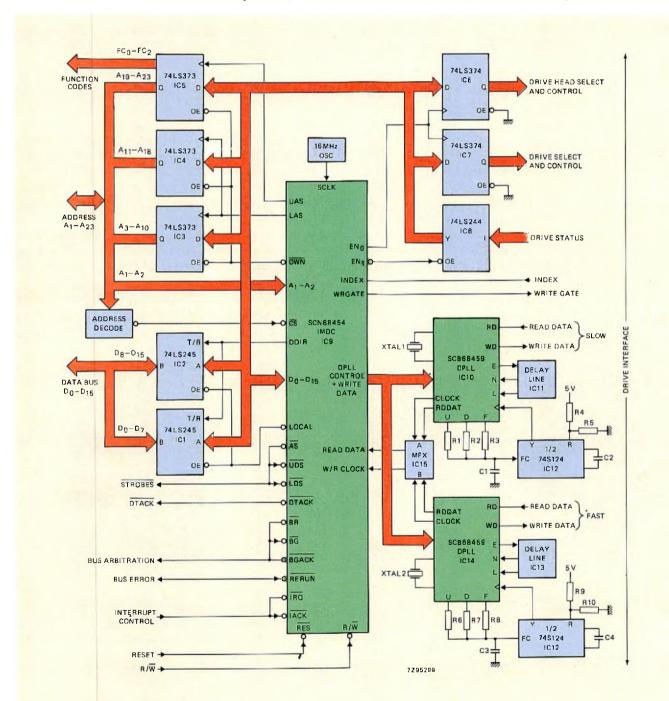

The use of the IMDC and DPLL hardware in the design of a controller is rather straightforward. As Fig.1 shows, you need only a few ICs - some octal buffers, an address decoder, a multiplexer, and a couple of delay lines and voltage-controlled oscillators (VCOs) - in addition to the

IMDC and two DPLLs. With conventional ICs, you'd need more than 90 devices to provide the same features found in the IMDC/DPLL-implemented design.

The controller's interface to the 68000-based host system's bus consists of five octal buffers: three 74LS373s for address and function codes and two 74LS245s for data. Address lines A<sub>1</sub> and A<sub>2</sub> and all other control lines can be tied directly to the system bus. Once the host has activated the IMDC by sending the IMDC's address to the address decoder (which activates the IMDC's chip-select ( $\overline{CS}$ ) line), lines A<sub>1</sub> and A<sub>2</sub> directly address the IMDC's internal registers.

Tied to the controller side of these five buffers is a 16-bit bus, called the local bus, which is controlled by the IMDC. When the IMDC wants to send an address to the host, it first puts the high-order addresses  $A_{19}$  to  $A_{23}$  and function codes FC<sub>0</sub> to FC<sub>2</sub> on bus lines D<sub>8</sub> to D<sub>15</sub> and asserts the upper address strobe (UAS). IC<sub>5</sub> retains the data after UAS returns LOW.

Next, the IMDC puts the lower-order address codes A3 to A18 on the bus and asserts the lower address strobe (LAS). When LAS is driven LOW, IC3 and IC4 retain the address. Finally, the IMDC puts the remaining address bits on lines A1 and A2 and sends the address through a normal 68000-bus cycle using the address strobe,  $\overline{AS}$ , and the data strobes,  $\overline{UDS}$  and  $\overline{LDS}$ . If during a consecutive addressing operation, the higher-order address lines remain unchanged, the IMDC doesn't reload the upper address lines.

The local bus also transfers data to and from the host system. When the IMDC uses DMA to read data from host memory, for example, it first latches that data into IC<sub>1</sub> and IC<sub>2</sub>; the state of the data-direction (DDIR) line determines which port of these bidirectional buffers will accept the data for buffering, and the LOCAL line enables the buffers.

Then, using the local bus, the IMDC moves the data to temporary storage in its 128 byte first-in, first-out (FIFO) buffer before transferring the data to a disk. A write operation is just the opposite: data from the disk is sent to the FIFO, then to the bidirectional buffers, and then to the host memory.

The local bus also carries control information between the IMDC and the disk units. With EN<sub>0</sub> HIGH, data is latched into  $IC_6$  and  $IC_7$ . With  $EN_1$  LOW, buffer  $IC_8$  passes information back to the IMDC.

Data is written to or read from a drive by means of the DPLL. In Fig.1, two DPLLs are used: one for a slow read/ write data path (floppy-disk drive), and the other for a fast read/write data path (rigid-disk drive). The example uses two parts because different drives can require different read-data rates and associated voltage-controlled-oscillator

#### DISK CONTROLLER

(VCO) timing, and because the two write clocks require different crystals. If the data rates for both types of drive attached to the IMDC were the same, then the circuit would only require one DPLL. In any case, you only require one IMDC to control four disk units.

In this case, each DPLL uses a separate VCO, ½ of a 74S124. You attach the VCO to the DPLL via three resistors and a capacitor. The resistors attach to the pump-up, pump-down and frequency-pump pins of the DPLL. The voltages that the DPLL pumps across these resistors are summed by the capacitor. The sum point of the four passive devices attaches to the VCO's frequency-control pin.

In addition to the four passive devices used for frequency control, passive elements control other VCO parameters. Two resistors (you could use one trim pot instead) set the frequency range, and a capacitor sets the range's centre frequency.

The final part that the DPLL requires is the crystal. This crystal must have a frequency that is twice the data rate of the disk drive or drives attached to the DPLL. The DPLL function requires only three ICs and eight passive components. Many other designs would require amplifiers and a lot of components to accompish the same function.

You need the multiplexer, IC<sub>15</sub>, when you incorporate two or more DPLLs into a design. IC<sub>15</sub> selects the Read Data and Read/Write Clock from the DPLL for the drive chosen. The other control signals can go directly to each DPLL.

#### INITIALIZATION

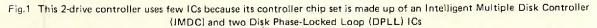

Before the IMDC performs any operation, three areas must be initialized: one in the controller and two in the host system. These areas are the IMDC's internal registers and two special areas of the host memory – the event control area (ECA) blocks and the ECA pointer table. These three areas are critical to the controller's unique way of performing. By writing to the IMDC's registers, the host system tells the controller what operations to perform, and by looking at the ECA pointer table and the ECA blocks, the IMDC knows how to perform them.

There are seven addressable registers in the IMDC (Fig.2). To initialize them, the host must load the first four registers – the ECA registers – with the address of the ECA pointer table. It then loads the fifth register – the Interrupt Vector register – with the vector-priority number assigned to the IMDC. The last two registers are initialized just prior to actual operation; before initializing them, the ECA pointer table and the ECAs themselves must be initialized.

The ECA pointer table contains the addresses of the ECA blocks, there can be as many as four - one for each of four drives. The block addresses are arranged by drive number in ascending order. The ECA block addresses need not be contiguous; the only requirement is that the IMDC should be able to address them.

The ECA blocks must also be initialized. That is, each block must contain the drive parameters that the IMDC

needs in order to determine whether the drive is rigid or floppy. Normally, once you set up these areas, you shouldn't need to change them.

While there is normally a separate ECA block for each drive, you can use an ECA block for more than one disk unit if you take proper care. If there are common parameters in ECA blocks, save those parameters separately from the unique parameters that are associated with a particular disk's physical address. After you access the unique parameters, branch to the common parameters.

Within the ECA block, eleven IMDC commands provide read and write data transfers (Table 1). Status gets updated at the completion of each requested operation. The status consists of two areas: a main status and an extended status. For each command completion, it is necessary to check only the main status to determine whether an error is posted. If there is no error, the extended status provides additional information about the operation.

The System Buffer Address and Disk Physical Address define where to transfer data from and to during a read or write. The remainder of the ECA block defines special parameters for each command and drive type. The IMDC uses these bytes to determine whether the disk unit is rigid or floppy, and the extent of storage capabilities. Included are the parameters that define step rate, head load time (if required) and other physical features.

In the IMDC, there are only two registers that the system software uses during disk operations: the Interrupt Source and Drive Status registers. To request an IMDC operation, the host software must set one of four bits in the Drive Status register. Each bit corresponds to one of the four drives. Setting a bit flags the IMDC to use the ECA pointer register plus an appropriate offset to get the ECA block address. The IMDC then uses this address to obtain the what, where and how for the current request.

| TABLE I       IMDC commands |             |                                 |  |  |

|-----------------------------|-------------|---------------------------------|--|--|

| command<br>mnemonics        | HEX<br>code | description                     |  |  |

| WRMS                        | 00          | write multiple sector           |  |  |

| WRDD                        | 01          | write with deleted data flag    |  |  |

| VER                         | 10          | verify sector data              |  |  |

| REMS                        | 11          | read multiple sector            |  |  |

| PRP                         | 12          | programmable record processing  |  |  |

| TSR                         | 13          | transparent sector read         |  |  |

| RETD                        | 20          | read identifier                 |  |  |

| FORM                        | 40          | format track                    |  |  |

| CALB                        | 41          | recalibrate to track zero       |  |  |

| CORR                        | 81          | correct data with ECC remainder |  |  |

| DIAG                        | 80          | diagnostic                      |  |  |

When the IMDC completes the posted command, it sets the appropriate bit in the Interrupt Status register and asserts the interrupt line to the host processor. The system software then reads the ECA status to determine proper command completion, and the cycle continues as necessary. You can set each of the bits in the Drive Status register independently of the others. Resetting a bit before an operation is complete aborts the request and sets an interrupt. Figure 3 shows a sample flowchart. Figure 4 contains an interrupt service routine for the IMDC written in 68000 microprocessor assembly language.

Fig.3 This flowchart contains all the interrupt handling for a simple disk-controller system

| :           | IN     | TERRUPT SERVICE ROU | TINE FOR IMOC                 |

|-------------|--------|---------------------|-------------------------------|

| *********** |        |                     |                               |

|             |        |                     | SAVE REGISTER                 |

| IMDC-INTR   | MOVE.L | D0,-(SP)            |                               |

|             | MOVE B | MAIN STATUS, DO     | GET MAIN STATUS BITS          |

|             | BEQ.S  | INTR-CONT           | SKIP ERROR REPORT IF OK       |

| :           |        |                     |                               |

|             | OSR.L  | ERROR-REPORT        | GO TO ERROR REPORTING ROUTINE |

|             |        |                     |                               |

| INTR-CONT   | MOVE.8 | INTR SOURCE.DD      | GET THE FINISHED DRIVE NUMBER |

|             | EOR.B  | DO, DRIVE-STATUS    | CLEAR DRIVE-BUSY BIT          |

|             |        |                     | ,                             |

|             | MOVE   | SR.00               | GET 68000 STATUS BITS         |

|             | AND.W  | #INTR-MASK.DD       | CLEAR INTERRUPT-MASK BITS     |

|             |        |                     | RETURN STATUS BITS TO 68000   |

|             | MOVE   | D0,SA               | HETURN STATUS BITS TO BOOD    |

|             |        |                     |                               |

|             | MOVE.L | (SP)+,00            | RETURN SAVED REGISTER         |

| 2           |        |                     |                               |

|             | RTR    |                     | RETURN FROM INTERRUPT         |

Fig.4 This interrupt service routine for the Intelligent Multiple Disk Controller is written in 68000 assembly-language code

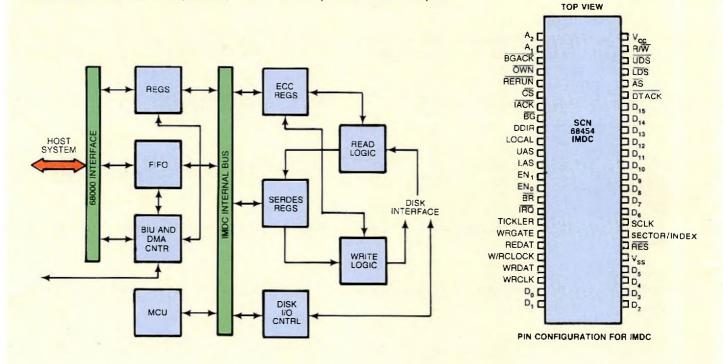

The SCN68454 Intelligent Multiple-Disk Controller (IMDC) illustrated in Fig.A is a microprogrammed disk-control subsystem that employs a memory-to-memory architecture. Bus compatible with the 68000 microprocessor family and its vectored interrupt structure, the IMDC has 31 address lines for the DMA transfer, a 128-byte first-in, first-out (FIFO) buffer, a 31-bit address counter and user-specified data transfers of either 8 or 16 bits to the host data bus. Housed in a standard 48-pin DIP, the IMDC needs only a single 5 V power supply.

The IMDC is the interface to both the host system and the disk units. The IMDC and host system use the IMDC's seven internal registers for communication about the task to be performed. After the IMDC accepts a command from the host, an onchip direct-memory-access (DMA) controller takes charge of all transfers between system memory and IMDC. The IMDC uses its onchip FIFO buffer to provide temporary storage during data transfers.

The IMDC's disk-interface section contains the read and write logic, the serial/ deserial register, the error check and correction (ECC) register, and the disk input/ output (I/O) control logic. The table shows the input and output lines.

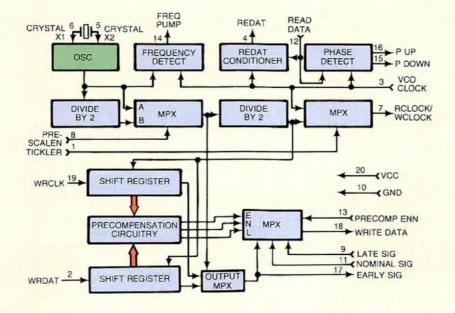

Complementing the IMDC is the SCB68459 Disk Phase-Locked Loop (DPLL),

#### A CLOSER LOOK AT THE CHIP SET

a 20-pin bipolar IC. Like the IMDC, it requires only a single 5 V power supply. The block diagram (Fig.B) shows the DPLL's internal architecture.

The DPLL uses an external voltagecontrolled oscillator to provide a variable clock rate to track the read data from the disk unit. The on-board crystal oscillator also generates the write clock. The DPLL operates with a composite data rate of 100 kHz to 10 MHz for precision management of the bit stream flowing between the disk drive(s) and the host system. Precompensation logic is built into the chip; designers can use this precompensation to write-compensate the modified-frequencymodulation (MFM) data to the disk unit.

However, the devices are not limited in scope to use with the 68000 microprocessor family. Designers can integrate the IMDC and DPLL for use with any microprocessor architecture that employs either an 8- or 16-bit data bus. In any system design, expect a relatively low component count. The 2-chip set integrates the equivalent functions of 90 or more ICs. Because of this high level of integration, the chips reduce PC-board space by as much as 90%. Correspondingly, manufacturing costs are reduced and reliability increased.

The ability to detect and correct data errors is an important feature of any disk

controller. The IMDC and DPLL support multiple-sector read/write with implied seek and automatic bad-sector handling. The IMDC can correct data errors by using either 32- or 40-bit user-specified ECC polynomials or with the CRC-CCITT (cyclic redundancy check) polynomial.

One powerful IMDC feature is real-time record processing, which allows the user to specify the search criteria on a characterby-character basis and to specify the action that is to occur on completion of the search.

The IMDC supports the IBM 3740 and System 34 media formats as well as soft- or hard-sector formats. The device handles both frequency-modulation (FM) and modified-frequency-modulation (MFM) data formats with data rates as high as 2 million bits/sec for FM and 10 million bits/sec for MFM-regardless of the host processor's operating speed.

The introductory version of the chip set controls as many as four rigid and/or floppy drives. At present, these drives must have Shugart SA850, SA1000 or Seagate ST560 standard interfaces. Future changes in the IMDC's mask-programmable microcode will let you use the chip with other interfaces, such as ESDI, ANSI and SMD.

Fig.A The Intelligent Multiple Disk Controller provides an interface between the host system and the disk units

|             |                | input                                 |                | output                     |

|-------------|----------------|---------------------------------------|----------------|----------------------------|

| bus<br>line | signal<br>name | definition                            | signal<br>name | definition                 |

| DO          | INDEX          | rigid-disk index signal               | HEAD1          | head select 2°             |

| D1          | READY          | disk ready                            | HEAD2          | head select 2 <sup>1</sup> |

| D2          | SEEKC          | seek complete                         | HEAD4          | head select 2 <sup>2</sup> |

| D3          | TR0A           | track-zero first signal               | HEAD8          | head select 2 <sup>3</sup> |

| D4          | TR1A           | track-zero second signal              | HEAD16         | head select 2 <sup>4</sup> |

| D5          | WFA            | floppy write-protect                  | not use        | ed                         |

| D6          | WFB            | write fault                           | STEP           | head step pulse            |

| D7          | not used       | d                                     | DIR            | direction of head          |

| D8          | not used       | d                                     | LWC            | low write current          |

| D9          | not used       | d                                     | мот            | motor on                   |

| D10         | not used       | d                                     | PRECOM         | precompensation enable     |

| D11         | not used       | d                                     | HDL            | head load for floppies     |

| D12         | not used       | d                                     | SELO           | drive 0 select             |

| D13         | not used       | d                                     | SEL1           | drive 1 select             |

| D14         | not used       | b b b b b b b b b b b b b b b b b b b | SEL2           | drive 2 select             |

| D15         | not used       | b                                     | SEL3           | drive 3 select             |

Fig.B The Disk Phase-Locked Loop (DPLL) uses an external voltage-controlled oscillator for the variable clock rate which tracks the read data from the disk unit

#### FORMATTING DIFFERENT DRIVE TYPES

The IMDC lets you format disks to several different standards. The device supports both the IBM single-density (IBM 3740) and double-density (IBM System 34) formats. and it can format both hard- and soft-sectored disks. The user can also specify either a 1- or 2-byte cylinder field within the sector header. This accommodates the next generation of rigid disk units which may have more than 256 cylinders.

Each of the format options has a fixed number of bytes that are repeated within each sector; the IMDC automatically writes those bytes. The IMDC fetches from a table in memory the bytes that vary, such as the cylinder number, head and sector number. The System Buffer Address in the ECA table points to this table.

For each sector on each track of a floppy disk, the software driver first puts into ECA memory the cylinder number, side, sector number and record length. Using DMAs, the IMDC then puts the information into the FIFOs during the format operation. Because the user places the information into the ECA, he or she can specify the sector mapping on the track. This can take place in any order the user wants, and it links together as many consecutive sectors as the system software requires. The IMDC can read consecutively numbered sectors over the total track length.

The information for a rigid-disk format is the same as for the floppy-disk format, except that there is no sector length placed in the sector header. With a rigid disk, formatting takes place one track at a time. This allows the user to perform other disk operations without waiting for the whole disk to be formatted. For some drives, the formatting time is several minutes.

#### HANDLING BAD SECTORS

The IMDC provides the user with a bad-sector feature. If, after formatting a track, tests show that an area has an unreliable sector, the IMDC provides a bad-sector flag, along with an alternative physical address. During a read or write to that sector, the IMDC finds the flag, reads the alternative sector address and goes to that sector. The IMDC then moves the drive head to that sector, performs a seek operation (if one is required by a read-operation), and completes the transfer operation to that location in the normal way. The IMDC then returns to the track with the bad sector and continues the read operation at the next sector.

The IMDC's ability to select alternative sectors is especially useful during multiple-sector data transfers, the user is not aware of any interruptions in the actual data transfer. It also relieves the system software of the responsibility of maintaining an alternative-sector map on the disk and performing the extra operations required during the data transfers.

An unusual feature built into the disk controller is its ability to search for a character string and then perform an operation. With this feature (the Programmable Record Processing (PRP) command), you can instruct the IMDC to locate a specific string of characters within a logical data block on a disk. After the match, the IMDC can read the logical data block, process a pointer within the data block or locate all blocks that satisfy some search criteria.

You specify the PRP functions by filling the Scan Control Word Table (SCWT) with the string and instruction parameters. The SCWT is part of the system memory, and its address is placed into the ECA table in the PRP parameters area. Each word of the SCWT consists of two parts, one data and the other an instruction; each part is eight bits long. The IMDC divides the FIFO memory into two parts for the PRP command; one part is dedicated to the character string and instructions, and the other is to be used during the disk data transfers. The FIFO memory receives the PRP commands and character string before the operation begins.

The physical sector address and a byte-count offset specify the start of the first byte to be scanned. You can specify the end of the record for which you are looking in terms of either a fixed record length or an end-of-record character.

You can transfer either the records for which you are searching or their locations to the system memory. In either case, you begin by reading records on the disk sequentially. When a record meets the search criteria, you can either immediately transfer the record's data into the system memory, or you can tell the IMDC to log the location of the record match and return the logged location to system memory.

You can write a software driver for the IMDC in two levels: entry level – for cold-start (power-on) entry to the drives, or normal level – for access to the drives during normal operation. Both levels can be part of the same driver, with flags and tests to route the program to the correct procedures.

As previously noted, the IMDC registers, ECA pointer table and ECA blocks must be initialized before any operation is performed. At power up, a typical operating system would put into the ECA pointer table the address of each ECA block and fill the ECA block with the parameters that define the disk types. Although these parameters would not usually change during normal operation, a diagnostic routine might call for such a change. Table 2 shows the ECA block parameters used by each command.

During successive disk operations, the parameters most likely to change from one operation to the other, are the Command Code, Buffer Address and the Physical Disk Address (cylinder, head and sector), which define the nature, location and quantity of the requested transfer. Therefore, the operating system should, at least, pass these parameters to the normal-level software driver. In some cases, the buffer length will differ from the sector length, so it, too, should be updated with each command. For example, a read (REMS) operation without any data transfer becomes a seek command.

The last thing the driver must know is what drive to activate. This unit's number becomes the busy bit set in register 7 of the IMDC, reflecting the fact that it is the selected drive. As it is possible to request more than one operation at a time, the driver must be sure that it does not permit a previously requested drive's bit to be overwritten.

|                                  |      |      |     |      | com | nand mn | emonics |      |      |      |      |

|----------------------------------|------|------|-----|------|-----|---------|---------|------|------|------|------|

| ECA parameter used               | WRMS | WRDD | VER | REMS | PRP | TSR     | RETD    | FORM | CALB | CORR | DIAG |

| COMMAND CODE                     | •    |      |     |      | •   | •       |         |      | •    |      |      |

| STATUS BYTES                     |      | •    | •   | •    | •   | •       | •       | •    | •    | •    |      |

| MAX NUMBER OF RETRIES            | •    | •    | •   |      | •   |         | •       |      | •    |      |      |

| DMA COUNT                        | •    | •    | •   | •    | •   | •       | •       |      |      | •    |      |

| COMMAND OPTIONS                  | •    | •    | •   | •    | •   | •       | •       | •    |      | •    |      |

| BUFFER ADDRESS                   | •    | •    | •   | •    | •   | •       | •       | •    |      | •    |      |

| BUFFER LENGTH REQUEST            | •    | •    | •   | •    | •   | •       | •       | •    |      | •    |      |

| CYLINDER NUMBER                  | •    | •    | •   | •    | •   | •       | •       | •    | •    |      |      |

| HEAD NUMBER                      | •    | •    | •   | •    | •   | •       |         | •    |      |      |      |

| SECTOR NUMBER                    | •    | •    | •   | •    | •   | •       |         |      |      |      |      |

| PRP COMMAND CONTROL WORD         |      |      |     |      | •   |         |         |      |      |      |      |

| PRP PARAMETERS                   |      |      |     |      | •   |         |         |      |      |      |      |

| NO – PRE INDEX GAP               |      |      |     |      |     |         |         | •    |      |      |      |

| N1 – POST INDEX GAP              |      |      |     |      |     |         |         | •    |      |      |      |

| N2 – SYNC BYTE COUNT             | •    | •    |     |      |     |         |         | •    |      |      |      |

| N3 – POST-ID GAP                 | •    | •    |     |      |     |         |         | •    |      |      |      |

| N4 – POST-DATA GAP               |      |      |     |      |     |         |         | •    |      |      |      |

| N5 – ADDRESS MARK CONTROL        | •    | •    | •   | •    | •   | •       | •       | •    |      |      |      |

| ECC MASK                         | •    | •    | •   | •    | •   | •       | •       | •    |      | •    |      |

| MOTOR-ON DELAY                   | F    | F    | F   | F    | F   | F       | F       | F    | F    |      |      |

| NUMBER OF HEADS                  | •    | •    | •   | •    | •   | •       | •       | •    |      |      |      |

| ENDING SECTOR NUMBER             | •    | •    | •   | •    | •   | •       | •       | •    |      |      |      |

| STEPPING RATE                    | •    | •    | •   | •    | •   | •       | •       | •    | •    |      |      |

| HEAD SETTLING TIME               | •    | •    | •   | •    | •   | •       | •       | •    | •    |      |      |

| HEAD LOAD TIME                   | F    | F    | F   | F    | F   | F       | F       | F    |      |      |      |

| SEEK TYPE                        | •    | •    | •   | •    | •   | •       | •       | •    | •    |      |      |

| LOW WRITE CURRENT BOUNDARY TRACK | •    | •    | •   | •    | •   | •       | •       | •    |      |      |      |

| PRECOMP BOUNDARY TRACK           | •    | •    | •   | •    | •   | •       | •       | •    |      |      |      |

| MAX NUMBER CYLINDERS/TRACKS      | •    | •    | •   | •    | •   | ٠       | •       | •    |      |      |      |

| SECTOR LENGTH/LAST SECTOR NUMBER | •    | •    | •   | •    | •   | •       | •       | •    |      |      |      |

| FLAG BYTE                        |      |      | •   | •    |     | •       | •       |      |      |      |      |

| B-TREE POINTER                   |      |      |     |      | •   |         |         |      |      |      |      |

TABLE 2

ECA parameters used by each command

F = floppy only.

#### ACKNOWLEDGEMENT

This article originally appeared in the October 4 issue of EDN, copyright 1984, Cahners Publishing Co.; permission to reprint is gratefully acknowledged.

# Liquid-crystal displays for automotive applications

#### E. LOWARD and P. STREIT

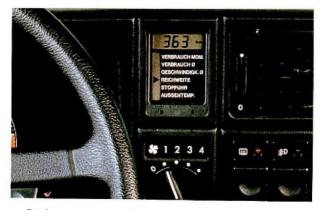

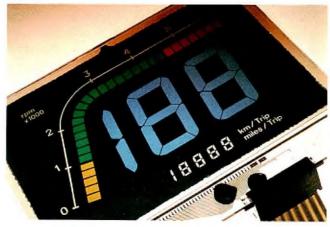

The LCD is no stranger to the car dashboard. These days you'll find it in displays for the clock, for the radio and for the trip computer (Figs.1 to 3), as well as for many other auxiliary functions that are rapidly becoming regarded as essential features of the modern car. You don't have to look far to find the reasons for this current popularity. Low operating voltage and power consumption are probably the principal ones, and you can also add its small size, low cost and outstanding design flexibility, all of which make it extremely attractive to the dashboard designer. And provided some simple operating rules are adhered to, legibility is extremely good. Finally, there's its straightforward drive circuitry which is fully compatible with the digital output signals generated by the auxiliary functions within the dashboard.

At present, small displays for auxiliary functions in the car are generally designed for positive contrast viewing mode, i.e. with black segments on a bright background. These are mounted so that they can operate by reflection during bright daylight, and they have rear illumination (operating in what's known as the transflective mode) or indirect front lighting for low-light-level and night-time viewing.

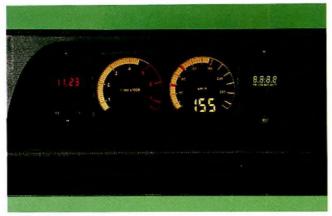

A car cockpit, however, is a rather special environment in which both ergonomics and styling play important roles (Fig.4). In the latter respect, there's little doubt that current styling is strongly influenced by the conventional 'mechanical' dashboard, so to gain acceptance, a modern 'electronic' dashboard must exhibit its information with bright, partly-coloured symbols on a dark background. For the LCD this means operating in what's known as the transmissive mode in reverse contrast with permanent backlighting and intermediate colour filters. We'll refer to this mode as the 'quasi-active' mode since it leads to an appearance directly comparable to that of active displays like the LED, VFD (vacuum fluorescent display) or ELD (electro-luminiscent display).

Fig.1 Philips car radio model AC930 with Videlec LCD

Fig.2 Trip computer (Bosch) with Videlec LCD (Opel)

Fig.3 Clock module (Borg) with Videlec LCD (BMW4 series)

Fig.4 Display module from RT-Philips for radio/clock/temperature (Renault R25) with Videlec LCD

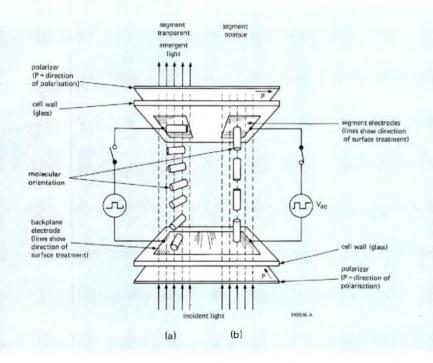

Fig.5 Principle of operation of TN-LCD (positive contrast mode). In the OFF-state (a), the plane of polarization is rotated 90°. In the ON-state (b), the plane of polarization is not rotated.

#### OPTIMIZING THE LCD FOR QUASI-ACTIVE OPERATION

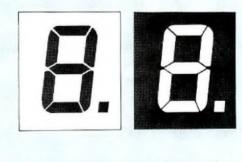

By far the most commonly used liquid-crystal technology and the most promising for today's automotive industry is the twisted nematic (TN) type (Ref.1). The optical property of the liquid-crystal layer of such a display can be roughly characterized by the property that in the OFF state, the plane of polarization of linearly polarized light is rotated by 90°, whereas in the ON state (i.e. with an electric field applied normal to the liquid-crystal layer), the plane of polarization is not rotated (Fig.5). With the liquid-crystal layer between two polarizers rotated 90° to each other, the non-energized zones will be transparent and the energized one will be dark. If the polarizers are aligned, the picture will be reversed, showing transparent segments on a dark background (Fig.6).

Fig.6 Positive and reverse contrast mode

So at first sight, it would appear to be a simple matter to transform a standard positive TN-LCD into a reversecontrast one – simply rotate one polarizer through  $90^{\circ}$  and you'll get complete reversal of the display. Unfortunatelyit's not that simple and some important factors have to be considered when operating in reverse-contrast mode.

To understand this, it's necessary to introduce a basic figure of merit for displays: the *contrast ratio*  $C_r$ , defined as the ratio of light intensity between light and dark areas, i.e.  $C_r = (I_{bright})/(I_{dark})$ .

For good legibility, i.e. high  $C_r$ ,  $I_{bright}$  must be very much greater than  $I_{dark}$ .  $C_r$  will then, of course, be much more sensitive to variations of  $I_{dark}$  than to variations of  $I_{bright}$  (Fig.7), so it's very important to know how  $I_{dark}$ varies with cell homogeneity, driving conditions and polarizer quality.

For a standard TN-LCD with crossed polarizers and dark information on a light background,  $I_{dark}$  is the residual transmission of the energized segments, and its value is determined principally by the drive voltage and by the polarizer efficiency. For optimum contrast with standard TN-LCDs, you need a drive voltage close to saturation and good polarizers.

Ibright (constant)

Fig.7 Contrast ratio dependence on light intensities {|bright/ldark}

For a TN-LCD with reversed contrast,  $I_{dark}$  is the residual transmission of the background in its quiescent (inactive) state. This is independent of driving conditions and is influenced mainly by the optical quality of the cell and by its rotational characteristics, i.e. the way it transmits polarized light.

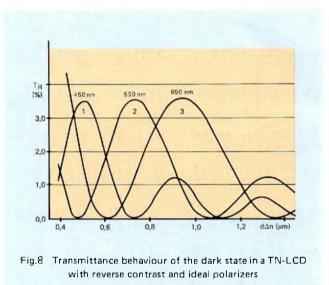

Specifically, the anisotropic nature of the liquid-crystal material means that any liquid-crystal cell of finite thickness will turn linearly-polarized light into elliptically-polarized light. The degree of ellipticity depends on the wavelength  $\lambda$ , cell thickness d and birefingence  $\Delta n$  of the liquid-crystal material. The quantity  $d\Delta n$  is known as the optical thickness of the display, and for any given wavelength, certain discrete values of  $d\Delta n$  lead to zero ellipticity (Fig.8). For white light there's no perfect solution and ellipticity essentially decreases with increasing  $d\Delta n$ . This shows itself as light leakage in the dark zones of the display and hence reduced contrast.

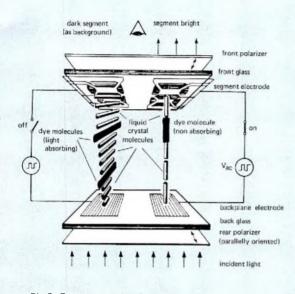

There are various ways of reducing this light leakage (see Ref.2). You can, for instance, increase d or  $\Delta n$ , or reduce the angle of twist of the cell. None of these methods, however, are without drawbacks. A far better solution, and one which we use in our displays, is the use of *pleochroic dyes*.

#### Using pleochroic dyes to reduce light leakage

A pleochroic dye consists of rod like molecules that align with the liquid-crystal molecules. The dye essentially has no effect on light propagating parallel to its molecular axis, but it will strongly absorb light of a given wavelength propagating perpendicular to the molecular axis if this axis also lies in the plane of polarization. So when the liquidcrystal cell is in the ON state, the liquid-crystal and dye molecules are aligned parallel to the propagation direction (right side of Fig.9) and the dye has practically no effect.

Fig.9 Reverse contrast TN-LCD with dye admixture: principle of operation

When the cell is in the OFF state, the liquid-crystal and dye molecules are aligned perpendicular to the propagation direction (left side of Fig.9) and the dye effectively forms a supplementary absorption system.

So by choosing the appropriate dye, the light leakage in the dark zones (which is wavelength dependent) can be suppressed. The dye can also be used to suppress disturbing rainbow effects caused by variations in light leakage due to small differences in cell thickness.

A further problem with reverse-contrast TN-LCDs is that the choice of operating voltage is far more critical than it is for positive contrast displays, and to avoid OFF-segment visibility (at least for low multiplex rates), it should be between 200 and 500 mV lower. However, it's safe to say that all measures taken to reduce leakage into the dark zones of a reverse-contrast TN-LCD will also reduce OFF-segment visibility.

So the above approach, using optimized liquid-crystal materials with pleochroic dyes has led to reverse-contrast quasi-active LCDs with high contrast ratio and extremely low leakage, permitting the use of LCD panels with uniform appearance without need of a black mask.

#### COLOURED TN DISPLAYS

Colour can be introduced into TN-LCDs in three ways: with colour-selective polarizers, colour filters or coloured back-lighting. Colour-selective polarizers produce coloured segments on a bright background (or vice versa). Colour filters and coloured backlighting are basically the same, each being used to best advantage with reverse-contrast LCDs.

We expect the second (i.e. colour filters) to become the most popular with reverse-contrast LCDs. This will probably be realized either by separate mechanical filters behind the display, or better still, by printing translucent colours on the display itself.

Figure 10 shows a prototype reverse-contrast LCD with printed coloured segments. To guarantee good legibility for all illumination levels from darkness to direct sunlight, new transflector materials will have to be developed with a higher transmission coefficient than those of current materials (which are optimized for operation in the reflective mode only).

Fig.10 Reverse contrast prototype LCD with printed colour fields

### DRIVING MODE – CONNECTIONS AND DRIVER INTEGRATION

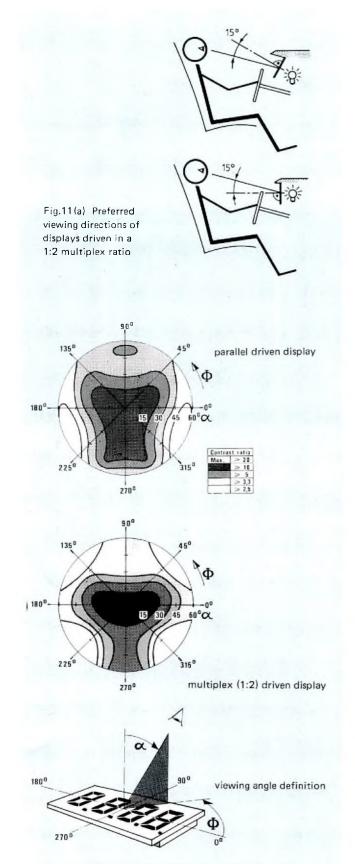

For multiplexed LCDs, the OFF-segment visibility imposes constraints on operating voltage, reducing the viewing angle and changing the viewing cone symmetry. In a car, however, the main requirement is for a wide horizontal viewing angle (the vertical viewing angle being relatively unimportant), and a multiplex ratio of 1:2 is generally considered quite satisfactory. For auxiliary features, however, in driver information systems, for example, higher multiplex ratios will be necessary. It's advisable to incline the cell normal slightly relative to the principal viewing direction (Fig.11), say around  $\pm 15^{\circ}$ .

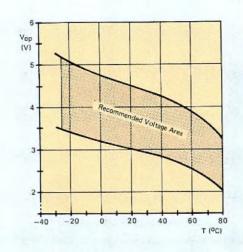

For optimum contrast and to keep the OFF segments invisible, the operating voltage  $V_{\rm OP}$  must be chosen so that the OFF voltage is just below the threshold voltage  $V_{\rm th}$  (the voltage at which contrast first appears). Too high an operating voltage causes the OFF segments to become visible, too low a voltage reduces contrast. Figure 12 shows the recommended voltage area for a multiplex ratio of 1:2.

Since the threshold voltage has a negative temperature coefficient, compensation will probably be necessary to allow operation over the wide temperature ranges likely to be encountered in motor vehicles. For this, specialized integrated circuits are becoming available.

Fig.11(b) Isocontrast diagram for TN-LCD

Fig.12 Recommended voltage for driving a MUX 1:2 TN LCD. Off segments visible at  $\alpha > 40^{\circ}$  and  $\phi = 270^{\circ}$ . Typical contrast ratio < 2,5 at  $\alpha = 0^{\circ}$

#### VIDELEC INTEGRATED DISPLAY (VID)®

An important benefit of the 1:2 multiplex mode is that it almost halves the number of connections to the display (compared with a directly-driven display) – important for system reliability. However, for large dashboard display systems with quite high information density, contacting still remains a major problem, and the best solution will undoubtedly be to integrate the driver onto the glass.

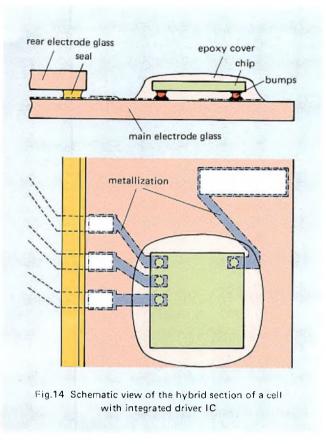

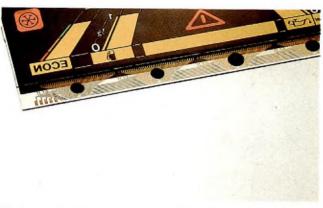

For this, Videlec now has available a new chip-on-glass technology in which the driver IC is bonded directly to the glass of the LCD. Only general-purpose drivers are integrated onto the glass to allow the display system to interface directly with an external controller (Fig.13). The driver is bonded in what's known as 'flip-chip geometry' (with the chip face down on the contact pads, Figs 14 and 15) requiring the smallest amount of extra glass for the hybrid section.

Fig.13 Prototype Videlec integrated display (VID) with chip-onglass and printed translucent colours, the LCD is driven in a multiplex 1:2 mode

The manufacturing process fits well into standard LCD technology and is partly implemented in batch production (Refs 4 and 5). Some of the advantages offered by this new chip-on-glass technology are:

- shorter connections between segments and driver output

- lower stresses induced in the glass during bonding

Fig.15 Detail of custom-designed Videlec integrated display (VID) showing the cascade of driver ICs (PCF8576)

- compact bond geometry for good thermal matching, giving high immunity to thermal cycling and thermal shocks

- excellent humidity resistance and complete immunity to light penetration.

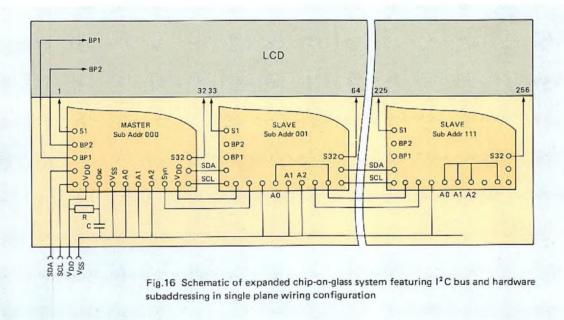

The principal constraint of this new technology is that it's limited to single-plane wiring configurations and chip layouts. This presents no problem, however, with Videlec's new general-purpose PCF8576 driver IC (see the Table and Fig.16) which allows for chip cascading in single-plane configurations. The PCF8576 is equipped with a standard serial-bus ( $I^2C$ ) interface and hardware sub-addressing. It's programmable in driving mode from direct to multiplex 1:4, and it can handle complicated display systems with up to 16 chips on the bus (with five external contacts on each display element).

Fig.17 Example (work prototype) of a dashboard combination

### Features – PCF8576 universal LCD driver for low multiplex rates

- Single chip controller/driver

- Selectable drive configuration: direct, MUX 1:2, 1:3, 1:4

- Selectable driving method: 2-, 3-, 4-level

- 40 segment lines (up to 160 elements)

- I<sup>2</sup>C bus interface, compatible with any 4-, 8-, 16-bit microprocessor

- 2 V to 9 V power supply range

- Separate LCD and logic supplies possible

- Power saving mode available

- 40 × 4 bit RAM for display data storage

- Auto-increment addressing and hardware subaddressing

- Versatile blinking capabilities (selected segments or whole display)

- Cascadable with up to 16 drivers (max. 2560 elements)

- Optimized for single plane wiring

- Compatible with Videlee chip-on-glass technology

- Very low external component count (at most one resistor)

- Space-saving 56 lead VSO-56 package

Finally, 5 to 8 contacts for supply lines and serial bus will still be necessary, but in a dashboard, there'll be more than enough space for a plug or clip-on arrangement. And since only one small connector will then provide access to the display system, mounting of the display will be independent of its electrical connections, an evident advantage in an environment subject to considerable vibration.

#### ACKNOWLEDGEMENT

The authors are indebted to Dr. M. de Zwart for his help in preparing this article.

#### REFERENCES

- 1. A. SCHELLING: "Liquid Crystal Displays". Videlec publication, reprinted from Electronic Components and Applications, Vol. 5, No. 4, Sept. 1983, pp. 233 to 244.

- 2. Dr. M. DE ZWART: "Contrast improvement in TN-LCDs operating in the negative-contrast mode". Paper presented at Electronics Displays '84, Nov. 28th 1984, London, reprint available from Videlec.

- Dr. H. U. BEYELER: "Liquid Crystal automotive displays; present possibilities, future technology trends". Paper given at S.A.E. conference, Boston, May 1982; reprint available from Videlec.

- 4. Dr. P. STREIT: "Integration of driver IC onto Liquid Crystal Displays". Paper given at S.I.D. International Symposium, Philadelphia, May 1983.

- 5. Dr. P. STREIT: "LCDs with chip on glass (Videlec Integrated Displays)". Paper given at Electronic Displays '83, Nov. 1983, London; reprint available from Videlec.

Videlec, jointly established by BBC Brown Boveri and Philips in 1980 and now completely owned by Philips, specializes in LCD technology to meet the requirements of original equipment manufacturers. Besides a wide range of standard products, Videlec offers a complete service in custom-designed LCDs.

## An integrated approach to CD players Part 1: The optical pick-up

#### J. NIJHOF

A much-publicised advantage of the Compact Disc (CD) system is its high level of immunity to dust, fingerprints and scratches on the compact discs. To this list can be added its immunity to (within-specification) disc defects such as pinholes and track eccentricity introduced by the pressing equipment. Less-publicised, but even more important, are the marked differences in the ability of individual players to handle these defects and, in addition, the knocks, vibration and g-forces experienced in cars.

This article and Part 2 will describe some of the novel aspects of our new ICs and optical pick-up that can be used to manufacture players that will play mishandled discs under adverse conditions without producing any detectable sound colouration. Benefits for the player manufacturer include

- simple designs (few ICs with virtually no external components),

- flexible designs owing to the use of a standardized inter-IC digital audio bus,

- designs that can be upgraded to accommodate future trends in digital signal processing.

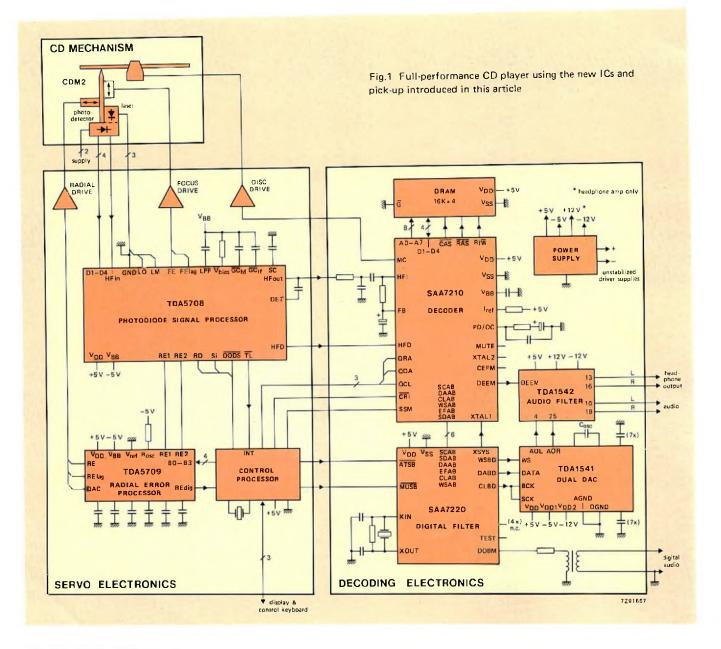

A full-performance player using the new ICs is shown in Fig.1. All player functions are integrated in the new chip set, reducing the cost of a player's electronics significantly. Furthermore, no factory adjustment of players is necessary. Two servo ICs, with automatic gain and offset correction, control the pick-up, and a single decoder chip incorporates the demodulator PLL and VCO, error corrector and a basic concealment function for uncorrectable audio data. For full-performance players, an additional chip containing a digital oversampling filter and an enhanced concealment function is available. The chip set is completed by a dual 16-bit DAC for maximum fidelity and an integrated analog filter with outputs for an audio amplifier and for a head-phone.

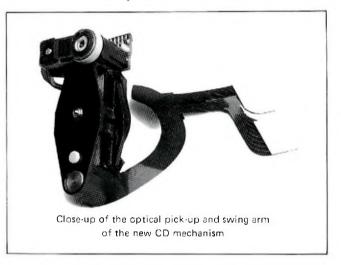

The new CD mechanism (CDM2) comprising pick-up, swing arm and disc drive motor. Just 30 mm high and with an operating temperature range of -30 to +75°C, the mechanism is suitable for home, car and portable players. The size reduction has been achieved, without the need to resort to folded optics, by using a new optical arrangement that requires only four components.

#### **CD OPTICAL PICK-UPS**

Before we describe the CDM2 pick-up\*, it will be useful to summarize the stringent requirements to be met by a pickup servo-system, and to review the pick-ups in current use.

The function of the optical pick-up of a CD player is to generate a high-quality r.f. signal (eye pattern) for the player's demodulator from a disc's pit/land transitions which contain the audio data, track number, title, etc. To generate an eye pattern from which all the data on the disc can be retrieved, the laser spot should follow the centre of the  $0,6\,\mu\text{m}$  wide track to within about  $\pm 0,1\,\mu\text{m}$ , with no interference from adjacent tracks *just 1,6\,\mu\text{m} away*. Since the track on the disc may be slightly eccentric due to tolerances in disc pressing equipment, and to handle the effects of vibration, the servo should furthermore be able to accommodate a maximum side-to-side track swing of about  $300\,\mu\text{m}$ . The radial tracking servo system capable of meeting these, already demanding, requirements should in addition be able to absorb the effects of knocks to the player and external vibration.

The requirements for the focusing servo are equally severe. For adequate read-out, the focusing servo has to keep the laser beam focused on the reflecting layer of the disc to within  $\pm 0.5 \,\mu\text{m}$ , even with a maximum disc warp of 1 mm.

Manufacturers use a variety of techniques (with varying success) to generate the error signals for the tracking and focusing servos.

<sup>\*</sup> a product of Philips Consumer Electronics Division.

#### CD2 - SECOND GENERATION CD SYSTEM

CD2 is the first all-integrated system for CD players. CD2 means improved performance for the listener, and simpler more flexible designs for the manufacturer. This additional flexibility stems from a single-chip decoder concept which can be expanded for full-performance designs by adding a digital oversampling filter IC. An analog filter IC can be used to make either a low-order analog filter for a full-performance player or a high-order filter for a low-cost player. Two bipolar ICs provide all the control servo functions for a singlebeam swing arm pick-up. A full-performance player is shown in Fig.1. This player which requires *no factory adjustment* comprises:

#### CD mechanism

CDM2: a smaller version of our swing arm mechanism CDM1 in a tough plastic surround. Height of the CDM2 is 30 mm. Operating temperature range is -30 °C to +75 °C. These features and a very short arm with low moment of inertia make CDM2 suitable for use in portable and car CD players.

#### Servo electronics

TDA5708: bipolar photodiode signal processor

- photodiode signal preamplifiers with separate r.f. and d.c. a.g.c.s for optimum generation of the r.f. data signal and the focusing/tracking error signals

- tracking error signal amplifier

- focusing error signal processor with focus normalising and start-up circuit

- data equalizer

- r.f. level and track-loss detectors

- regulated supply for the reading laser diode

- low current consumption: 15 mA (8 V 14 V).

#### TDA5709: bipolar radial error processor

- tracking error processor with automatic asymmetry control

- a.g.c. circuitry with automatic start-up and wobble generator

- tracking control for fast forward/reverse scan, search, repeat and pause functions

- low current consumption: 10 mA (8 V 14 V).

#### **Decoding electronics**

The decoder comprises three ICs compared with the six ICs of our previous decoder. In addition, an IC is available for constructing a variety of low-pass analog filters.

SAA7220: NMOS digital filter with enhanced concealment of uncorrectable errors

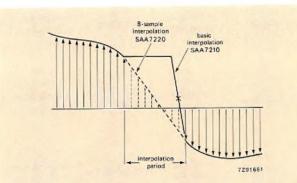

- two identical phase-linear digital FIR filters with 120 filter coefficients

- four times oversampling

- linear interpolation of up to 8 consecutive erroneous samples

- I<sup>2</sup>S data I/O for compatibility with future sound processors

- integrated digital audio output according to the Philips-Sony proposal

- soft mute of audio when starting, stopping or pausing

- 12 dB attenuated audio facility when scanning.

#### TDA1541: bipolar dual 16-bit DAC

- two separate DACS on one chip (no multiplexing, so no delay between the stereo channels)

- operates at bit rates up to 6 Mbits/s for use with four times oversampled data in the CD system

- programmable for offset binary or two's complement signals

- J<sup>2</sup>S input format

- 1 μs (typ.) settling time to ±1 LSB.

#### TDA1542: bipolar dual analog output IC

- can be used to make a low-order analog filter for a fullperformance player with digital filtering, or a high-order filter for a low-cost player using a single-chip (SAA7210) decoder

- two identical circuits for stereo applications

- incorporates de-emphasis switch and silent switch-on/off circuitry

- headphone output.

#### SAA7210: NMOS single-chip decoder

- comprises all decoding functions:

- demodulator with adaptive data slicer

- fully-integrated demodulator PLL

- subcoding data processor

- error corrector with adaptive error-correction strategy

- basic interpolation and sample-and-hold circuit

- improved error correction of up to a 15-frame burst error

- large (64-frame) FIFO storage for portable and car player applications

- I<sup>2</sup>S (inter-IC signal) data output.

#### Tracking

Four basic techniques are available for generating a radial tracking error signal:

- single-beam push-pull tracking

- single-beam differential phase detection (DPD) or heterodyne tracking

- single-beam h.f. wobble tracking

- three-beam tracking (using two auxiliary beams to generate the error signal).

#### Focusing

Three basic techniques are available for generating a focus signal:

- astigmatic (cylindrical lens) focusing

- Foucault (knife edge) focusing

- critical angle focusing.

The three most popular tracking-focusing combinations found in CD pick-ups are:

- single-beam push-pull tracking with Foucault focusing (a design of Philips Audio Division)

- three-beam tracking with astigmatic focusing

- DPD with critical angle focusing.

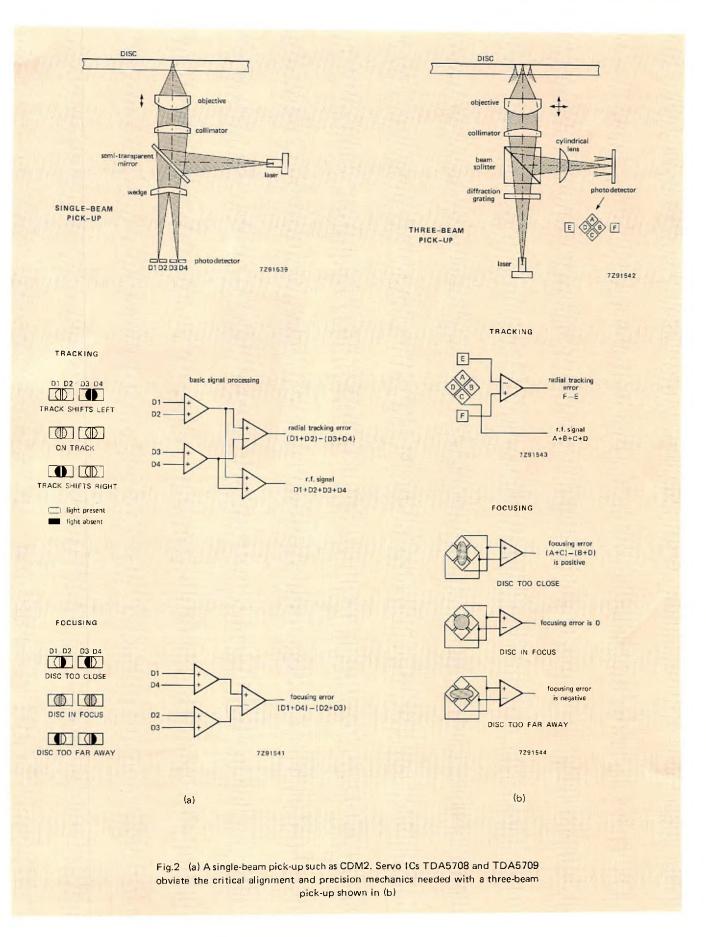

The first two are in common use and are shown in Fig.2. CDM2 uses a version of the first combination with a low-frequency wobble injected onto the radial error signal for optimum tracking. The pick-up is mounted in a swing arm which describes an arc across the disc during playback. In contrast, a three-beam pick-up is usually mounted in a sled capable of movement along a disc radius. A single-beam pick-up can also be mounted in a sled-driven system; a 3-beam pick-up on the other hand won't work in the swing arm since the three beams have to be aligned and maintained in a fixed position relative to the track. Table 1 shows the relative merits of CDM2 and a typical three-beam pick-up. Table 2 gives brief data on CDM2.

|                                            | CDM2                                                                                                          | typical three-beam pick-up                                                                                                                                                                                                                                                             |

|--------------------------------------------|---------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| mechanics                                  | simple – just one moving part                                                                                 | complex, two-stage radial movement<br>using a lead screw. A moveable mirror is<br>often used to deflect the reading beam<br>quickly over small distances to handle<br>track eccentricity                                                                                               |

| optics                                     | 4 components:<br>objective (single aspherical lens)<br>collimator,<br>wedge,<br>fixed semi-transparent mirror | at least 5 components:<br>objective,<br>collimator,<br>grating (with adjustment)<br>cylindrical lens<br>beam splitter                                                                                                                                                                  |

|                                            | only one adjustment needed during player<br>assembly – horizontal position of the<br>photodetector            | several critical alignments needed during<br>player assembly including the alignment<br>of the beams used to generate the radial<br>error signal                                                                                                                                       |

| focusing                                   | Foucault; objective moved by a coil/<br>magnet combination                                                    | astigmatic: objective moved by a coil/<br>magnet combination                                                                                                                                                                                                                           |

| interference in the radial<br>error signal | virtually none – all signals derived from a single spot on the disc                                           | the l.f. components of the eight-to-<br>fourteen modulation used in the CD<br>system create interference with a 3-beam<br>pick up. Not relevant when playing video<br>discs there being no l.f. components in<br>the modulation (Philips Laservision<br>players have a 3-beam pick-up) |

| shock tolerance                            | good <sup>1</sup> )                                                                                           | good                                                                                                                                                                                                                                                                                   |

| electronics                                | depends on the playability required <sup>2</sup> )                                                            | depends on the playability required <sup>2</sup> )                                                                                                                                                                                                                                     |

TABLE 1

Comparison of the CDM2 single-beam/swing arm pick-up and a three-beam/sled pick-up

1) a swing arm is more immune to the translational forces associated with everyday bumps.

<sup>2</sup>) playability is the ability of a CD player to reproduce the original recorded sound under adverse playing conditions (scratched discs, moving player etc.) without interrupting the audio output, see panel.

#### PLAYABILITY

Standard test discs are available to all licensees and distributors of the Compact Disc digital audio system. These discs readily expose weaknesses in the design of a CD player by testing a player's ability to tolerate small defects in a disc without producing audible clicks or pauses in the reproduced sound (playability).

On the surface of each disc are a series of opaque dots which represents dust and dirt, a simulated fingerprint, and gaps in the recorded track which simulate minor imperfections in the pit pattern. A player's ability to handle these artifical defects is a good measure of its ability to cope with real production defects such as air bubbles, pin-holes, enclosures and scratches.

#### Test disc '4A'

| test        | details                                                                                                  | requirement of the CD<br>system specification             |

|-------------|----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|

| fingerprint | a simulated fingerprint<br>that reduces the light<br>reflected onto the<br>photodiodes in the<br>pick-up | should produce no<br>audible distortion                   |

| stain       | a series of opaque dots<br>with diameters of 300,<br>500, 600 and 800 μm                                 | the 300 µm dot should<br>produce no audible<br>distortion |

| wedge       | 400 μm to 900 μm gaps<br>in the recorded pit<br>pattern                                                  | the 400 µm gap should<br>produce no audible<br>distortion |

| TABLE 2Brief data on the CDM2 | mechanism     |

|-------------------------------|---------------|

| length                        | 130 mm        |

| width                         | 100 mm        |

| height                        | 30 mm         |

| weight                        | 325 g         |

| operating temperature range   | -30 to +75 °C |

| supplies                      |               |

| laser                         | 55 mA typ     |

| radial drive                  | 30 mA typ     |

| focus drive                   | 25 mA typ     |

| disc drive                    | 30 mA typ     |

| objective                     |               |

| numerical aperture            | 0,46          |

#### CDM2 PICK-UP

#### Mechanics

The pick-up is mounted at the end of a low-inertia balanced arm pivoted at its centre. A coil housed in the arm, see photo, and a permanent magnet attached to the chassis form a linear motor used both to track and to fast-feed the pickup across the disc. When the motor is energised, the pick-up can be directed quickly to any track (<1 s from inner to outer track), and can follow the centre of the track accurately to within 0,1  $\mu$ m. Large track eccentricities can be followed because there is no vignetting (the whole pick-up moves, not only an objective as in a three-beam pick-up). Since there is only one moving part (the arm pivot), the mechanism is extremely reliable and wear is minimal.

For comparison, it will be useful to say a few additional words about a three-beam pick-up. A three-beam pick-up needs a linear movement. A disc is tracked by moving the pick-up objective along a radius of the disc. Often, a moveable mirror is inserted in the optical path to deflect the laser beam quickly over small distances, to handle track eccentricity for example. Two auxiliary beams are used to generate a tracking error signal. Alignment of these beams is critical, and the sled carrying the pick-up and the lead screw and guide all have to be precision components. Any misalignment of the auxiliary beams during the life of the player will impair tracking. Fast-feeding is done by moving the complete optical assembly radially across the disc, for example, by means of a lead screw. The thread of the leadscrew is always a compromise between the fine thread required for normal tracking during playback (35 mm per hour to take up the tracking movement) and the coarse thread required for fast feed (35 mm in 1 second, say).

#### Optics

A feature of the CDM2 pick-up is its simple diffractionlimited optics. The laser point source is focused on the information layer of the disc by two lenses: a spherical glass objective with a plastic aspherical skin, and a sperical glass collimator (most CD pick-ups, including our own CDM1, use a three-element objective and a two-element collimator). The thin plastic skin of the objective is attached using a proprietary process (Ref.1). Owing to the glass body, the objective is stable in humid conditions and temperatures up to 85  $^{\circ}$ C, while the aspherical skin provides the desired aberration-free optical performance.

The low-profile optics of CDM2 has been obtained by interchanging the positions of the laser and photodetector used in our previous pick-up (Fig.2(a) and Ref.2). Furthermore, an inexpensive semi-transparent mirror is used instead of a beam-splitter cube. Astigmatism introduced into the reflected beam by the mirror is corrected by a plastic component (the wedge, in Fig.2(a)) which also dissects the beam into the two halves from which the tracking and focusing error signals are generated.

One could ask, why not use the reflected astigmatic beam to generate the error signals directly (i.e. astigmatic focusing in combination with push-pull tracking)? Our experience indicates that the error signals generated in this way are noisier than with Foucault focusing/push-pull tracking.

#### Virtually no interference in the radial error signal

The CDM2 pick-up derives the tracking error, the focusing error and the audio signals from one spot on the disc. Compared with a three-beam pick-up, this has two advantages:

- virtually no interference from the r.f. signal in the radial error signal

- allows lower mechanical tolerances in the pick-up, giving long-term optimum tracking with no adjustment of the radial error signals needed.

#### Shock tolerance

The tracking servo-system for CDM2 is optimised to handle disc defects and the effects of vibration. The latter can be reduced further by mounting the CDM2 mechanism in a well-designed floating suspension. This suspension should have the characteristics given in Table 3 with progressive damping for large-amplitude shocks.

| TABLE 3Recommended characteristics of a suspensionfor CDM2 |               |           |  |  |  |

|------------------------------------------------------------|---------------|-----------|--|--|--|

| Resonant frequ                                             | ency          | zt        |  |  |  |

| x axis                                                     | 25 ± 4 Hz     | - 14      |  |  |  |

| y axis                                                     | $25 \pm 4$ Hz | 100/00    |  |  |  |

| z axis                                                     | 25 ± 4 Hz     |           |  |  |  |

| Φ                                                          | 45 ± 4 Hz     | 75        |  |  |  |

| Q damping                                                  | 5             | 7Z91549 Ø |  |  |  |

#### Electronics

Some aspects of the decoding electronics are described in Part 2.

#### REFERENCES

- BRAAT, J. J. M., 'Aspherics', Philips Technical Review, Vol. 41, No. 10, 1983, p. 258.

- CARASSO, M. G., PEEK, J. B. H. and SINJOU, J. P., The Compact Disc Digital Audio System, Philips Technical Review Vol. 40, No. 6, 1982, pp. 151 to 155.

#### ACKNOWLEDGEMENTS

- 1. This article is based on an article that appeared in Japanese in the December 1984 issue of Audio, Video, Electronics and Record, Tokyo, Japan; permission to publish is gratefully acknowledged.

- 2. The author wishes to acknowledge the assistance given while preparing this article. Particular thanks are due to colleagues at the Compact Disc Laboratory, Philips Consumer Electronics Division and at Philips Research Laboratories, Eindhoven.

## An integrated approach to CD players Part 2: The decoding electronics

#### J. NIJHOF

In Part 1, we introduced a new single-beam optical pick-up and servo ICs for Compact Disc (CD) players, the advanced designs of which allow the manufacture of small players that can handle disc defects such as scratches, pin holes and track eccentricity, as well as the knocks, vibration and g-forces encountered in portable systems. Hand in hand with this advance come exciting developments in the signal-processing circuitry. Developments that, among other things, allow full advantage to be taken of the error-correction capability of the CD system, to produce high-performance players with no detectable sound colouration.

This article describes some of these new developments, in particular the integrated CD decoder. The decoder requires no adjustment and is suitable for all CD players – those with a single-beam pick-up and those with a threebeam pick-up. Besides the audio application, the decoder can be used in many other applications requiring a highperformance high-reliability Reed-Solomon decoder, e.g. CD ROM.

Supporting the decoder IC, several circuits have been developed to facilitate the manufacture of players with:

- fewer ICs and fewer peripheral components

- greater design flexibility

- improved sound reproduction.

Such a player is shown in Fig.1.

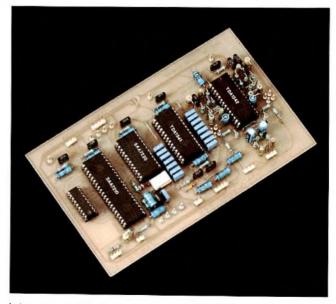

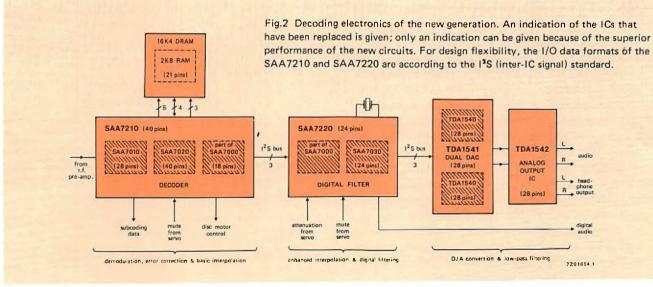

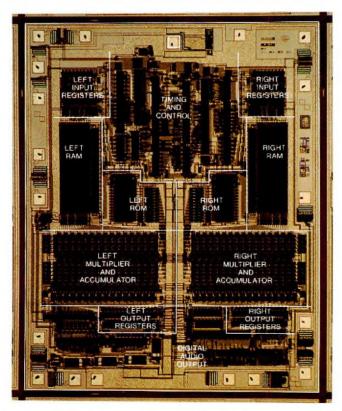

Figure 2 shows the new decoding electronics and the six ICs (shaded) it replaces (Ref.1). The SAA7210 decoder IC incorporates the functions of demodulation, error correction and basic interpolation. The SAA7220 digital filter IC incorporates enhanced interpolation circuitry and a phase-linear digital FIR filter. A dual 16-bit DAC TDA1541 (operating at 176,4 kHz) followed by a stereo analog output

IC TDA1542 replaces two DACs and two discrete analog filters.

The data format between the SAA7210, the SAA7220 and the TDA1541 is according to the  $I^2S$  (inter-IC signal) specification\*, giving the player manufacturer maximum design flexibility. This would allow the SAA7220 to be omitted in Fig.2, for low-cost players, leaving the manufacturer free to design his own low-pass filter.

\* Inter-IC signal (I<sup>2</sup>S) communication is a communication format for digital audio. The I<sup>2</sup>S bus is a three-line bus comprising: clock, serial data line, and a control line used to select left and right channel words.

Laboratory model of the new high-performance decoding electronics for CD players

#### requiring a balanced differential filter, varicap diode, coil, resistors and capacitors

#### FEATURES OF THE NEW DECODER

#### Further integration of the demodulator PLL

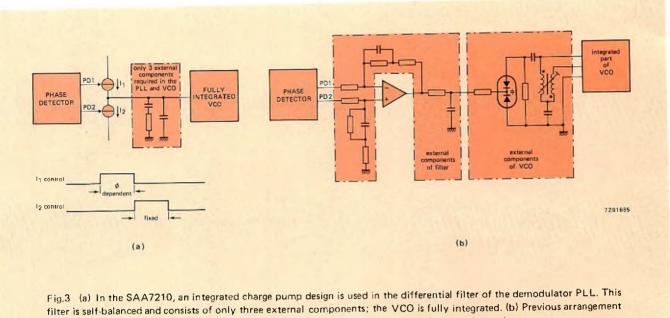

A feature of the SAA7210's demodulator PLL is that it requires virtually no peripheral components. The VCO is a fully-integrated RC oscillator; it requires no peripheral components. The differential filtering circuitry of the PLL uses a self-balancing charge pump design that requires only one filter comprising just three low-tolerance components (Fig.3).

#### More efficient processing of subcoding data

Besides the audio information recorded on a compact disc, information representing track numbers, playing times, titles and composers is recorded so that tracks can be played in any desired sequence and titles and elapsed playing times etc. can be displayed. This information, termed Q-channel subcoding data, is derived continually in the SAA7210 from the demodulated r.f. signal. A new handshaking protocol between the SAA7210 and control processor reduces the time the control processor spends handling subcoding data. When the processor wants data, a request is sent (via QRA, see Fig.1) to the SAA7210 which, when a full Q-channel frame is ready, acknowledges the request and enables the serial data output QDA. The processor sends a clock signal (QCL) to shift the data out of the SAA7210.

The first negative-going edge of the clock signal resets the acknowledge signal thereby releasing the request line. If the processor doesn't require all the subcoding data, say only the number of a track (contained in the first sixteen bits), it can reset the request line after these bits have been received, thereby disabling the QDA output of the SAA7210 which resumes collecting new subcoding data.

#### Adaptive error-correction

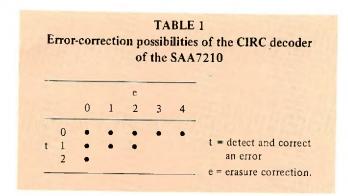

Until now, no CD player has made full use of the errorcorrecting capability of the CD system's Cross-Interleaved Reed-Solomon Code (CIRC). This code enables up to four erroneous symbols\* (in a 32-symbol block) to be corrected if the CIRC decoder is given prior information about the position of the errors. This type of correction, where the position of an error is known, is called an erasure correction. When the positions of errors are unknown, up to two erroneous symbols can be corrected. A decoder with the maximum error-correction capability (like that of the SAA7210) can make the corrections shown in Table 1.

For optimum error-correction, only the following corrections of Table 1 are relevant:

- t = 2 look for and correct two errors, positions unknown

- e = 1, t = 1 make one erasure correction, and look for and correct one additional error

- e = 2, t = 1 make two erasure corrections, and look for and correct one additional error

- e = 3 make three erasure corrections

- e = 4 make four erasure corrections.

A new approach to error-correction in the SAA7210 known as adaptive error-correction discriminates between the errors found on a compact disc. This discrimination:

- enables more corrections to be made (e.g. longer burst 'errors)

- makes the corrections more reliable.

- \* 14 bits.

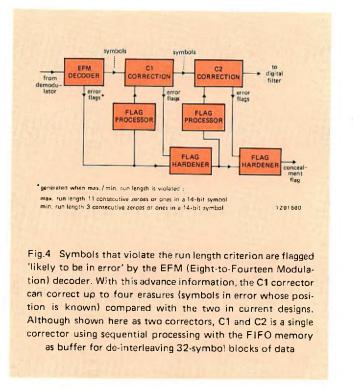

As shown in Fig.4, these improvements are achieved by using additional error flags generated by the EFM decoder (using the bit run-length criteria to flag symbols likely to be in error) and by using multi-level error flags generated by the C1 and C2 corrector\*.

With the error flags, several error-correction strategies are available, the strategy chosen depending on the type and number of error flags which are set by the defects on a disc.

To determine the typical defects to be found on a disc, and therefore the strategy for correcting them, special test discs with known data patterns were manufactured on normal production equipment. These discs enabled typical manufacturing defects to be identified. Normal handling defects such as scratches and fingerprints were then introduced on each disc. Extensive testing with these discs demonstrated that the error-correction was significantly improved by using multi-level flags to signal symbols in error, three flags (two bits) being sufficient:

- hard error-flag (most reliable flag)

- medium error-flag

- soft error-flag (least reliable flag).

A no-error flag is indicated by setting both bits to zero.

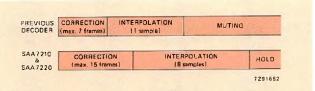

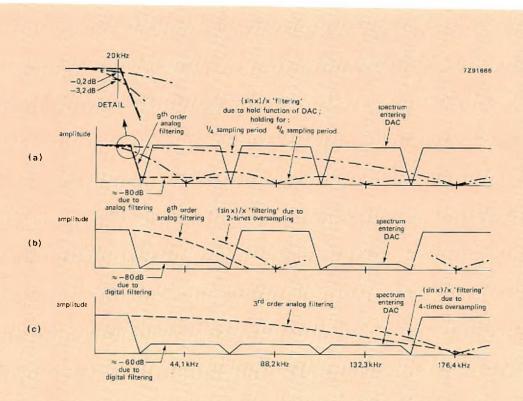

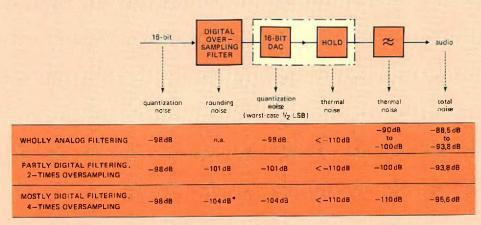

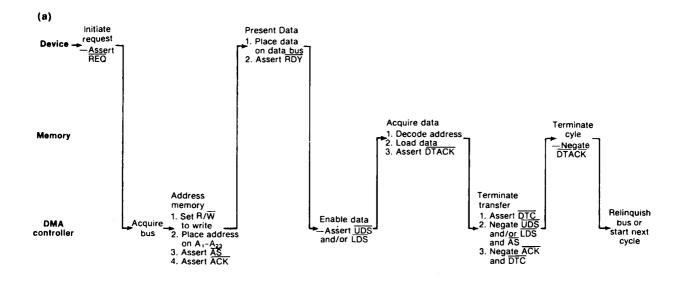

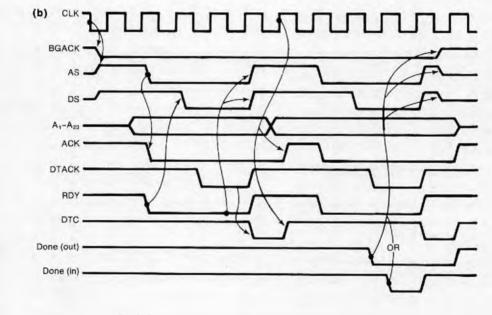

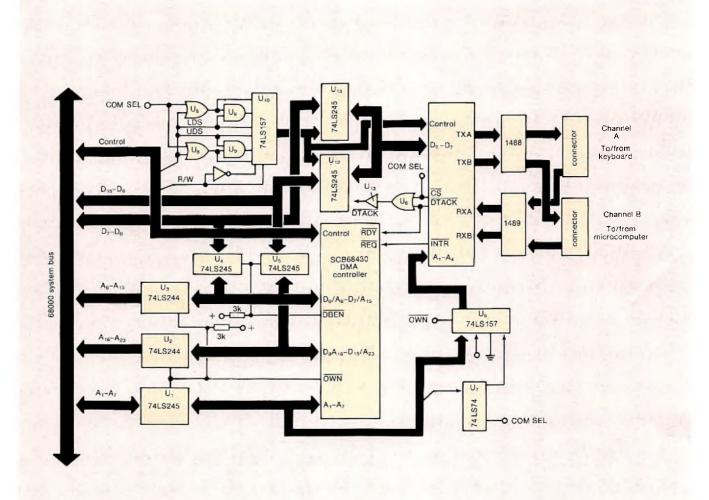

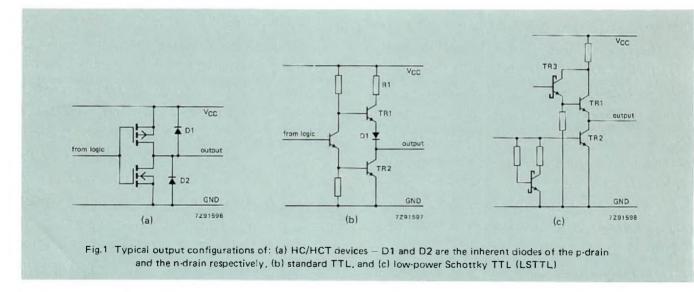

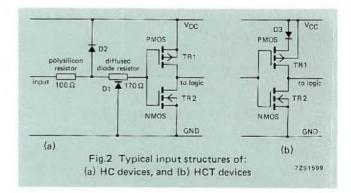

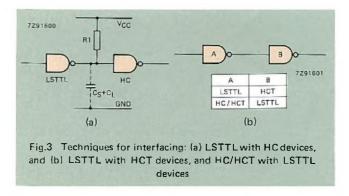

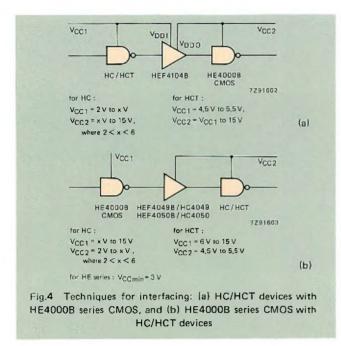

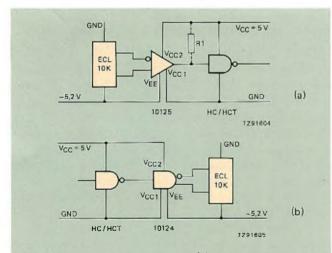

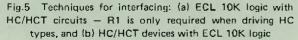

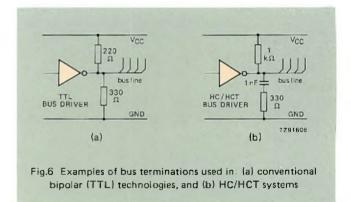

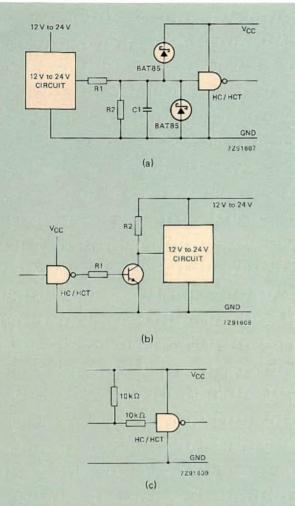

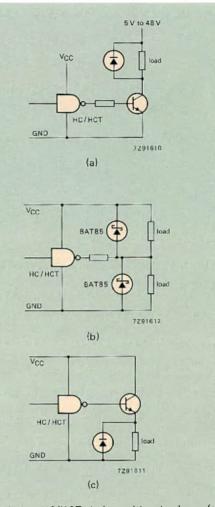

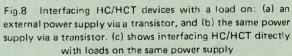

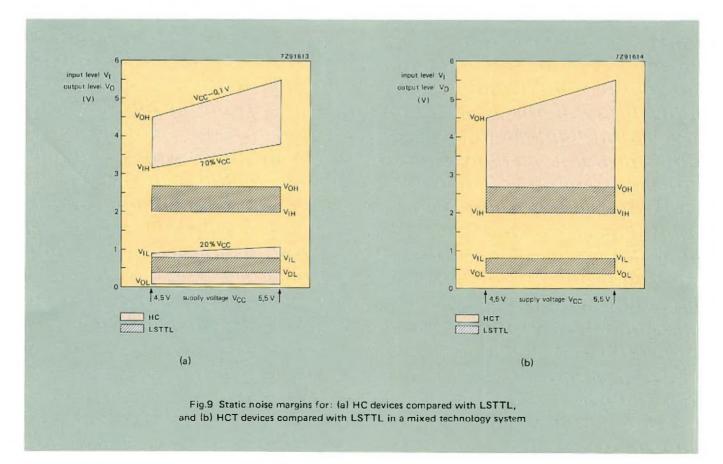

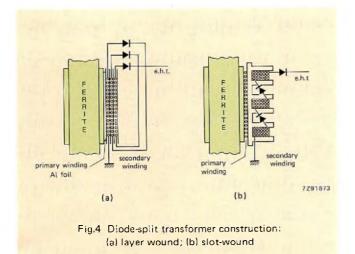

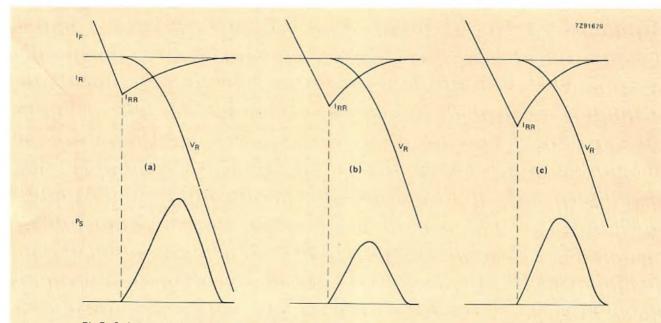

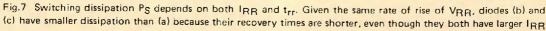

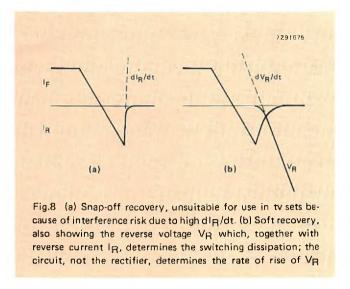

With these flags, the best correction strategy is selected by a flag processor, see Fig.4. For example, when two symbols in a block of thirty-two are flagged with soft errorflags, it is best to attempt a t=2 correction (rather than an e=1 and a t=1, or an e=2, t=1 correction). When two symbols are flagged with hard flags, it is usually better to attempt an e=2 correction and to look for and correct another symbol in error with the remaining t=1 capability. After a correction, the input flags are compared with the new flags produced by the corrector to update (harden) the flags for the next stage of processing. Flag hardening progressively improves the reliability of all flags, so that very reliable e=3 and e=4 corrections can also be made.