# **Electronic components & applications**

## Electronic components & applications

Volume 8, No.1

Editor: Ian L. A. Crick

Design and production: Cees J. M. Gladdines Bernard W. van Reenen Jacob Romeijn

Design consultant: Theo Kentie

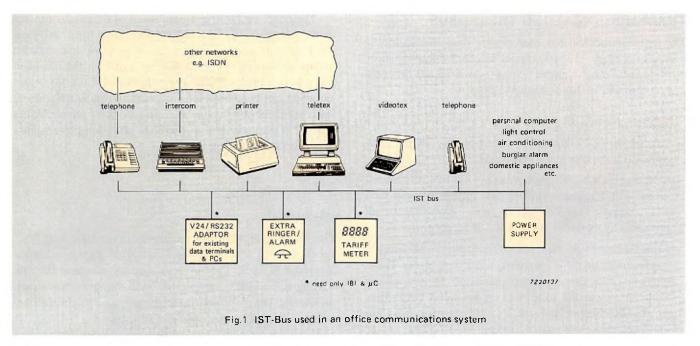

Since the dawn of history, man has striven to improve communication. His first primitive attempts with horns, drums and smoke signals had the major disadvantages of being shortdistance and in code. Not till the invention of the telegraph, about 150 years ago, was a real breakthrough made. Although still in code, telegraphy opened the door for plain language, long-distance communication media such as telephony, radio and more recently, tv and computers. With every success, demands grew so that now the only way existing networks can efficiently handle the enormous volume of information that has become the life-blood of modern society is to go digital. The IST (Integrated Services Terminal) bus described on page 52 allows many benefits of the fullydigital ISDN systems of the future to be enjoyed today. The perfect communication medium may be in sight, but will this really lead to perfect understanding? Or will the legacy of Babel continue to confound us!

### Contents

| High-speed 12-bit tracking ADC using<br>programmable logic sequencers<br>David Wong                                 | 2  |

|---------------------------------------------------------------------------------------------------------------------|----|

| Ceramic-chip capacitors – high-rel products with a<br>promising future<br>W. Langenhorst and R. Waser               | 15 |

| Stereo sound generator for sound effects and music<br>synthesis<br><i>Mike Roberts</i>                              | 21 |

| Harvard architecture pushes microcontroller IC into<br>high-speed realm<br>Greg Goodhue, Jesse Jenkins and Ata Khan | 32 |

| Integrated video programming system (VPS) decoder<br>Axel Lentzer and Günther Stäcker                               | 39 |

| High-temperature electrolytic capacitors<br>Ad Otten and Just Slakhorst                                             | 45 |

| Integrated Services Terminal (IST) Bus –<br>the low-cost LAN and associated interface<br>René Kohlman               | 52 |

| Abstracts                                                                                                           | 62 |

| Authors                                                                                                             | 64 |

All information in Electronic Components and Applications is published in good faith, but the publishers assume no liability for any consequence of its use, its publication does not imply a licence under any patent. Specifications and availability of goods montioned in it are subject to change without notice.

## High-speed 12-bit tracking ADC using field-programmable logic sequencers

#### DAVID WONG

The high-speed 12-bit tracking ADC described in this article is based on two logic sequencers type PLS179 from our bipolar Schottky Programmable Logic Device (PLD) Series-24 (24-pin DIL) Family. These ICs are field-programmed by selective blowing of fusible Nichrome links and interconnected to form a 12-bit Successive Approximation Register (SAR), up/down counter and biphase clock generator. Features of the PLS179 logic sequencer are:

- 45 product terms (32 logic terms, 13 control terms)

- 20 inputs (8 dedicated)

- 4 I/Os and 8 registered I/Os

- typical propagation delay 25 ns (input to output)

- typical power dissipation 725 mW

- maximum clock frequency 18 MHz

- operating temperature range 0 to 75 °C

- encapsulated in 24-pin plastic DIL (PLSI79N or 28-pin PLCC (PLSI79A)

- supported by Automated Map And Zap Equation (AMAZE) PLD design software which is free of charge to PLD users.

Further details of the PLS179 and the AMAZE software are given in the Reference.

#### **OPERATING PRINCIPLES OF THE ADC**

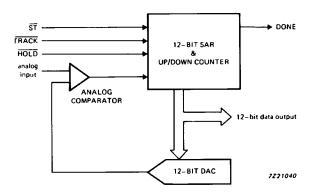

The simplified block diagram in Fig.1 illustrates the principle of operation of the ADC.

When input  $\overline{ST}$  is set LOW, the 12-bit SAR is initially loaded with its half full-scale value ( $2^{11} = 2048$ ) which is

then converted to analog form by a 12-bit DAC. An analog comparator senses whether the output level from the DAC is greater or less than the analog input level and causes the SAR to increment or decrement until parity is achieved by successive approximation. Output DONE is then set HIGH. When output DONE is HIGH, and as long as inputs  $\overline{ST}$  and HOLD are HIGH, a tracking mode of operation is available during which the SAR is converted into a 12-bit up/down counter by setting the TRACK input LOW. The up/down counter is incremented or decremented under control of the COMPARE inputs at the rate of one LSB per clock period to follow the analog input variations. The up/down counting can be halted at any time by setting the HOLD input LOW. The digital data output then remains constant indefinitely. This facility provides a very good sample-and-hold function because, unlike with analog sample-and-hold circuits using capacitor storage, the output level doesn't decay due to charge leakage.

Fig.1 Simplified block diagram of the 12-bit high-speed ADC.

#### DETAILED DESCRIPTION OF THE ADC

#### Successive approximation register

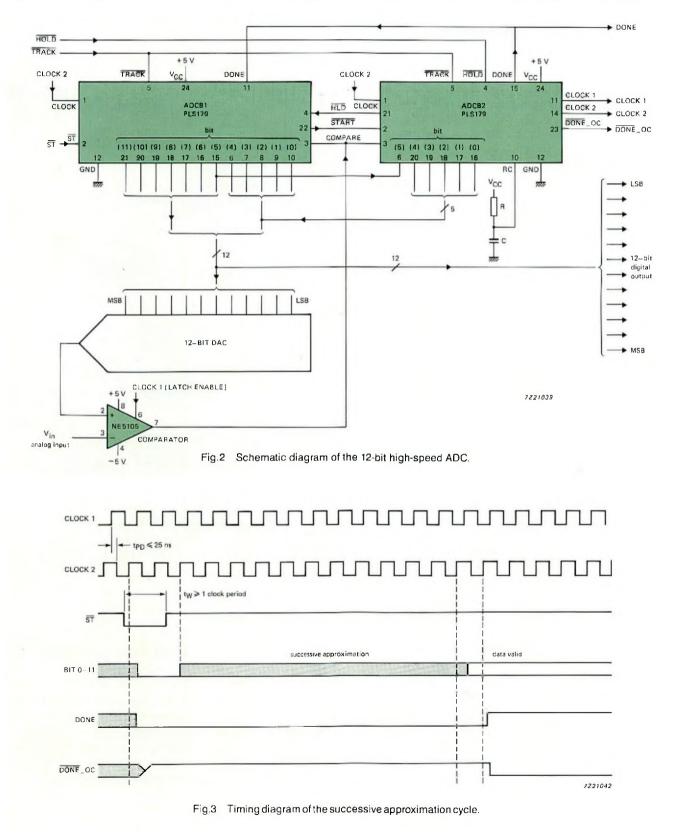

The starting conditions for the initial successive approximation cycle are the TRACK and HOLD inputs set HIGH and the ST input set LOW. On the rising edge of the first CLOCK 2 pulse after the ST input has been set LOW, the 12-bit SAR is loaded with its half full-scale value ( $2^{11} = \text{binary 2048}$ ) and the DONE output is reset LOW (open-collector output DONE\_OC high-impedance). The digital output from the SAR is in natural binary format i.e. if all twelve bits are '0' the digital output value is  $2^{12} - 1 = 4095$ . As shown in Fig.2, bits 0 to 4 are registered in PLS179 ADCB2 and bits 5 to 11 are registered in PLS179 ADCB1.

The digital output value from the SAR (initially binary 2048) is converted to analog form by the 12-bit DAC and compared with the analog input level by the SE/NE5I05 comparator. The comparator output (HIGH if the digital output value is greater than the analog input level, and LOW if it is less) is applied to the COMPARE input of both PLS179s. The output from the SE/NE5I05 comparator is latched by CLOCK 1 to prevent violation of the set-up time due to changes of the analog input level whilst the SAR/counter is incrementing/decrementing. If an analog comparator without a latching facility is used instead of an SE/NE5I05, an external latch must be used.

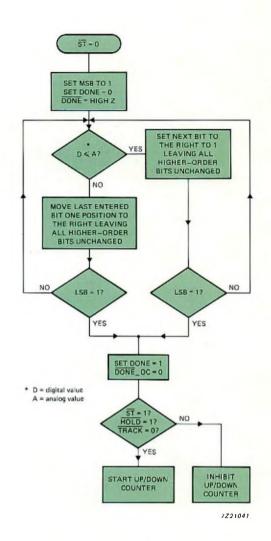

Figure 4 is a flow chart of the successive approximation algorithm for the SAR which can be summarized as follows. If the digital output value from the ADC is greater than the analog input level (D>A), move the last bit in the SAR that was set to '1' one position to the right; otherwise, set the next bit to the right to '1'. Repeat this procedure until all 12 bits have been operated upon. Consequently, the last action in the successive approximation cycle is always to set the LSB in the SAR (bit 0) to '1'.

At the rising edge of the CLOCK 2 pulse following the setting of the LSB in the SAR to 'l', the initial successive approximation cycle is complete and output DONE is set HIGH and open-collector output DONE\_OC is set LOW. The states of these two outputs are latched until they are reset by setting the ST input LOW again to start another successive approximation cycle. Bit maps illustrating the SAR contents during successive approximation of analog input levels higher and lower than the initial half full-scale value of the SAR (binary 2048) are given in Fig.5 and Fig.6 respectively.

The initial successive approximation cycle takes 13 periods of CLOCK 2 to complete. It is essential that the analog input level to the comparator remains constant during this period. If rapidly varying analog inputs are to be converted it will therefore be necessary to incorporate an analog sample-andhold circuit (controlled by output DONE) at the analog input to the ADC.

Fig.4 Flow chart of the SAR algorithm.

#### Up/down counter

When output DONE is HIGH (successive approximation cycle complete) and input HOLD is HIGH, input TRACK can be set LOW to convert the SAR into a 12-bit up/down counter consisting of 12 toggle flip-flops, each with two p-terms for directional control. The up/down counter can track variations of the level of the analog input signal at the rate of one LSB per CLOCK 2 period. The counting can be inhibited at any time by setting the HOLD input LOW. The digital output value from the ADC then remains constant indefinitely.

|      |     |    |   |   | A = 3 | 3000  |      |   |   |   |   |         |

|------|-----|----|---|---|-------|-------|------|---|---|---|---|---------|

|      |     |    |   |   |       | BITNU | MBER |   |   |   |   | ALC: NO |

| D    | 11  | 10 | 9 | 8 | 7     | 6     | 5    | 4 | 3 | 2 | 1 | 0       |

| 0    | 0   | 0  | 0 | 0 | 0     | 0     | 0    | 0 | 0 | 0 | 0 | 0       |

| 2048 | 1   | 0  | 0 | 0 | 0     | 0     | 0    | 0 | 0 | 0 | 0 | 0       |

| 3072 | 1   | 1  | 0 | 0 | 0     | 0     | 0    | 0 | 0 | 0 | 0 | 0       |

| 2560 | 1   | 0  | 1 | 0 | 0     | 0     | 0    | 0 | 0 | 0 | 0 | 0       |

| 2816 | 1   | 0  | 1 | 1 | 0     | 0     | 0    | 0 | 0 | 0 | 0 | 0       |

| 2944 | 1   | 0  | 1 | 1 | 1     | 0     | 0    | 0 | 0 | 0 | 0 | 0       |

| 3000 | 1   | 0  | 1 | 1 | 1     | 1     | 0    | 0 | 0 | 0 | 0 | 0       |

| 3032 | 1   | 0  | 1 | 1 | 1     | 1     | 1    | 0 | 0 | 0 | 0 | 0       |

| 3016 | 1   | 0  | 1 | 1 | 1     | 1     | 0    | 1 | 0 | 0 | D | 0       |

| 3008 | 1   | 0  | 1 | 1 | 1     | 1     | 0    | 0 | 1 | 0 | 0 | 0       |

| 3004 | 1   | 0  | 1 | 1 | 1     | 1     | 0    | 0 | 0 | 1 | 0 | 0       |

| 3002 | 1   | 0  | 1 | 1 | 1     | 1     | 0    | 0 | 0 | 0 | 1 | 0       |

| 3001 | 1   | 0  | 1 | 1 | 1     | 1     | 0    | 0 | 0 | 0 | 0 | 1       |

|      | MSB |    |   |   |       |       |      |   |   |   |   | LSB     |

set to half full-scale D < A: set bit 10 to 1 D > A: shift bit 10 right D < A: set bit 8 to 1 D < A: set bit 7 to 1 D < A: set bit 6 to 1 D = A: set bit 5 to 1 D > A: shift bit 5 right D > A: shift bit 4 right D > A: shift bit 3 right D > A: shift bit 2 right D > A: shift bit 1 right LSB=1: set DONE=1

D = digital value A = analog value

Fig.5 SAR bit map for counting up to binary 3000.

|      |       |            |   |   | A = | 523 |   |   |   |   |   |     |

|------|-------|------------|---|---|-----|-----|---|---|---|---|---|-----|

| D    | 1.1.1 | BIT NUMBER |   |   |     |     |   |   |   |   |   |     |

| U    | 11    | 10         | 9 | 8 | 7   | 6   | 5 | 4 | 3 | 2 | 1 | 0   |

| 0    | 0     | 0          | 0 | 0 | 0   | 0   | 0 | 0 | 0 | 0 | 0 | 0   |

| 2048 | 1     | 0          | 0 | 0 | ٥   | 0   | 0 | 0 | 0 | 0 | 0 | 0   |

| 1024 | 0     | 1          | 0 | 0 | 0   | 0   | 0 | 0 | 0 | 0 | 0 | 0   |

| 512  | 0     | 0          | 1 | 0 | 0   | 0   | 0 | 0 | 0 | 0 | 0 | 0   |

| 768  | 0     | 0          | 1 | 1 | 0   | 0   | 0 | 0 | 0 | 0 | 0 | 0   |

| 640  | 0     | 0          | 1 | 0 | 1   | 0   | 0 | 0 | 0 | 0 | 0 | 0   |

| 576  | 0     | 0          | 1 | 0 | 0   | 1   | 0 | 0 | 0 | 0 | 0 | 0   |

| 544  | 0     | 0          | 1 | 0 | 0   | ٥   | 1 | 0 | 0 | 0 | 0 | 0   |

| 528  | 0     | 0          | 1 | 0 | 0   | 0   | 0 | 1 | 0 | 0 | 0 | 0   |

| 520  | 0     | 0          | 1 | 0 | 0   | 0   | 0 | 0 | 1 | 0 | 0 | 0   |

| 524  | 0     | 0          | 1 | 0 | 0   | 0   | 0 | 0 | 1 | 1 | 0 | 0   |

| 522  | 0     | 0          | 1 | 0 | 0   | 0   | 0 | 0 | 1 | 0 | 1 | 0   |

| 523  | 0     | 0          | 1 | 0 | 0   | 0   | 0 | 0 | 1 | 0 | 1 | 1   |

|      | MSB   | -          |   | - |     |     |   |   |   |   |   | LSB |

set to half full-scale D > A: shift bit 11 right D > A: shift bit 10 right D < A: set bit 8 to 1 D > A: shift bit 8 right D > A: shift bit 7 right D > A: shift bit 6 right D > A: shift bit 5 right D > A: shift bit 4 right D < A: set bit 2 to 1 D > A: shift bit 2 right D < A: set bit 1 to 1 LSB=1: set DONE=1

MSB

D = digital value

A = analog value

Fig.6 SAR bit map for counting down to binary 523.

#### Input latches

Since inputs ST and HOLD may not be synchronised with CLOCK 2 there would be a possibility of them assuming a metastable state if some precautions were not taken. They are therefore each effectively latched by a flip-flop and two p-terms configured as a non-inverting D flip-flip at outputs START and HDL respectively. Once latched, their logic states become effective at the rising edge of the next clock pulse.

#### Clock generator

PLS179 ADCB2 generates biphase clock pulses (CLOCK 1 and CLOCK 2), the frequency of which is controlled by the RC network at pin RC. It is recommended that the value of the capacitor be made less than 1 nF. The actual RC time-constant for a particular frequency must be determined experimentally (see Application Note 13 in the Reference for further details). The two clocks are basically anti-phase but the propagation delay of CLOCK 2 is 25 ns longer than that of CLOCK 1. CLOCK 2 controls the SAR and the up/down counter, CLOCK 1 controls the comparator latch.

#### Comparator SE/NE5105

Our high-speed, high-precision comparator SE/NE5105 has an input offset voltage of only 100  $\mu$ V, an input offset current of 3 nA and a response time of 36 ns with 1.2 mV of overdrive. It operates from a dual 5 V supply and incorporates an active-HIGH output latch. It has a voltage gain of 88 dB and is capable of driving 10 TTL loads.

#### FIELD PROGRAMMING THE PLS179s

The PLS179s are field-programmed using our PLD programming software called Automated Map And Zap Equation (AMAZE) as shown in the appendices. The SAR circuit is first designed as a state-machine (file name: ADCS.SEE) and then, after pin assignments have been made, partitioned into two PLS179s. The up/down counter, input latches, bi-phase clock generator and open-collector output DONE\_OC are then implemented by using Boolean equations in the appropriate .BEE files (file names: ADCB.BEE and ADCB2.BEE) in AMAZE. These files are then assembled to produce fuse maps for programming the two PLS179s (ADCB1.STD and ADCB2.STD).

#### AMAZE SOFTWARE

The AMAZE software consists of the following five modules:

- Boolean Logic And State Transfer (BLAST) entry program

- Program Table Editor (PTE)

- PAL To PLD (PTP) conversion program

- Device Programmer Interface (DPI) program

- PLD SIMulator (PLD SIM) program.

Each AMAZE software package will be made available in various combinations of the foregoing modules.

#### Features

- multiple modules allow expansion for future requirements

- modules are user-friendly

- both HELP and ERROR messages available

- document print-out: header, pin diagram, Boolean equation and fuse map

- interfaces with most commercially available programmers

- SIMULATOR programs provide test and applications assistance

#### BLAST module

This module helps engineers to implement their designs in PLD logic. It checks design data and automatically compiles a program table from Boolean and state-machine equations. Data from the program table is then used to produce a Standard File which contains the fusing codes in a form that is acceptable to AMAZE modules PLD SIM and DPI.

BLAST reports any logic or syntax errors and lists the equations in a sum-of-products form which helps the user to minimize the number of logic equations entered. BLAST automatically partitions state-machine designs into specified devices and then deletes any redundant terms during compilation.

BLAST can also be used to modify a logic-set currently programmed into a device by overlaying new data onto unused fuses.

The main features of BLAST are:

- screen menus for inputs

- full compiler for performing product term manipulation

- document print-out: header, pin diagram, fuse map etc.

#### PTE module

The Program Table Entry (PTE) module is an interactive editor which allows the logic designer to enter data into AMAZE in the form of program tables. Each PLD data sheet in the Reference includes the program table format applicable to the specified IC. PTE can also be used to document completed designs and to change logic functions which have previously been defined in the BLAST module.

The main features of PTE are:

- program tables are exactly as defined in the data sheets

- interactive with BLAST

- uses our standard H and L input format.

#### **PTP** module

The Programmable array logic To Programmable logic device (PTP) module is a conversion program which allows easy transfer of the PAL20 circuits to our 20-pin PLDs. PTP can automatically upload the PAL pattern from a commercially available programmer, convert the pattern into a PLD pattern, and then download it into the programmer. The PAL pattern and its corresponding PLD pattern are documented, and the PLD pattern can be directed to other AMAZE modules. PTP can also convert the PAL fuse file in a HEXPLOT format.

The main features of PTP are:

- automatic assembler

- reduces duplicated p-terms

- supports all our 20-pin PLS15X programmable logic sequencers.

#### **DPI** module

The Device Programmer Interface (DPI) software module provides the interface between the standard file created by the AMAZE modules and a commercial programmer. It allows both download (sending from host to programmer) and upload (sending from programmer to host) operations. It supports both JEDEC and our H and L formats to convey fusing information to and from most commercially available programmers.

The main features of DPI are:

- screen menus for inputs

- provides JEDEC or H and L formats

- download/upload to/from commercially available programmers uses our standard H and L input format.

#### PLD SIM module

The PLD SIMulator (PLD SIM) software module simulates the operation of the logic defined for our PLDs. The input to the program is the Standard File generated by other AMAZE modules. The simulator can be run manually or automatically. In the automatic mode, it creates a file of vectors for testing the programmed IC. In the manual mode, it allows the operator to assign an input vector and observe the resultant output.

The main features of PLD SIM are:

- simple input form

- test vector generation (on Rev.D or later)

- output can be used as input to PLD fault grader

- software applications support prior to programming.

#### AMAZE software compatibility

| software     | hardware requirements                                                                                                                                            |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 82SOFT523-SS | IBM-PC or IBM-XT or compatible<br>computer 256K memory<br>PC-DOS operating system, version 2.0<br>or higher<br>2 floppy disc drives or 1 floppy +<br>1 hard disc |

| 82SOFT211-SS | VAX series computer<br>VMS operating system (any revision)                                                                                                       |

AMAZE is supplied fully-documented and complete with the appropriate magnetic media. Applications support is provided by our field service engineers in most areas. Contact your local sales organization listed on the rear cover for further information about AMAZE and our Programmable Logic Devices (PLDs).

#### REFERENCE

Philips Data Handbook IC13 "Semi-custom Programmable Logic Devices (PLD)", ordering code 9398 139 00011.

Appendix 1 -State equations for the SAR

EDEVICE SELECTION ADCB1/PLS179 ADCB2/PLS179 **ESTATE VECTORS** [ /START, BIT11, BIT10, BIT9, BIT8, BIT7, BIT6, BIT5, BIT4, BIT3, BIT2, BIT1, BITO, DONE ] INIT = 0 ---- ---- - b ; "START CONVERSION PROCESS" HALFSCALE = - 1000 0000 0000 0 b ; "SET SAR TO HALF SCALE" = 1 1000 0000 0000 0 b ; "PRESENT STATE = 2048 (HALF SCALE)" ST2048 = 1 -100 0000 0000 0 b ;= 1 --10 0000 0000 0 b ; ST1024 ST512 ST256 = 1 ---1 0000 0000 0 b ; = 1 ---- 1000 0000 0 b ; ST128 = 1 ---- -100 0000 0 b ; ST64 = 1 ---- --10 0000 0 b ; ST32 = 1 ---- --- 1 0000 0 b ; ST16 = 1 ---- 1000 0 b j STB = 1 ---- --- -100 0 b j ST4 = 1 ---- --- --- 10 0 b j ST2 = 1 ---- ---- 1 0 b i ST1 AD1024 = - -1-- ---- - b ; "ADD 1 BIT TO THE RIGHT" - ----- ---- - b j AD512 = - ---1 ---- - b j AD256 AD128 = - ---- 1---- - b 3 • - ---- -1-- --- - b j AD64 = - ---- --- - b ; AD32 = - ---- --- - b AD16 1 ADB = - ---- 1--- - b 1 = - ---- -1-- - b ; AD4 **-** ----- --1- - b AD2 8 = - ---- ---- ---- b ; AD 1 = - ---- ---- 1 b g END - - 01--- --- - b ; SH1024 "SHIFT ONE BIT TO THE RIGHT" = - -01- ---- - b ; 8H512 = - --01 ---- - b ; SH256 = - ---0 1---- - b j SH128 = - ---- 01-- --- b j SH64 = - ---- -01- ---- - b SH32 = - ---- --- b ; SH16 = - ---- --- b j SHB = - ---- 01-- - b ; SH4 = - ---- -01- - b ; SH2 = - ---- ---01 - b ; SH1 = - ---- ----0 1 b i SHO *<b>EINPUT VECTORS* [ COMPARE ] GREATER = 1 b ; "IF DIGITAL OUTPUT IS GREATER THAN ANALOG INPUT, ...." = 0 b ; "IF DIGITAL OUTPUT IS LESS THAN ANALOG INPUT, ...." LESS

Appendix 1 (cont.)

COUTPUT VECTORS *<b>CTRANSITIONS* WHILE [ INIT ] IF [] THEN [ HALFSCALE ] "INITIALIZE REGISTER TO HALF SCALE" WHILE [ ST2048 ] IF [ GREATER ] THEN [ SH1024 ] "IF GREATER THAN, SHIFT 1 BIT" IF [ LESS ] THEN [ AD1024 ] "IF LESS THAN, ADD 1 BIT" WHILE [ ST1024 ] IF [ GREATER ] THEN [ SH512 ] IF [ LESS ] THEN [ AD512 ] WHILE [ ST512 ] IF [ GREATER ] THEN [ SH256 ] IF [ LESS ] THEN [ AD256 ] WHILE [ ST256 ] IF [ GREATER ] THEN [ SH128 ] IF [ LESS ] THEN [ AD128 ] WHILE [ ST128 ] IF [ GREATER ] THEN [ SH64 ] IF [ LESS ] THEN [ AD64 ] WHILE [ ST64 ] IF [ GREATER ] THEN [ SH32 ] IF [ LESS ] THEN [ AD32 ] WHILE [ ST32 ] IF [ GREATER ] THEN [ SH16 ] IF [ LESS ] THEN [ AD16 ] WHILE [ ST16 ] IF [ GREATER ] THEN [ SHB ] IF [ LESS ] THEN [ ADB ] WHILE [ ST8 ] IF [ GREATER ] THEN [ SH4 ] IF [ LESS ] THEN [ AD4 ] WHILE [ ST4 ] IF [ GREATER ] THEN [ SH2 ] IF [ LESS ] THEN [ AD2 ] WHILE [ ST2 ] IF [ GREATER ] THEN [ SH1 ] IF [ LESS ] THEN [ AD1 ] WHILE [ ST1 ] IF [ GREATER ] THEN [ SHO ] IF [] THEN [END]

Appendix 2 – Pin lists

File Name : ADCB1 Date : Time : \*\*\*\*\*\*\* \*\* FNC \*\*PIN ----- PIN\*\* FNC \*\* LABEL LABEL \*\* CK \*\* 1-1 \*\* I \*\* 2-1 \*\* I \*\* 3-1 \*\* I \*\* 4-1 1-24 \*\* +5V \*\*VCC 1-23 \*\* /B \*\*N/C CLOCK /ST i-22 \*\* 0 i-21 \*\* 0 COMPARE ##/START Ρ ##BIT11 /HLD \*\* 5-1 1-20 ## 0 /TRACK \*\* I L ##BIT10 l-19 \*\* 0 l-18 \*\* 0 l-17 \*\* 0 ## I ## 6-1 ##BIT9 BIT4 5 \*\* 7-1 ##BIT8 ## I BIT3 1 \*\* 8-i BIT2 **\*\*** I 7 ##BIT7 ## I 1-16 ## D \*\* 9-1 9 ##BIT6 BIT1 l-15 \*\* 0 \*\*BIT l-14 \*\* /B \*\*N/C \*\* I ## 10-1 ##BIT5 BITO ## I \*\* 11-1 DONE 1-13 \*\* /DE \*\*N/C GND **\*\*** 0V ## 12-1

```

File Name : ADCB2

Date :

Time :

```

#### \*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*

| LABEL   | ** | FNC | ** | PIN  |     | - PII | 4## | FNC | ++ LABEL       |

|---------|----|-----|----|------|-----|-------|-----|-----|----------------|

| CLOCK   | ** | CK  | ** | 1-1  | 1   | -24   | **  | +5V | ++VCC          |

| /START  | ** | I   | ** | 2-1  | 1   | -23   | **  | /B  | ##/DONE_OC     |

| COMPARE | ** | I   | ** | 3-1  | :   | -22   | **  | В   | **N/C          |

| /HOLD   | ** | I   | ** | 4-1  | P   | -21   | **  | 0   | ##/HLD         |

| /TRACK  | ** | I   | ** | 5-1  | LI  | -20   | **  | 0   | ##BIT4         |

| BIT5    | ** | I   | ** | 6-1  | S I | -19   | **  | 0   | ##BIT3         |

| N/C     | ** | I   | ** | 7-:  | 1 : | -18   | **  | 0   | **BIT2         |

| N/C     | ** | I   | ** | 8-:  | 7 1 | -17   | **  | 0   | ##BIT1         |

| N/C     | ** | I   | ** | 9-1  | 9 1 | -16   | **  | 0   | <b>#</b> *BITO |

| RC      | ** | /B  | ** | 10-: | 1   | -15   | **  | 0   | **DONE         |

| CLOCK1  | ** | 0   | ** | 11-: | :   | -14   | **  | /0  | #*CLOCK2       |

| GND     | ** | ٥V  | ** | 12-1 | 1   | -13   | **  | /0E | **N/C          |

|         |    |     |    |      |     | _     |     |     |                |

```

Appendix 3 – Boolean equations for the up/down counter and input latches

```

```

ODEVICE TYPE

PLS179

edrawing

<b>REVISION

ODATE

ESYMBOL

FILE NAME : ADCB1

COMPANY

ONAME

ODESCRIPTION

<u><b>@COMMON PRODUCT TERM</u>

<b>@COMPLEMENT ARRAY

€I/O DIRECTION

COUTPUT POLARITY

<b>EFLIP FLOP CONTROL

FC = 1

"SET ALL FLIP FLOP TO BE J/K"

COUTPUT ENABLE

REGISTER LOAD

QASYNCHRONOUS PRESET/RESET

<b>QFLIP FLOP MODE

<b>QLOGIC EQUATION

"NON-INVERTING INPUT LATCH: /START = /ST "

START : J = ST ;

K = /ST ;

"UP/DOWN COUNTER ROUTINE"

/BIT5 : T = /START * TRACK * DONE * /HLD * COMPARE * /BIT0 * /BIT1 *

/BIT2 * /BIT3 * /BIT4

/START * TRACK * DONE * /HLD * /COMPARE * BITO * BIT1 *

BIT2 * BIT3 * BIT4 ;

/BIT6 : T = /START * TRACK * DONE * /HLD * COMPARE * /BIT0 * /BIT1 *

/BIT2 * /BIT3 * /BIT4 * /B1T5 +

/START * TRACK * DONE * /HLD * /COMPARE * BITO * BIT1 *

BIT2 * BIT3 * BIT4 * BIT5 ;

/BIT7 : T = /START * TRACK * DONE * /HLD * COMPARE *

/BITO * /BIT1 * /BIT2 * /BIT3 * /BIT4 * /BIT5 * /BIT6 +

/START * TRACK * DONE * /HLD * /COMPARE *

BITO * BIT1 * BIT2 * BIT3 * BIT4 * BIT5 * BIT6 ;

/BITE : T = /START * TRACK * DONE * /HLD * COMPARE * /BITO * /BIT1 *

/BIT2 * /BIT3 * /BIT4 * /BIT5 * /BIT6 * /BIT7 +

/START * TRACK * DONE * /HLD * /COMPARE * BITO * BIT1 *

BIT2 * BIT3 * BIT4 * BIT5 * BIT6 * BIT7 ;

/BIT9 : T = /START * TRACK * DONE * /HLD * COMPARE * /BIT0 * /BIT1 *

/BIT2 * /BIT3 * /BIT4 * /BIT5 * /BIT6 * /BIT7 * /BIT8 +

/START * TRACK * DONE * /HLD * /COMPARE * BITO * BIT1 *

BIT2 * BIT3 * BIT4 * BIT5 * BIT6 * BIT7 * BIT8 ;

/BIT10 : T = /START * TRACK * DONE * /HLD * COMPARE * /BIT0 * /BIT1 *

/BIT2 * /BIT3 * /BIT4 * /BIT5 * /BIT6 * /BIT7 * /BIT8 *

/BIT9 +

/START * TRACK * DONE * /HLD * /COMPARE * BITO * BIT1 *

BIT2 * BIT3 * BIT4 * BIT5 * BIT6 * BIT7 * BIT8 *

BIT9 ;

/BIT11 : T = /START * TRACK * DONE * /HLD * COMPARE * /BIT0 * /BIT1 *

/BIT2 * /BIT3 * /BIT4 * /BIT5 * /BIT6 * /BIT7 * /BIT8 *

/BIT9 #

/BIT10 +

/START * TRACK * DONE * /HLD * /COMPARE * BITO * BIT1 *

BIT2 * BIT3 * BIT4 * BIT5 * BIT6 * BIT7 * BIT8 *

BIT9 * BIT10 ;

```

HIGH-SPEED 12-BIT TRACKING ADC

Appendix 3 (cont.)

```

@DEVICE TYPE

PLS179

edrawing

@REVISION

eDATE

@SYMBOL

FILE NAME : ADCB2

COMPANY

ENAME

@DESCRIPTION

@COMMON PRODUCT TERM

COMPLEMENT ARRAY

@I/O DIRECTION

DO = RC;

"RC OSCILLATOR"

D3 = DONE :

"ENABLE /DONE OC TO OUTPUT A LOGIC LOW."

COUTPUT POLARITY

@FLIP FLOP CONTROL

FC = 1;

COUTPUT ENABLE

REGISTER LOAD

€ASYNCHRONOUS PRESET/RESET

<b>@FLIP FLOP MODE

"MO, M1, M2, M3, M4, M5 = 1 ; SET FO - F5 TO J/K FLIP FLOPS."

<b>QLOGIC EQUATION

"NON-INVERTING INPUT LATCH : /HLD = /HOLD "

: J = HOLD ;

HLD

K = /HOLD ;

"UP/DOWN COUNTER ROUTINE"

: T = /START * TRACK * DONE * /HLD ;

1 T = /START * TRACK * DONE * /HLD * /COMPARE * BITO +

/BITO

/BIT1

/START * TRACK * DONE * /HLD * COMPARE * /BITO ;

/BIT2

: T = /START * TRACK * DONE * /HLD * /COMPARE * BITO *

BIT1 +

/START * TRACK * DONE * /HLD *

COMPARE * /BITO * /BIT1 ;

/BIT3

: T = /START * TRACK * DONE * /HLD * /COMPARE * BITO *

BIT2 +

BIT1 #

/START * TRACK * DONE * /HLD * COMPARE * /BITO * /BIT1 * /BIT2 ;

/BIT4 : T = /START * TRACK * DONE * /HLD * /COMPARE *

BITO #

BIT1 # BIT2 #

BIT3 +

/START * TRACK * DONE * /HLD * COMPARE * /BITO * /BIT1 * /BIT2 *

/BIT3 ;

/DONE_OC

= /(1);

"RC OSCILLATOR"

= /(1) ;

RC

CLOCK1

= RC ;

CLOCK2

= / ( CLOCK1 ) ;

"BUILT-IN DELAY OF 1 tPD"

```

| PL6179                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ! F/F TYPE !                                                                                      | E(b)= !E(a) = !POLARTY!                                                           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|

| PL8179<br><br>E !                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                   | 0 ! 0 !LILILI                                                                     |

| R ! ! I ! B(1)<br>M !C!                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ! Q(p) !                                                                                          | Q(n) ! B(o) !                                                                     |

| $\begin{array}{c} - \frac{1}{2} \cdot \frac{7}{4} - \frac{5}{4} - \frac{3}{2} - \frac{1}{2} \cdot \frac{9}{3} - \frac{1}{2} - \frac{9}{4} - \frac{1}{2} - \frac{1}{4} + \frac{1}{4}$ | 17.6.5.4.3.2.1.0!         1         1         1         1         1         1         1         1 | 7_6_5_4_3_2_1_0!3_2_1_0<br>H,                                                     |

| 1 1 1 1 T H O S / / O I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | B / B B B B B B B<br>I B I I I I I I I<br>T T T T T T T T T T<br>D A 1 1 9 B 7 6 5<br>R 1 0       | / B B B B B B B N N D B<br>S I I I I I I I I / / O I<br>T T T T T T T T T C C N T |

Appendix 4 – Fuse maps

Appendix 4 (cont.)

| PL8179                                                                                          | ! F/F TYPE                             | ! E(b)= !E(a) = !P                                                | DLARTY!     |

|-------------------------------------------------------------------------------------------------|----------------------------------------|-------------------------------------------------------------------|-------------|

| PL8179<br><br>T !<br>E !                                                                        |                                        | .! 0 ! 0 !L                                                       | LiHiL!      |

| R ! ! I ! B(i)<br>M !C!                                                                         | ! Q(p)                                 | ! Q(n) !                                                          | B(o) !      |

| !_!7_6_5_4_3_2_1_0!3_2_1_0<br>0!A! L!                                                           | -! <sub>1</sub>                        | ·!O H,!.                                                          | !           |

| 2!A!,L H!<br>3!A!,L - L H!                                                                      | -!- L, L<br>-!- L, L L                 | .!0, 0 - !.                                                       | · • • • • ! |

| 4!A!, L - H H!, L - L H!, L - L H!                                                              | -!- L L L L                            | !0 0 !.                                                           | !           |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                            | -!- LH H H L                           | !0 0 !.                                                           | !           |

| 9!A!,L - L H!<br>10!A!,L - H H!<br>11!A!,!                                                      | -!- L - H,H H H L<br>-!                | .!0 - 0 !.                                                        | • • • •!    |

| $\begin{array}{c} 12!A!$                                                                        | -!                                     | 10                                                                | . A!        |

| 15!A! H, H H!<br>16!A! H L H!                                                                   | -!- – н н,н н н н<br>-!- – н н.н н н н | 1!0 - L -,!.<br>1!0 - L!.                                         | · · · ·!    |

| 17!A!, H H!<br>18!A!, L H!<br>19!A!, H H!                                                       | -! L H,H H H H<br>-! L.H H H H         | $1!0 L_{1}!$                                                      | • • • •!    |

| 20!A!, L H!<br>21!A!, H H!<br>22!A!, L H!                                                       | -! L,H H H H<br>-! L H H H             | 1!0 L !.                                                          | • • • •!    |

| 23!A! H H!                                                                                      | -!,- L H H<br>-!,- L H H               | 1!0 + + + - !                                                     | !           |

| 25!A!, H H!<br>26!A!, H!<br>27!0!0 0 0 0,0 0 0 0!0 0 0                                          | -!, L H<br>D!0 0 0 0,0 0 0 0           | 1!0, L!.<br>)!0 0 0 0.0 0 0 0!4                                   | · · · ·!    |

| 28!0!0 0 0 0,0 0 0 0!0 0 0<br>29!0!0 0 0 0,0 0 0 0!0 0 0<br>30!0!0 0 0 0,0 0 0 0!0 0 0          | 0 0 0 0,0 0 0 0<br>0 0 0 0,0 0 0 0     | )!0 0 0 0,0 0 0 0!#<br>)!0 0 0 0.0 0 0 0!#                        | A A A A!    |

| 31!0!0 0 0 0,0 0 0 0!0 0 0 0<br>Fc!A!,!                                                         | )!0 0 0 0,0 0 0 0<br>-!                | 9!0 0 0 0,0 0 0 0!#<br>-!                                         | A A A!      |

| Pb!.!0000,000000000           Rb!.!0000,0000000000000000000000000000000                         | 0 0 0 0,0 0 0 0<br>0 0 0 0,0 0 0 0     | )!<br>)!                                                          |             |

| Pal. 10 0 0 0,0 0 0 010 0 0 0<br>Ral. 10 0 0 0,0 0 0 010 0 0 0<br>Lal. 10 0 0 0,0 0 0 0 0 0 0 0 | 0 0 0 0 0 0 0 0 0                      | )!                                                                | •           |

| D3!-!                                                                                           |                                        | . 1                                                               | •           |

| D1! - !                                                                                         | -!                                     | :<br>• 9                                                          | •           |

| N N N B / / C / / C C F<br>/ / / I T H O B D L L C<br>C C C T R O M T O O O                     | . / H I I I I I O                      | ) N / B B B B B D /<br>  / H I I I I I O D<br>  C L T T T T T N D | LLC         |

| 5 A L P A N C C<br>C D A R E K K<br>K R T _ 2 1                                                 | D43210E                                | D 4 3 2 1 0 E N                                                   |             |

| ĒŪ                                                                                              |                                        | ā                                                                 | 5           |

### Ceramic-chip capacitors high-rel products with a promising future

#### W. LANGENHORST and R. WASER

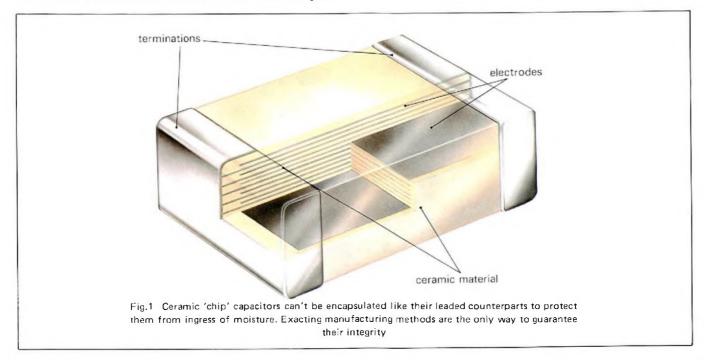

As surface-mount technology started picking up in a big way, it was inevitable that it would create headaches for component manufacturers. The task of converting leaded components into SMDs isn't always a straightforward one, and if these components have to be supplied as naked chips, the headaches, for some manufacturers at least, can be quite severe.

A perfect example of this can be found in ceramicmultilayer capacitors. In earlier times when these were leaded devices, a lot of manufacturers experienced a disturbing number of early failures due to breakdown at low voltage. These failures were the result of metallic bridging between electrodes induced by electromigration. And this was caused by ingress of moisture due to delamination, cracks and voids in the ceramic, all the result of poor manufacturing methods. The answer was quite simple. Many manufacturers just sealed the ceramic from moisture by encapsulating their capacitors, and were thus able to continue with their manufacturing methods unchanged. The customer, of course, was quite satisfied since these encapsulated capacitors were then perfectly reliable.

For these manufacturers, however, the problem was not solved, just contained. And with the rapid growth of surface-mount technology, ceramic-multilayer capacitors in chip form became increasingly in demand and the problem returned. This time there could be no easy answer, so despite their many attractive properties, ceramic-'chip' capacitors have not been accepted by the market as readily as they might have been.

#### CERAMIC-CHIP CAPACITORS

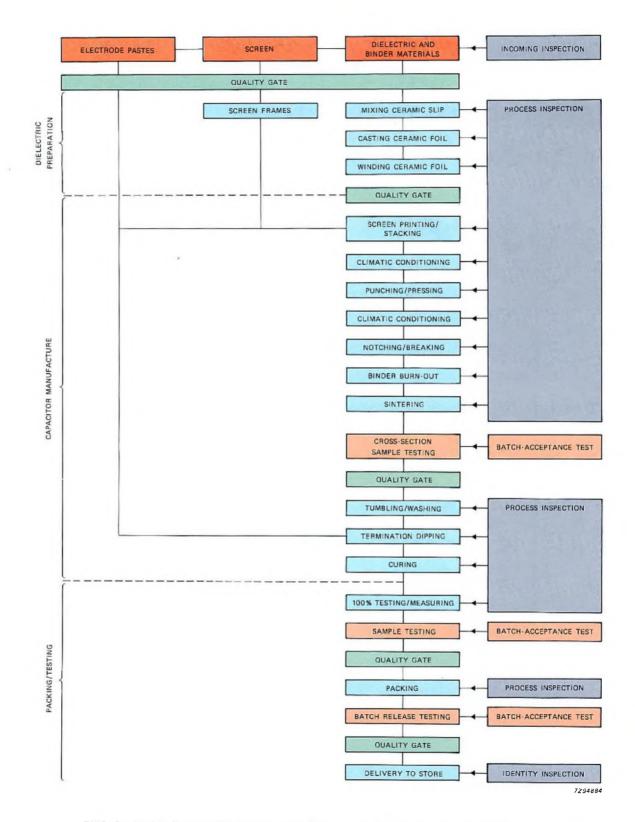

Fig.2 Production flow chart for our ceramic multilayer capacitors showing the principal features assuring their high quality which includes among other things their immunity from low-voltage breakdown

But not all manufacturers relied solely on encapsulation to guarantee the integrity of their multilayer capacitors. For many, their manufacturing methods were sufficiently stringent from the start to assure that their capacitors would never suffer from low-voltage breakdown. For these manufacturers, the apparent reluctance of the market to accept ceramic-chip capacitors is totally unjustified.

Our ceramic-multilayer capacitors are a prime example of this. Recognizing at an early stage the coming importance of surface-mount technology, we entered the market directly with chip capacitors. Our manufacturing methods, therefore, had to be stringent from the start, with the result that our capacitors are virtually immune from lowvoltage breakdown. With this, potentially the most common cause of early failure in ceramic-multilayer capacitors, eradicated, the short-term reliability of our capacitors, as we'll demonstrate, can be considered beyond reproach.

And what of long-term reliability? Long-term failures are generally a function of material properties, and one of the most common causes of long-term failure in ceramicmultilayer capacitors has been dielectric degradation. This is the decrease in insulation resistance that can occur when a capacitor is stressed at high voltage and high temperature over a long period. Since dielectric degradation occurs only late in life, and ceramic-multilayer capacitors normally have a very long lifetime, it's difficult to detect by normal life testing.

Using accelerated-life testing techniques, however, at temperatures up to  $500 \,^{\circ}$ C and voltages up to  $250 \,\text{V}$ , we've demonstrated that the ceramic used in our capacitors is highly stable and not subject to dielectric degradation during the normal lifetime of the capacitors. Thanks to these stringent testing techniques and to the advances in ceramic technology made in recent years, we can confidently predict lifetimes for our ceramic multilayer capacitors running into tens or even hundreds of years.

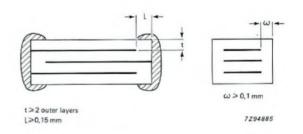

- Built-in safety margins on key parameters such as dielectric thickness and creepage distance. The latter, which is the overlap between adjacent silver-palladium electrodes and hence the distance between each set of electrodes and the opposite end termination (Fig.4), must be greater than 0,15 mm.

- Closely controlled in-line processes (see Fig.2).

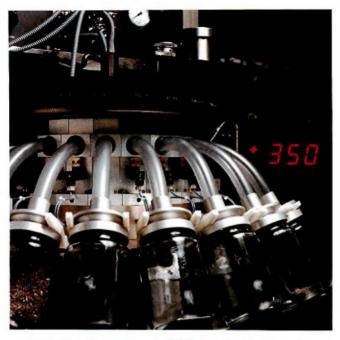

- 100% final electrical inspection in which the capacitors are subjected to a 350 V pulse (6 times nominal voltage). Although not in itself a test that induces low-voltage failure, this test is invaluable for weeding out weak components and components that may later become liable to low-voltage failure.

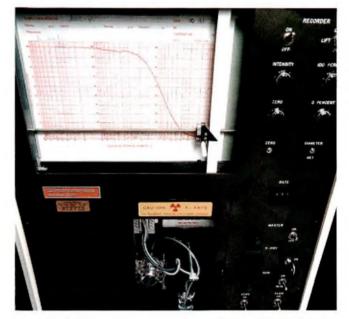

Fig.3 The equipment shown here meters particle size to ensure that we use only the highest grade ceramic

#### **EXACTING MANUFACTURING METHODS**

Figure 2 is a production flow chart for our ceramic-multilayer capacitors showing the features assuring their integrity. Foremost among these are the following:

- Careful control of ceramic properties. This is done by our incoming inspection procedure which accepts only the highest grade ceramic and which carefully meters particle size (Fig.3) to ensure optimum size distribution to produce the best possible ceramic density.

- The use of a proprietary multilayer manufacturing process specially developed to optimize ceramic properties and minimize mechanical defects (see box).

Fig.4 The overlap between adjacent silver-palladium layers determines the gap between each set of electrodes and the opposite end termination. This gap can form a creepage current path and is hence known as the creepage distance. Thanks to our proprietary manufacturing process (see box) we can ensure that this distance is never less than 0,15 mm

#### CERAMIC-CHIP CAPACITORS

Fig.5 Capacitors undergoing 100% final electrical inspection. More than 40 000 capacitors an hour can be tested with this equipment which among other things subjects each capacitor to a 350 V pulse

Fig.6 Capacitors undergoing the loaded humidity test

#### THE CERAMIC IS THE KEY

A major feature of our manufacturing process is the use of a water-based system for manufacturing the ceramic foil. In contrast to other processes, in which the ceramic slip is produced from a mix of ceramic particles, an organic solvent and a high concentration of plastic binder, in our process, the slip is made up of ceramic particles lightly coated with plastic binder and suspended in water. The slip, therefore, has a much lower binder content than that of most of our competitors. So on drying out, the 'green' ceramic, as it's called, has initially a high porosity, allowing rapid drying of the silver-palladium electrode layer after screen printing. This, in turn, allows screen printing and stacking to be performed at a single station, giving far greater accuracy of electrode alignment. What's more, the high porosity of the ceramic foil gives greater adhesion between the ceramic and the silver-palladium layer, and so significantly reduces the risk of delamination.

After screen printing and stacking, the multilayer sheets are compacted (at a pressure of around 3000 kg/cm<sup>2</sup>) to remove air trapped between the layers and to increase their 'green' density. Although this reduces the porosity considerably, its initial high value means that after compacting, the porosity is still higher than it would be with cerarnic produced by conventional processes. This ensures that the next stage: binder burn-out, can take place with a far lower risk of voids appearing in the ceramic; and this risk in further reduced thanks to the very low binder content.

Another possible source of voids, dust failing on the green ceramic, is virtually eliminated by confining all production stages before firing to a production area with an advanced air-conditioning system that keeps dust levels below 10 000 particles\*/ft<sup>3</sup> in the ceramic-casting, screen-printing and termination-dipping areas, and below 100 particles\*/ft<sup>3</sup> in the screen fabrication area.

To further reduce the risk of delamination, the silverpalladium used for the electrodes is impregnated with ceramic. This minimizes mechanical stresses during sintering by reducing the shrinkage of the electrodes so that it more closely matches that of the dielectric.

\* dust particles larger than 5 µm.

#### **PROVEN INTEGRITY**

Our component testing procedure eminently demonstrates the effectiveness of our manufacturing process.

Since low-voltage breakdown is the result of shortcomings in the manufacturing process, it's necessarily batch related. Many of the tests in our batch-release procedure are therefore directed specifically towards triggering low-voltage breakdown in our capacitors. Most notable of these is the loaded humidity test during which we attempt to induce breakdown by subjecting the capacitors to low voltage under extremes of temperatures and humidity. We also limit the maximum current through the capacitors to prevent the current from 'healing' potential breakdown spots by melting away any metallic bridges induced by electromigration.

|                    |          |                                | -              |               | test parameters             |                             |                         |  |

|--------------------|----------|--------------------------------|----------------|---------------|-----------------------------|-----------------------------|-------------------------|--|

| quantity<br>tested |          | component-<br>hours of<br>test | voltage<br>(V) | temp.<br>(°C) | relative<br>humidity<br>(%) | series<br>resistance<br>(Ω) | catastrophi<br>failures |  |

| 5000               | 1000 hr. | 5 x 10 <sup>6</sup>            | 5              | 125           | _                           | 150                         | 0                       |  |

| 5000               | 56 days  | 6,7 x 10 <sup>6</sup>          | 1              | 40            | 95                          | 1 M                         | 0                       |  |

| 384                | 56 days  | $0,52 \times 10^{6}$           | 1,5            | 85            | 85                          | ΙM                          | 0                       |  |

| * 75               | 56 days  | 0,1 x 10 <sup>6</sup>          | 63             | 85            | 85                          | 1 M                         | 0                       |  |

| * 46               | 56 days  | 0,06 x 10 <sup>6</sup>         | 50             | 85            | 85                          | 6,8 k                       | 0                       |  |

\* development group experimental tests.

#### Results of testing for early failures

definition of catastrophic failure:

$\Delta C/C > 1,5$  x specified value

$\tan \delta > 1,5 \ x \ specified \ value$

$R_{ins} < 0,1 x$  specified value.

The table gives the latest results of our loaded humidity tests. By the end of 1985 we had completed more than 12 million component-hours of testing without a single catastrophic failure.

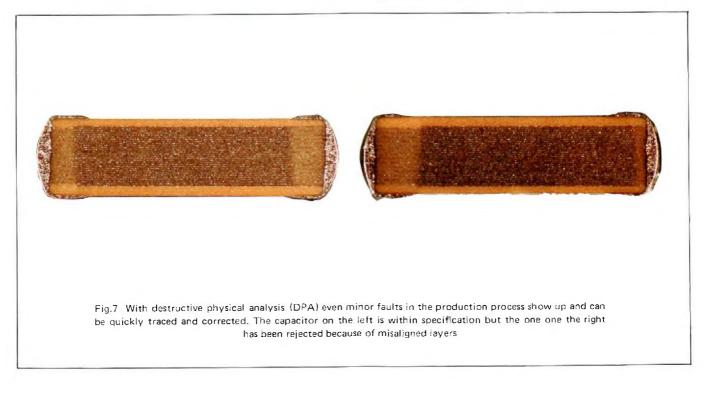

As a further check on our manufacturing process, we perform what's known as destructive physical analysis (DPA) of selected capacitors in which we take a section through the ceramic and examine it microscopically (40x to 1500x magnification) for cracks, voids and delaminations, as well as for poor screen printing, misaligned layers and bent electrodes. With this test, even minor faults in the production process show up (Fig.7) and can be quickly traced and corrected.

#### LONG-TERM RELIABILITY

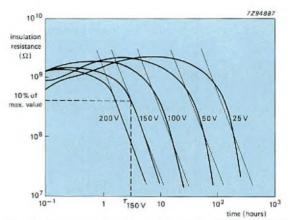

Since the lifetime of ceramic-multilayer capacitors can be reckoned in hundreds of years, it's obviously impractical to search for long-term failures using standard life tests. Instead, we've conducted extensive accelerated-life testing of our capacitors at temperatures up to 500 °C to determine how their most common long-term failure mechanism: dielectric degradation, is likely to affect their lifetime.

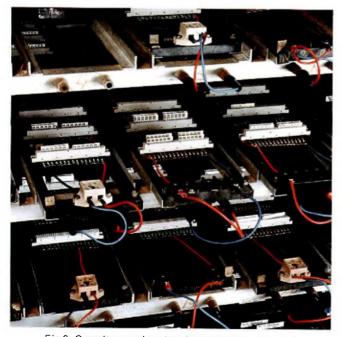

The equipment shown in Fig.8 has been specially developed to measure leakage currents of ceramic multilayer capacitors at temperatures up to 500 °C, and at test voltages

#### CERAMIC-CHIP CAPACITORS

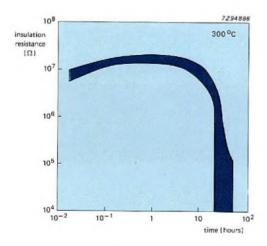

up to 2 kV. Figure 9 shows results of tests using this equipment. The figure plots insulation resistance against time for a typical test batch and clearly demonstrates that dielectric degradation is indeed a material-related phenomenon.

Figure 10 shows typical plots of insulation resistance against time, in this case at applied voltages between 25 V and 200 V, and at a test temperature of 200 °C. The figure clearly shows that at 200 °C, dielectric degradation of the ceramic can begin within around 10 hours.

Fig.8 Specially designed furnace insert that holds up to 16 capacitors to allow their insulation resistance to be measured at temperatures up to 500 °C and at test voltages up to 2 kV

From curves such as these we can determine the mean lifetime  $\tau$ , arbitrarily defined as the time at which insulation resistance has fallen to 10% of its maximum value. (Note: this failure criterion is much more stringent than that used

Fig.9 Plot of insulation resistance against time for Z5U ceramic-multilayer capacitors at 300 °C, 5 V. For all capacitors tested the trend (allowing for individual spread) is quite clear (a slight increase in insulation resistance followed by a rapid drop), and clearly demonstrates that dielectric degradation is a material-related phenomenon

Fig.10 Typical plots of mean insulation resistance against time for 16 Z5U ceramic-multilayer capacitors measured at applied voltages between 25 V and 200 V, and at a test temperature of 200 °C

Fig.11 Extrapolated Arrhenius plots with 50 V applied to various ceramic materials. The line on the far right is the measured behaviour of an experimental fast-degrading material and demonstrates the validity of extrapolating the other plots as straight lines

in standard life tests according to IEC regulations which just count the number of capacitors failing to meet specification.) Arrhenius plots of log ( $\tau$ ) against reciprocal temperature (1/T) can then be made. As Fig.I 1 shows, such plots are substantially linear, allowing extrapolation of capacitor lifetimes for normal operating temperatures.

From Arrhenius plots like these, we've predicted lifetimes for our ceramic multilayer capacitors extending into hundreds and even thousands of years. For example, capacitors produced from our X7R material under an applied voltage of 50V have a predicted lifetime at 125 °C of over 1000 years.

## Stereo sound generator for sound effects and music synthesis

#### MIKE ROBERTS

All the sophisticated application software in the world can't compensate for a home computer that communicates with its user in an unattractive or confusing way. To enhance present levels of visual and audio communication from computer to user, a stereo sound generator, SAA1099, and a 64-colour encoder, TEA2000 (Ref.1), have been developed, each giving software and hardware designers the scope to add more realism to their products.

The sound generator SAA1099 is described in this article. It can produce a wide variety of sound effects including simulations of musical instruments, and the sounds required for arcade/home-computer games. Whereas most integrated sound generators have only three frequency generators, the SAA1099 has six, and the tones from each can be mixed with several kinds of noise. Because there are six frequency generators, full musical chords (including the tonic) can be produced, and two chords (excluding tonics) can overlap. All musical notes in an 8-octave range can be produced. A stereo effect that can give width to scenes in video games is produced by duplicating the six sound components to form identical left and right-channel signals, weighting the signals of each channel, and combining them to form a stereo signal.

Besides the stereo sound facility, effects such as Doppler shifts can be imitated with a minimum of software control. Outside the home computer market, the SAA1099 can be used to good effect in model railways and cars, electronic musical instruments and audible alarms, to name just a few applications. The SAA1099 readily interfaces with most 8-bit microcontrollers and requires only a simple filter to suppress any high-frequency components in the audio output. It has been designed in such a way that a minimum of external components are required. Table 1 gives additional data on the SAA1099; see also Refs 2 and 3.

| TABLE 1                                            |

|----------------------------------------------------|

| Brief data on the SAA1099 (all values are typical) |

| supply voltage                         | V <sub>DD</sub>  | 5 V                                |

|----------------------------------------|------------------|------------------------------------|

| supply current                         | IDD              | 70 mA                              |

| reference current (pin 6)              | Iref             | 250 μΑ                             |

| total power dissipation                | P <sub>tot</sub> | 500 mW                             |

| external clock                         |                  | 8 MHz                              |

| data input                             |                  | 8-bit parallel<br>(TTL-compatible) |

| output frequency range                 |                  | 31 Hz to 7,81 kHz<br>(8 octaves)   |

| output                                 |                  | pulse width modulated              |

| operating ambient<br>temperature range | T <sub>amb</sub> | 0 to +70 °C                        |

| package                                |                  | 18-pin plastic DIL                 |

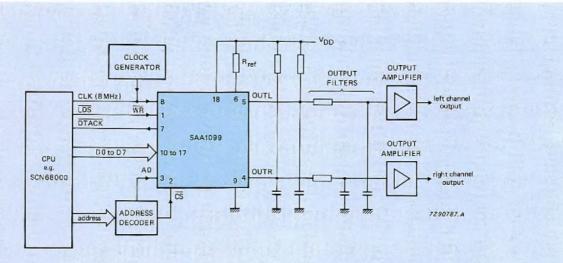

#### COMPLETE SOUND GENERATOR

Figure 1 shows a complete sound generating system. From an 8-bit wide data input from a microprocessor, the SAA1099 generates a variable-amplitude stereo analog signal chopped at a rate of 62,5 kHz. A simple external low-pass filter suppresses the high frequency components of the output signal. The incoming data which shapes the spectrum of the audio output is multiplexed to simplify interfacing, the signal A0 being used to indicate whether the data is a register address, or data for the register. The A0 signal is used with the CS and WR signals to control the data transfers from the microprocessor to the SAA1099. These control signals are compatible with a wide range of microprocessors. In addition, for optimum interfacing with an SCN68000 series microprocessor, the SAA1099 has a DTACK output. All internal timing is derived from an external 8 MHz clock.

| TABLE 2         Function of the A0 input |      |       |     |    |    |    |    |            |                                             |

|------------------------------------------|------|-------|-----|----|----|----|----|------------|---------------------------------------------|

| A0                                       | data | a bus | inp | ut | 14 |    |    |            | function                                    |

|                                          | D7   | D6    | D5  | D4 | D3 | D2 | D1 | D0         | Same and and                                |

| 0                                        | D7   | D6    | D5  | D4 | D3 | D2 | D1 | <b>D</b> 0 | data for internal<br>registers, see Table 3 |

| 1                                        | x    | x     | X   | х  | A3 | A2 | Al | A0         | internal register<br>address, A3 is the MSB |

Table 2 shows the function of the A0 input. When A0 = 1, the bus data indicates the address of the control register in the SAA1099 to be written and this address is loaded into the command register. The next data byte on the bus, which contains the control information for the register that has been addressed, is written to the register when A0 = 0. Once addressed, a control register can be updated without further addressing.

#### **CIRCUIT DESCRIPTION**

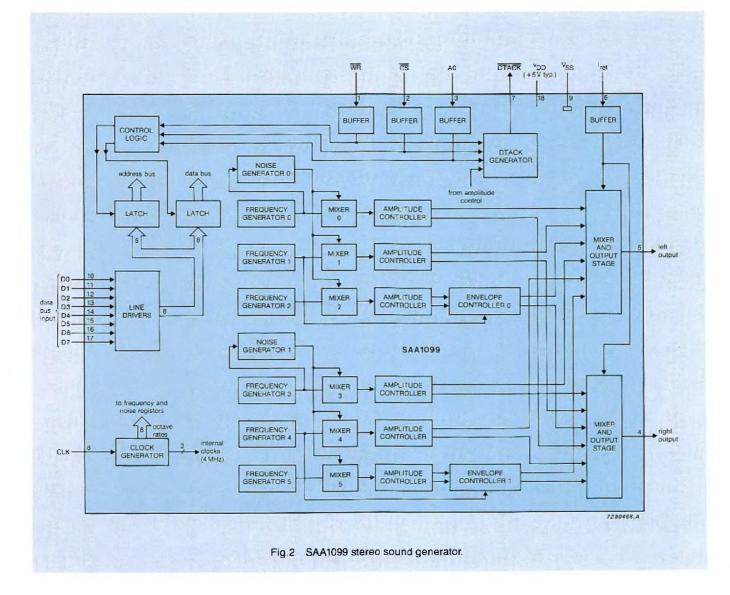

#### Frequency generators

The SAA1099, see Fig.2, has six frequency generators each of which can generate 256 tones in each of eight octaves from 31 Hz to 7,81 kHz. Each generator can be switched on and off individually, making it possible to preselect a tone and to make it audible when required. To simplify the software, the frequency generators can be synchronized at start-up

and when changing frequencies, octaves and envelopes using the frequency reset bit, see 'Synchronization'. The outputs of frequency generators 0 and 3 can each control a noise generator while those of generators 1 and 4 can each control an envelope generator for creating special effects.

Table 3 gives the addresses and the bit allocation of the SAA1099's internal registers used to control the frequency generators and its other sound-generating circuitry.

#### Noise generators

Two noise generators each have a programmable output controlled by the contents of register 16 which determines whether the output is:

- software-controlled via frequency generator 0 or 3 (which then produces no tone). The 'colour' of the noise generated is derived from twice the frequency of the frequency generator output, i.e. from 61 Hz to 15,6 kHz.

- one of three pre-defined noises based on clock frequencies of 7,8 kHz, 15,6 kHz or 31,25 kHz. In this case, the output of noise generator 0 can be mixed with the outputs of frequency generators 0, 1 and 2, and the output of noise generator 1 can be mixed with the outputs of frequency generators 3, 4 and 5, see Fig.2. For mixing, the amplitude of the tone is increased relative to that of the noise.

#### Noise/frequency mixers

The SAA1099 has six mixers, one per frequency generator, for mixing tones with noise. Dependent on the status of bits D0 to D5 of registers 14 and 15, each mixer can be set:

- to mix the noise and the tone

- to pass the tone only

- to pass the noise only

- to pass neither tone nor noise.

#### Amplitude controllers

The SAA1099 has six amplitude controllers used, for example, to create a stereo effect. Each controller duplicates the signal from one of the noise/frequency mixers to form left and right-channel components and assigns one of sixteen amplitudes set by the contents of the control registers 00 to 05 to each component. A stereo effect can be produced simply by varying the amplitude of each component. To move a sound from one channel to another requires, per tone, only one update of the contents of the appropriate amplitude register.

Fig.1 Sound generation system for home computers and video games equipment.

| register  | data bus input                                               |                                                                                          |

|-----------|--------------------------------------------------------------|------------------------------------------------------------------------------------------|

| address   | D7 D6 D5 D4 D3 D2 D1 D0                                      | description/remarks                                                                      |

|           | MSB LSB                                                      |                                                                                          |

| 00        | amp. right channel amp. left channel                         | controller 0                                                                             |

| 01        | amp. right channel amp. left channel                         | controller 1                                                                             |

| 02        | amp. right channel amp. left channel                         | controller 2                                                                             |

| 03        | amp. right channel amp. left channel                         | controller 3                                                                             |

| 04        | amp. right channel amp. left channel                         | controller 4                                                                             |

| 05        | amp. right channel amp. left channel                         | controller 5                                                                             |

| 06        | x x x x x x x x                                              | reserved for possible expansion                                                          |

| 07        | x x x x x x x x x                                            | reserved for possible expansion                                                          |

| 08        | tone number for frequency generator 0                        |                                                                                          |

| 09        | tone number for frequency generator 1                        |                                                                                          |

| 0A        | tone number for frequency generator 2                        | fragmency of tops (Hz) = $15625 \times 2^{\text{octave number}}$                         |

| 0B        | tone number for frequency generator 3                        | frequency of tone (Hz) = $\frac{10025 \times 2}{(511 - \text{tone number})}$ , see notes |

| 0C        | tone number for frequency generator 4                        |                                                                                          |

| 0D        | tone number for frequency generator 5                        |                                                                                          |

| 0E        | x x x x x x x x x                                            | reserved for possible expansion                                                          |

| 0F        | x x x x x x x x x                                            | reserved for possible expansion                                                          |

| 10        | X octave no. of X octave no. of                              | octave $0(0\ 0\ 0)$ : 31 Hz to 61 Hz; octave 1 (0 0 1): 61 Hz to 122 Hz                  |

| 11        | freq. gen. 1 freq. gen. 0<br>X octave no. of X octave no. of | octave 2 (0 1 0): 122 Hz to 244 Hz; octave 3 (0 1 1): 245 Hz to 488 Hz                   |

| 11        | freq. gen. 3 freq. gen. 2                                    | octave 4 (1 0 0): 489 Hz to 977 Hz; octave 5 (1 0 1): 978 Hz to 1,95 kHz                 |

| 12        | X octave no. of X octave no. of                              | octave 6 (1 1 0): 1,96 kHz to 3,91 kHz; octave 7 (1 1 1): 3,91 kHz to 7,81 kHz           |

|           | freq. gen. 5 freq. gen. 4                                    |                                                                                          |

| 13        | x x x x x x x x                                              | reserved for possible expansion                                                          |

| 14        | X X 5 4 3 2 1 0                                              | frequency enable (active-HIGH); 0 to 5 refer to the noise/frequency mixers               |

| 15        | X X 5 4 3 2 1 0                                              | noise enable (active-HIGH); 0 to 5 refer to the noise/frequency mixers                   |

| 16        | X X generator 1 X X generator 0                              | noise generator clock frequency:                                                         |

|           | 0 0 0                                                        | 31,25 kHz                                                                                |

|           | 0 1 0 I                                                      | 15,6 kHz                                                                                 |

|           | 1 0 1 0                                                      | 7,8 kHz                                                                                  |

|           | 1 1 1 1                                                      | 61 Hz to 15,6 kHz (freq. generator 0 or 3 controlling noise generator 0 or 1 respectiv   |

| 17        | x x x x x x x x                                              |                                                                                          |

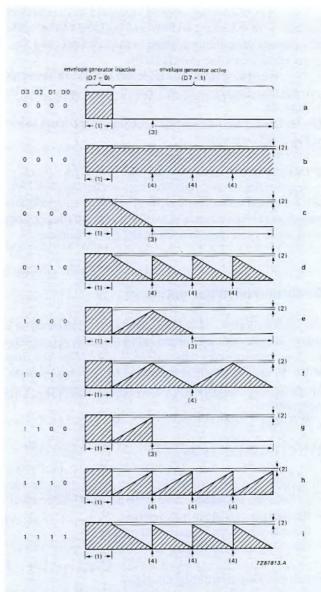

| 18        | envelope generator 0                                         | see Table 4 and Fig. 3                                                                   |

| 19        | envelope generator 1                                         | see Table 4 and Fig. 3                                                                   |

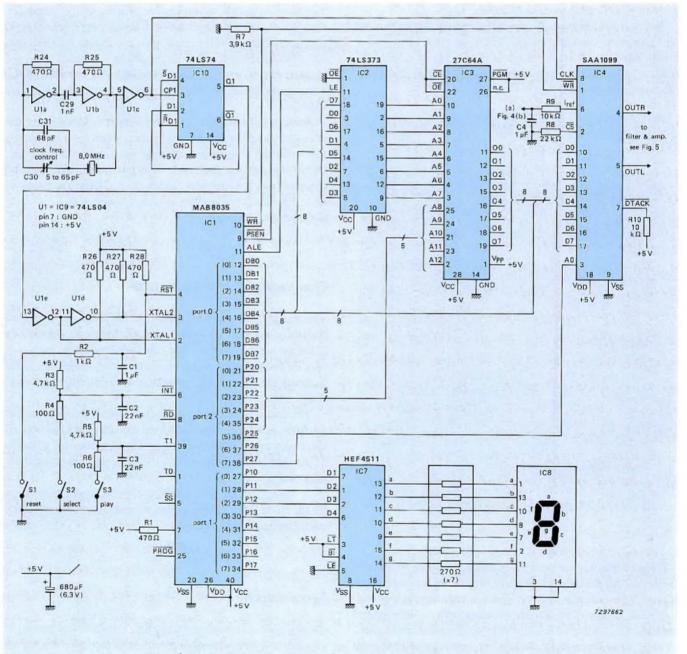

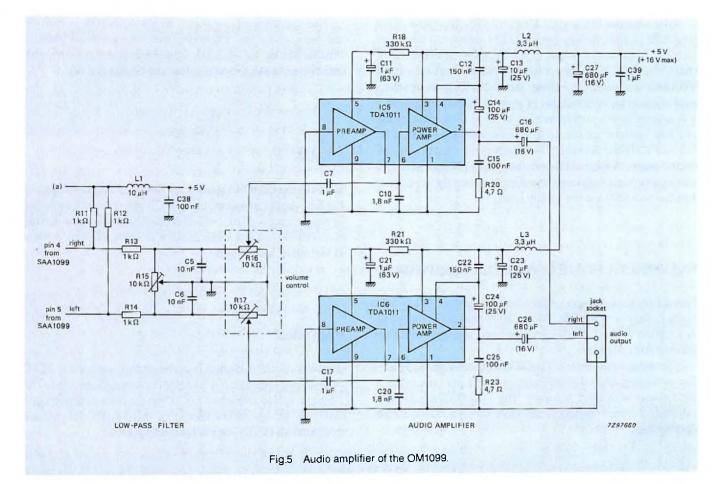

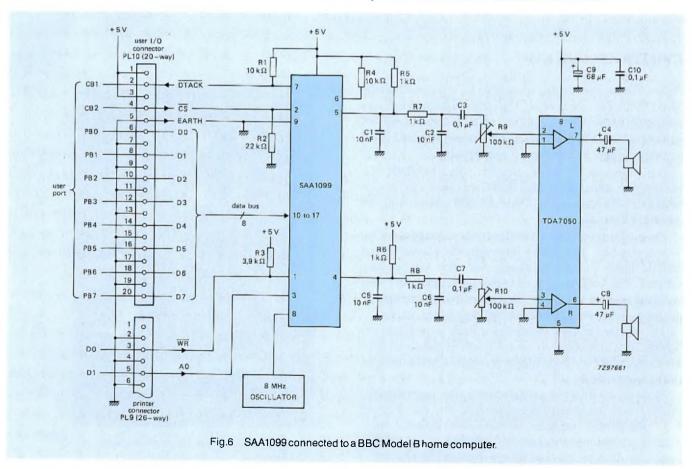

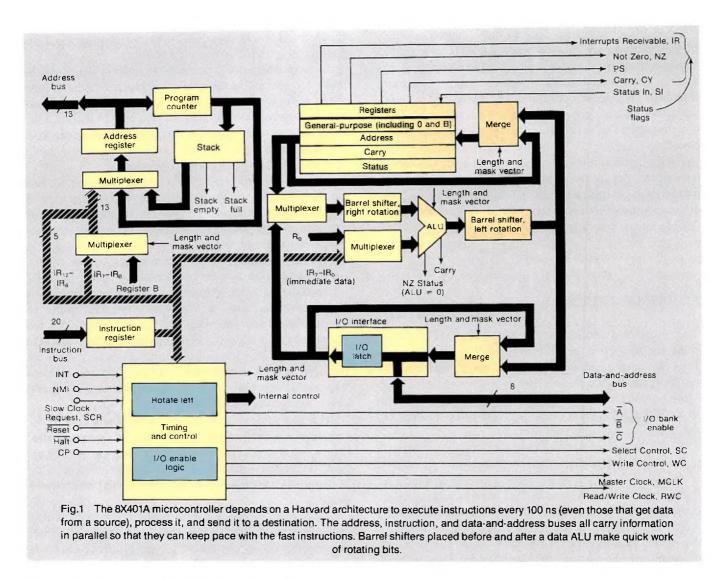

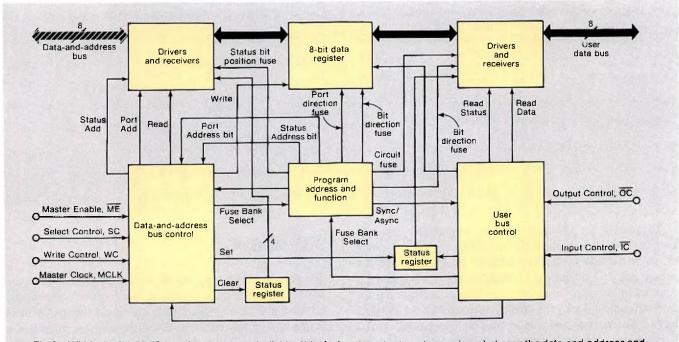

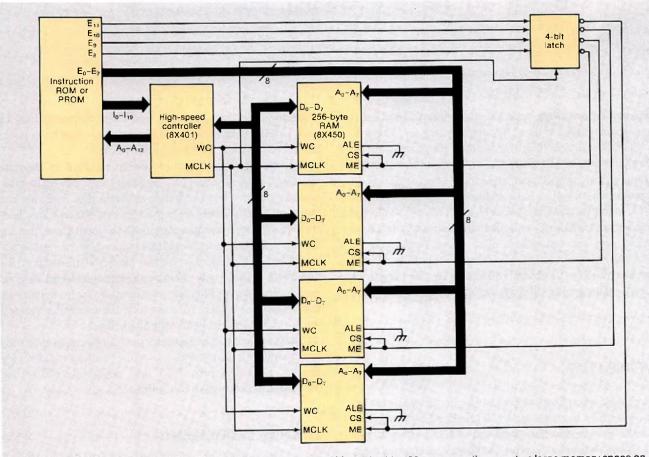

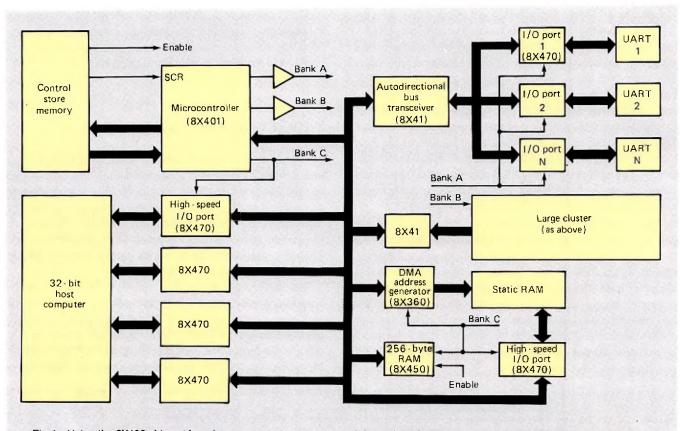

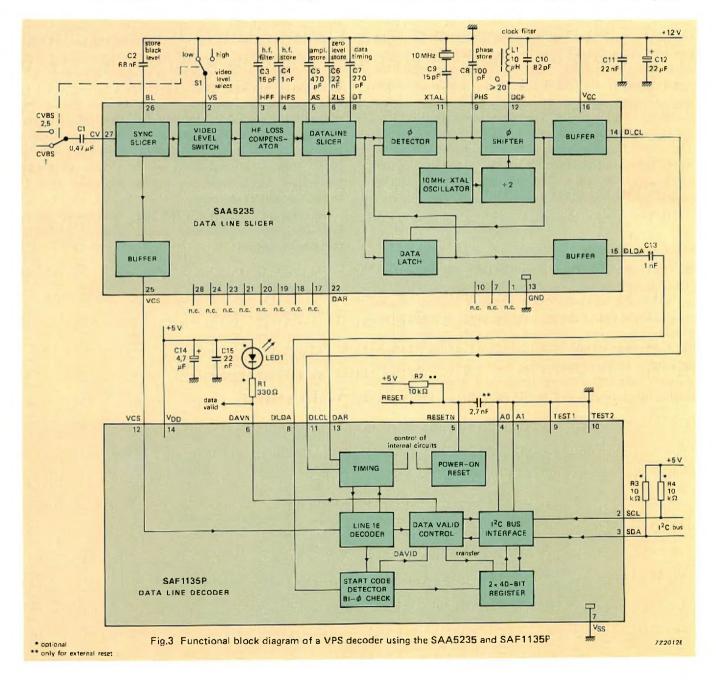

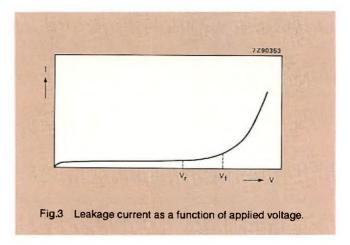

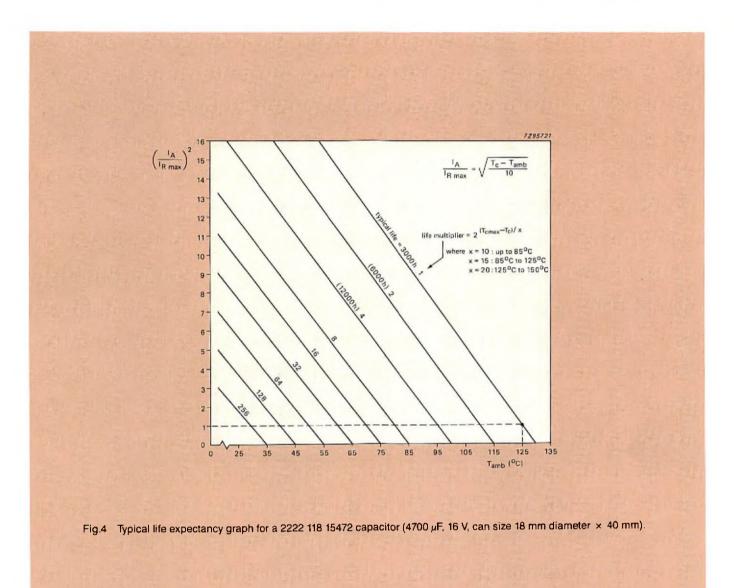

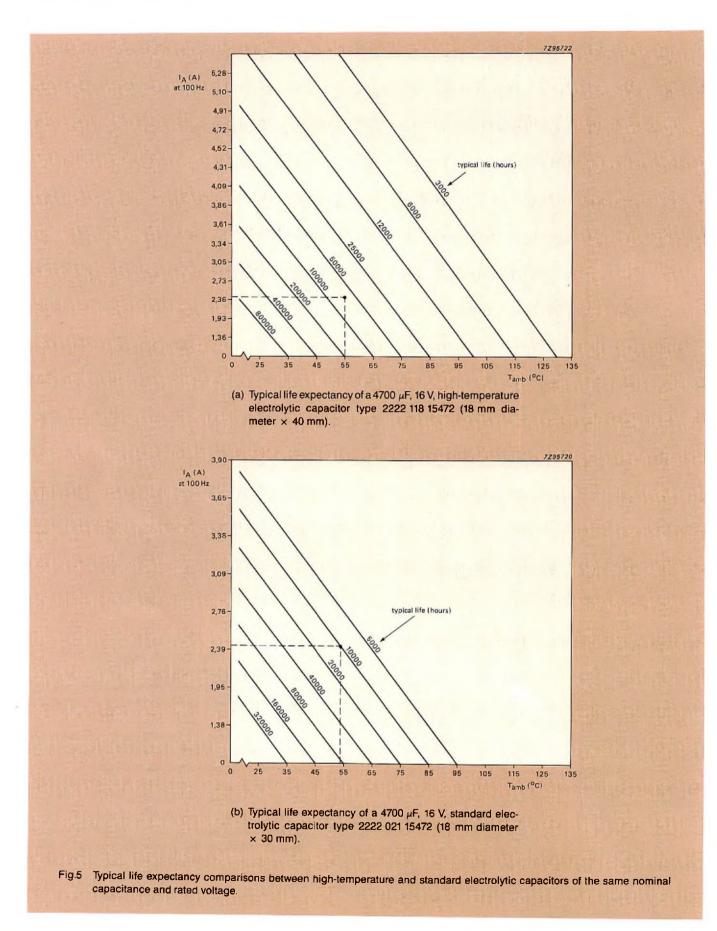

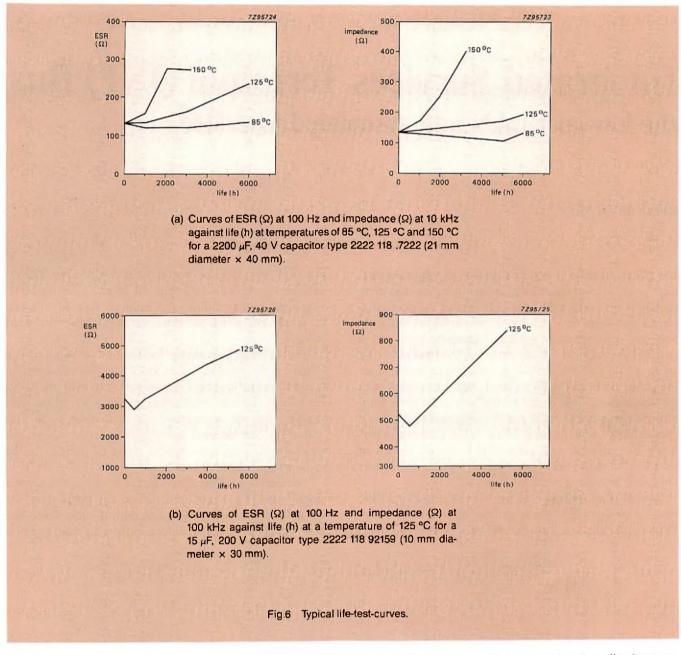

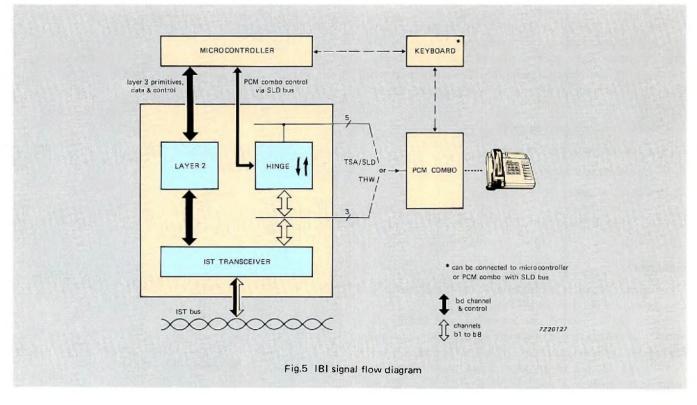

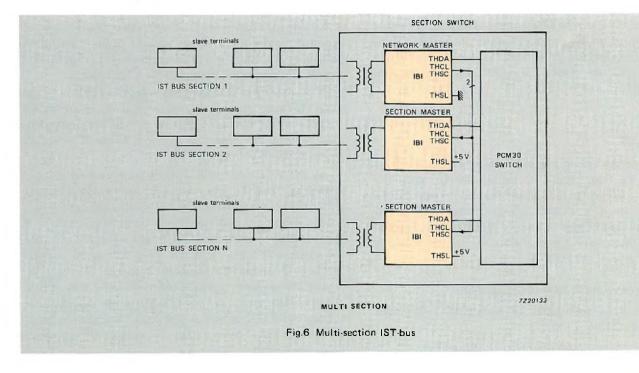

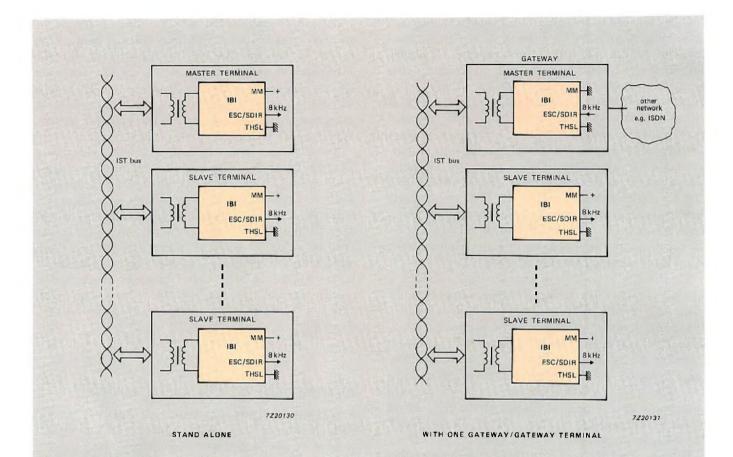

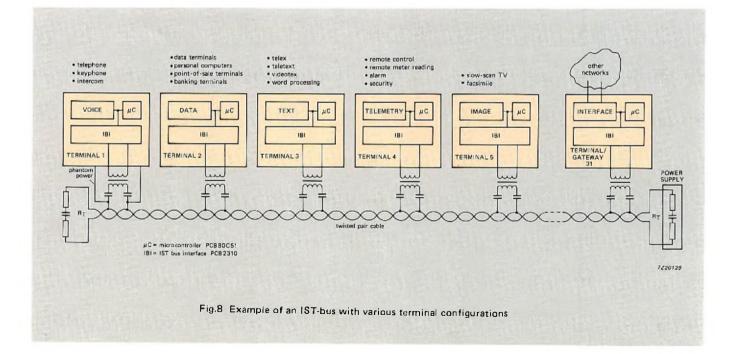

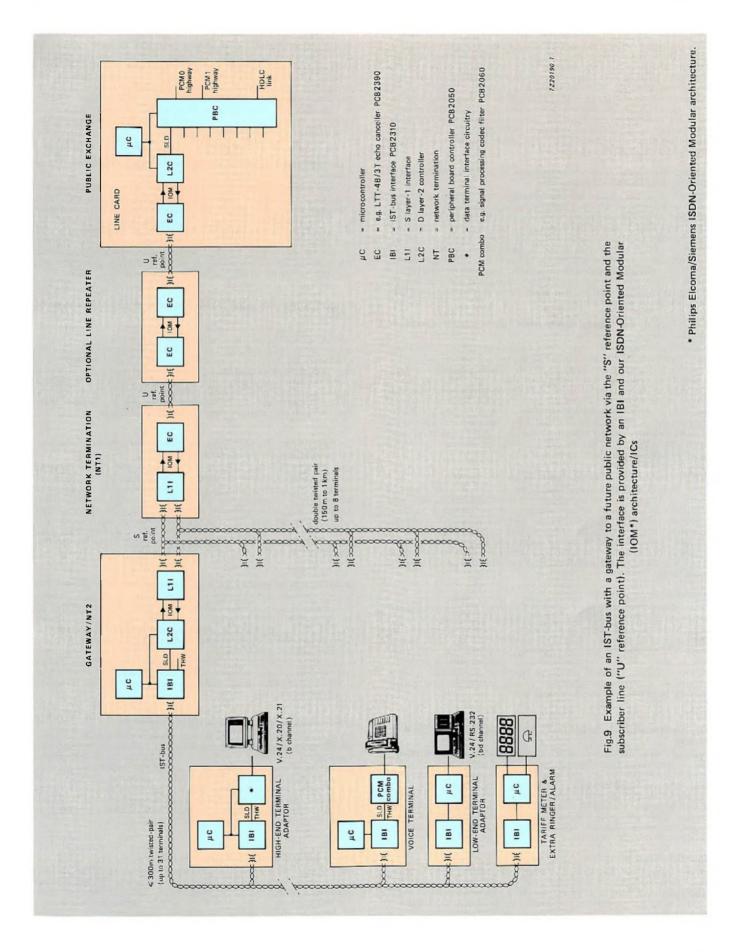

| 1A        | x x x x x x x x                                              |                                                                                          |