# **Electronic components & applications**

# Electronic components & applications

Volume 8, No.3

#### Editor: Ian L. A. Crick

Design and production: Cees J. M. Gladdines Bernard W. van Reenen Jacob Romeijn

Design consultant: Theo Kentie

Ever since the humble transistor radio appeared in the 1950s, Philips has spearheaded development of solid-state entertainment equipment. Colour TVs, radios, analogue and digital cassette recorders, digital TVs and CD players are just some of the items that have emerged. Now, however, the airwaves are so congested that broadcasters need to transmit at such high frequencies that their signals can only be radiated far enough by satellite-borne transmitters. This year sees the launch of the first satellite solely for the re-transmission of public radio, TV and teletext services. From its geostationary orbit 36 000 km above the earth, it will radiate multi-lingual news, sport and entertainment pro-grammes to Western Europe. Once again Philips has met the technological challenge and, with Nordic VLSI and Plessey Semiconductors, has developed a DBS TV transmission decoder and IC set for handling signals encoded in accordance with any of today's European DBS TV transmission standards. The architecture of this advanced decoder, described on page 186, is such that it can also accommodate the requirements of any future TV services.

# Contents

| Two-chip modem for high-speed LAN systems <i>P. M. Shah</i>                                                    | 130 |

|----------------------------------------------------------------------------------------------------------------|-----|

| Multiple-step stress testing proves the reliability of solid aluminium capacitors<br>E. Dekker and H. Schmickl | 137 |

| Third generation decoding ICs for CD players<br>R. Finck and D. Slowgrove                                      | 145 |

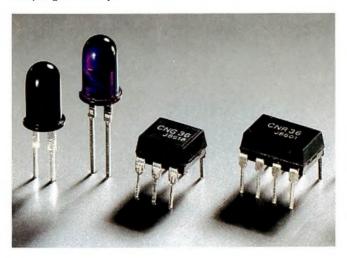

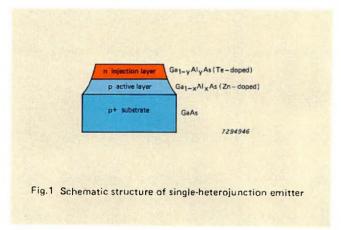

| Single-heterojunction GaAlAs –<br>a new technology for infrared LEDs and optocouplers<br>M. C. Boissy          | 153 |

| Highly-accelerated humidity testing of CMOS ICs<br>W. Nachbauer                                                | 156 |

| New pinouts for ACL add reliability and simplicity<br>to logic systems<br>R. Croes and A. de Pagter            | 167 |

| Video ADCs using folding and interpolation techniques <i>P. Piver</i>                                          | 171 |

| Enhanced computer-controlled Teletext<br>circuit SAA5243<br>J. Kinghorn                                        | 175 |

| First multistandard decoder chip-set for DBS TV                                                                | 186 |

| Research News                                                                                                  | 188 |

| Abstracts                                                                                                      | 189 |

| Authors                                                                                                        | 192 |

|                                                                                                                |     |

All information in Electronic Components and Applications is published in good faith, but the publishers assume no liability for any consequence of its use; its publication does not imply a licence under any patent. Specifications and availability of goods mentioned in it are subject to change without notice.

## **Two-chip modem for high-speed** LAN systems

#### **PRASANNA SHAH**

Modems that employ the frequency-shift-keying (FSK) modulation technique are particularly suitable for LAN applications because of their high noise immunity and amplitude independence, which together yield a low biterror rate. FSK modems are also relatively easy to construct and are, therefore, inexpensive in comparison with those employing more esoteric modulation techniques. Low-speed FSK modems have been available in ICs for some years but, until recently, FSK modems that could operate at speeds higher than 19200 bits/s were available only at the board level and employed many discrete and small-scale-integration (SSI) components.

Now, however, you can obtain a complete, high-speed modem in the form of two ICs: the NE5080 transmitter and the NE5081 receiver. These ICs can provide transmission rates as high as 8 Mbits/s, depending on the attenuation characteristics and the length of the cable used to connect the nodes. For maximum error-free transmission rate, the coaxial cable should be kept short (since transmission rate falls with increasing cable length). Nevertheless, it's still possible to achieve a transmission rate of 500 kbits/s over a 30 000 m length of cable without any repeaters. You can adjust the sensitivity of the receiver to compensate for the cable length and for the noise level of the environment. For a signal-to-noise ratio of 20 dB, the typical error rate of a link using this modem is one in  $10^{12}$  bits.

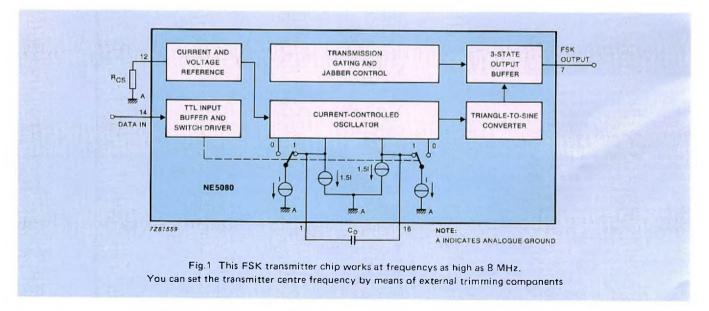

The NE5080 transmitter IC, which consists of six functional blocks (Fig.1), contains an on-chip voltage regulator that provides the current and voltage references used by the internal circuitry. It's possible to adjust the transmitter's centre frequency by selecting appropriate values for the tuning capacitor ( $C_0$ ) and resistor ( $R_{cs}$ ).

The TTL data-input circuits and their associated switchdriver circuits switch the current sources (I) into or out of the circuit according to the current value of the input bit.

The switching process changes the total average current that charges or discharges  $C_0$  from 1.51 to 2.51, or vice versa. The change in current causes the current-controlled oscillator to shift its output from one frequency to another in a manner that keeps the output phase continuous and eliminates sharp discontinuities in the output waveform. This Continuous-Phase FSK (CPFSK) technique has the advantage of confining most of the power to the main lobe of the spectrum; the consequent reduction of the power radiated into the sidebands reduces adjacent-channel interference (Ref.1).

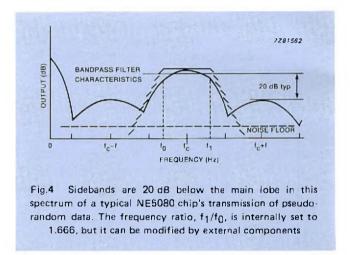

The ratio of the two output frequencies is equal to the ratio of the average currents that charge and discharge  $C_0$ . The values of the current sources are fixed, and they normally yield a constant frequency ratio (f0/f1) of 1.666; however, by adding external components you can modify this ratio, which determines the bandwidth used by a particular channel.

The transmission chip's triangle-to-sine-wave converter circuitry converts the triangular output of the currentcontrolled oscillator to a sine wave with a total distortion of 2% or less. The transmission-gating circuits permit or prevent the transmission of data. The disable function not only puts the 3-state output buffer into the high-impedance state but also shuts off the current-controlled oscillator to prevent any feed-through to the output circuit.

The chip's jabber-control circuits are similar to its transmission-gating circuits, except that the jabber-control circuits provide a means of programming the length of the transmission. This feature acts as a failsafe that prevents a malfunctioning NE5080 transmitter or transmitter controller from tying up the network. To make use of the feature, you can connect an external capacitor from the chip's jabber-control pin (pin 3, not shown in Fig.1) to ground; an internal current source provides a small current to charge this capacitor. When the voltage across the capacitor reaches a preset threshold level, the jabber-control circuits disable the output buffer and shut off the oscillator. For

point-to-point communications, which do not need the jabber-control feature, you can disable the circuitry by grounding pin 3.

#### Adjusting receiver sensitivity

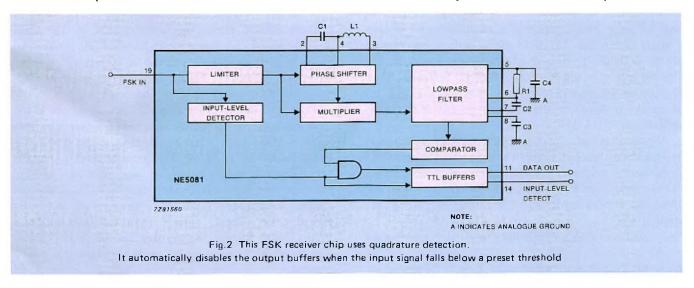

The NE5081 receiver IC (Fig.2), like the NE5080 transmitter, contains an on-chip voltage regulator that provides all the voltage- and current-reference levels needed by the internal circuitry. The input-limiter circuits accept the incoming FSK signal and maintain their output amplitude at a constant level for all input-signal amplitudes ranging from 16 to 1100 mV (rms).

A phase shifter and a balanced analogue multiplier use a quadrature-detection scheme to demodulate the incoming data. To use the receiver IC, you need to select the values of the phase-shifter tank circuit ( $L_I$  and  $C_I$ ) to resonate at the centre frequency of the incoming carrier. To ensure good selectivity, the tank circuit must have a high Q factor. The balanced analogue multiplier accepts both the original amplitude-limited carrier signal and the phase-shifted derivative, and it generates signals containing both the baseband data and high-order harmonics.

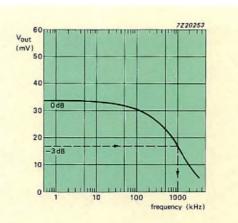

A simple, second-order Butterworth lowpass filter eliminates the original carrier frequency and the high-order intermodulation products. The output of the filter contains only baseband data that is the equivalent of the original data applied to the transmitter at the remote end of the link. External resistors and capacitors allow adjustment of the filter's cutoff frequency.

A comparator determines the status of the input bit by comparing the output of the lowpass filter to a programmable reference threshold. By means of an external resistor, the threshold of the input-level-detection circuitry can be set to correspond to the minimum input-signal amplitude that is detectable above the noise. If the input signal amplitude falls below this preset threshold, the leveldetection circuitry disables the receiver output buffers so

that noise will not be interpreted as data. The level-detection circuitry also generates a flag signal. When the flag is at logic 1, the input-signal amplitude is above the threshold, and the output buffers are presenting valid data.

The transmitter's high drive capability and the receiver's wide dynamic range allow the use of long lengths of cable (both coaxial and twisted pair) without any repeaters.

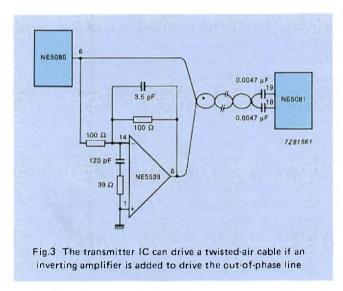

The receiver chip has built-in differential input circuits, so no extra components are needed at that end of the link. The transmitter chip has a single-ended output, so an inverting amplifier is needed to provide the inverted signal to the line. A single amplifier based on an opamp with a wide unity-gain bandwidth (Fig.3) is usually adequate for this purpose. However, if your inverting amplifier causes severe phase delay (which could impair the link's noise immunity or error rate), you'll have to add a matching non-inverting amplifier to drive the in-phase line and restore the phase balance.

Although a link employing these transmitter and receiver ICs has high inherent immunity to noise, some situations may require additional precautions. The ambient electrical-noise level in a factory environment, for example, is much higher than that of an office environment because of the EMI/RFI generated by heavy-duty machines. The bit-error rate of a link is a function of the S/N ratio. Thus, to improve the bit-error rate in a noisy environment, it's necessary to filter out the excess noise power at the receiver input.

Choice of active or passive filters for this purpose will depend upon the signal strength at the receiver input. If the signal strength is great, you can use an inexpensive passive LC bandpass filter. For low signal levels, an active filter will boost the in-band signal while attenuating the out-of-band noise.

If you elect to use a passive filter, keep the Q factor of the circuit as high as possible. To minimize the attenuation of the in-band signal, make sure that the Q factor is at least 35.

The filter's characteristics will depend upon the spectrum of the transmitted signal.

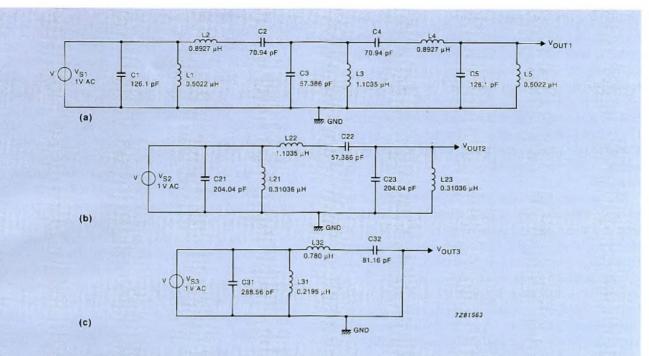

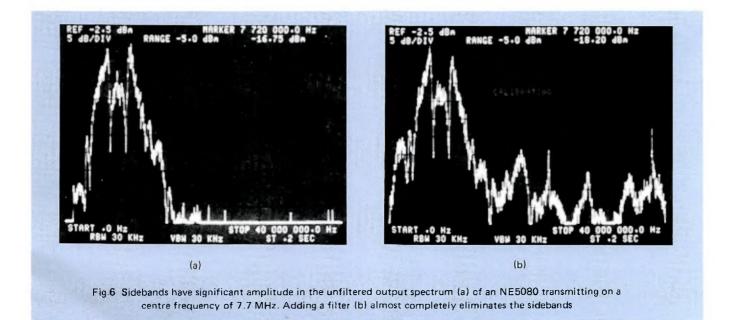

Figure 4 shows a typical spectrum at the output of an NE5080 that is transmitting a pseudorandom data stream. The figure indicates the filter characteristics needed to eliminate the sidebands and out-of-band noise. You can use 2-, 3-, or 5-pole Butterworth passive filter for this purpose (Fig.5). Figure 6 shows the actual spectra obtained in a test of the chip's transmission of a pseudorandom data stream at 7.7 MHz, with and without the 5-pole filter. This filter attenuates the sidebands and the out-of-band noise by more than 40 dB, so it yields a much-improved S/N ratio and a lower bit-error rate.

When designing active filters for a high-frequency carrier, be sure to pick an amplifier with the widest possible unity-gain bandwidth: the NE5539, for example, is well suited to this application because of its 350 MHz unitygain bandwidth (Ref.2).

You can extend the principle of filtering sidebands and out-of-band noise to create a multichannel frequencydivision-multiplexed (FDM) system. The modem chip set can work over a wide range of centre frequencies (from less than 50 kHz to more than 20 MHz). Thus, it's possible to connect several transmitter/receiver pairs to the same coaxial cable to provide a multichannel FDM system. An appropriate filter at each transmitter output and receiver input can eliminate crosstalk between the channels. This capability is important for several reasons.

First, an FDM system makes efficient use of one of the most expensive components in any digital communications network — the cable. Second, you can use the same printboard layout for all of the FSK modems on the network; to change the centre frequency, you need only modify the values of a few resistors and capacitors. Third, you can upgrade the speed of any node on the network merely by removing the existing modem board and substituting a similar board that you've adjusted for the desired speed. You won't have to make any other hardware or software changes.

Fig.5 These Butterworth filters are tuned to 20 MHz. The 2-pole version (a) is often adequate for a frequency ratio of 1.666. For smaller ratios, you'll need the sharper cutoff of the 3-pole (b) or 5-pole (c) versions in order to eliminate the sidebands

When you select the centre frequencies of the various channels in an FDM network, make sure that the higher channels avoid the harmonics of the lower channels. For example, the centre frequency of the first channel can be set to approximately 50 kHz, which will permit the channel to operate at a rate of 19.2 kbits/s. Because the frequency ratio  $(f_0/f_1)$  is 1.666, the band edges of this channel fall at 25 kHz and 75 kHz, so the total bandwidth is 50 kHz.

You can set the second channel's centre frequency at 455 kHz. The band edges of this channel fall at 250 kHz and 750 kHz, so the bandwidth is 500 kHz, which permits a data rate of approximately 192 kbits/s. You can centre the third channel at 5 MHz, yielding a data rate of approximately 2 Mbits/s, and the fourth channel at 21 MHz, yielding a data rate of about 8 Mbits/s. Careful filtering of the sidebands in each channel will ensure high data integrity and will improve the overall performance of the system.

#### Modifying the frequency ratio

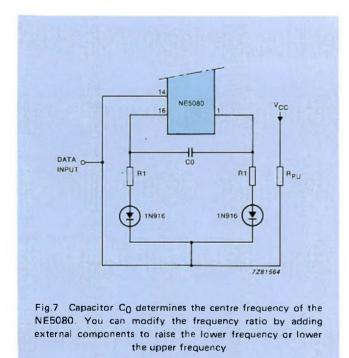

Although the frequency ratio,  $f_0/f_1$  of the NE5080 transmitter is internally set at 1.666, you can change the ratio by raising the lower frequency ( $f_0$ ) or by lowering the upper frequency ( $f_1$ ). As a result, the main lobe of the spectrum is narrower, and the bandwidth occupied by the channel is reduced. There's a tradeoff to consider, however. The reduced bandwidth of each channel allows the cable to accommodate more channels but results in a poorer noise margin; thus, the probability of a bit error is slightly increased.

The technique for raising the lower frequency is shown in Fig.7. When the data input is a logic 1, the input line is held at 5 V through the pullup resistor, RpU, and the two diodes are reverse-biased. Under these conditions, capacitor  $C_0$  is charged and discharged from the IC's internal current sources. When the data input goes to a logic 0, the input voltage drops to almost 0V and the two diodes become forward biased. As a result, the total current available for charging and discharging capacitor  $C_0$  increases, and the output frequency of the current-controlled oscillator falls.

The value of the two matched resistors  $(R_1)$  determines the amount of additional current available, and thus the  $f_0/f_1$  ratio. It's essential that a close match be maintained between the two resistors to avoid excessive distortion at the FSK output. In selecting diodes for this application, consider their switching speed and capacitance; the 1N916 is fast and has a capacitance of only 2 pF, but even faster diodes with lower capacitance (such as the FD777) are available. In making any modifications to Fig.7's circuit you'll have to take into account the stability of the ratio for a specific value of  $R_1$  over a wide range of centre frequencies. It's evident from Fig.8 that a channel's deviation ratio remains constant for a fixed value of  $R_1$  over a wide range of values for capacitor C<sub>0</sub>. Note, however, that if you reduce the deviation from the centre frequency, you'll also reduce the maximum data rate for that channel. Likewise, increasing the frequency ratio will increase the possible data rates, but at the cost of extra bandwidth. If you reduce the frequency ratio, you'll also have to increase the Q factor of the receiver tank circuit so that the main lobe of the resonant circuit becomes narrower, thus corresponding to the main lobe of the modified transmitter spectrum.

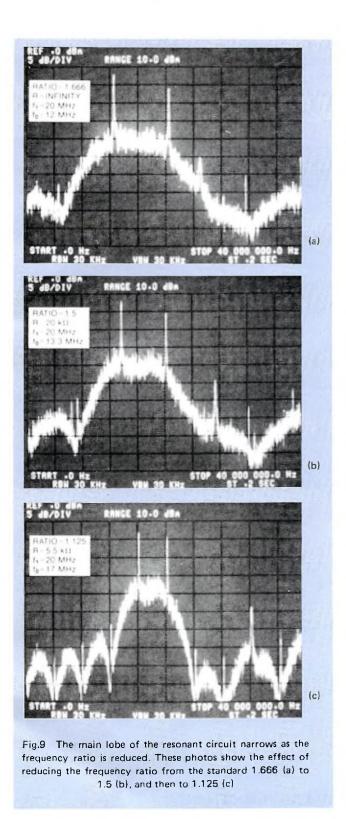

You can see the effect of reducing the frequency ratio in the spectrum photographs (Fig.9). The main lobe grows progressively narrower, and so the filter must have a sharp cutoff to ensure that the sidebands are attenuated by at least 60 dB with respect to the main lobe. You'll need to use a Butterworth filter with five or more poles, or a Chebyshev or ripple filter that provides even sharper cutoff than the Butterworth type does.

If you use a  $20 k\Omega$  resistor in the circuit shown in Fig.7, you'll get a frequency ratio of 1.5, as the curve in Fig.8 shows. This ratio allows you to use a 30 MHz cable to accommodate six channels instead of four. If you reduce the ratio even further (for example, to 1.125), the same total bandwidth can accommodate many more channels.

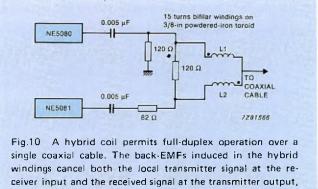

#### A hybrid coil provides full-duplex capability

It's possible to make even more efficient use of cable resources. So far, all the applications discussed have required two cables for full-duplex communication (simultaneous transmission and reception by a given channel). However, full-duplex communication is possible over a single coaxial cable by adding a hybrid coil (Fig.10). The hybrid coil consists of 15 turns of 0.5 mm or 0.4 mm bifilar windings on a powdered-iron toroid core.

so that the signals do not interact

The sinusoidal signal from the NE5080 transmitter enters the hybrid at the dotted terminal of winding L<sub>1</sub>. Because of the mutual inductance of the windings, the transmitter signal induces an equal and opposite signal in winding L<sub>2</sub>, which cancels the transmitter signal that reaches the receiver through the 120 $\Omega$  resistor. Similarly, received signals entering the dotted terminal of winding L<sub>2</sub> create an equal and opposite signal in winding L<sub>1</sub>. Hence, the incoming signal goes directly to the NE5081 receiver without interacting with the transmitted signal. The resistances shown in the schematic yield an effective termination resistance of 75  $\Omega$ .

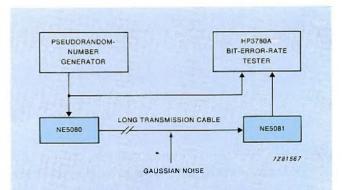

The bit-error rate is the measure of data integrity within any data-communications network, so you should include a test of this parameter in your design procedures. A typical method of testing bit-error rate is to compare the bit stream applied directly to a bit-error-rate tester with the same bit stream that has passed through a modem link (Fig.11).

Fig.11 To determine a link's error rate – which is a function of its S/N ratio – you can use an error-rate tester to compare the bits sent with the bits received over the link, or you can examine the eye pattern at pin 8 of the NE5081 receiver

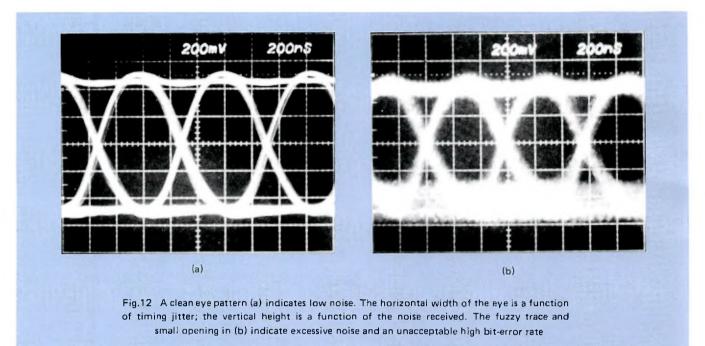

There's another quick and easy way to evaluate the performance of the link, a method that doesn't require a bit-error-rate tester. Simply connect the pseudorandomnumber generator, the transmitter, the cable, and the receiver, to establish a data link carrying a pseudorandom bit stream. Then connect an oscilloscope to the receiver at pin 8, from which you can obtain an "eye" pattern (Fig.12). If the eye pattern looks clean, you can be fairly certain that the system is relatively noise- and error-free. A fuzzy pattern with small openings indicates excessive noise, which would probably lead to data errors.

#### REFERENCES

- FREEMAN, ROGER L, Telecommunication Transmission Handbook, 2nd ed., John Wiley & Sons, New York, N.Y., 1981, p. 601-606.

- 2. Signetics Linear LSI Data and Applications Manual AN140, Signetics Corp., 1985.

- 3. Signetics Linear LSI Data and Applications Manual AN195, Signetics Corp., 1985.

#### ACKNOWLEDGEMENT

The author is sincerely thankful to Michael Sera for his help in the passive bandpass filter designs, simulations, and applications testing.

This article originally appeared in the March 31 issue of EDN, copyright 1987, Cahners Publishing Co.; permission to publish is gratefully acknowledged.

# Multiple-step stress testing proves the reliability of solid aluminium capacitors

#### EVERT DEKKER and HELFRIED SCHMICKL

The technology of solid aluminium (SAL) electrolytic capacitors is backed by several decades of user experience. Because of their well-earned reputation for reliability, longlife and resistance to temperature extremes, they have secured a large share of the professional and industrial capacitor market. In comparison with more expensive tantalum capacitors their only disadvantage was that they were bulkier. This has been eliminated by new developments in aluminium etching (incorporated in our new 123 series) resulting in SALs which are half their previous size. This makes them comparable to tantalum capacitors of the same CV product. Moreover, the foil winding technique used in the 123 series promises SAL capacitors with CV products previously the exclusive domain of wet electrolytics.

Testing of solid aluminium capacitors has exposed no failure mechanisms. (A failure mechanism, as defined by IEC publication 271, is a physical, chemical or other process which ultimately results in failure). Wet aluminium electrolytic and solid tantalum capacitors, however, both display inherent failure mechanisms.

Determination and assessment of reliability in new components such as the 123-series capacitors is a time-consuming process when using conventional testing methods. Instead we use a technique of evaluating the useful life of components by applying a series of simultaneous stress tests, and increasing the levels of stress in stages to induce failure. This process, known as *multiple-step stress testing*, can achieve in weeks, results that would normally take months, or even years, of standard life-tests. To prove the validity of this form of testing, the results obtained from endurance tests of the earlier 121 series were compared with the results of multiple-step stress testing of components in this same series.

### SOLID ALUMINIUM ELECTROLYTIC CAPACITORS

Solid aluminium electrolytics have no known inherent wear-out failure mechanisms; their use can increase overall system reliability. In addition, their electrical and thermal characteristics remain constant throughout a very long life. These characteristics are far superior to those of wet aluminium electrolytics and are comparable, indeed in many respects superior, to those of tantalums, see Table 1. A brief description of the construction of the 123-series capacitors is given in the panel on page 141.

#### Failure mechanisms

Tantalum, wet aluminium and SAL electrolytic capacitors have been available long enough for complete endurance tests to have been carried out. The failure mechanisms (where they exist) of each type have also been documented.

Field crystallization of the essentially amorphous tantalum oxide dielectric is the basic failure mechanism of solid tantalum capacitors (Ref.1). The growth of these higher conductivity oxide crystals during operation of the capacitors causes an increase in leakage current. The capacitor eventually short-circuits, and, since crystalline growth is primarily dependent on applied voltage, high voltage capacitors are more susceptible to failure. The effect of field crystallization can be minimized by using high-purity tantalum to reduce the number of crystallization nucleation sites (an impurity in the crystal grid).

For wet aluminium electrolytic capacitors, the failure mechanism is a gradual drying out of the electrolyte, reducing capacitance and increasing impedance until, eventually, the capacitor goes open-circuit.

|                                                                 | wet aluminium                        | solid tant                    | alum                                        | solid alun                    | ninium                            |

|-----------------------------------------------------------------|--------------------------------------|-------------------------------|---------------------------------------------|-------------------------------|-----------------------------------|

|                                                                 | (Ta replacement<br>types)            | axial leads                   | radial leads                                | axial leads                   | radial leads                      |

| temperature range (°C)                                          | -40 to +85                           | -55 to +125                   | 55 to +85/125*                              | -80 to +250                   | -80 to +175                       |

| effect of temp. derating on life<br>and failure rate            | significant                          | significant                   | significant                                 | negligible                    | negligible                        |

| voltage derating above 85 °C                                    | not usable                           | 2/3 of U <sub>R</sub>         | 2/3 of UR                                   | not required                  | 40 V types only                   |

| effect of voltage derating on<br>life and failure rate          | negligible                           | significant                   | significant                                 | slight                        | slight                            |

| inrush current                                                  | large                                | small                         | small                                       | small                         | small                             |

| allowed reverse DC<br>– level<br>– duration                     | 1 V<br>brief                         | 5% of U <sub>R</sub><br>brief | 5% of U <sub>R</sub><br>brief               | 30% of UR continuous          | 30% of UR<br>continuous           |

| guaranteed life (h)<br>– at 85 °C<br>– at 125 °C<br>– at 155 °C | 2000<br>not usable<br>not usable     | 2000<br>2000<br>not usable    | 1000/2000*<br>not usable/2000<br>not usable | 8000<br>8000<br>5000          | 5000<br>2000<br>2000              |

| ailure mechanism                                                | drying out of electrolyte            | field<br>crystallization      | field<br>crystallization                    | none known                    | none known                        |

| ailure rate (U <sub>R</sub> , 125 °C,<br>0 Ω/V, 60% confidence) | 10 <sup>-6</sup> /h (85 °C)<br>≤2 kh | 10 <sup>-s</sup> /h<br>≤2 kh  | 3 x 10 <sup>-s</sup> /h<br>≤2 kh            | 10 <sup>-7</sup> /h<br>≤20 kh | 5 x 10 <sup>-</sup> ′/h<br>≤10 kh |

The testing of SAL electrolytics has so far failed to reveal any failure mechanism, either short-circuit or opencircuit (Ref.2). In fact, these capacitors can actually improve with age, as the leakage current decreases during the life of the capacitor. This is in total contrast to both wet aluminium and solid tantalum electrolytics, which have intrinsic failure mechanisms that ultimately result in the breakdown of the capacitor.

#### Multiple-step stress testing of SALs

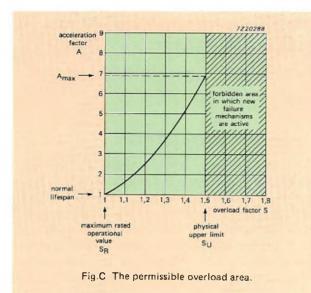

The first consideration for setting up a multiple-step stress test for a SAL electrolytic capacitor is to determine which stress factors affect the lifetime. For each stress factor, the maximum rated operational value (SR), and the physical upper limit (SU, above which the component will be subject to new failure mechanisms rather than failure due to accelerated ageing), are to be specified. The difference between SU and SR for each factor is divided into 10 equal steps.

For the duration of the first test period, the capacitors are subjected to all stress factors at their absolute maximum rated operational value, after which they are checked for conformity to specification. Each stress parameter is then increased to  $S_R + 0,1 (S_U - S_R)$  for the next test period and the capacitors are checked at the end. For the third period, the stress parameters are raised to  $S_R + 0.2 (S_U - S_R)$ , and so on until they are tested at their physical upper limit (SU) for the duration of the last (the eleventh) test period.

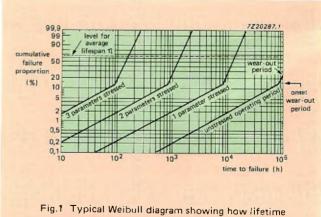

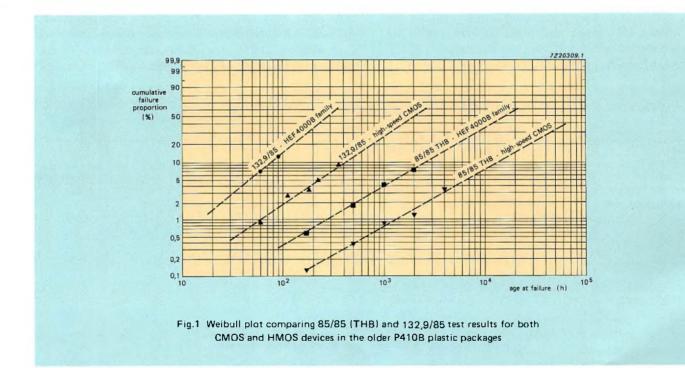

It is important that all stress parameters are increased at the same time for each step in order to cause an exponential increase of the test severity (see Appendix) and hence an exponential reduction of the lifetime. This is illustrated in the typical Weibull diagram of Fig.1.

decreases as the number of stressed parameters increases

#### MULTIPLE-STEP STRESS TESTING OF SALS

|                                                        | Ele                    | ectrical da    | TABLE 2<br>ta for SAL electrol                             | ytics under test                                          |               |             |                              |

|--------------------------------------------------------|------------------------|----------------|------------------------------------------------------------|-----------------------------------------------------------|---------------|-------------|------------------------------|

|                                                        | nominal<br>capacitance | UR             | max. RMS<br>ripple current<br>at T <sub>amb</sub> = 125 °C | max. leakage<br>current at U <sub>R</sub><br>after 1 min. | max.<br>tan δ | max.<br>ESR | max. impedance<br>at 100 kHz |

| device [1] 2222 121 13331<br>device [2] 2222 123 13102 | 330 μF<br>1000 μF      | 6,3 V<br>6,3 V | 430 mA<br>760 mA                                           | 150 μΑ<br>440 μΑ                                          | 0,18<br>0,18  | 1,1<br>0,36 | 0,2<br>0,2                   |

When the life expectancy of a component is known from years of conventional life testing, that of a new component of like technology can be predicted accurately and quickly by multiple-step stress testing both components and comparing the results obtained. Additionally, any inherent defects in the new component design which could cause failure mechanisms can be identified early in development and eliminated.

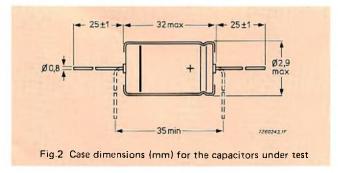

To establish the life expectancy of the 123-series SAL, we tested a  $1000\,\mu\text{F}$  123-series capacitor and a  $330\,\mu\text{F}$ 121-series capacitor according to the multiple-step stress test; the 121-series capacitor, for which there are 15 years of life-test results, being the reference. Both capacitors have the same case, the dimensions of which are shown in Fig.2. Electrical data for both samples are given in Table 2. The stress factors for the test are based on the supposed physical limits of the 123-series, and the full test schedule and measured results are given in Table 3.

The measured results show stability of all parameters with no trend toward deterioration. There were no complete failures and no evidence of a failure mechanism in either the 121-series reference capacitor or the 123-series test capacitor.

Two conclusions can be drawn from these results: the new 123-series capacitors are as reliable as the earlier and larger 121-series; and the supposed physical limits of the 123-series are not the real limits. In particular, a much higher ripple voltage can be superimposed on the DC voltage. Furthermore, the ripple current can be higher. This has been verified by a subsequent thermal and electrical analysis (Ref.3). Finally, the leakage current (specified as a function of the CV product) is the same as for the 121-series capacitors. This has all been included in the new product specification.

## Reliability and life expectancy of SAL electrolytic capacitors

Experience indicates that the stress parameters most likely to influence the reliability and useful life of SAL electrolytics are temperature and applied voltage. The results of the above tests on the 123-series capacitors show that it's permissible to go up to, and even exceed, the supposed limits of both these stress parameters without the capacitor failing. Therefore, it is reasonable to say that the true upper temperature limit for SAL electrolytic capacitors is above 175 °C. This is supported by field results taken at 250 °C (see Ref.10).

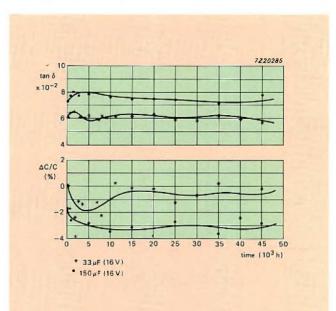

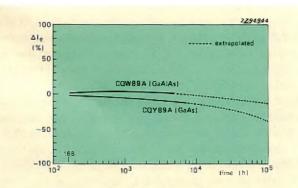

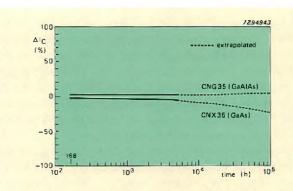

From the test results described here, and confirmed by simple endurance testing, at a temperature of 175 °C and a rated voltage (UR) of 6,3 V, these capacitors have a predicted useful life greater than 2000 hours. Moreover, life expectancy falls exponentially with operating temperature (see Appendix). For example, at 125 °C and 6,3 V, the life expectancy is more than 50000 hours. Figure 3 shows the results on parameter values after 45000 hours endurance testing, comparing again the 121 and 123 ranges.

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | W                                                                                                 | Multiple-step stress test results for axial solid aluminium capacitors         | p stress t                                                                    | est results                                                                                                                                                                                                                                                                                                                   | s for axia                                                     | l solid alı                   | uminium      | capacitor     | S             |               |               |               |                             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|-------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|-------------------------------|--------------|---------------|---------------|---------------|---------------|---------------|-----------------------------|

| stress step<br>time (h)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                   | 1<br>24                                                                        | 2<br>24                                                                       | 3<br>24                                                                                                                                                                                                                                                                                                                       | 4<br>72                                                        | 5<br>24                       | 6<br>24      | 7<br>24       | 8<br>24       | 9<br>72       | 10<br>24      | 11<br>24      | physical<br>limit           |

| stress factor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | device1)                                                                                          |                                                                                |                                                                               |                                                                                                                                                                                                                                                                                                                               |                                                                |                               |              |               |               |               |               |               |                             |

| DC voltage (V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | [1]<br>[2]                                                                                        | 6,3<br>6,3                                                                     | 6,8<br>6,8                                                                    | 7,3<br>7,3                                                                                                                                                                                                                                                                                                                    | 7,8<br>7,8                                                     | 8,3<br>8,3                    | 8,8<br>8,8   | 9,3<br>9,3    | 9,8<br>9,8    | 10,3          | 10,8<br>10,8  | 11,3<br>11,3  | 28,8 <sup>2</sup> )<br>11,5 |

| ambient temperature (°C)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | [1]<br>[2]                                                                                        | 125<br>125                                                                     | 130<br>130                                                                    | 135<br>135                                                                                                                                                                                                                                                                                                                    | 140<br>140                                                     | 145<br>145                    | 150<br>150   | 155<br>155    | 160<br>160    | 165<br>165    | 170<br>170    | 175<br>175    | 175 <sup>3</sup> )<br>175   |

| RMS ripple current (mA)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | [1] <sup>6</sup> )<br>[2]                                                                         | 342<br>940                                                                     | 380<br>1040                                                                   | 420<br>1140                                                                                                                                                                                                                                                                                                                   | 1240<br>1240                                                   | 1340<br>1340                  | 1440<br>1440 | 1500<br>1540  | 1500<br>1640  | 1500<br>1740  | 1525<br>1840  | 1540<br>1940  | 1370*)<br>1290              |

| RMS ripple voltage (V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | [1]<br>[2]                                                                                        | 1,5<br>1,24                                                                    | 1,65<br>1,34                                                                  | 1,8<br>1,47                                                                                                                                                                                                                                                                                                                   | 5,24<br>1,65                                                   | 5,61<br>1,77                  | 5,9<br>1,9   | 6,0<br>2,1    | 6,0<br>2,1    | 6,0<br>2,2    | 6,0<br>2,38   | 6,0<br>2,56   | 12,4 <sup>5</sup> )<br>0,1  |

| peak ripple voltage (V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | [1]<br>[2]                                                                                        | 2,1<br>1,8                                                                     | 2,3<br>1,9                                                                    | 2,5<br>2,1                                                                                                                                                                                                                                                                                                                    | 7,4<br>2,3                                                     | 7.9<br>2.5                    | 8,3<br>2,7   | 8,5<br>3,0    | 8,5<br>3,0    | 8,5<br>3,1    | 8,5<br>3,4    | 8,5<br>3,6    | 17,5 <sup>5</sup> )<br>0,2  |

| sum of DC voltage + peak ripple voltage<br>as multiplier on UR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | [1]<br>[2]                                                                                        | 1,3<br>1,3                                                                     | 1,4<br>1,4                                                                    | 1,6<br>1,5                                                                                                                                                                                                                                                                                                                    | 2,4<br>1,6                                                     | 2.6<br>1,7                    | 2,7<br>1,8   | 2,8<br>2,0    | 3,0<br>2,1    | 3,0<br>2,1    | 3.1<br>2,3    | 3,1<br>2,4    | 4,6<br>1,8                  |

| measured results?)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                   |                                                                                |                                                                               |                                                                                                                                                                                                                                                                                                                               |                                                                |                               |              |               |               |               |               | sp            | specification.)             |

| leakage current as multiplier on CV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | [1]                                                                                               | 0,006 0,025                                                                    | 0,006<br>0,024                                                                | 0,005<br>0,024                                                                                                                                                                                                                                                                                                                | 0,004                                                          | 0,003 0,017                   | 0,003        | 0,002 0,013   | 0,002 0,012   | 0,001 0,012   | 0,002 0,018   | 0,002 0,018   | 0,1                         |

| $\Delta C$ as a % of initial capacitance at 100 kHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | [1]<br>[2]                                                                                        | -2,2<br>-2,2                                                                   | -2,7<br>-2,9                                                                  | -3,1                                                                                                                                                                                                                                                                                                                          | -7,3                                                           | -9,6<br>-4,4                  | -11,0        | -13,6<br>-5,2 | -14,9<br>-5,5 | -16,1<br>-5,7 | -15,7<br>-5,9 | -15,3<br>-6,2 | 10%                         |

| tan & (dissipation factor as a % at 100 Hz)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | [1]<br>[2]                                                                                        | 4,4<br>17,2                                                                    | 4,5<br>17,2                                                                   | 4,8<br>17,0                                                                                                                                                                                                                                                                                                                   | 6,6<br>16,8                                                    | 9,8<br>18,6                   | 9,0<br>18,2  | 9,9<br>18,5   | 9,5<br>18,4   | 10,0<br>18,2  | 9,8<br>18,6   | 8,6<br>16,5   | 22%                         |

| impedance at 100 kHz (mΩ)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | [1]<br>[2]                                                                                        | 93<br>150                                                                      | 94<br>147                                                                     | 91<br>141                                                                                                                                                                                                                                                                                                                     | 83<br>132                                                      | 87<br>138                     | 82<br>136    | 84<br>139     | 86<br>134     | 90<br>137     | 92<br>141     | 80<br>128     | 240                         |

| Device type [1] – Axial lead solid aluminium capacitor series 121, 330 $\mu$ F, UR = 6,3 V.<br>Device type [2] – Axial lead solid aluminium capacitor series 123, 1000 $\mu$ F, UR = 6,3 V.<br>Voltage limit is 60% of the anode foil forming voltage.<br>Temperature limit: at 175 °C discolouration of the tin and insulation occurs, the capacitors can electrically go beyond t<br>Ripple current limit is derived from an inner temperature 20 °C higher than ambient.<br>For the 330 $\mu$ F reference capacitor (device [1]), the ripple current setting was hampered by power supply limitations.<br>Average of six samples. | nium capac<br>nium capac<br>ming volta<br>ion of the t<br>ner temper<br>between li<br>ce [1]), th | itor series<br>ge.<br>in and insu<br>ature 20°C<br>mit value a<br>e ripple cur | 121, 330,<br>123, 1000<br>lation occ<br>higher th<br>nd applicd<br>rent setti | or series 121, 330 $\mu$ F, UR = 6,3 V.<br>or series 123, 1000 $\mu$ F, UR = 6,3 V.<br>and insulation occurs, the capacitors can electrically go beyond this temperature.<br>ure 20°C higher than ambient.<br>it value and applied value of the voltage.<br>it pple current setting was hampered by power supply limitations. | ,3 V.<br>6,3 V.<br>pacitors ca<br>t.<br>he voltage<br>pered by | n electrica<br>,<br>power sup | ully go beyd | ond this te   | mperature     |               |               |               |                             |

#### MULTIPLE-STEP STRESS TESTING OF SALs

At 85 °C, the useful life of SAL electrolytics is so extended that it is no longer feasible to predict it. This has been confirmed by years of observation of solid aluminium electrolytic capacitors in the telecommunications industry, thus justifying the extremely low failure rate of  $1 \times 10^{-9}$ /h (1 FITS) specified for these components.

On the basis of these qualities, our SAL electrolytic capacitors have established an excellent reputation in aerospace electronics, in professional electronics, and recently, because of their resistance to high temperature and to polarity reversal, in automotive electronics.

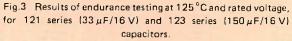

#### SOLID ALUMINIUM ELECTROLYTIC CAPACITOR CONSTRUCTION

The 123-series SAL electrolytic capacitors are a development of the earlier bulkier 121-series. The higher CV product density of the 123-series is achieved through intensified etching of the aluminium-foil electrodes.

The internal structure of a SAL electrolytic has a capacitive element with five layers. Layer 1, the anode foil, is high-purity (99,99%) aluminium about  $100\,\mu$ m thick. It's layer 2, however, that determines the capacitance and other electrical characteristics. This layer is formed by the deep etching and oxidization of the aluminium foil of layer 1, the oxide lining the etched pits to form the dielectric. Layer 3 consists of low-resistivity manganese dioxide held in a glassfibre web that also acts as a spacer. Layers 4 and 5 are similar to layers 1 and 2; layer 5 is the cathode aluminium foil, and layer 4 formed by the etching and oxidization of this foil (though less deeply etched than layer 2).

The cut-away view of the 123-series capacitor shows the basic construction. The anode and cathode foils, together with the glass-fibre web, are wound on a solid aluminium pin to which the anode foil is welded. The cathode foil connection is made by an aluminium strip welded at both ends; experience has shown that welding gives better reliability than any other form of connection.

Cut-away view of a 123-series solid aluminium electrolytic capacitor

#### APPENDIX

### Theoretical considerations of multiple-step stress testing

From the number of failures in a given number of components over a period (under stated conditions of stress e.g. voltage, current, temperature), it is possible to gain data on the overall picture of reliability. Each component possesses its own reliability characteristic and some of the basic expressions for interpreting the data are as follows:

- $R(t) = e^{-\lambda t} = reliability the fraction of components$ that have not yet failed after elapsed time $t (assuming constant failure rate <math>\lambda$ ).\*

- $F(t) = 1 e^{-\lambda t} =$  cumulative failure proportion the fraction of components that have failed after elapsed time t (again assuming constant  $\lambda$ ).

It then follows that R(t) = 1 - F(t).

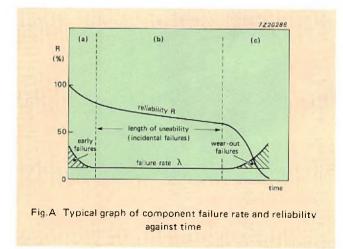

#### Bathtub curve

A plot of reliability R and failure rate  $\lambda$ , against time t, results in a graph showing typical curves for the component (see Fig.A). The failure rate curve, known as a "bathtub" curve due to its shape, is in three distinct parts:

- (a) early failures ( $\lambda(t)$  decreasing)

- (b) incidental failures ( $\lambda(t)$  constant)

- (c) wear-out failures ( $\lambda(t)$  increasing).

The times at which early failures (caused largely by manufacturing faults) end, and wear-out begins are important as it is from these points that the typical useful life, and hence lifetime, are deduced and defined.

\* failure rate = the average number of component failures per component-operating hour (1/h). For high reliability applications, λ will be in the region 10<sup>-6</sup>/h to 10<sup>-9</sup>/h. The period for which  $\lambda$  is constant (Fig.A, section (b)) is the operational section in which manufacturers' data on failure rates will apply and on which system designers will base calculations for overall system reliability. The overall reliability and failure rate in an electronic system are calculated from:

$R_S = R_1 \cdot R_2 \cdot R_3 \dots R_n$

and

$$\lambda_{\rm S} = \lambda_1 + \lambda_2 + \lambda_3 \dots + \lambda_n$$

From this, it is clear that the overall reliability and failure rate in an electronic system are most affected by the weakest single element present. Similarly, the overall reliability decreases as the number of elements in the system increases.

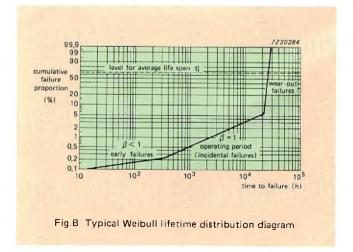

#### Weibull distribution functions

Although the name "bathtub curve" is pictorially descriptive, it's unsuitable for the exact determination of  $\lambda(t)$ , R(t), and the points at which the useful life starts and ends. A more accurate prediction can be made by applying the Weibull distribution function:

$$R(t) = e^{-(t/n)^{\beta}}$$

where  $\beta$  = Weibull "shape parameter", and n = 1/ $\lambda$  is the average lifetime (in hours), defined as the length of time for which 1/e (36,7%) components are operational (for constant  $\lambda$ ).

The Weibull function is transformed into a linear equation by taking the logarithm twice, thus:

$\ln \ln (1/R(t)) = \beta \ln t - \beta \ln n.$

A plot on Weibull probability paper with  $\ln \ln (1/R(t))$  as ordinate, and  $\ln (t)$  as abscissa, shows that the Weibull equation transforms the bath-tub curve into three straight lines of differing ( $\beta$ ) gradients as shown in Fig.B.

With this Weibull lifetime distribution diagram, it is possible to accurately define the end of the period of early failures, and the onset of wear failures (from sections (a) to (b), and (b) to (c) respectively on the bathtub curve), by the two points of intersection of these three lines. Each section is defined as follows:

(a)  $\beta < 1$  – early failure period ( $\lambda(t)$  decreases)

(b)  $\beta = 1 - \text{constant failure period } (\lambda(t) \text{ constant})$

(c)  $\beta > 1$  – wear-out failure period ( $\lambda(t)$  increases).

In fact, it is not necessary to have  $\beta = 1$  in section (b) as this occurs only when failures are determined totally by stochastic processes.

#### Arrhenius' law and accelerating factors

The reaction of most chemical processes increases exponentially as the temperature is increased. Temperature is therefore an accelerating factor. So if the operating temperature of a component under test is increased above its normal rating, the onset of wear failures occurs earlier and the average lifetime is shortened. Conversely, at a lower temperature, the lifetime can be expected to be longer.

The temperature influence can be described by making use of the analogy between the reaction constant of a process and the failure rate of a component, as both are defined as the decrease per unit time of the concentration of a species divided by the actual concentration of the species. Thus, from Arrhenius' law, the expression for the failure rate  $\lambda$ , at absolute temperature T, can be written:

$$\lambda(T) = Ae^{-B/kT}$$

where A and B are constants, k = Boltzmann constant and T = absolute temperature. The constant B is normally referred to as the activation energy of the process.

The information available cannot always be reduced to comply with Arrhenius' law. when the temperature is the only accelerating factor. The equations that describe test results fall apart even more when additional stress factors are involved. Parameters that reduce lifetime are, for example, vibration, humidity, pressure and, in particular for capacitors, the applied voltage.

Denoting the applied voltage by V, and general stress parameters by  $S_1$ .  $S_2$ , etc., the following equations apply  $(n, G, A_1, A_2, B_1, B_2, etc. are constants)$ :

For integrated circuits the Eyring law (Ref.4):

$$\lambda(T,S) = A \exp ((-B+B_1S_1+B_2S_2+...)/kT)$$

For ceramic capacitors (Ref.5):

$$\lambda(T,V) = A_1 \cdot V^n \exp(-B/kT);$$

For solid tantalum capacitors (Ref.6):

$$\lambda(T,V) = A_2 \cdot V^n \cdot 2^{B_3(T-B_4)};$$

and for capacitors in general (Ref.7):

$\lambda(T,V) = (A_3 \cdot V^n + A_4) \exp((B_5 T^G);$ and

$\lambda(\mathbf{T},\mathbf{V},\mathbf{S}) = (\mathbf{A}_5\mathbf{S}_5 + \mathbf{A}_6\mathbf{S}_6 \dots) \lambda(\mathbf{T},\mathbf{V}).$

Apparently, an adequate model is lacking to describe the failure mechanisms during actual testing. Probably a degradation process controlled by the Arrhenius activation energy is "polluted" by other unknowns that are applied to the components under test. These could be caused by the test process itself (e.g. handling, thermal gradients, influence by surrounding components, atmosphere). They could also derive from the production and handling history of the components, by which they may have already experienced some non-identified stresses before actual testing starts.

From all equations, however, it is clear that there is an exponential increase of failure rate with temperature (therefore the average lifetime decreases exponentially), and an acceleration of the increase by applied voltage and other stresses.

Thus the ageing process of a component or system is accelerated by the maximum possible amount if it is loaded with all known stress factors simultaneously (multiplestress testing). The absolute level of the applied stress factors also influences the accelerated ageing process, so the lifetime period can be adjusted through both the number of, and the level of, the stress parameters applied.

This technique of applying several stress factors, and increasing the level of stress applied in stages. to accelerate the lifetime is known as *multiple-step stress testing*. The acceleration (or "time-lapse") factor can be calculated from the relationship between lifetimes under normal and under stressed conditions. This relationship is determined particularly accurately with the aid of the Weibull distribution graph.

However, to obtain correctly predicted results, the following conditions must be complied with:

- 1. The failure characteristic must remain the same.

- 2. The normal wear curve must be parallel to the accelerated wear curve on the Weibull graph. This is, in fact, verification of condition 1.

- 3. The failure analysis of all test batches must display the same fault mechanism.

- 4. The upper limits of the stepped stress parameters must not exceed conditions outside the operating area of the component (in the forbidden area, for example, boiling point) as this could induce new chemical processes that produce different fault mechanisms (Fig.C).

#### MULTIPLE-STEP STRESS TESTING OF SALS

If conditions 1 to 4 are fulfilled, then the acceleration factor will be as follows:

#### acceleration factor = $t_{ON}/t_{OA}$

where  $t_{ON}$  = time of onset of wearout failures under normal conditions, and  $t_{OA}$  = time of onset of wearout failures under accelerated conditions. One disadvantage of this method is that the accuracy of prediction decreases as the acceleration factor increases.

To describe the above conditions in terms of the Weibull function, both the shape factor  $\beta$  and the point in time at which the first failure occurs must be independent of temperature (Ref.8). This is also necessary though not sufficient, in order to be able to apply Arrhenius' law. If the shape factor  $\beta$  in the operating period is not equal to 1, then the pre-exponential acceleration factor is difficult to identify. This is what happens for solid tantalum capacitors (Ref.9).

#### REFERENCES

- 1. B. Goudswaard and F. J. J. Driesens, Failure mechanisms of solid tantalum capacitors, Electrocomponent Science and Technology, Vol. 3 (1976), pp. 171-179.

- 2. J. Brettle and N. F. Jackson, Failure mechanisms in solid electrolytic capacitors, Electrocomponent Science and Technology, Vol. 3 (1977), pp. 233-246.

- E.H.L.J.Dekker and C.J.M.Lasance, Thermal and Electrical Analysis of Solid Aluminium Capacitors, Active and Passive Components, Vol.12 (1987), pp. 167-186.

- 4. W. Workman, Failure modes of integrated circuits and their relationship to reliability, Microelectronics and Reliability, Vol. 7 (1968), pp. 257-264.

- 5. W.J. Minford, Accelerated life testing and reliability of high K multilayer ceramic capacitors, IEEE Transactions on Components, Hybrids, and manufacturing Technology, Vol. CHMT-5 (1982), pp. 297-300.

- Y. Hasegawa and K. Morimoto, Characteristics and failure analysis of solid tantalum capacitors, NEC Research and Development, Vol. 50 (1978), pp. 79-94.

- 7. Mil-handbook 217D, 1982, p. 5.1.7-3.

- H. C. Boge, Description of endurance behaviour of electronic components using the Weibull distribution and the Arrhenius equation, NTZ Archiv, Vol. 5 (1983), pp. 242-244 (in German).

- J. N. Burkhart, Use of accelerated testing techniques in military specification MIL-C-39003, Proc. 4th Capacitor and Resistor Technology Symposium (1984), pp.111-117.

- G. Hörmansdorfer and E. Nolte, Borehole geophone for ultra deep wells, Research Note T84-230. Bundesministerium fuer Forschung und Technologie, Eggenstein-Leopoldshafen 1984 (in German).

## **Third-generation decoding ICs for CD players**

#### **RAINER FINCK and DAVE SLOWGROVE**

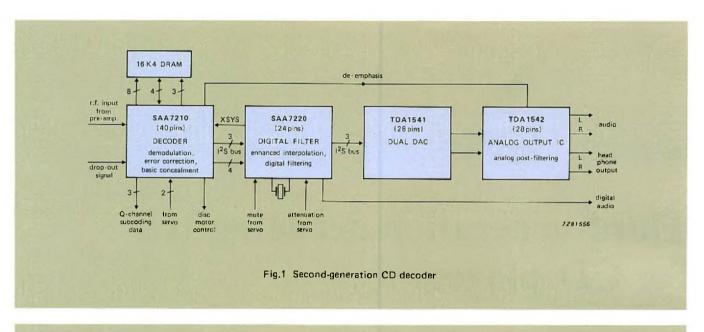

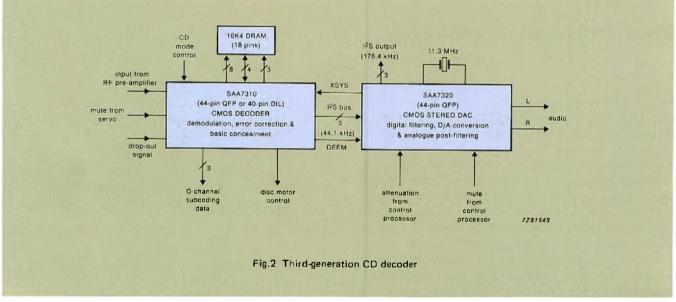

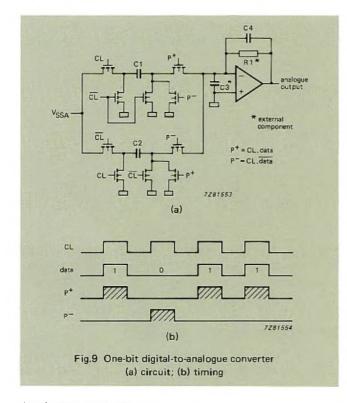

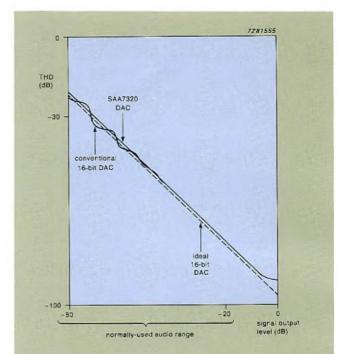

Since its introduction in 1984, our second-generation fourchip set for CD decoders (Ref.1) has won the acclaim of player manufacturers and listeners alike for the quality of the sound it can reproduce - for example, see Refs 2 to 6. With this chip-set, the first to make full use of the errorcorrection capability of the CD system's Cross-Interleaved Reed-Solomon code, and the first to discriminate between the errors on a disc (for more reliable corrections), sound reproduction reached levels of fidelity that even surpassed those available with our first-generation circuits. Indeed, the decoding system shown in Fig.1 has become the industry standard. What's more, the extremely high level of integration used has reduced the size of the decoding circuitry and the number of peripheral components in a CD player significantly, simplifying board design and lowering assembly costs.

Still higher levels of integration are used in a new CMOS chip set introduced in this article. Intended for use in players in the middle and low end of the market (for example, in audio stacks and portables), this third-generation chip set comprises just two ICs which together perform all the decoding functions and D/A conversion required in a CD player.

Besides retaining many of the benefits of our secondgeneration circuits, the new chip set:

- operates from a single (+5 V) supply

- consumes less power

- has an extended operating temperature range  $(-40 \degree C \text{ to } +85 \degree C)$

- has improved facilities for concealing data lost as a result of large external knocks, as commonly encountered by car players and portables. So there is less muting of the audio and hence fewer audible clicks.

- has a software-controlled inhibit of the data interpolation circuitry for CDI and CD ROM applications.

- has improved digital filtering (128 taps instead of 120).

Figure 2 shows the new decoding circuits. The SAA7310 (Ref.7) performs the same functions as the SAA7210 - demodulation, full error-correction, and basic interpolation of uncorrectable audio samples. In addition, it controls the new data interpolation inhibit and the data concealment procedure.

The SAA7320 (Ref.8) includes a phase-linear digital low-pass filter, two new-design high-linearity DACs and operational amplifiers for analogue post-filtering. The level of integration in the SAA7320 is the highest of any current CD circuit. Like the SAA7220 digital filter IC, the SAA7320 has facilities for attenuating the audio output by 12 dB, which can be used at the start of 'fast forward/fast reverse' commands and a search for a track, for example. In addition, the soft mute facility which can be used when moving to another track and during pauses is retained.

The data format between the SAA7310 and SAA7320 is according to the  $I^2S$  (inter-IC sound) specification<sup>1</sup>), which allows combinations of second and third-generation ICs (such as the SAA7310, SAA7220 and TDA1541) to be used in a player, giving the player manufacturer maximum design flexibility, see Table 1.

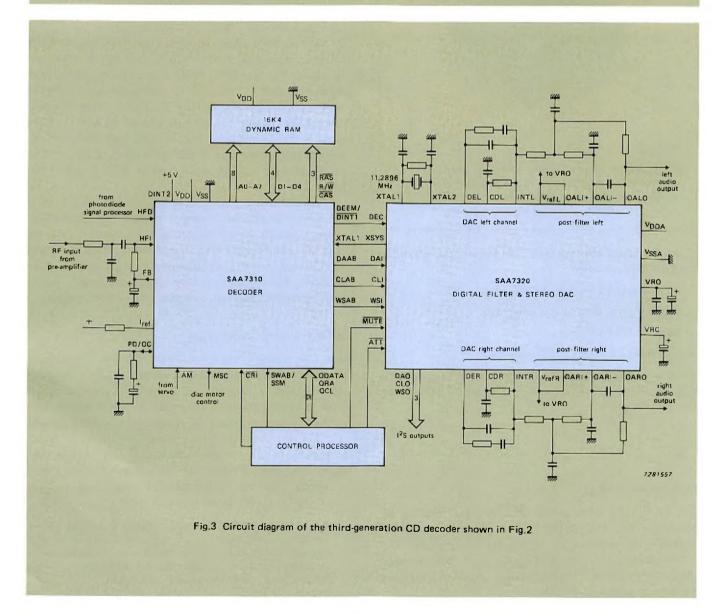

Figure 3 is the circuit diagram of a complete CD decoder using the SAA7310 and SAA7320. As the figure shows, the circuit which includes on-chip stereo low-pass filtering requires only a few passive peripheral components.

I<sup>2</sup>S communication is a communication format for digital audio. The I<sup>2</sup>S bus is a 3-line bus comprising: clock, serial data line, and a control line used to select left and right channel words (Ref.9).

|                         |                   |                     | Decodir          | TABLE 1<br>ug ICs for CI | ) players            |                                                              |                                      |

|-------------------------|-------------------|---------------------|------------------|--------------------------|----------------------|--------------------------------------------------------------|--------------------------------------|

|                         | de-<br>modulation | error<br>correction | in terp<br>basic | olation<br>enhanced      | digital<br>filtering | D/A<br>conversion                                            | application                          |

| 1st generation          | SAA7010           | SAA7020             | SAA7000          |                          | SAA7030              | 2 x TDA1540<br>plus discrete<br>analogue low-<br>pass filter | home players                         |

| 2nd generation          |                   | SAA7210             |                  | SAA                      | 7220                 | TDA1541 plus<br>TDA1542                                      | home and<br>full-performance players |

| 3rd generation          |                   | SAA7310             |                  |                          | SA                   | A7320                                                        | portable and home players            |

| 2nd & 3rd<br>generation |                   | SAA7310             |                  | SAA                      | 7220                 | TDA1541 plus<br>TDA1542                                      | full-performance players             |

#### **SAA7310 DECODER**

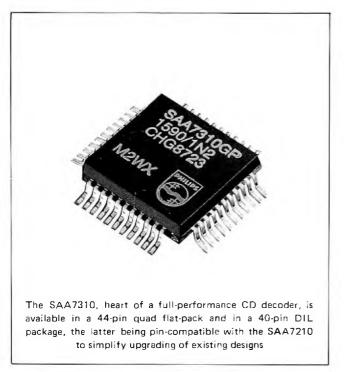

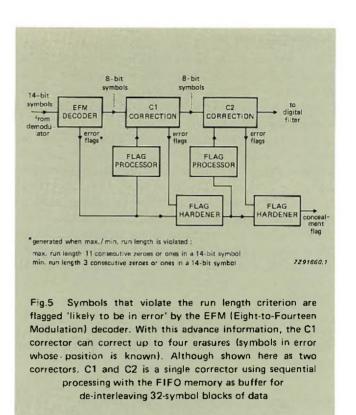

The SAA7310 performs all the functions necessary to decode an amplified and filtered version of the EFM (eight-to-fourteen modulated) data stream generated by the pick-up of a CD player. The SAA7310 is available in a 44-pin quad flatpack, or in a 40-pin DIL package suitable for upgrading an SAA7210-based decoding system. The pinning of the DIL version makes the SAA7310 virtually a drop-in replacement for the SAA7210.

All the features of the SAA7210 decoder are retained in the SAA7310, namely:

- fully integrated VCO in the demodulator PLL

- efficient processing of subcoding data

- adaptive error-correction

- operates with a large FIFO memory.

These and the new muting facility and selector for nondigital-audio applications such as CDI and CD ROM are summarized below.

#### **Demodulator PLL**

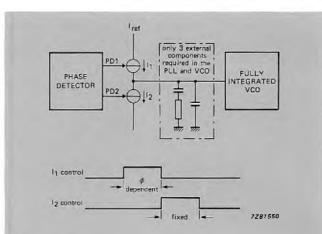

The SAA7310's demodulator PLL requires virtually no peripheral components. The VCO is a fully-integrated RC oscillator; it requires no peripheral components. The differential filtering circuitry of the PLL uses a self-balancing charge pump design that requires only one filter comprising just three components (Fig.4).

Fig.4 In the SAA7310, an integrated charge pump design is used in the differential filter of the demodulator PLL. This filter is self-balanced and consists of only two external components. The VCO is fully-integrated

#### Efficient processing of subcoding data

As well as the audio data, Q-channel subcoding data<sup>1</sup>) is derived continually in the SAA7310 from the incoming RF signal. The time spent by the control processor handling subcoding data is reduced by a handshaking protocol between the processor and the SAA7310. When the processor wants data, a request is sent to the SAA7310 which, when a full Q-channel frame is ready, acknowledges the request and enables the Q-channel serial data output. The processor sends a clock signal to shift the data out of the SAA7310.

The first negative-going edge of the clock signal resets the acknowledge signal thereby releasing the request line. If the processor doesn't require all the subcoding data, say only the number of a track (contained in the first sixteen bits), it can reset the request line after these bits have been received, thereby disabling the Q-channel output of the SAA7310 which resumes collecting new subcoding data.

#### Adaptive error-correction

The CD system's Cross-Interleaved Reed-Solomon Code (CIRC) enables up to four erroneous symbols<sup>2</sup>) (in a 32-symbol block) to be corrected if the CIRC decoder is given prior information about the position of the errors. This type of correction, where the position of an error is known, is called an erasure correction. When the positions of errors are unknown, up to two erroneous symbols can be corrected. A decoder with the maximum error-correction capability (like that of the SAA7310 and the SAA7210) can make the corrections shown in Table 2.

- <sup>1</sup>) Besides the audio information recorded on a compact disc, information representing track numbers and playing times is recorded so that tracks can be played in any desired sequence and titles and elapsed playing times etc. can be displayed. This information is termed Q-channel subcoding data.

- <sup>2</sup>) 14 bits.

| Error-correct  |     | sibiliti<br>he SA |      |         | RC de   | coder |

|----------------|-----|-------------------|------|---------|---------|-------|

|                |     |                   | eras | ure cor | rection | s     |

|                |     | e=0               | e=1  | e=2     | e=3     | e=4   |

|                | t=0 |                   |      |         |         |       |

| t corrections* | t=1 |                   |      |         |         |       |

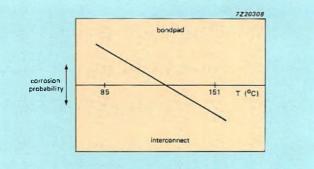

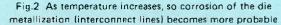

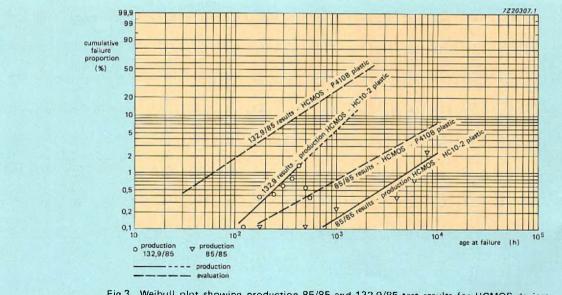

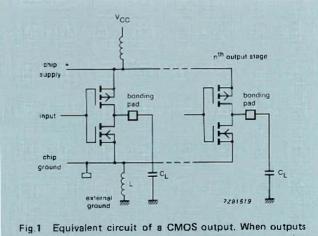

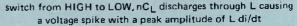

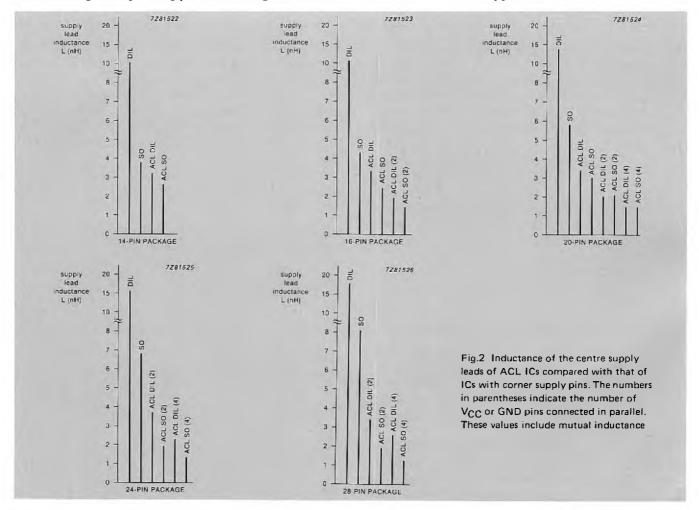

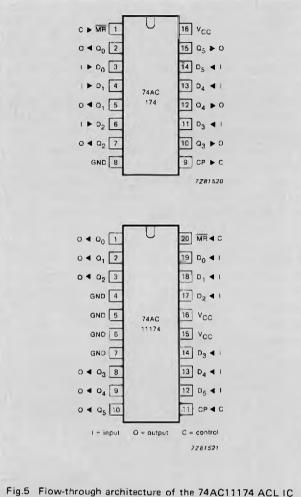

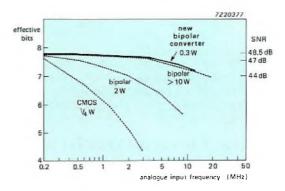

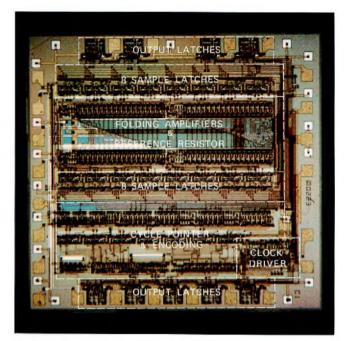

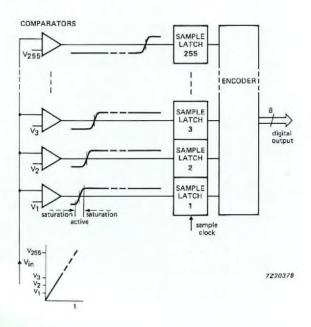

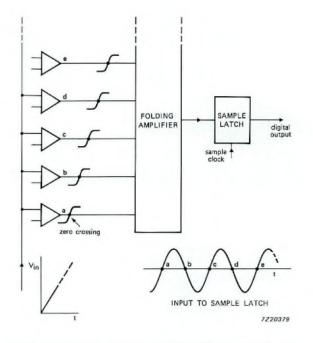

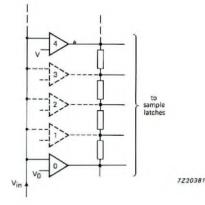

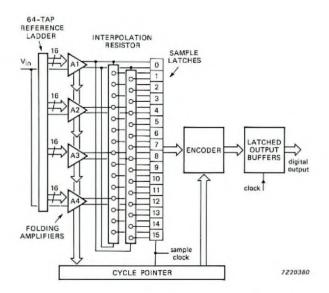

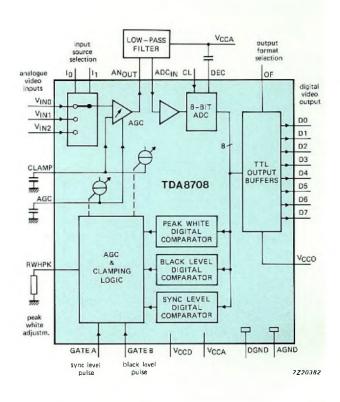

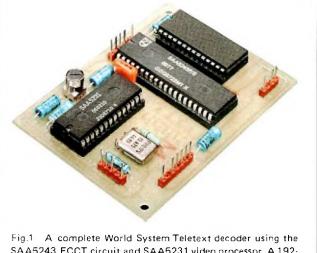

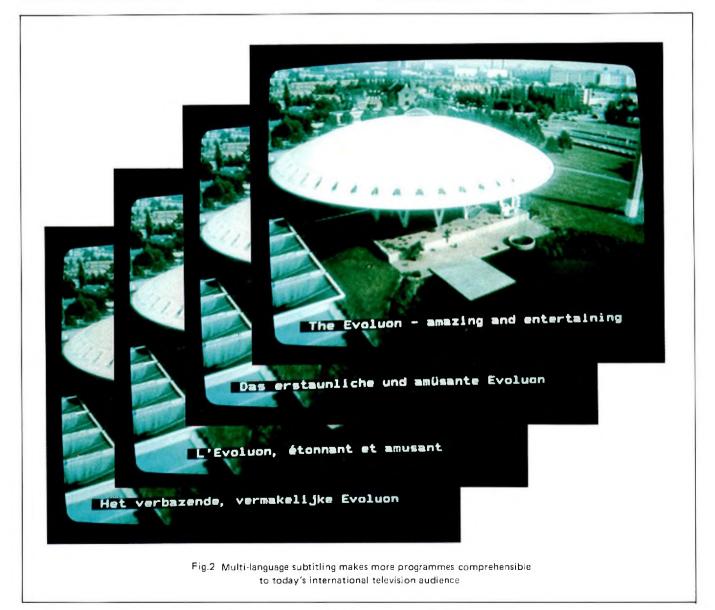

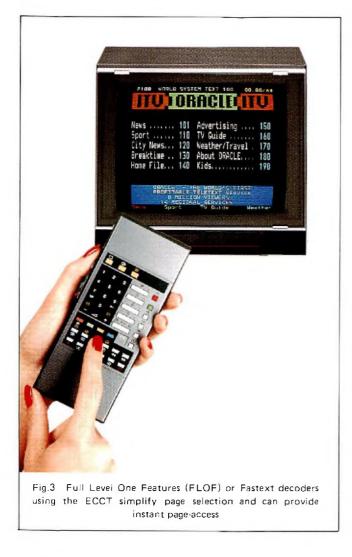

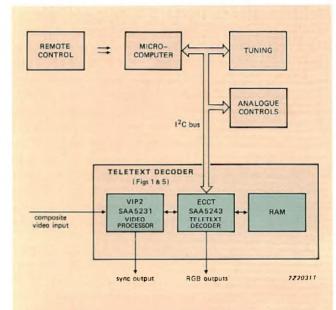

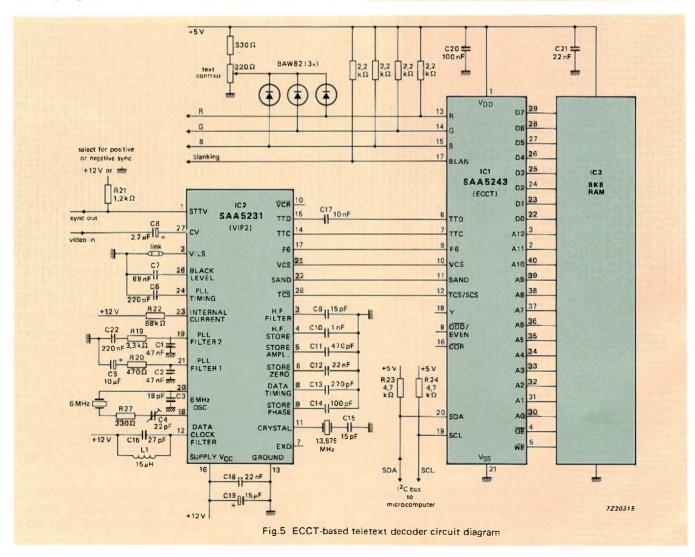

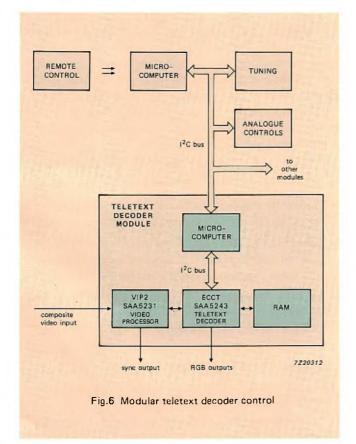

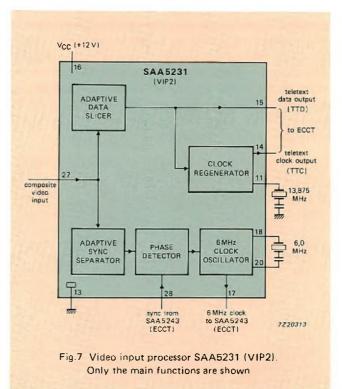

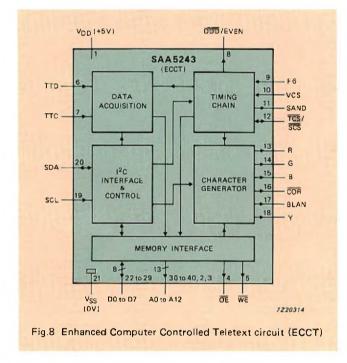

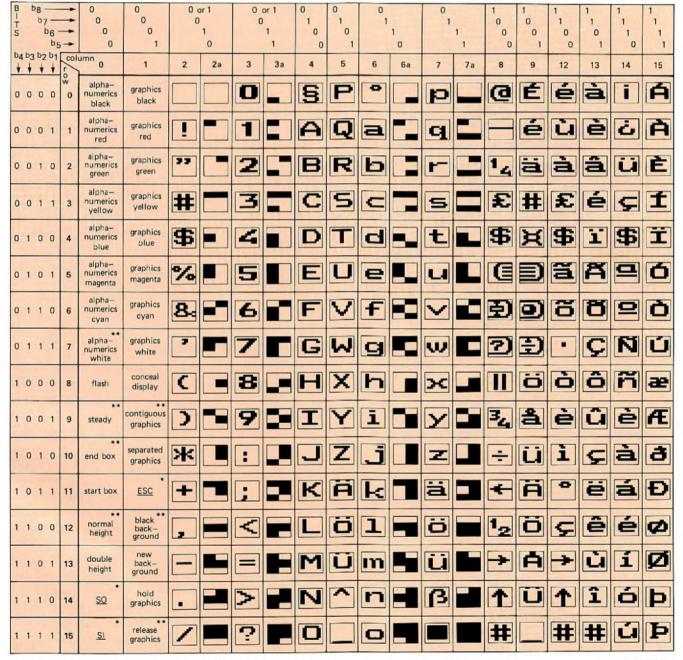

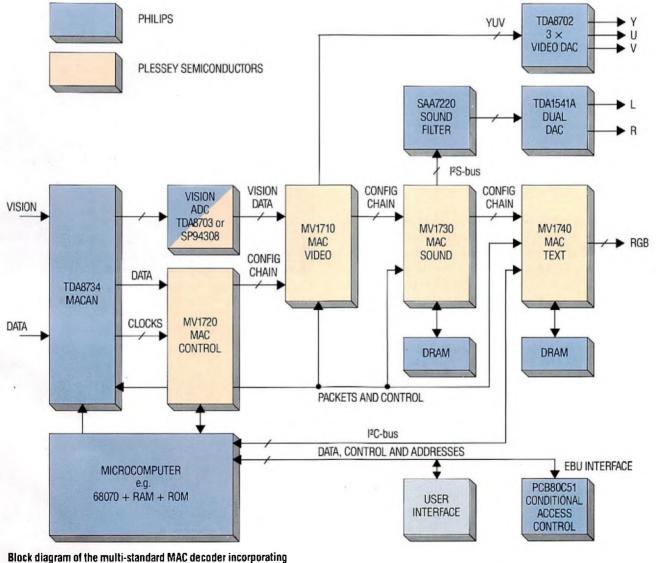

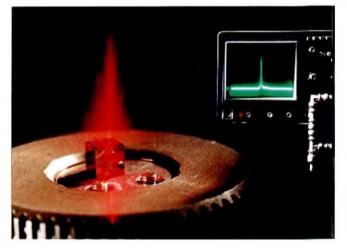

|                | t=2 | •                 |      |         |         |       |