### **Philips Components**

## Electronic components & applications

Volume 9, No.4

Editor: Ian L. A. Crick

Design and production: Cees J. M. Gladdines Bernard W. van Reenen Jacob Romeijn

Design consultant: Theo Kentie

The picture of an oil tanker discharging oil into the sea exemplifies the irresponsibility of much of today's industry. In the past, the world could absorb such abuse with comparative ease since the greatest of man's enterprises amounted to little more than flea bites on its surface. The effects of pollution, however, are cumulative and our world is fast becoming very sick indeed. Environmental organizations have long recognized this and have spared no effort in alerting industry and the authorities to the disease, and to the need for responsible, concerted action before the disease becomes terminal. Heavy industry, nuclear power and motor vehicles are the main targets of these groups but that doesn't mean that other areas can afford to relax. The electronic-components industry too, can play its part in helping to clean up our world. Already much effort has gone into reducing the use of toxic materials in electronic components, and into developing environmentally-friendly packing materials. Maybe the world can never regain its pre-industrial purity, but we should at least ensure that our children's legacy is a viable one.

### Contents

| Analog multi-standard colour decoder ICs |     |

|------------------------------------------|-----|

| TDA4650 and TDA4660                      | 194 |

| E. Bruns and K. Juhnke                   |     |

| Logic-level FETs                         | 208 |

| A. Woodworth                             |     |

| ICs for electronically tuned car radios  | 211 |

| A. Garskamp                              |     |

| Chip-on-foil – the flexible approach     | 225 |

| to LCD modules                           |     |

| W. Stijns                                |     |

| ICs and Discrete Semiconductors          | 240 |

| for TV and VCR Tuners                    |     |

| N. Baars                                 |     |

| Abstracts                                | 253 |

| Authors                                  | 256 |

|                                          |     |

All information in Electronic Components and Applications is published in good faith, but the publishers assume no liability for any consequence of its use; its publication does not imply a licence under any patent. Specifications and availability of goods mentioned in it are subject to change without notice.

### Analog multi-standard colour decoder ICs TDA4650 and TDA4660

#### ECKHARD BRUNS, KLAUS JUHNKE

In Europe, in particular, there are many areas where TV transmissions of more than one colour transmission standard can be received. Multi-standard colour decoding is also an essential part of satellite TV reception and has been considerably extended by the requirements of the VCR, S-VHS standard. To satisfy the resulting demand for multi-standard TV colour decoders, we introduced the TDA4555/57 in the early 1980s. These ICs have been extremely successful and have been in mass production for nearly a decade. However, recent advances in switched-capacitor technology have now enabled us to replace the discrete glass delay line by integrated baseband delay line filters. The TDA4650 retains all the features of the TDA4555/57 which have been so successful, but is adapted to operate together with the switched-capacitor baseband delay line filters of the TDA4660.

It is essential for the multi-standard colour decoder to identify accurately and quickly the TV colour standard of the input signal for both CVBS signals and the separate luminance and chrominance components in S-VHS format from a VCR. It is equally essential to integrate as many of the functions of the multi-standard colour decoder as possible. Also, this multi-standard colour decoder is based on a line-locked clock, so its output colour-difference signals can be processed by a feature module to provide memory-based features (e.g. picture-in-picture, 100/120 Hz displays).

The baseband delay lines use CMOS switchedcapacitor technology, based on serial sampling of the baseband colour-difference signals at a line-locked clock frequency. Delaying the baseband colour-difference signals by exactly one line and adding the non-delayed colour-difference signal provides comb filtering with a frequency response which is periodic in the line frequency. The comb filter maxima are integer multiples of the line frequency, the minima are at successive half multiples of the line frequency.

Multi-standard colour decoding with baseband delay lines has the following advantages:

- there are no delay line coils and potentiometer and therefore, no delay line adjustments

- the circuit configuration of the baseband delay line is the same for all colour transmission standards

- cross colour interference is reduced for NTSC colour signals due to the comb filters

- the possibility of crosstalk between the FM SECAM colour carriers (diaphoty) is eliminated.

#### ANALOG COLOUR DECODER ICs

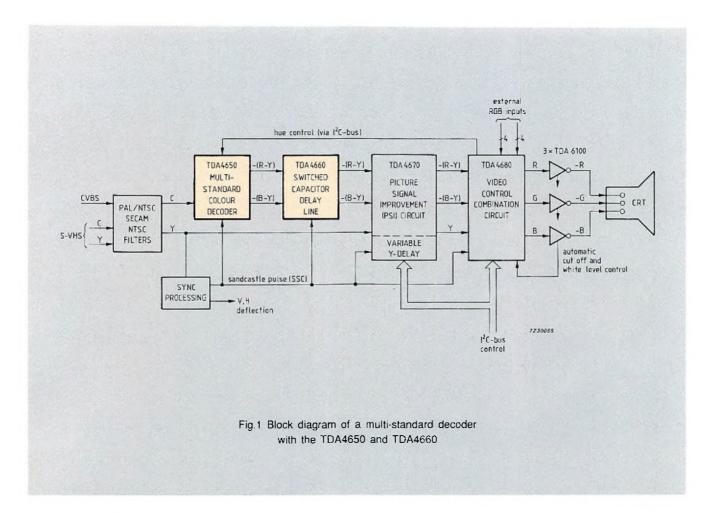

The TDA4650 and the TDA4660 are complementary in their function, therefore, the TDA4650 provides colourdifference signal outputs to the TDA4660 at pre-defined voltage levels, see Fig.1. The TDA4650, Multi-standard Colour Decoder performs colour transmission standard identification and multi-standard chrominance signal control and demodulation. The TDA4660, Switched Capacitor Delay Line, contains the two line-locked comb filters for an integrated multi-standard colour decoder. The TDA4660 can, however, be used with any colour decoder as a baseband colour-difference signal filter.

The colour-difference output signals from the TDA4660 are compatible with the TDA4670 Picture Signal Improvement (PSI) Circuit and the TDA4680 Video Control Combination Circuit. Both the TDA4670 and the TDA4680 incorporate l<sup>2</sup>C-bus control for display signal processing and control, the TDA4680 can select two external RGB inputs (e.g. peritelevision connector, teletext, etc.). The super sandcastle pulse (SSC) synchronizes colour decoding, luminance and colour-difference signal processing and correlates the RGB colour signals with the raster.

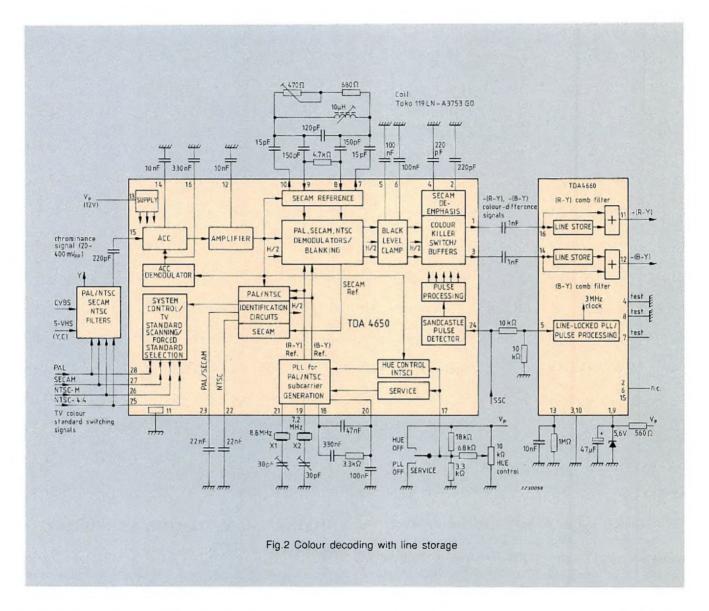

### COLOUR TRANSMISSION STANDARD IDENTIFICATION

Colour transmission standard identification consists of an automatic control and scanning sequence with identification circuits which identify the transmitted colour standard, see Fig.2. The automatic control and scanning sequence sets the mode of the TDA4650 sequentially to PAL, SECAM, NTSC-M and NTSC-4.4. The outputs from the TV standard scanning circuits not only establish the internal mode of the Multi-standard Colour Decoder but also select the appropriate external PAL/NTSC SECAM NTSC filter (via the voltages on pins 25 to 28). The TDA4650 interrogates the chrominance signal by comparison with the characteristics of the chrominance signals of the different colour transmission standards in sequence. When a transmission conforming to a colour transmission standard is identified by the identification circuits, the mode of the TDA4650 is automatically selected.

The TDA4650 can decode colour signals which are defined according to the following transmission standards:

#### ANALOG COLOUR DECODER ICs

- QAM (Quadrature Amplitude Modulation) of the colour carrier by the colour-difference signals.

- standard NTSC, NTSC-M ( $f_{sc} = 3.579545$  MHz) referred to as NTSC-3.5.

- non-standard NTSC, with  $f_{sc} = f_{sc}(PAL) =$ 4.43361875 MHz. This colour transmission standard is used in the Near East and is referred to as NTSC-4.4. As the colour carrier frequency is the same as that of the PAL-B, G, H, I standards, the same crystal oscillator is used to generate the reference frequency for both.

- **PAL**, characterized by the phase reversal of the (R-Y) colour-difference signal on alternate scan lines. PAL-B, G, H, I: colour carrier frequency  $f_{sc} = 4.43361875$  MHz. PAL-M: colour carrier frequency  $f_{sc} = 3.57561149$  MHz. PAL-N: colour carrier frequency  $f_{sc} = 3.58205625$  MHz.

- SECAM, characterized by transmission of the (R-Y) and (B-Y) colour-difference signals on alternate scan lines and frequency modulation of the colour carriers. The frequency of the colour-difference signals may vary between 3.900 and 4.756 MHz. The frequencies of the no-colour carriers are:

$f_o (B-Y) = 4.250 \text{ MHz},$  $f_o (R-Y) = 4.40625 \text{ MHz}.$

#### **Control And Scanning Sequence**

The automatic control and scanning sequence determines the mode of the TDA4650 selected by the colour transmission standard scanning and system control circuits. These circuits switch the mode sequentially to the PAL, SECAM, NTSC-M and NTSC-4,4 standards, each for a duration of four field periods (80 ms). This time interval is a good compromise between the stabilization of the chrominance signal at the input to the identification circuits and the suppression of the noise content of the chrominance signal. If the current chrominance signal is not identified, the control and scanning sequence selects the mode of the next colour transmission standard so that the chrominance signal is always identified within 320 ms. This time is increased by two field periods (colour switch-on delay) to 360 ms, at which time the colour-difference signals are enabled.

To provide reliable SECAM chrominance signal identification under all conditions, e.g. for SECAM-PAL transcoded signals, or when PAL chrominance signals are distorted by reflection, the control and scanning sequence includes PAL priority switching. The PAL priority circuit switches the Multi-standard Colour Decoder to the PAL mode after a SECAM chrominance signal is first identified. If a PAL chrominance signal is not identified during the following scanning period, the Multi-standard Colour Decoder reverts to the SECAM mode for a second identification. The PAL priority circuit increases the maximum identification time together with the colour switch-on delay to 520 ms (this is a worst-case condition, assuming, for example, that a SECAM chrominance signal exists but the control and scanning sequence starts in the NTSC-M mode). A further precaution for reliable SECAM identification is to identify the SECAM chrominance signal at 50 Hz only. An NTSC chrominance signal (60 Hz) can therefore, never be identified as a SECAM chrominance signal.

If no colour transmission standard is identified, as with black and white transmissions, or an unprepared colour transmission standard exists, the control and scanning sequence scans continuously. The colour decoding remains switched off until a subsequent chrominance signal is identified. If, due to interference, the established colour transmission standard is temporarily not identified, a delay of two field periods is included to prevent the immediate start of the control and scanning sequence.

During the control and scanning sequence, the amplitude of the colour transmission standard switching signals on pins 25 to 28 is approximately +2.5 V. When a colour transmission standard is identified, the amplitude of the associated switching signal rises to typically +5.8 V and the other switching signals are set to less than 0.5 V. The switching signal is used to select the appropriate chrominance filter and chrominance trap of the PAL/NTSC SECAM NTSC filters. If

an external voltage greater than +9 V is applied to one of pins 25 to 28, then this forces the selection of PAL, SECAM, NTSC-M or NTSC-4.4. Forced standard selection overrides the colour transmission standard identification. The automatic colour-killer switch still operates with forced standard selection.

The TDA4650 requires a 3-level super sandcastle pulse (SSC) to generate all the necessary internal timing pulses. The sandcastle pulse amplitudes are >7.7 V for the burst key pulses,  $4.5 \pm 0.4$  V for the horizontal blanking pulses and  $2.5 \pm 0.5$  V for the vertical blanking pulses. Level detector circuits separate the three components of the sandcastle pulse from which the pulse processing circuits generate the required internal timing and clamping pulses.

#### **Colour Transmission Standard Identification Circuits**

The colour transmission standard identification circuits compare the mode of the Multi-standard Colour Decoder with the input chrominance signal, the result of this comparison determines the colour transmission standard. The identification circuits examine the nature of the signals present during the back porch interval of the chrominance signal. For PAL and NTSC chrominance signals this is the colour burst at the colour carrier reference frequency but for SECAM chrominance signals these are the no-colour frequencies (4.250 and 4.40625 MHz).

NTSC-M and NTSC-4.4 modes compare the phase of the colour burst signal with the (B-Y) reference signal generated by dividing the 7.2 or 8.8 MHz crystal oscillator frequency by two (NTSC-M and NTSC-4.4 respectively). In each case, the phase discriminator output pulses are unipolar. The pulses are integrated by an external capacitor connected to pin 22 to provide a DC level.

For PAL identification, the phase of the colour burst signal is compared with that of the (R-Y) reference signal, generated by dividing the 8.8 MHz crystal oscillator frequency by two. The output pulses from the phase discriminator alternate in polarity but, after being fed through an H/2 demodulator, have the same polarity as the NTSC pulses. These pulses are integrated by an external capacitor connected to pin 23 to provide a DC level.

In contrast to the QAM standards, SECAM uses frequency modulation of the colour carriers. For SECAM identification, the alternating no-colour carrier frequencies present on the back porches are demodulated. The two no-colour carrier frequencies generate

#### ANALOG COLOUR DECODER ICs

pulses of alternate polarity (as with PAL) which are therefore fed to the H/2 demodulator. The unipolar output pulses are integrated by the external capacitor connected to pin 23, again to provide a DC level.

The voltages present on pin 23 (PAL and SECAM discriminator outputs) and pin 22 (NTSC discriminator output) are used to identify the chrominance signal. These voltages are fed to comparators and logic circuits to derive a correct identification of the colour transmission standard. The capacitor voltage consists of a fixed component derived from internal biassing at half the supply voltage (6 V), plus an extra component  $\delta$ V22 or  $\delta$ V23 provided by the input chrominance signal.

Table 1 summarizes the resultant voltage levels on the capacitors connected to pins 22 and 23 generated by input chrominance signals conforming to each of the transmission standards. When а colour colour transmission standard is identified, the appropriate capacitor voltage increases (+) above the internal biassing value (0). In the PAL and SECAM modes, the voltage on the capacitor connected to pin 23 increases when the colour transmission standard is identified. In the NTSC-M and NTSC-4.4 modes, the voltage on the capacitor connected to pin 22 always increases when an NTSC transmission is identified. As shown in Table 1, for black and white signal transmissions no input chrominance signal can be identified, the average capacitor currents are zero, and  $\delta V22$  and  $\delta V23 = 0$ .

When the TDA4650 is in the NTSC-4.4 mode, both PAL and NTSC phase discriminators are activated. The NTSC phase discriminator uses the (B-Y) colourdifference reference signal at 4.43 MHz which, in comparison with the colour burst signal of the PAL or NTSC-4.4 signal, generates pulses of the same polarity. These pulses charge the capacitor on pin 22 to  $V_c + \delta V_c$ . If the input chrominance signal conforms to the PAL colour transmission standard, the NTSC phase discriminator also outputs pulses with constant polarity since the PAL colour burst includes a component which is constant in the negative (B-Y) axis on each line. These pulses also charge the capacitor on pin 22 to  $V_c + \delta V_c$  so that, even though the TDA4650 mode is set to NTSC-4.4, the voltage on pin 22 is  $V_c + \delta V_c$ . Furthermore, since the PAL phase discriminator and H/2 demodulator are activated, the capacitor on pin 23 is also charged to  $V_c + \delta V_c$ . Finally, if the input chrominance signal conforms to the NTSC-M or SECAM standard, the frequency difference between the colour burst and the 4.43 MHz reference frequency is so large that the output from the NTSC phase discriminator is zero ( $\delta V22 = 0$ ).

#### **PAL/NTSC Reference Frequency Generation**

To identify and demodulate PAL and NTSC quadrature amplitude-modulated chrominance signals, the reference signals (R-Y) and (B-Y) are required. These reference signals are generated by a PLL consisting of a Voltage-Controlled Crystal Oscillator (VCXO), crystals X1 and X2, a 2:1 frequency divider and a phase detector. The phase detector compares the phase of the colour burst signal with the (R-Y) reference signal. The VCXO frequency is double the colour burst frequency for both X1 (PAL, NTSC-4.4) and X2 (NTSC-M) inputs at pins 21 and 19 respectively. This circuit has the advantage that both the quadrature colour-difference reference signals (R-Y) and (B-Y) are generated at the output of the frequency divider.

The colour burst output from the Automatic Colour Control (ACC) circuits is fed directly to the phase detector for PAL but via the hue control for NTSC. The phase of the colour burst signal is shifted by at least  $\pm 30^{\circ}$  by 3  $\pm 1$  V applied to pin 17 from the resistive

| TDA4650  | PAL  |      | NTSC- | 4.4  | NTSC- | M    | SECA | M    | b/   | w    |

|----------|------|------|-------|------|-------|------|------|------|------|------|

| mode     | δV22 | δV23 | δV22  | δV23 | δV22  | δV23 | δV22 | δV23 | δV22 | δV23 |

| PAL      | 0*   | +    | 0"    | 0    | 0"    | 0    | 0.   | 0    | 0    | 0    |

| NTSC-4.4 | +    | +    | +     | 0    | 0     | 0    | 0    | 0    | 0    | 0    |

| NTSC-M   | 0    | 0    | 0     | 0    | +     | 0    | 0    | 0    | 0    | 0    |

| SECAM    | 0*   | 0    | 0*    | 0    | 0*    | 0    | 0^   | +**  | 0    | 0    |

|       |      |     |     |       | TABLE 1       |          |     |         |          |      |

|-------|------|-----|-----|-------|---------------|----------|-----|---------|----------|------|

| δV22. | δV23 | for | the | input | chrominance s | signal . | and | TDA4650 | decoding | mode |

0 average capacitor charge current is zero,  $\delta V_c = 0$ ,  $V_c =$  supply voltage

+ average capacitor charge current >0,  $\delta V_c$  >0 (reference oscillator locked and correct H/2 demodulator switching).

\* NTSC phase discriminator switched off.

\*\* 50 Hz SECAM transmission only.

potential divider. The phase detector is enabled by the burst key pulses from the pulse processing circuits. The PLL time-constant is determined by the second-order filter between pins 18 and 20.

Pin 17 is also connected to the SERVICE switch which is used to set up the crystal oscillator frequencies for PAL, NTSC-4.4 and NTSC-M. If the voltage on pin 17 is less than 0.5 V (e.g. connected to ground), the colour burst signal and the colour-killer switch are inhibited but colour decoding remains operational. The PLL is switched off and the VCXO free-runs. This enables the trimmer capacitors in series with crystal oscillators X1 (PAL and NTSC-4.4) and X2 (NTSC-M) to be adjusted for minimum colour rolling. If the voltage on pin 17 is greater than 5.5 V (e.g. connected to the supply voltage), hue control and the colour-killer switch are inhibited but otherwise the PLL and colour decoding operate normally.

The crystal oscillator is selected by internal switching under control of the colour transmission standard selection and switching circuits in accordance with the mode demanded by the automatic control and scanning sequence. VCXO lock-on frequency ranges are determined by the characteristics of the external secondorder filter. To prevent interference, the VCXO is switched off when SECAM is selected.

#### CHROMINANCE SIGNAL CONTROL

The TDA4650 (and the TDA4660) must provide colourdifference signals of constant amplitude so that they are independent of variations in the amplitude of the CVBS or S-VHS chrominance signal. This maintains a fixed relationship between the amplitudes of the luminance signal (Y) and the -(R-Y) and -(B-Y) colourdifference signals independent of the IF filter characteristics and receiver de-tuning. For PAL and NTSC, the reference signal used for Automatic Colour Control (ACC) is the amplitude of the colour burst signal. For SECAM, the reference signals are the amplitudes of the no-colour frequency signals on the back porch.

The chrominance signal input is AC-coupled via pin 15 to a gain-controlled chrominance amplifier for which the chrominance signal gain is set by in-phase synchronous demodulation. This technique has the advantage that it has a single time-constant, determined by the capacitor connected to pin 16, for all colour transmission standards. It further uses the noise content of the chrominance signal to prevent the colour saturation increasing with high noise levels (colour bright-up effect). In-phase synchronous demodulation is also independent of the mode of the TDA4650 so that the chrominance signal stabilizes quickly. This is also important during the automatic control and scanning sequence to guarantee quick identification of the colour transmission standard. The chrominance amplifier uses low-distortion symmetrical circuits to avoid generation of even harmonics of SECAM chrominance signals. Biassing for the chrominance amplifier is stabilized by an independent DC feedback loop, decoupled by the external capacitor at pin 14.

The nominal peak-to-peak amplitude of the chrominance signal input at pin 15 is 200 mV with a 75% colour-bar signal. The ACC range is 20 mV to 400 mV which is adapted to a 1 V peak-to-peak CVBS signal input to the PAL SECAM PAL/NTSC filters.

The gain-controlled chrominance signal, including the colour burst signal, is fed to the colour transmission standard identification circuits and to the PLL for reference signal generation (via the hue control for NTSC chrominance signals). In addition, for PAL and NTSC, the chrominance signal is fed to the line/field blanking circuit prior to demodulation. In the case of SECAM, the chrominance signal is fed to a limiteramplifier prior to demodulation.

### CHROMINANCE SIGNAL DEMODULATION

The PAL/NTSC or SECAM chrominance signal demodulators are selected according to the automatic control and scanning sequence. The VH (vertical and horizontal pulses) from the pulse processing circuits blank the colour-difference signals. The H/2 signal inverts the phase of the PAL (R-Y) chrominance component and blanks the SECAM colour-difference signals line sequentially for compatibility with the TDA4660.

#### **PAL/NTSC Chrominance Signal Demodulation**

The (R-Y) and (B-Y) components of PAL/NTSC chrominance signals are demodulated by two conventional, differential balanced, synchronous cross-coupled amplifiers. The chrominance signal from the colour burst blanking circuits is fed to the emitters of the differential amplifiers while the (R-Y) and (B-Y) reference signals from the PLL are fed to the bases of the The VH pulses inhibit demodulator transistors. PAL/NTSC chrominance signal demodulation during the vertical and horizontal components of the sandcastle pulse.

#### ANALOG COLOUR DECODER ICs

The phase of the chrominance signal to the emitter of the (R-Y) demodulator is inverted line-sequentially by a PAL switching circuit, switched by the H/2 signal. This circuit is disabled in the NTSC mode. The PAL switching circuit provides the necessary phase reversal to demodulate the PAL (R-Y) colour-difference signal on successive horizontal scan lines with consistent polarity.

The gains of the PAL and NTSC demodulators are set so that the colour-difference signals at the outputs of the TDA4660 have nominal peak-to-peak values of -(R-Y) = 1.05 V and -(B-Y) = 1.33 V. Therefore, the outputs of the TDA4650 are approximately half these values in the PAL and NTSC modes.

#### SECAM Chrominance Signal Demodulation

The SECAM frequency-modulated (R-Y) and (B-Y) colour-difference signals are transmitted on alternate scan lines. Therefore, to decode these signals using baseband delay lines, only a single FM demodulator is required.

The SECAM chrominance signal is demodulated by a quadrature demodulator which follows a limiteramplifier; this removes residual amplitude variations after automatic colour control. The quadrature demodulator is, as for PAL and NTSC, a four-quadrant linear multiplier with two pairs of inputs. One pair is directly connected to the SECAM chrominance signal from the limiter-amplifier and the other pair is connected to the external SECAM reference tuned circuit. This tuned circuit shifts the phase of the chrominance signal depending on its frequency. An additional high-pass filter consisting of 150 pF capacitors and a 4.7 k $\Omega$  resistor compensates for phase shifts after the SECAM reference tuned circuit.

During the H and V blanking intervals, SECAM chrominance signal demodulation is inhibited and artificial black levels are superimposed on the SECAM colour-difference signals. These SECAM artificial black levels are adjusted to the different black levels of the demodulated two colour-difference signals. The offsets of the two SECAM artificial black levels are determined by the black level frequency offsets of the SECAM chrominance signal and the FM-demodulator efficiency  $(\delta V/\delta f)$ . The SECAM artificial black level offsets are internally set to a fixed value, therefore the FM-demodulator efficiency (mainly determined by the resonant frequency and the Q-factor of the SECAM reference tuned circuit) has to be adjusted to the internal value.

The line-sequential -(R-Y) and -(B-Y) SECAM colour-difference signals are de-multiplexed on to the parallel colour-difference signal paths. During the line-sequential, inactive colour-difference signal time the appropriate (clean) black levels are superimposed on the SECAM colour-difference signals.

In the TDA4660, the line-delayed colour-difference signal is added to the undelayed colour-difference signal. Therefore, for SECAM colour-difference signals, the active signal from the previous line which has been stored in the delay line is repeated during the black level line interval. To obtain the same colour-difference signal voltages at the outputs of the TDA4660 for all colour transmission standards, the amplitudes of the colour-difference signal outputs from the TDA4650 in the SECAM mode are twice those for PAL and NTSC. Thus the colour-difference signal outputs of the TDA4650 in the SECAM mode are -(R-Y) = 1.05 V and -(B-Y) = 1.33 V peak-to-peak (values for 75% colour-bar signal).

#### **Demodulator Output Stages**

The outputs of the PAL/NTSC and SECAM chrominance signal demodulators are connected in parallel. The colour-difference signals are filtered by low-pass filters with -3 dB frequencies at 1.0 MHz to suppress high-frequency interference signals and mixing products.

To establish a reference black level for all three colour transmission standards, the colour-difference signals are fed to the black level clamp circuit. The black level is set by comparing the colour-difference signal with a DC reference voltage during the burst key component of the sandcastle pulse. For PAL and NTSC modes, both colour-difference signals are clamped on each line. For the SECAM mode, alternate colour-difference signals are clamped on successive lines using the H/2 signal. The black level clamp circuits use the capacitors on pin 6 (R-Y) and pin 5 (B-Y) for storage.

In the SECAM mode only, the colour-difference signals are switched to a SECAM de-emphasis circuit. The de-emphasis time-constants are determined by the capacitors on pin 2 (R-Y) and pin 4 (B-Y). 220 pF capacitors and internal resistors set the SECAM de-emphasis time-constants to  $1.85 \ \mu s$ .

The colour-difference signals are finally fed to the colour-killer switch. When the colour-killer is operational (no colour transmission standard detected) the colour-difference signal outputs are switched to the reference black level. The -(R-Y) and -(B-Y) colour-

difference signals are fed through buffer amplifiers (NPN emitter followers) to pins 1 and 3.

The TDA4650 is in a 28-pin DIL (SOT-117) package and operates over an ambient temperature range of 0 to  $+70^{\circ}$ C.

#### BASEBAND SWITCHED-CAPACITOR DELAY LINES

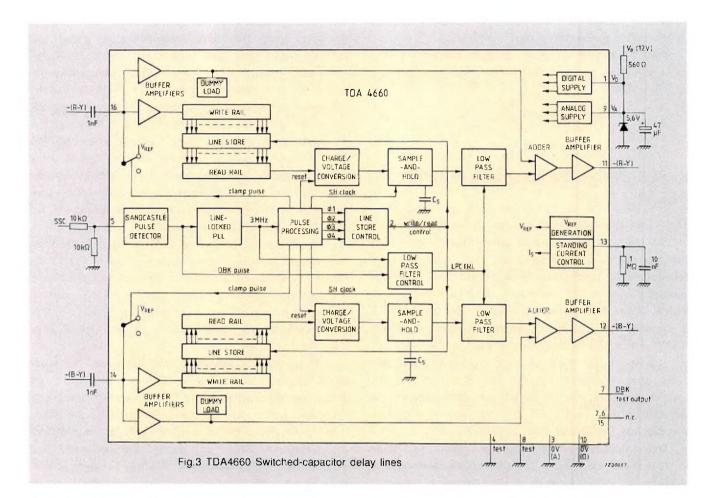

The TDA4660, Switched-Capacitor Delay Line, consists of two colour-difference comb filters. Each comb filter consists of an undelayed signal path and a 64  $\mu$ sdelayed signal path, see Fig.3. All the necessary switching signals are generated from a master clock with a nominal frequency of 3 MHz. The master clock is derived from a 6 MHz Current-Controlled Oscillator (CCO) which is line-locked by a PLL to the burst key component of the sandcastle pulse (SSC). Since the delay lines are locked to the line frequency via the burst key pulses, the TDA4660 functions correctly at the different PAL and NTSC line frequencies and at the variable line frequencies from a VCR.

The switched capacitor delay line operates according to the mode demanded by the colour transmission standard. In the PAL mode it operates as a geometric adder to satisfy the requirements of PAL demodulation. In the NTSC mode it reduces cross-colour interference. In the SECAM mode the delay line repeats the colourdifference signal on consecutive horizontal scan lines. The adder doubles the output signal amplitude in the PAL and NTSC modes.

The colour-difference signals are capacitively coupled to the TDA4660 at pins 16 and 14. The colourdifference signals are clamped at 1.5 V DC ( $V_{REF}$ ) before being fed to the buffer amplifiers of the parallel, delayed and undelayed signal paths. The output of the undelayed colour-difference signal buffer amplifiers are fed directly to one input of the adders. These buffer amplifiers are loaded by dummy loads to ensure that the undelayed colour-difference signal paths have the same frequency and phase response as the buffer amplifiers of the delayed colour-difference signal paths with their capacitive loads. The delayed colour-difference signal paths with their signal is fed to the write rail from where it is switched by the parallel switches to the line store capacitors.

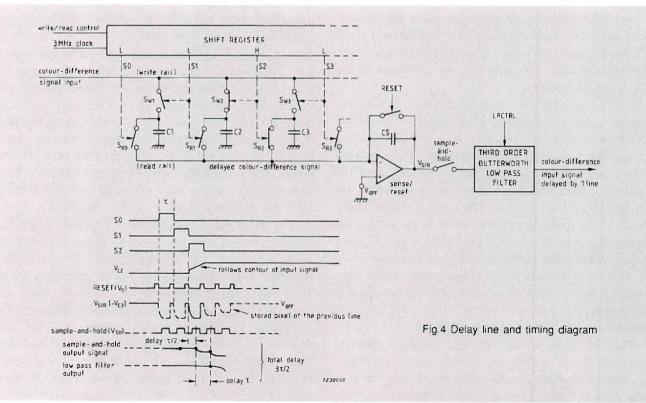

The line store consists of 190 parallel capacitors, each with a write switch and a read switch, see Fig.4. In contrast to most sample-and-delay circuits the line stores have a parallel structure. This eliminates the wellknown cumulative error of series structures (e.g. CCD devices), since the pixel information is stored and delayed using only one write and one read charge transfer. Sampling and storage of the colour-difference signal for a complete horizontal line is performed by connecting each capacitor to the write rail in sequence, controlled by the shift register output logic signal. Simultaneous with writing the n<sup>th</sup> sample on to capacitor  $C_n$ , the  $(n + 1)^{th}$  sample from the previous line is being read, i.e. at the same instant that  $C_2$  is connected to the write rail to write the present colour-difference signal voltage, the charge of  $C_3$  is being transferred via the read rail to the sense/reset capacitor  $C_s$ .

The sense/reset circuit converts the charge read from the storage capacitor into a voltage. This is fed to the sample-and-hold circuit and then to a passive third-order Butterworth low-pass filter. The -3 dB cut-off frequency is 1 MHz which removes the 3 MHz master clock component present in the delayed signal read from the line store.

For a line frequency of 15.625 kHz and a master clock frequency of 3 MHz, there are 192 master clock cycles per horizontal line. There are 190 line store capacitors since due to the clock timing, the delay between the input buffer amplifier and the output from the sense/reset circuit is exactly one horizontal line period minus  $3\tau/2$ , where  $\tau = 333$  ns. The sample-and-hold circuit introduces a delay of  $\tau/2$  and the low-pass filter a delay of exactly  $\tau$ . As a result, the delayed colour-difference signal is delayed by exactly one line period at the input to the adder.

The delayed and undelayed colour-difference signals are added in the adder circuits. To correctly match the delayed and undelayed colour-difference signals, the timing error between them at the input to the adder must be less than 90 ns and the gain error between them less than  $\pm 0.2$  dB. The outputs of the adder circuits are buffered and fed to pins 11 and 12. The output colour-difference signals from the TDA4660 have peak-to-peak levels of -(R-Y) = 1.05 V and -(B-Y) =1.33 V with output impedances of nominally 300  $\Omega$ .

The pulse processing circuits are locked to the line frequency using the burst key component of the sandcastle pulse on TDA4660, pin 5. The timing reference is the leading edge of the burst key pulse. The burst key component is extracted from the sandcastle pulse in the sandcastle pulse detector. The comparator switching threshold voltage is 1.5 V less than the maximum value of the burst key component. This extracted burst key component is the Digital Burst Key (DBK) pulse and is the reference for the linelocked PLL.

#### ANALOG COLOUR DECODER ICs

The line-locked PLL contains a 6 MHz CCO, the frequency of which is divided by two to generate the 3 MHz master clock with a duty factor of 50%. In the PLL, the master clock frequency is divided by 192 to generate the line frequency pulses (FH2). The FH2 and DBK pulses are compared in the phase detector of the PLL and the resultant error signal is filtered and used to correct the frequency of the CCO. The 3 MHz master clock is buffered and fed to the pulse processing circuits.

The pulse processing circuits generate four clock signals ( $\phi$ 1- $\phi$ 4) for line store control, the reset pulse train for the sense/reset circuits, the sample-and-hold clock signals and the clamp pulses for the input buffer amplifiers. The line store clocks are fed to the shift register to clock the switches of the 190 capacitors. The clocked write control pulse controls the duration of the horizontal scan line. The clamp pulses have a duration of 2 µs and occur 1 µs after the leading edge of the burst key component of the sandcastle pulse.

The delay in the third-order Butterworth low-pass filters has to be exactly  $\tau$  to correctly match the delayed and undelayed colour-difference signals at the input to the adder. This delay has to be exact not only for both PAL and NTSC colour transmission standards but also for the variable line frequencies from VCRs. Since all the clocks and pulse trains in the TDA4660 are locked to the line frequency, the shift register logic outputs (S0- S189), sense/reset timing, the sample-andhold clock and the clamp pulses all automatically track the input line frequency. To achieve an exact delay of  $\tau$  in the low-pass filter, it also has to be locked to the existing line frequency. This is achieved by varying the -3 dB cut-off frequency of the Butterworth low-pass filters.

The Butterworth low-pass filters are multiple R/C structures in which the resistor values are controlled by the LPCTRL signal output from the low-pass filter control circuit. This contains a Butterworth low-pass filter, similar to those in the delayed colour-difference signal paths to monitor the delay, a pulse former, a phase detector and all the components necessary for a control loop. The pulse former generates a digital pulse with a duration of 5 clock cycles for every line which is fed to the low-pass filter input. The rise and fall times of the output pulses from this low-pass filter are considerably longer than those of the input pulses due to the filter bandwidth. The delay circuit measures the low-pass filter output voltage at the mid-point of the leading edge and exactly 5 clock cycles after it. When the low-pass filter has the correct bandwidth/delay, the difference between these two voltage measurements is zero. Otherwise, the voltage difference provides the control voltage to correct the bandwidth/delay of the Butterworth low-pass filter in the control loop. This control voltage (LPCTRL) is simultaneously fed to the Butterworth low-pass filters in the delayed colour-difference signal paths so that delay  $\tau$  automatically tracks the line frequency.

The TDA4660 is alignment-free and consumes only 35 mW from a single supply (+5.6 V). The TDA4660 is in a 16-pin DIL (SOT-38) package and operates over an ambient temperature range of 0 to  $+70^{\circ}$ C.

#### PAL/NTSC, SECAM, NTSC FILTERS

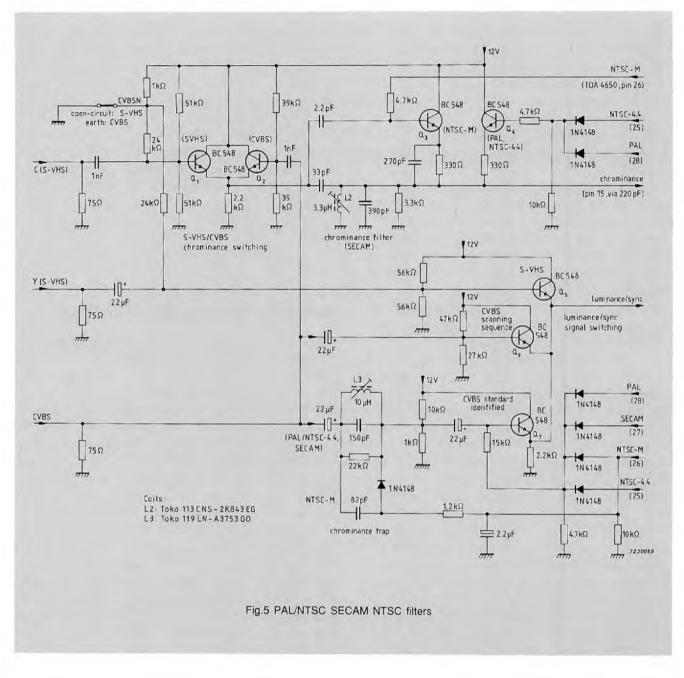

The logic levels of the colour transmission standard switching signals (TDA4650, pins 25, 26, 27 and 28) select the appropriate external chrominance filter. The filter circuits shown in Fig.5 also extract the luminance/sync component from the CVBS signal using chrominance trap, and provide S-VHS/CVBS а chrominance signal selection. The luminance channel is considerably simplified since aperture correction is not included to improve the luminance transient response. This is provided by the TDA4670, Picture Signal Improvement (PSI) Circuit, under control of the  $l^2C$ -bus.

When the CVBSN logic input is open-circuit the S-VHS chrominance signal is selected, when it is LOW, the CVBS signal is selected. The chrominance filter is a bandpass RLC tuned filter with a Q-factor of exactly 16, trimmed to 4.286 MHz in the SECAM mode for HF de-emphasis. For PAL and NTSC-4.4 modes this bandpass filter is substantially damped by a switched parallel 330  $\Omega$  resistor to establish a bandwidth of approximately 1.4 MHz (Q-factor approximately 3.2). In the NTSC-M mode, the resonant frequency of the bandpass filter is set to approximately 3.58 MHz by a switched parallel 270 pF capacitor, again damped by a 330  $\Omega$  parallel resistor. The logic signals from the TDA4650 pins 25, 26 and 28 switch transistors (Q3 and Q4) to select the PAL/NTSC-4.4, SECAM or NTSC-M chrominance filter as required.

The luminance/sync component is selected by one of three parallel emitter followers (Q5 to Q7). The emitter follower in operation is the one with the highest positive potential on its base which consequently switches off the other two. The S-VHS emitter follower (Q5) is switched on when the CVBSN logic input is

#### ANALOG COLOUR DECODER ICs

open-circuit, while the status of the two CVBS emitter followers is determined by the voltage levels on the TDA4650, pins 25, 26, 27 and 28. To avoid bandwidth limitation resulting from filtering during the automatic control and scanning sequence, the CVBS standard identified transistor (Q7) is inhibited by the reduced levels of the colour transmission standard switching signals (approximately +2.5 V). When a colour transmission standard is identified one of the colour transmission standard switching signals rises to typically +5.8 V. This switches on the CVBS standard identified transistor (Q7) and switches off the CVBS scanning sequence transistor (Q6).

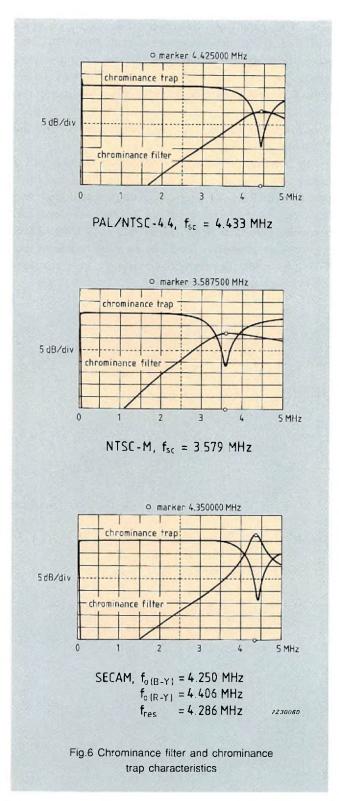

For the PAL-B, G, H, I, SECAM and NTSC-4.4 modes the chrominance trap center frequency is 4.4 MHz. For the NTSC-M mode, the center frequency of the chrominance trap tuned circuit is set to approximately 3.6 MHz by switching an additional 82 pF parallel capacitor. The frequency response characteristics of the chrominance filters and the chrominance traps are shown in Fig.6.

The PAL/NTSC SECAM NTSC filters of Fig.5 ensure that the bandwidth of the luminance signal is not restricted for S-VHS VCR inputs. Completely separate luminance and chrominance signal channels eliminates cross colour and cross luminance interference.

### Alignment Of PAL/NTSC SECAM NTSC Filters and the TDA4650

The PAL/NTSC SECAM NTSC filters require few components and are trimmed, together with the TDA4650, by the following procedure:

- Set CVBSN to LOW.

- Select the SECAM mode by connecting the +12 V supply to TDA4650, pin 27. Connect a SECAM colour-bar signal to the CVBS filter input and trim the 3.3  $\mu$ H inductor of the SECAM Bell filter (L2) for minimum chrominance amplitude-modulation at pin 15 using an oscilloscope.

- Trim the SECAM reference tuned circuit, TDA4650, pins 8 and 9, with the oscilloscope connected to pins 1 and 3 (refer to Fig.2). Adjust the 10  $\mu$ H inductor to set the no-colour level of the -(B-Y) colourdifference signal to the blanking voltage level. Then trim the parallel damping resistor to set the nocolour level of the -(R-Y) colour-difference signal to the blanking voltage level.

- Trim the PAL/NTSC-4.4 crystal oscillator frequency (X1, pin 21) with the PAL mode selected, i.e. TDA4650, pin 28 at +12 V. Set the SERVICE switch to PLL OFF (TDA4650, pin 17 less than 0.5 V) so that the crystal oscillator free-runs and is unaffected by the colour burst signal. Apply the PAL colour-bar signal to the CVBS filter input and trim the 30 pF capacitor in series with X1 for minimum beat frequency (colour rolling on the picture) of the -(R-Y) and -(B-Y) colour-difference output signals.

- Trim the chrominance trap inductor L3 in the PAL mode to obtain the minimum chrominance signal level at the luminance/sync (Y) output.

- Finally, select the NTSC-M mode by setting TDA4650, pin 26, to +12 V. Switch the SERVICE switch to PLL OFF (TDA4650, pin 17 less than 0.5 V) and apply the NTSC-M colour-bar signal to the CVBS filter input. Trim the 30 pF capacitor in series with crystal oscillator X2 for minimum beat frequency (colour tolling) of the -(R-Y) and -(B-Y) colour-difference output signals.

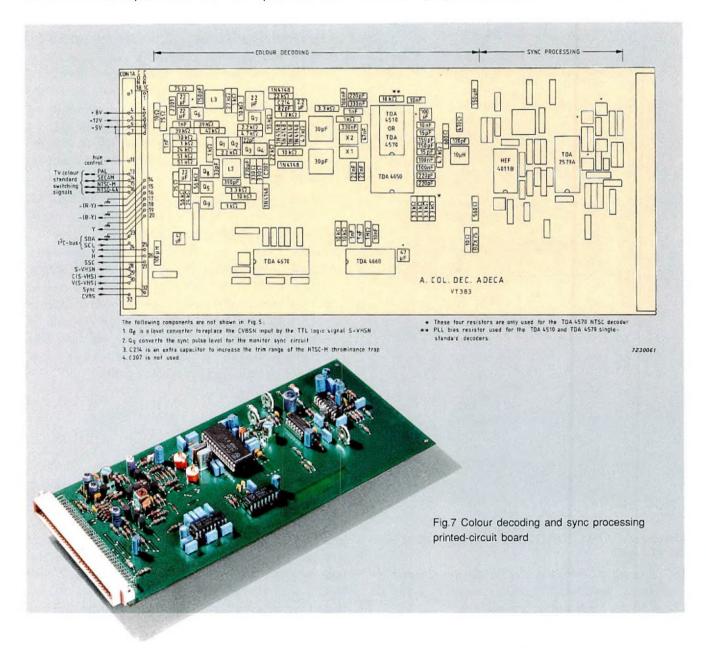

#### APPLICATIONS

The PCB shown in Fig.7 has been designed to include the TDA4650, TDA4660 and the PAL/NTSC, SECAM, NTSC filters. The complete printed-circuit board also includes the TDA4670, Picture Signal Improvement Circuit, the TDA2579A Horizontal/Vertical Synchronization Circuit and a HEF4011B, Quadruple 2-Input NAND Gate (for sandcastle pulse generation). I<sup>2</sup>C-bus control is necessary for the TDA4670 whereas both

#### ANALOG COLOUR DECODER ICs

multi-standard colour decoding and sync processing are independent of  $I^2C$ -bus control. If picture signal improvement is not required, the luminance and colourdifference inputs and outputs of the TDA4670 are bridged by jumpers. The SERVICE switch and the hue control resistors (TDA4650, pin 17) are the only components shown in Figs 2 and 5 which have to be connected externally to the printed-circuit board.

The PCB has a 96-pin connector interface. The inputs are the +12V supply (pin A5), the +8V supply (pin A4), the S-VHSN TTL logic signal (pin A28), the S-VHS chrominance and luminance signal components (pins A29 and A30), the CVBS signal (pin A32), the hue control input (pin A11), the four colour transmission standard switching signals (pins A13 to A16) and the  $1^{2}$ C-bus inputs SDA and SCL (pins A23 and

A24). The outputs are the colour-difference signals (pins C15 and C17), the luminance signal (pin C19), the super sandcastle pulse (pin C27), the monitor sync signal (pin C32) and the vertical and horizontal pulses (pins C25 and C26). The PCB supplies luminance and colour-difference signals to the TDA4680, Video Control Combination Circuit, or indirectly to the TDA4680 via a feature module.

To achieve the versatility needed to manufacture a family of colour decoders all based on the same PCB, the TDA4650 can be used for multi-standard decoding or it can be replaced by either of the single-standard decoders, TDA4510 (PAL) or TDA4570 (NTSC). These are low-cost alternatives and can be used instead of the TDA4650 with the appropriate changes in the colour decoder's peripheral components.

#### PERFORMANCE DATA

Typical performance data for the TDA4650 and TDA4660 are as follows:

#### TDA4650

vertical blanking pulse:

| supply voltage:                            | 12 V        |

|--------------------------------------------|-------------|

| supply current:                            | 65 mA       |

| chrominance signal input (75% colour-bar): | 200 mVpp    |

| -(R-Y) colour-difference output in         |             |

| PAL/NTSC modes:                            | 0.535 Vpp   |

| -(B-Y) colour-difference output in         |             |

| PAL/NTSC modes:                            | 0.675 Vpp   |

| -(R-Y) colour-difference output in         |             |

| SECAM mode:                                | 1.05 Vpp    |

| -(B-Y) colour-difference output in         | ••          |

| SECAM mode:                                | 1.33 Vpp    |

| hue control range in NTSC mode,            |             |

| (pin 17, 3 ±1 V):                          | ±30° min.   |

| transmission standard switching signal,    |             |

| OFF-state:                                 | 0.5 V max.  |

| transmission standard switching signal,    |             |

| scanning-state:                            | 2.45 V      |

| transmission standard switching signal,    |             |

| ON-state:                                  | 5.8 V       |

| transmission standard switching signal,    |             |

| forced selection:                          | 9.0 V min.  |

| TDA4660                                    |             |

| supply voltage:                            | 5.6 V       |

| supply current:                            | 5.5 mA      |

| -(R-Y) colour-difference output,           |             |

| PAL, NTSC, SECAM:                          | 1.05 Vpp    |

| -(B-Y) colour-difference output,           |             |

| PAL, NTSC, SECAM                           | 1.33 Vpp    |

| -(R-Y) to $-(B-Y)$ channel gain tolerance: | ±0.5 dB     |

| delay line time:                           | 64 ±0.06 μs |

| output impedance:                          | 300 Ω       |

| Super Sandcastle Pulse (SSC)               |             |

| burst key pulse:                           | >7.7 V      |

| horizontal blanking pulse:                 | 4.5 ±0.4 V  |

|                                            |             |

2.5 ±0.5 V

#### REFERENCE

Van Gurp. Boudewijns, Van Keeken: 'Switched Capacitor Chrominance Baseband Delay Lines For Colour Decoders', IEEE Transactions on Consumer Electronics, Vol. CE-33, No.3, August 1987.

### Logic level FETs

#### **ARTHUR WOODWORTH**

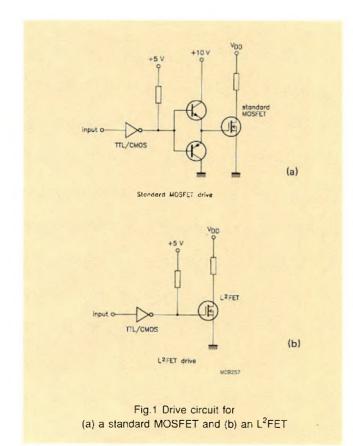

Standard power MOSFETs require a gate-source voltage of 10 V to achieve a 'saturated' on-state condition. With Logic Level FETs ( $L^2$ FETs) however, the same level of saturation is possible with a gate-source voltage of only 5 V. They can therefore be driven directly from 5 V TTL/CMOS ICs without the need for the level shifting stages required for standard MOSFETs. see Fig.1. This

makes them ideal for today's sophisticated automotive electrical systems, where microprocessors are being used to drive switching circuits.

This characteristic of  $L^2$ FETs is achieved by reducing the gate-oxide thickness from about 800 nm to about 500 nm, which reduces the threshold voltage of the device from the standard 2.1 – 4.0 V to 1.0 – 2.0 V. However, the result is a reduction in gate-source voltage ratings, from ±30 V for a standard MOSFET to ±15 V for the  $L^2$ FET. Nevertheless this is still an improvement over the industry standard voltage rating of ±10 V for  $L^2$ FETs.

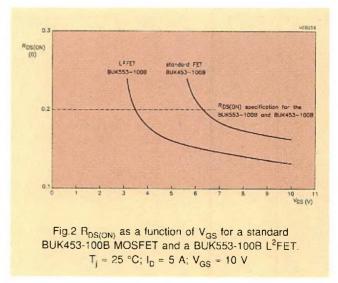

Although a 5 V gate-drive is ideal for L<sup>2</sup>FETs, they can be used in circuits with gate-drive voltages of up to 10 V. Using a 10 V gate-drive results in a reduced  $R_{DS(ON)}$  (see Fig.2), but the turn-off delay time is increased. This is due to excessive charging of the L<sup>2</sup>FET's input capacitance.

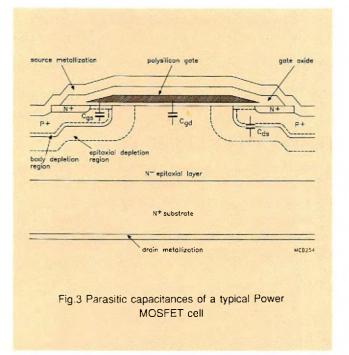

#### L<sup>2</sup>FET CAPACITANCES

Figure 3 shows the parasitic capacitance areas of a typical Power MOSFET cell. Both the gate-source capacitance  $C_{gs}$  and the gate-drain capacitance  $C_{gd}$  increase due to the reduction in gate-oxide thickness, although the increase in  $C_{gd}$  is only significant at low levels of  $V_{DS}$ , when the depletion layer is thin. Increases in input capacitance  $C_{rs}$  output capacitance  $C_{os}$  and reverse transfer capacitance  $C_{rs}$  result in an overall capacitance increase of 25% for the  $L^2$ FET, compared with a similar standard type, at  $V_{DS} = 0$  V. This is not a problem however, as these parasitic capacitances are virtually negligible at the standard measurement condition of  $V_{DS} = 25$  V.

### TRANSCONDUCTANCE AND GATE CHARGE

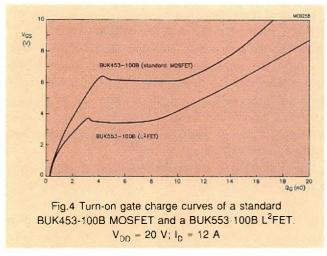

Forward transconductance  $g_{fs}$  is a function of the oxide thickness, so the  $g_{fs}$  of an L<sup>2</sup>FET is typically 40% – 50% higher than a standard MOSFET. This increase in  $g_{fs}$  more than offsets the increase in the overall capacitance of an L<sup>2</sup>FET, so the turn-on charge requirement of the L<sup>2</sup>FET is lower than that of the standard type, see Fig.4. For example, the standard BUK453-100B MOSFET requires about 17 nC to be fully switched on (at a gate-source voltage of 10 V), while the BUK553-100B L<sup>2</sup>FET only needs about 12 nC (at a gate-source voltage of 5 V).

#### SWITCHING SPEED

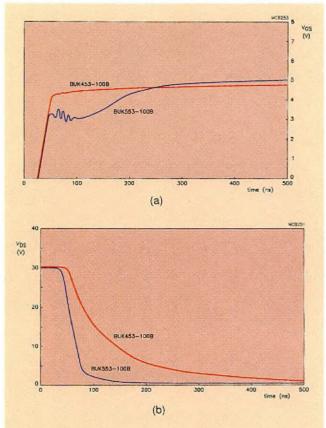

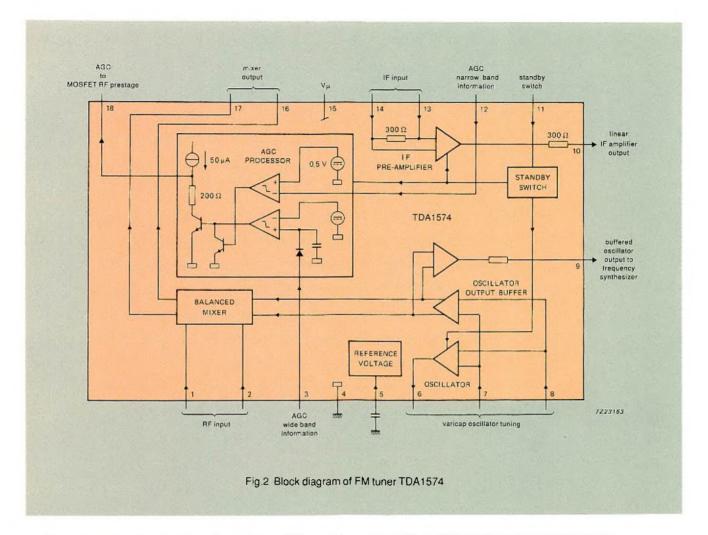

Figure 5 compares the turn-on performance of the standard BUK453-100B MOSFET and the BUK553-100B L<sup>2</sup>FET, under identical drive conditions of 5 V from a 50  $\Omega$  generator, using identical loads. Thanks to its lower gate threshold voltage V<sub>GS(TO)</sub>, the L<sup>2</sup>FET can be seen to turn on in a much shorter time from the low-level drive.

#### LOGIC-LEVEL FETs

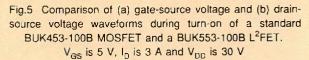

Figure 6 shows the turn-off performance of the standard BUK453-100B MOSFET and the BUK553-100B L<sup>2</sup>FET, again with the same drive. This time the L<sup>2</sup>FET is slower to switch. The turn-off times are determined mainly by the time required for  $C_{gd}$  to discharge. The  $C_{gd}$  is higher for the L<sup>2</sup>FET at low  $V_{DS}$ , and the lower value of  $V_{GS(TO)}$  leads to a lower discharging current, due to the internal resistance of the gate-drive circuit. The net result is an increase in turn-off time.

Fast switching in, for example, automotive applications is not important. In areas where it is important however, the drive conditions should be examined. For example, for a given load power, a 10 V drive requires a 50  $\Omega$  source impedance, whereas a 5 V drive will require one of only 12  $\Omega$ . This results in faster switching for the L<sup>2</sup>FET compared with standard MOSFETs.

#### **RUGGEDNESS AND RELIABILITY**

Automotive applications frequently require  $L^2FETs$  to withstand the energy of an unclamped inductive load turnoff. This energy is dissipated in the bulk of the silicon however, and stress is avoided in the gate oxide. A thinner gate oxide in  $L^2FETs$  does not affect their ruggedness or reliability. Good control of key process parameters such as pinhole density, mobile ion content and interface state density ensures good oxide quality. The present range of  $L^2FETs$  includes devices which can withstand drain-source voltages of up to 400 V.

The  $V_{GS}$  rating of an L<sup>2</sup>FET is about half that of a standard MOSFET, but this does not affect the  $V_{DS}$  rating, which can be the same for both types of FET. In principle, an L<sup>2</sup>FET version of any standard MOSFET is feasible.

#### **TEMPERATURE STABILITY**

In general, threshold voltage decreases with increasing temperature. Although the threshold voltage of  $L^2FETs$  is lower than that of standard MOSFETs, so is their temperature coefficient of threshold voltage (about  $\frac{1}{2}$  in fact), so their temperature stability compares favourably with standard MOSFETs.

#### APPLICATIONS

The automotive industry in particular will benefit from  $L^2$ FETs, which can switch regulators and converters, drive electromechanical parts like motors and solenoids, and are reliable enough to displace mechanical relays. Since they enable power loads to be driven directly from ICs, they may be considered to be the first step towards intelligent power switching. The low voltage ( $\leq 200$  V)  $L^2$ FETs are available in SOT186 and TO220 outlines, and have a  $T_{jmax}$  rating of 175 °C, rather than the industry standard of 150 °C. The projected MTBF is 2070 years at 90 °C, at a 60% confidence level.

### ICs for electronically-tuned car radios

#### ARNOLD GARSKAMP

A moving car is probably the worst possible operating environment for a radio. There are wide variations of battery voltage and temperature, considerable vibration, a lot of interference generated by the engine and constantly changing reception conditions. Furthermore, demands for extra facilities such as cassette and CD players severely limit the amount of space available for radio circuitry. Further difficulties arise because the increasing number of transmissions on the air makes tuning more difficult for the listener who must concentrate on driving rather than operating the radio.

Much research has been devoted to developing radio circuitry to solve these problems; highly integrated circuitry for increased reliability, variable-capacitance diode tuning, interference limiting and DC controlled audio functions are now commonplace. More recent innovations include microcomputer control of tuning with search facilities, preset station selection and digital frequency indication.

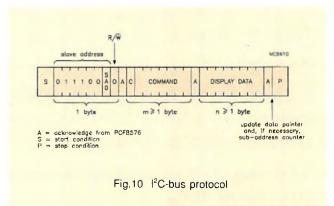

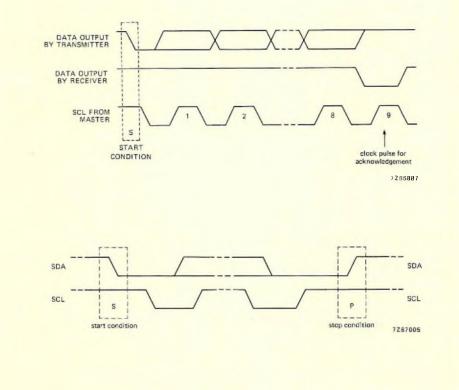

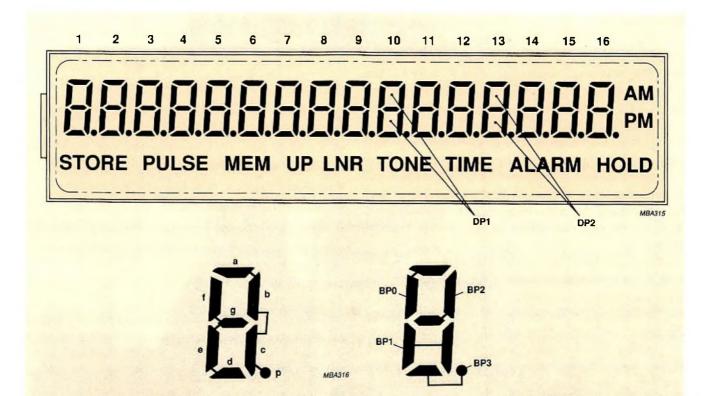

By using our unrivalled experience of developing and fabricating ICs and using them in Philips equipment we have now extended the horizons of car radio design yet further with a set of state-of-the-art ICs for electronically-tuned car radios. To demonstrate the capabilities of this new chip-set, we have developed the circuitry and software for an AM/FM stereo electronic car radio application proposal in which the tuning system, frequency display, stored station memory and audio functions are microcomputer-controlled via the simple bidirectional two-wire Inter IC  $(l^2C)$  bus<sup>11</sup>.

The partitioning of our car radio chip set is determined by the need to avoid peripheral interfaces and to meet the specific requirements of car radios, namely:

- To minimize wiring, the CMOS microcontroller and display driver must be positioned on or near the control panel close to the LCD display.

- To achieve sufficient input sensitivity to match the outputs from the tuner local oscillators, the PLL frequency synthesizer must be bipolar.

- Search tuning stop information is derived by IF counting to eliminate elaborate AM/FM window detection circuitry.

- To avoid spurious feedback and achieve unconditional stability, the IF counter must be as close as possible to the IF circuit from where it receives its input.

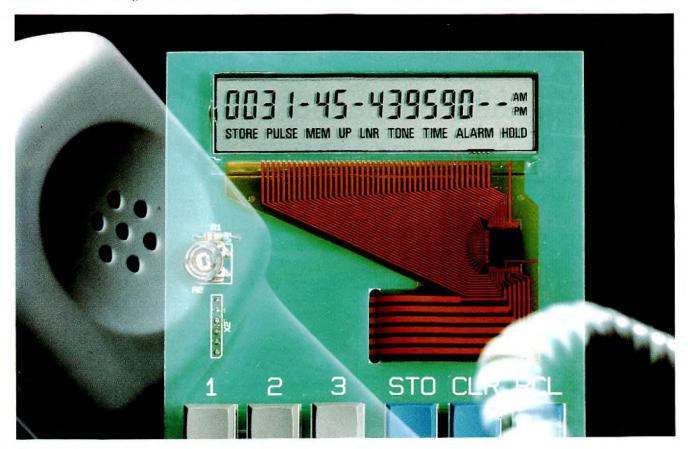

Development model of an electronically-tuned car radio built with the range of ICs described in this article. The control pushbuttons and LCD are in a separate unit (not shown) connected to the main radio by a cable.

(Photo by courtesy of Autosonik, Italy).

<sup>&</sup>lt;sup>11</sup> Purchase of Philips I<sup>2</sup>C components conveys a license under the Philips I<sup>2</sup>C patent to use the components in the I<sup>2</sup>C system, provided the system conforms to the I<sup>2</sup>C specifications defined by Philips.

We have met these requirements by keeping the PLL frequency synthesizer separate from the MOS microcontroller and fabricating it with bipolar technology. We have also integrated the digital IF counter on the same bipolar chip as the analog IF circuit. Future steps in our continuing systems approach to increase the level of integration and minimize peripheral components will include combining the tuner and PLL frequency synthesizer circuitry.

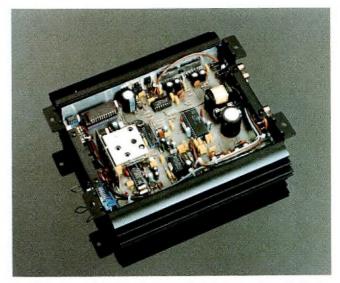

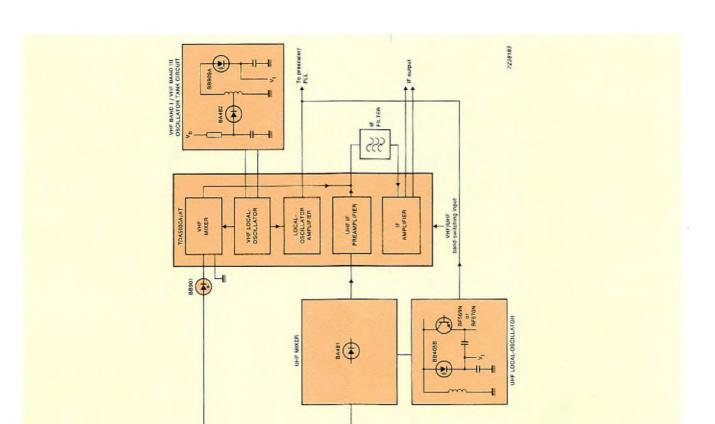

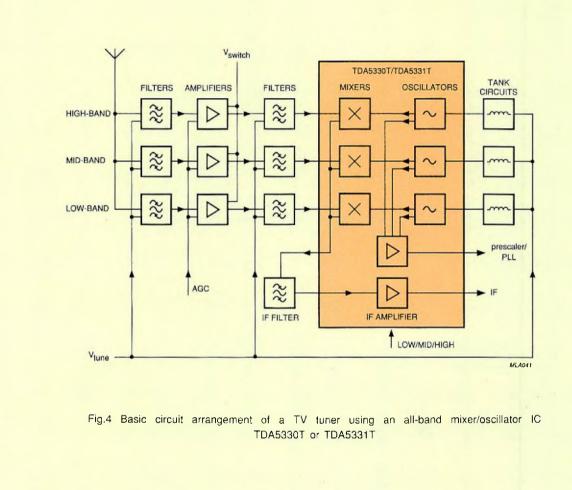

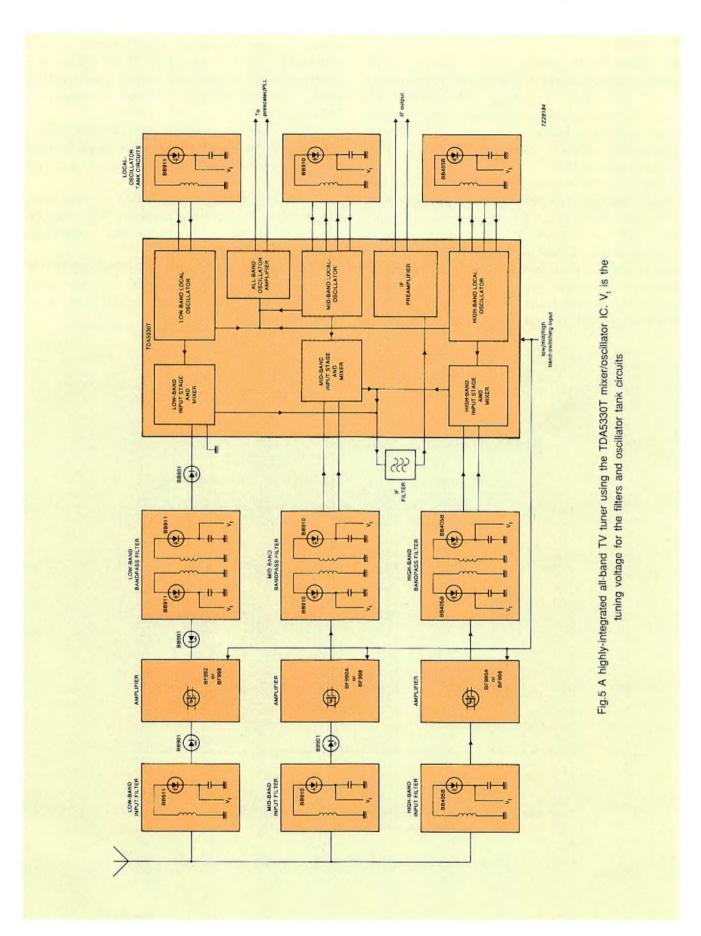

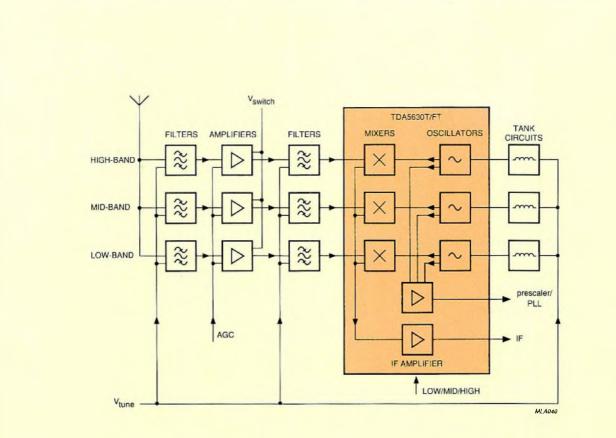

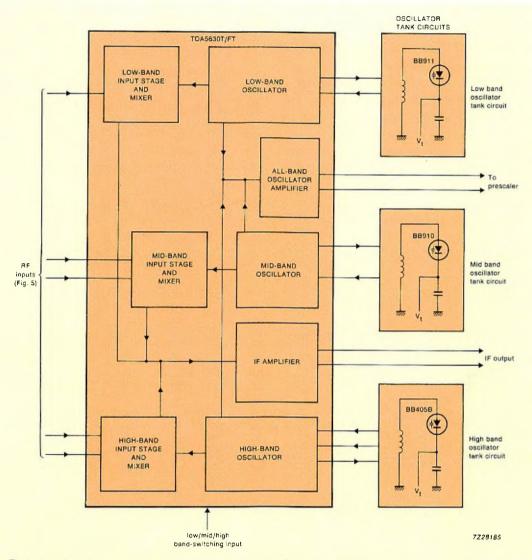

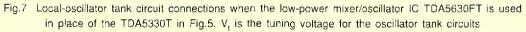

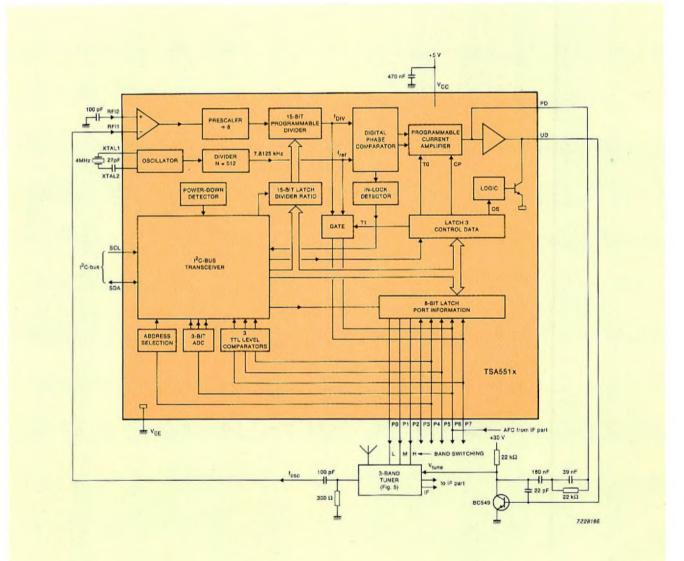

As shown in the overall block diagram of Fig.1, the car radio, the FM and AM tuner sections are integrated in the TDA1574 and TEA6200 respectively. The AM tuner has linear wideband input circuitry which eliminates alignment and AM band switching. Spurious intermodulation products are eliminated because the linear wideband circuitry can handle the strongest signals without influencing the weaker ones. The AM IF is increased to 10.7 MHZ so that low-pass filtering can adequately suppress the image frequency and higher out-of-band frequencies.

We have also increased the integration level of the IF system and tuning interface TEA6100. Since the main function of the digital section of this IC is to determine the correct tuning point for AM/FM stations (centre of the IF bandpass characteristic) by counting the 10.7 MHz IF, AFC is no longer necessary. We have therefore been able to insert a field-strength dependent (soft) muting stage with switch-on delay between the high gain IF amplifier and the FM detector in the analog section of the IC. Although the FM detector is a highly-integrated quadrature type, the soft

muting stage gives it the performance advantages of a discrete component ratio detector (good AM suppression and effective noise reduction during weak signal reception). The soft muting stage is controlled by an adjustable level from five internal IF level detectors. On FM, multipath and adjacent channel information is also derived from the level signal and can be used externally to automatically adjust the high-frequency audio response and/or control the stereo channel separation, or skip the station during search tuning.

The PLL frequency synthesizer TSA6057 is used for electronically tuning the AM and FM sections. It has a digital memory phase detector with its output applied to a programmable charge pump so that the loop gain can be software controlled to combine fast search tuning with stable locking. Two loop amplifiers allow the loop characteristics to be independently set for AM and FM.

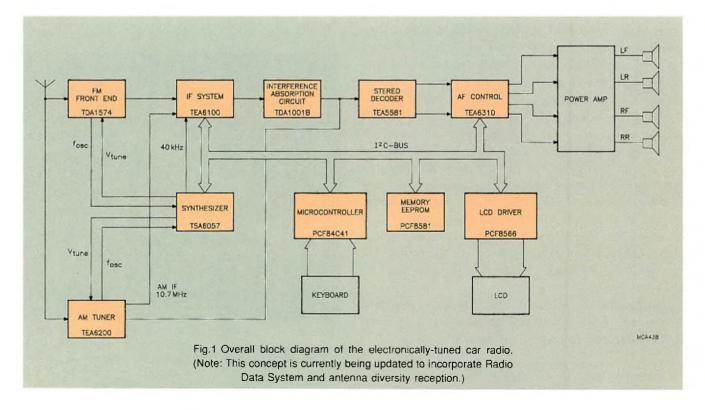

#### **FM TUNER TDA1574**

This bipolar IC (Fig.2) contains a mixer/oscillator, a singlestage linear IF preamplifier and an AGC processor which controls the gain of an external dual-gate MOSFET RF preamplifier with selectivity determined by external varicap-tuning at its input and output. The aerial is capacitively coupled to the tuned input circuit of the MOSFET.

The varicap-tuned oscillator is formed by a differential amplifier with an internal buffered connection to the mixer and an additional buffered output for direct connection to the frequency synthesizer. The mixer is a double-balanced multiplier to obtain good large signal handling and minimize radiation of the oscillator signal from the aerial. Its output is LC tuned for matching to an external ceramic filter at the input of the IF preamplifier. The output from the IF preamplifier is coupled to the IF system in the TEA6100 via a 10.7 MHz ceramic filter.

Additional features of the TDA1574 are:

- The AGC processor can be controlled by a combination of narrow-band and wide-band information (keyed AGC) or by narrow-band or wide-band information only.

- A stabilized reference voltage is available for setting the oscillator frequency range via a potentiometer.

- An electronic standby switch disables the oscillator. IF amplifier and AGC processor during AM reception.

- Oscillator is free of phase noise.

- Wide dynamic range and low noise figure.

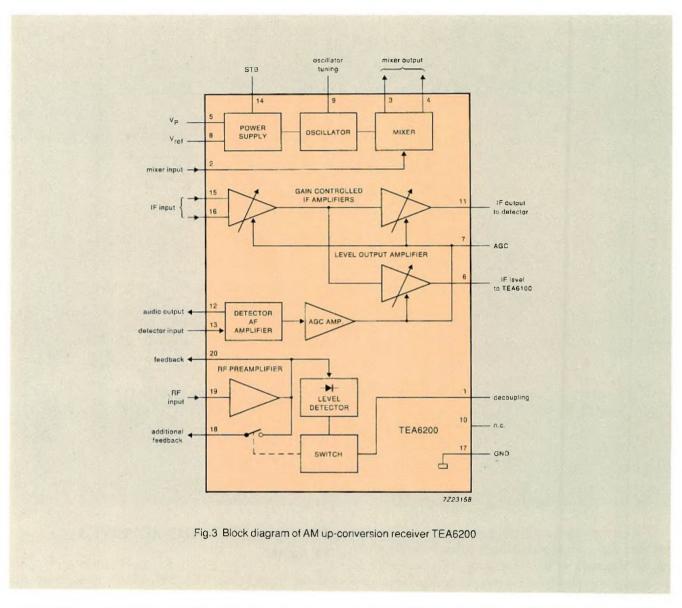

#### AM UP-CONVERSION RECEIVER TEA6200

At the input to the TEA6200 (Fig.3), a wideband RF preamplifier with capacitive feedback eliminates the need for input tuning and LW/MW/SW band switching components. Wide aerial input dynamic range (up to at least 2 V) is ensured by internally applying the output from the RF pre-amp to a level detector. For input signal levels above 320 mV, this detector operates an internal switch which can reduce the RF preamplifier gain by using an additional capacitor to increase the negative feedback.

Since this up-conversion receiver has an IF of 10.7 MHz, the image frequency is easily suppressed by a low-pass filter between pins 20 and 2 before the RF signal is applied to a double-balanced mixer. A local oscillator LC circuit at pin 9 is varicap tuned by a tuning voltage from frequency synthesizer TSA6057.

The IF output from the mixer is transformer coupled to a ceramic filter which determines the selectivity of the system at the input to the wideband gain-controlled IF amplifier.

An IF signal for use in the IF system and microcomputerbased tuning interface IC TEA6100 is derived from pin 6 and passed through a ceramic filter to eliminate noise and spurious signals. Another ceramic filter at the output of the IF amplifier serves the same purpose for the IF signal before it is demodulated and passed through an audio preamplifier to the output at pin 12.

Other features of the TEA6200 are:

- The RF input is protected against lightning induced surges.

- The high IF increases the oscillator frequency so that only a small min/max capacitance ratio is required to tune it. This means that an inexpensive single diffused varicap as used for FM radios can be used.

- Doesn't require alignment.

#### FM IF SYSTEM AND MICROCOMPUTER-BASED AM/FM TUNING INTERFACE TEA6100

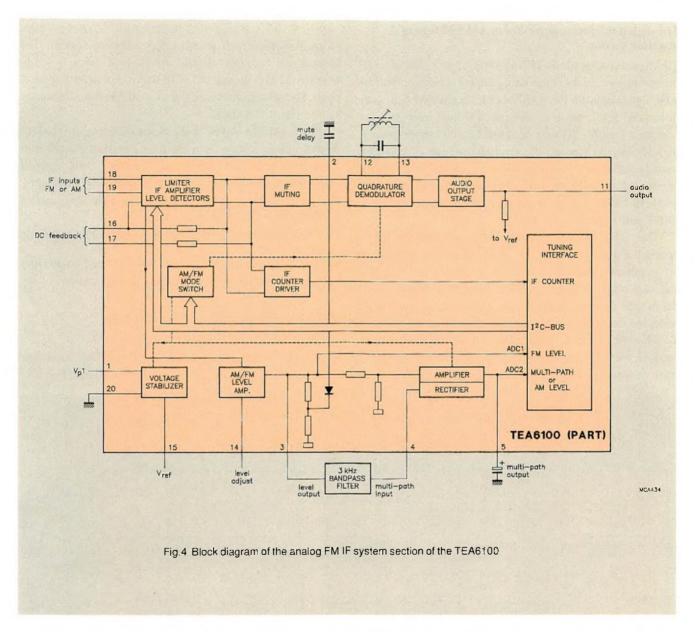

#### The analog FM IF system section

The analog section of the TEA6100 (Fig.4) can be softwarecontrolled to operate in an FM or AM mode. It comprises a 4-stage symmetrical limiting IF amplifier followed by IF level detectors/amplifier and a driver for the IF counter in the digital tuning interface section of the IC. In the FM mode only, the IF amplifier is followed by a soft muting stage, quadrature demodulator and a single-ended audio output stage. The IF signals from the AM (460 kHz or 10.7 MHz) and FM (10.7 MHz) front ends are applied to the software selectable inputs of the IF amplifier, the sensitivity of which can be adjusted at pin 14 to compensate  $\pm 10 \text{ dB}$ spreads of front-end gain.

The soft muting stage is controlled by a voltage derived from the IF level detectors which is also passed to the microcomputer via the digital tuning interface and made available at pin 3. A capacitor at pin 2 causes a delay so that the muting stage is switched on quickly and off slowly to avoid on/off effects due to rapid variations of the aerial signal. On FM, the level detectors also sense multipath and adjacent channel information which, after filtering at pins 3 and 4, is internally rectified, passed to the digital tuning interface and made available at pin 5. On AM, a capacitor at pin 5 decouples the amplitude modulation from the level information. The multipath/adjacent channel information at pin 5 during FM reception can be used to automatically adjust the high-frequency audio response and/or control the stereo channel separation, or skip the station during search tuning.

The inclusion of signal-dependent muting with switchoff delay after the IF amplifier allows considerable reduction of the number of peripheral components. This is because it allows the FM demodulator to be a highly integrated symmetrical quadrature type but adds the AM suppression and noise limiting capabilities more usually associated with a ratio detector which cannot be integrated.

Other features of the analog section of the TEA6100 are:

- A voltage stabilizer based on the band-gap principle allows the circuit to operate with a supply of between 7.5 V and 12 V.

- A reference voltage at pin 15 is switched on by software during FM operation. This is used as a source of level adjustment voltage for pin 14 on FM and allows the level adjustment voltage to be derived from an external source on AM.

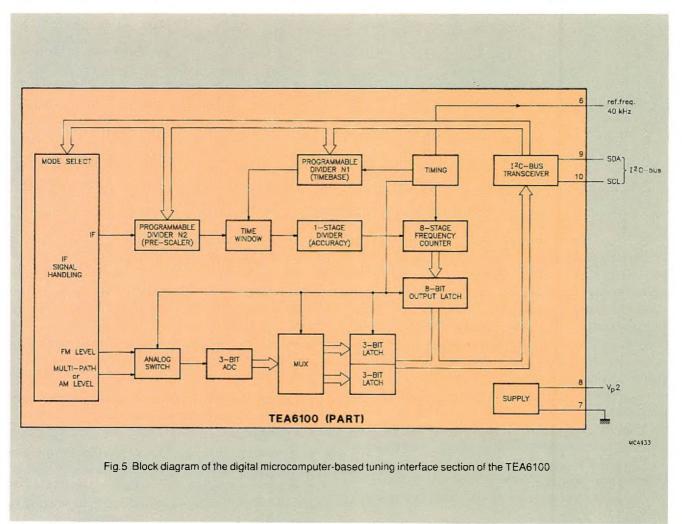

### The digital microcomputer-based AM/FM tuning interface section

The digital section of the TEA6100 (Fig.5) consists of an IF measuring system for determining the exact tuning point, an ADC and latches for the AM/FM IF level and FM multipath distortion level signals, and an I<sup>2</sup>C-bus interface for computer control. Because of the different channel spacing of AM and FM signals, the resolution of the IF counting must be adjustable. A unique feature of this IC is its ability to count a 10.7 MHz AM IF with a resolution of 500 Hz, a 460 kHz AM IF with a resolution of 250 Hz and a 10.7 MHz FM IF with a resolution of 6.4 kHz.

The AM/FM IF measuring system consists of a programmable prescaler, a time window circuit, a programmable timebase circuit, a 1-stage accuracy divider and an 8-stage frequency counter. The time window circuit defines the counting period. For example, if the window is wide, the counting period is long and the accuracy is high. To allow flexibility of application, a trade-off can be made between measuring speed and accuracy by switching the 1stage accuracy divider on (wide window/slow speed) or off (narrow window/high speed) under software control. The control and window signals are derived from a stable external 32 kHz source or, as in this radio, from a quartz-controlled 40 kHz reference signal available from frequency synthesizer IC TSA6057.

The AM/FM level and multipath/adjacent channel distortion information from the analog section is applied to a multiplexed 3-bit ADC and latched. This latched information, and the 8-bit latched IF count can be read by the microcomputer via the I<sup>2</sup>C-bus which also carries control data for AM/FM mode switching.

Other features of the digital section of the TEA6100 are:

- The power supply lines are fully isolated to prevent crosstalk between the digital and analog sections of the IC.

- Prescaler programmable for AM/FM and 460 kHz/10.7 MHz operation.

- Timebase circuit programmable for AM/FM, 32 kHz or 40 kHz reference frequency and high/low resolution.

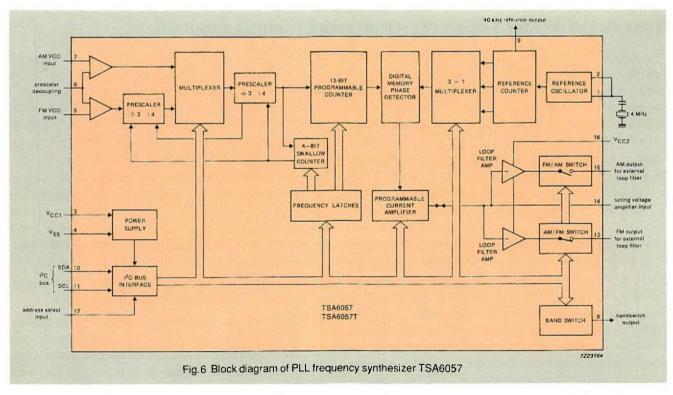

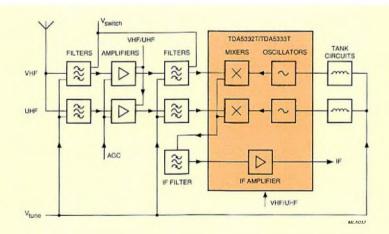

#### PLL FREQUENCY SYNTHESIZER TSA6057

As shown in Fig.6, this is an I<sup>2</sup>C-bus controlled AM/FM PLL frequency synthesizer with sensitive prescalers to receive VCO signals directly from the AM and FM tuners, a frequency counter comprising a 4-bit swallow counter plus a 13-bit main counter, a powerful digital memory phase detector for fast tuning and individual software-selected active loop filters for generating tuning voltages up to 10.5 V for the AM and FM tuners. The RC networks for the loop filters are external so that the loop characteristics can be individually determined for AM and FM. The IC has an operating frequency range of 512 kHz to 30 MHz for AM and 30 MHz to 150 MHz for FM. An on-chip low-distortion oscillator/counter controlled by a 4 MHz crystal generates a software-selectable internal reference frequency of 1 kHz, 10 kHz or 25 kHz for the phase detector on either AM or FM. It also generates a 40 kHz reference signal for the IF counter in the digital tuning interface section of the TEA6100.

Additional features of the TSA6057 are:

- The phase detector output is applied to programmable charge pump so that the loop gain can be software-controlled to ensure fast tuning and stable locking.

- Includes a software-controlled open-collector AM/FM switch.

- The I<sup>2</sup>C-bus interface address includes a bit that can be hard-wire programmed so that two synthesizers can be used in the same system.

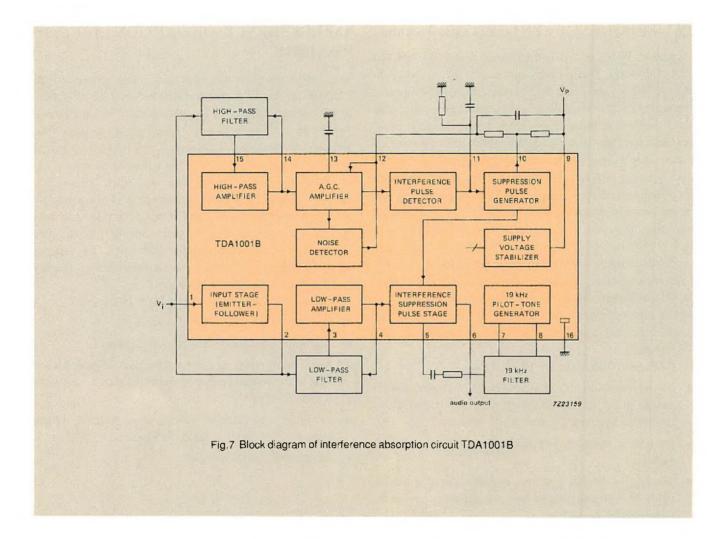

### INTERFERENCE ABSORPTION CIRCUIT TDA1001B

Our well-known interference and noise absorption IC TDA1001B (Fig.7) is incorporated between the IF system and the stereo decoder of the FM channel. Its operation is based on active high-pass filtering to separate the interference from the audio signal and using it to trigger suppression pulses to interrupt the audio signal after it has been delayed by an active low-pass filter. During the suppression periods, the audio output level is maintained by an external RC network. An internal 19 kHz generator sustains the stereo pilot tone during interference suppression. An AGC circuit decreases the trigger sensitivity during high duty factor interference, thereby preventing excessive/audio distortion.

Other important features of the TDA1001B are:

- Operates from a supply of 7.5 V to 16 V.

- Adjustable sensitivity to interference spikes.

- After interference absorption, the peak-to-peak amplitude of the residual pulse on the audio signal waveform is less than 3 mV.

- Continues to absorb interference spikes during extremely high level noise at the input.

- Internal voltage stabilization.

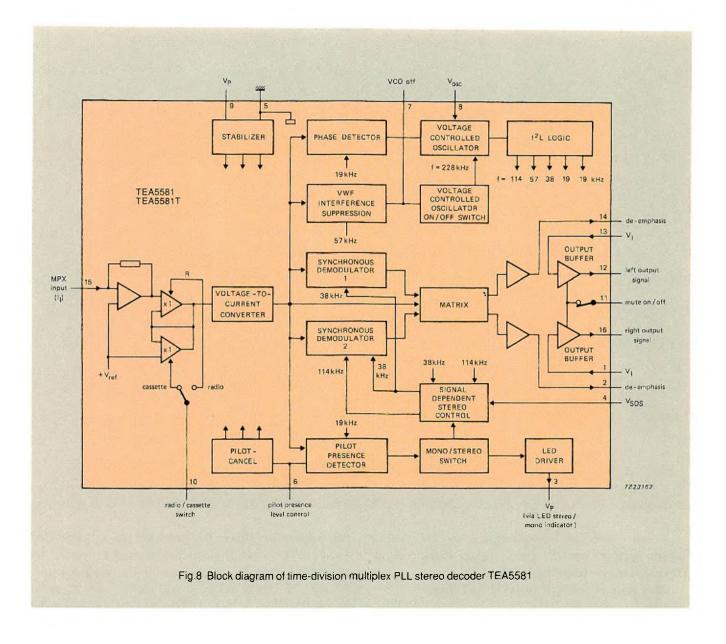

#### **TIME-DIVISION MULTIPLEX PLL STEREO DECODER TEA5581**

The main function of this IC shown in Fig.8 is to extract the L-R stereo information by phase comparing the detected stereo MPX signal with a stable 38 kHz subcarrier regenerated by a PLL. The L-R information is then matrixed with the MPX signal to recover the two stereo outputs. A radio/cassette switch input allows the MPX signal to be muted so that audio signals from an AM radio or cassette player can be applied to the  $V_1$  inputs of the output buffers which can be muted for silent tuning.

In addition to regenerating the 38 kHz subcarrier, a divider following the 228 kHz VCO in the PLL also generates a 19 kHz phase detector reference for locking the PLL to the pilot tone and a second 19 kHz reference (in phase with the pilot tone and in quadrature with the phase detector reference) for a pilot presence detector which drives a mono/stereo switch and "stereo" LED driver. The perfect symmetry of these squarewave reference signals results in a high degree of interference suppression and good channel separation. However, since the reference signals are squarewaves, demodulation of odd harmonics is

inevitable. To eliminate the effects of this, the frequency divider following the PLL also generates a 114 kHz reference for a second demodulator which generates a signal for suppressing the 3rd harmonic of the regenerated subcarrier. The frequency divider also generates 57 kHz for a circuit which suppresses interference caused by German traffic warning (VWF) broadcasts. The 19 kHz pilot tone is cancelled under control of the pilot presence detector before the MPX signal enters the demodulator. During weak signal reception, a signal dependent stereo (SDS) circuit, under control of a signal strength dependent signal from the FM IF system IC TEA6100, ensures smooth control of the stereo channel separation. Other features of the TEA5581 are:

- Compensation of an IF roll-off of 2 dB at 38 kHz results in 40 dB channel separation without adjustment.

- Supply voltage stabilization allows operation between 7 V and 16 V, gives excellent supply ripple rejection and a VCO frequency which is almost independent of supply voltage. The VCO can be inhibited during AM reception.

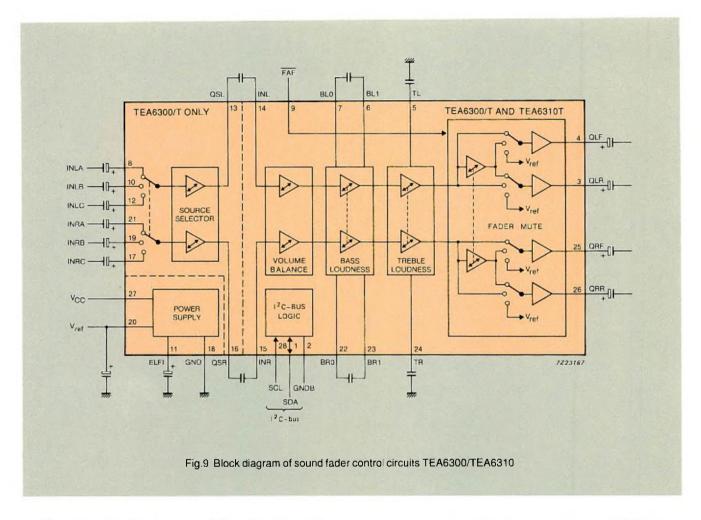

#### SOUND FADER CONTROL CIRCUIT TEA6300/TEA6310

The TEA6310 (Fig.9) consists of resistive voltage dividers connected to multi-input op-amps, the tail currents of which are digitally controlled to adjust volume level, stereo balance, bass level, treble level and fader/output selection. The advantages of this principle are very wide dynamic range combined with low noise and distortion because the gain is distributed over several stages. The low noise and distortion figures have resulted in approval for use with cassette players with Dolby B and C noise reduction.

The volume control has a maximum internal gain of 20 dB and a control range of 86 dB with a step resolution of 2 dB. The volume control also has a mute position for silent search tuning and preset station selection. The mute is automatically activated during switch on/off to eliminate

switching noise. Stereo balance control is achieved by individually adjusting the volume control of the two stereo channels.

The bass and treble controls have control ranges of +15 dB to -12 dB and +12 dB to -12 dB respectively, adjustable in 3 dB steps.

The fader control is independent of the volume control and has a control range of 0 to -30 dB in 2 dB steps. It permits sound distribution adjustment between two stereo pairs audio power amplifiers (front and back) and incorporates an extra mute function to silence a speaker pair. There is also a hardware override facility to permanently silence a speaker pair in a two-speaker system. The nominal output per channel into a 5 k $\Omega$  load is 500 mV.

If source selection is required (e.g. for FM, AM or cassette player inputs), sound fader control circuit TEA6310 can be replaced with a TEA6300.

Other features of the TEA6300/TEA6310 are:

- THD of only 0.05% at full output over the frequency range 20 Hz to 12.5 kHz.

- Input level for clipping is >1.65 V with an 8.5 V supply and >3 V with a 12 V supply.

- Crosstalk between the l<sup>2</sup>C-bus inputs and the audio output is -110 dB.

- Typical supply current consumption is 26 mA.

### CAR RADIO AUDIO POWER AMPLIFIER ICS

There is a trend in car radios toward higher audio output power because of the low efficiency loudspeaker enclosures and an increasing requirement for a wider dynamic range to suit compact disc reproduction. There is also a need to reduce the number of peripheral components because of the lack of space within the case of the radio. These requirements have led to the increasing use of Bridge-Tied Load (BTL) configurations which don't require an electrolytic capacitor in series with the loudspeaker(s). Finally, for power boosters and radios with an audio preamplifier like our TEA6310, the overall gain of the audio power amplifier need only be 20 dB instead of the 40 dB required for radios without an audio preamplifier. Our range of audio power amplifier ICs for car radios is fully described in the brochure 'Audio power amplifier ICs', ordering code 9398 369 00011.

### RADIO COMPUTER-CONTROL SYSTEM CCR310S

CCR310S is a radio receiver local/remote control system based on a PCF84C41 microcontroller with a software package to control radio functions such as tuning, sound functions and keyboard decoding via the simple 2-wire bidirectional  $l^2$ C-bus. It is adaptable for application in all markets.

#### **Microcontroller PCF84C41**

The PCF84C41 is a single-chip microcontroller used as the control processor for the radio. It has an 8-bit CPU, a 128-byte RAM, a 4 K ROM, an 8-bit programmable timer/event counter, a single level, three source interrupt structure and a hardware 1<sup>2</sup>C-bus interface. It is in a 28-pin DIL or SO package.

A similar microcontroller incorporating an LCD driver with 24 outputs (max. 96 segments) will be available shortly. This microcontroller (PCF84C430) will be in a 64lead quad flat-pack (SOT-208).

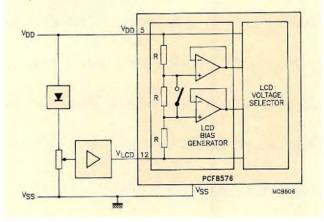

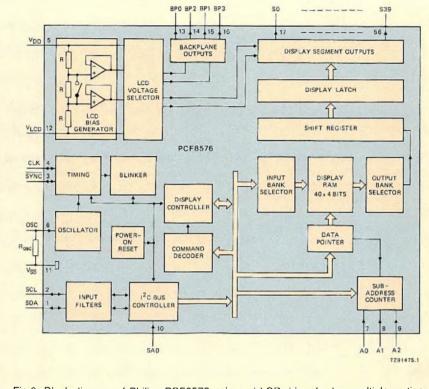

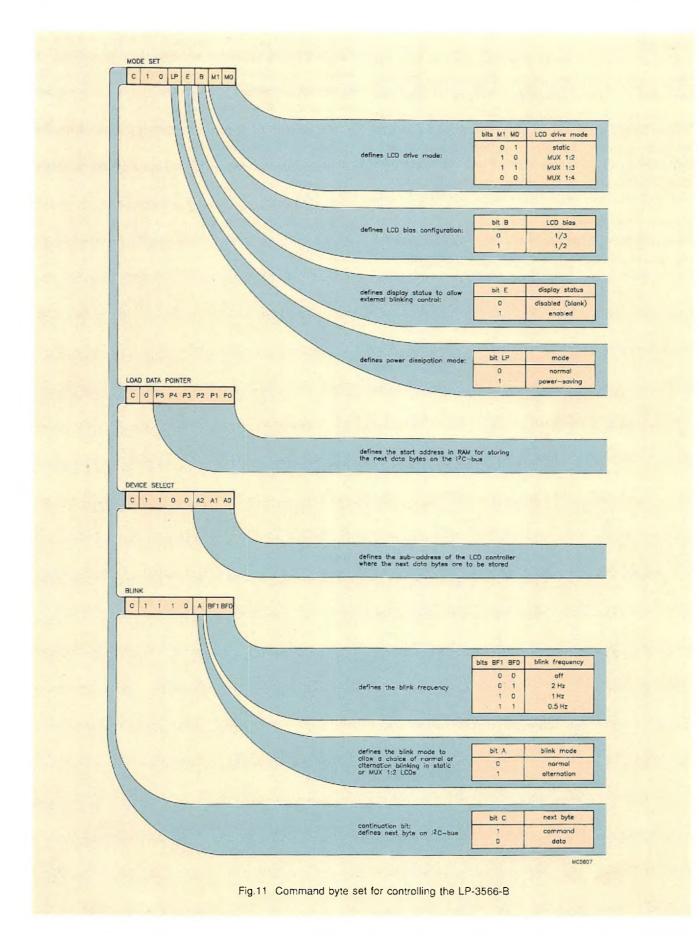

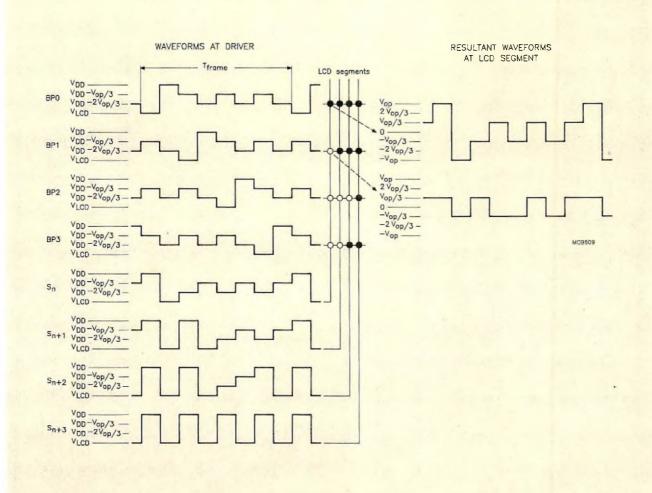

#### Universal LCD driver PCF8566

The PCF8566 interfaces to almost any LCD with low multiplex rates. It generates the drive signals for any static or multiplexed LCD containing up to four backplanes and up to 24 segments. It can be easily cascaded for driving larger LCDs.

#### EEPROM PCF8581

The PCF8581 is a  $5 \vee 1$ -Kbit electrically-erasable programmable read-only memory organized as 128 bits by 8 bits. The stored information can be altered word by word.

#### Brief specification of the system

#### Tuning

- Three frequency bands; FM, MW and LW.

- Automatic store (AST) tuning for FM and AM.

- Five presets for each band  $(2 \times 5 \text{ for the FM band})$ .

- Manual tuning up and down.

- Search tuning up and down.

- Direct access to a preset frequency.

- Silent search tuning (no interstation noise).

- Saving of last selected band and frequency.

#### Display

- 48 segment LCD, 1:3 multiplex, or LED.

- Indication of frequency, band, preset programme number, stereo, AST, loudness, signal level, cassette (CR) etc.

- Indication of bass, treble, stereo balance, fader, manual tuning ('t'), programming ('p') of the EEPROM and the position of balance, fader, bass or treble.

- Blinking during the AST search.

#### Control

• Up to 17 control keys.

#### Sound

- Volume, balance, fader, bass and treble control.

- Automatic muting during search tuning.

- Loudness switching.

- Sound settings in which unique frequency responses for different wavebands are programmable. These settings are recalled after power-on reset.

- Stereo/mono switching.

#### Memory

- Storage of 20 presets; 10 for FM, 5 for MW and 5 for LW.

- Storage of 10 presets for AST tuning; 5 for FM and 5 for MW.

- Storage of the analog sound control settings; volume, balance, fader, bass, treble, loudness and mute control.

- Storage of the last selected band and frequency at switch off.

- Check bytes to test whether the EEPROM is programmed.

#### **Options**

- Remote control with up to 32 keys.

- Enable or disable the loudness function.

- A single key to select balance, fader, bass and treble instead of four keys.

- 5 or 10 FM presets.

- Inputs for stereo cassette player and CD player.

#### **Power-on functions**

- Check if EEPROM is programmed; if not, then program it.

- Recall the last tuned frequency, sound controls and switch settings.

#### **Power-off functions**

• If the frequency has been changed since the radio was switched off, store the new frequency in the EEPROM before going into the "idle" mode.

#### **CUSTOMER SUPPORT**

#### PC-controlled demonstration board

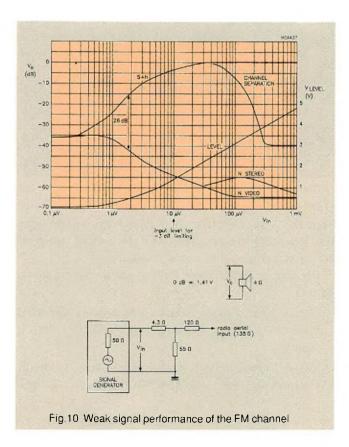

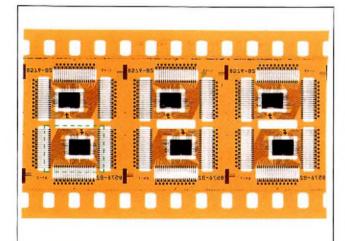

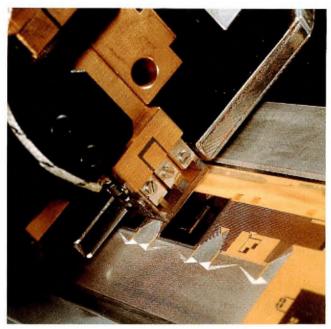

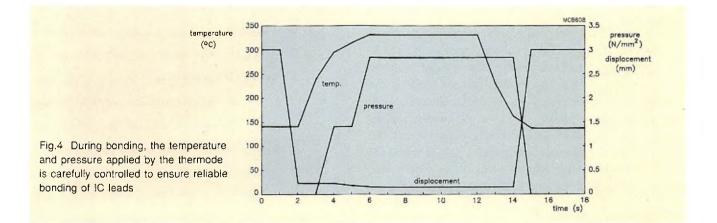

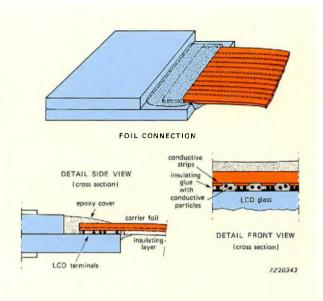

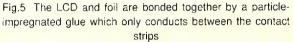

Digital tuning and control of radios via the simple 2-wire bidirectional Inter IC (I<sup>2</sup>C) bus has brought many benefits to both manufacturers and listeners. However, it has also caused many new headaches for design and service engineers who have to quickly gain an understanding of digital techniques and software with which they were previously unfamiliar. To help solve this problem, we've now extended our radio IC applications support to embrace both hardware and software.