# design techniques for electronics engineers

**World Radio History**

Mic. WILLIAMS

PROPERTY OF ORG. 8413

# design techniques for electronics engineers

#### **ELECTRONICS BOOK SERIES**

#### Also published by Electronics

- Microprocessors

- Large scale integration

- Data communications

- Applying microprocessors

- Circuits for electronics engineers

Library of Congress Catalog Card No. 77-8323

Copyrighte 1977 by McGraw-Hill, Inc. All rights reserved. Printed in the United States of America. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without the prior written permission of the publisher.

McGraw-Hill Publications Co. 1221 Avenue of the Americas New York, New York 10020

# design techniques for electronics engineers

### Electronics Magazine Book Series

## table of contents

#### 1. Easy steps to printed circuit boards

- 1. Ribbon cable makes coils for printed-circuit boards

- 2. Etching your own pc boards quickly and accurately

- 3. Soluble masks protect pc boards from solder

- 5. Versatile breadboard checks out designs quickly

- 7. Laminated bus strips ease pc-board layout

- 8. DVM locates short circuit on wired circuit board

- 10. Liquid crystals isolate electrical short circuits

- 11. Current tests ensure IC-package orientation

- 13. Make your own small switches for pc boards

#### 2. Microcircuit assembly techniques

- 14. Estimating substrate area and density for hybrid microcircuits

- 15. Hand-soldered DIP circuits can save testing dollars

- 16. Evaluating power dissipation in microcircuit design

#### 3. Selecting circuit components

- 18. Mixed dielectrics improve capacitor stability

- 18. Designing with preferred component values cuts costs

- 20. Comparing the power of C-MOS with TTL

- 22. Examining worst-case fan-out of standard C-MOS buffers

- 23. Drift-matched IC op amps can save money

- 24. How to really look at low-drift IC op amps

- 26. Ac power considerations in capacitor selection

- 28. Summing up the front-release rear-release connector debate

- 30. A guide to hybrid-circuit component compatibility

- 32. Bistable action of 555 varies with manufacturer

#### 4. Adjusting component values

- 33. Accurately trimming closed resistor loops

- 34. Pc board forms custom variable capacitor

- 36. Transistor gain boosts capacitor value

#### 5. Displaying LED versatility

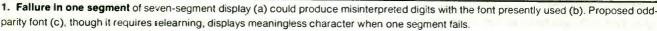

- 37. A fail-safe font of seven-segment digits

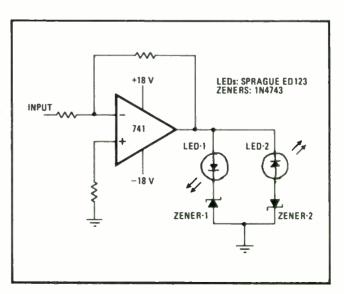

- 38. LEDs watch for overvoltages

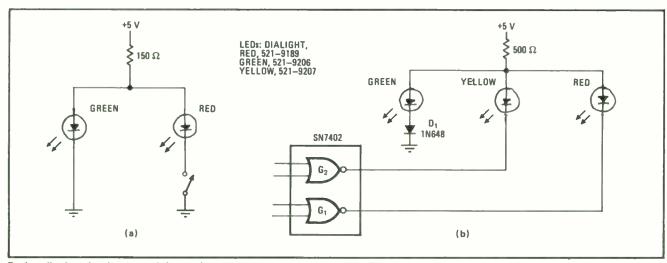

- 39. Different-color LEDs can switch each other

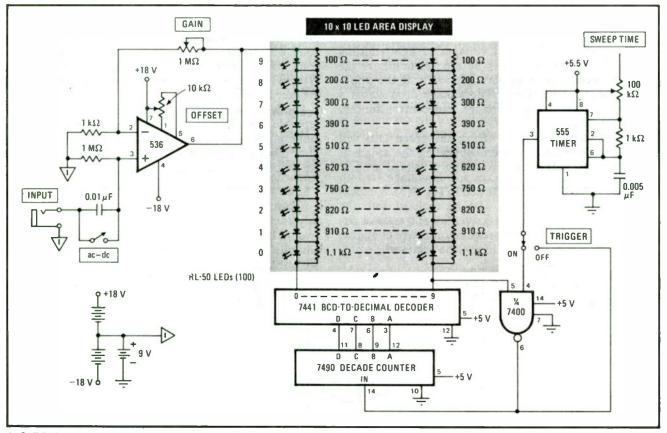

- 40. LEDs replace CRT in solid-state scope

- 41. Large hexadecimal display is legible from afar

- 43. Built-in LED display decoder simplifies digital-clock logic

- 44. Driving LEDs directly from C-MOS logic outputs

- 44. Seven-segment indicator shows Roman I through V

- 45. Light-emitting diode doubles as sensor

#### 6. Novel delay lines

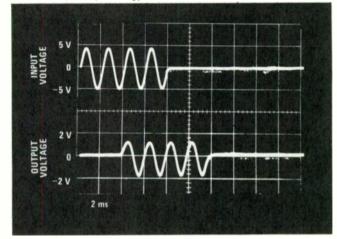

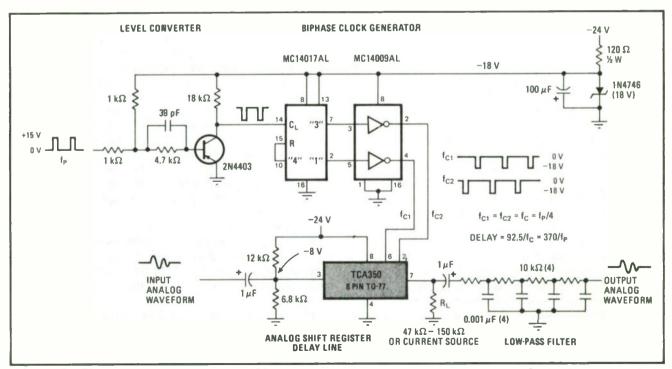

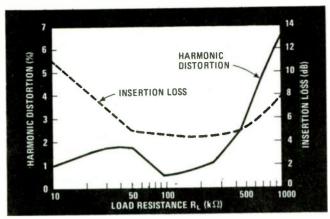

- 46. Bucket-brigade shift register generates constant phase delay

- 47. C-MOS decade divider clocks bucket-brigade delay line

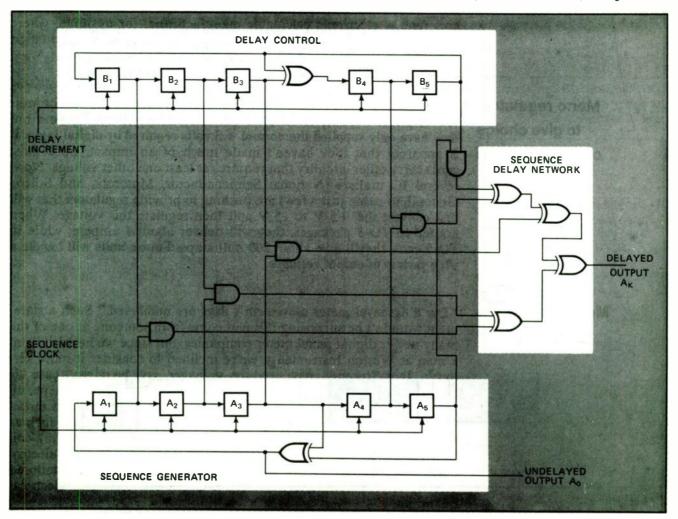

- 48. Logic approach to time delay uses only integrated circuits

#### 7. Displays have many forms

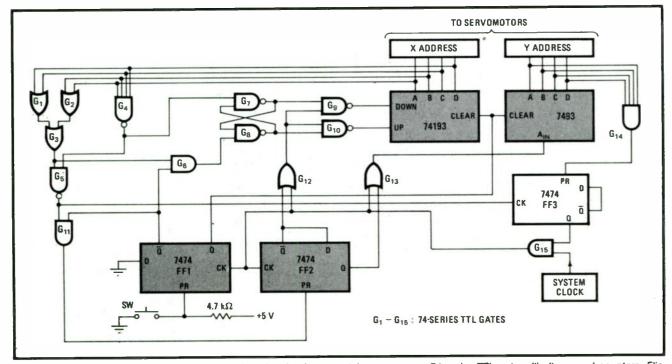

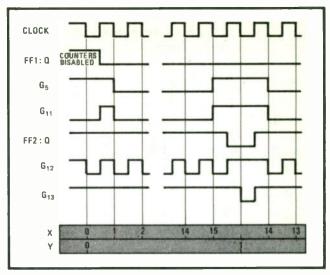

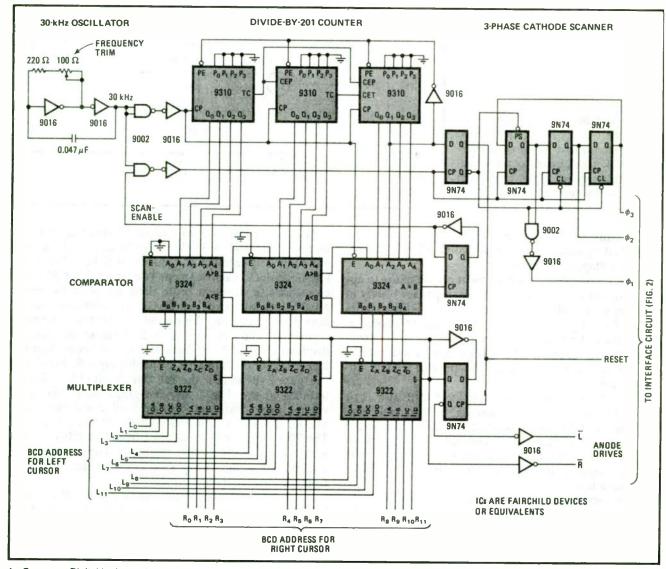

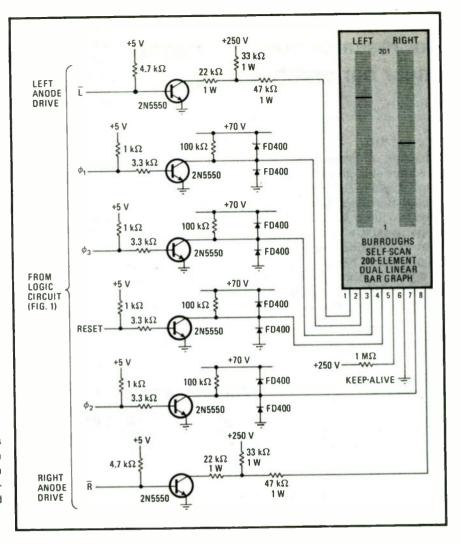

- 50. Back-and-forth scanner overcomes slewing-rate limits

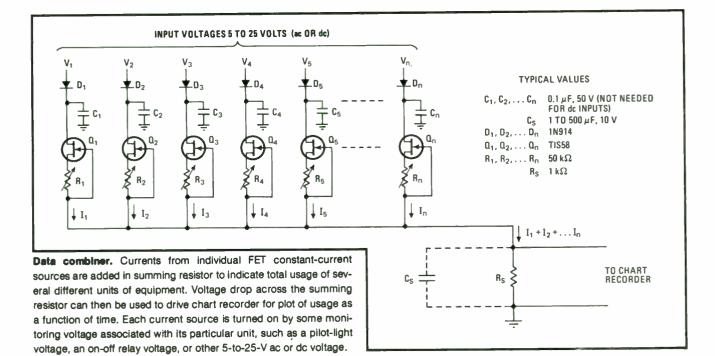

- 51. Chart recorder plots total of loads in several circuits

- 53. Addressable cursor enhances linear bar-graph display

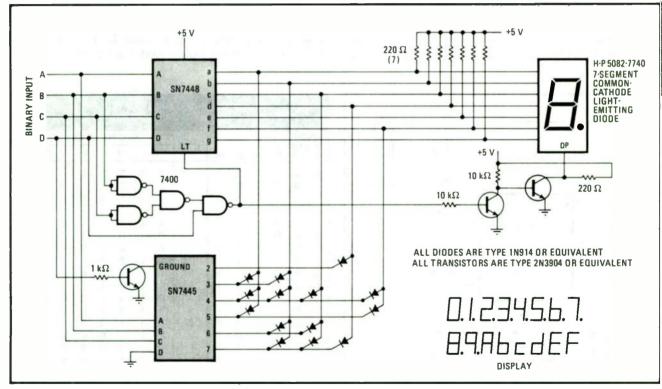

- 55. Decoders convert binary code for hexadecimal display

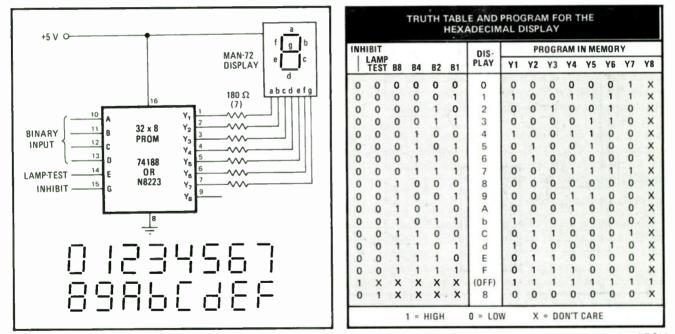

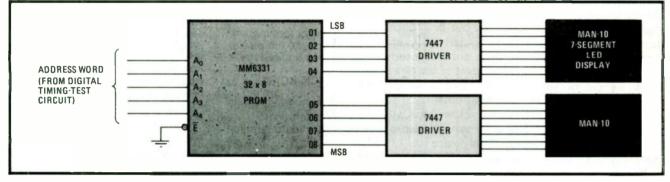

- 56. PROM converts binary code for hexadecimal display

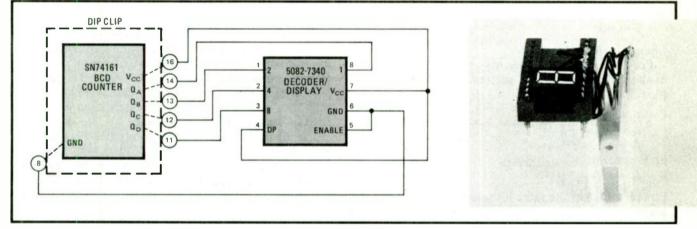

- 57. Clip-on monitor unit displays count in IC

#### 8. Graphical aids to design

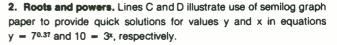

- 58. Semilog paper is short cut to finding filter frequencies

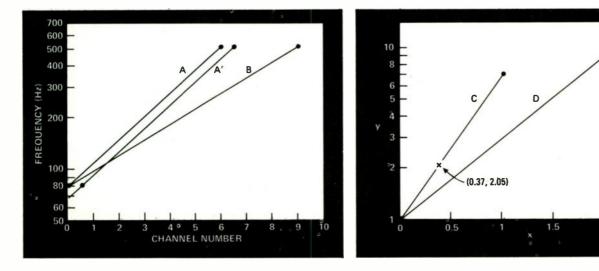

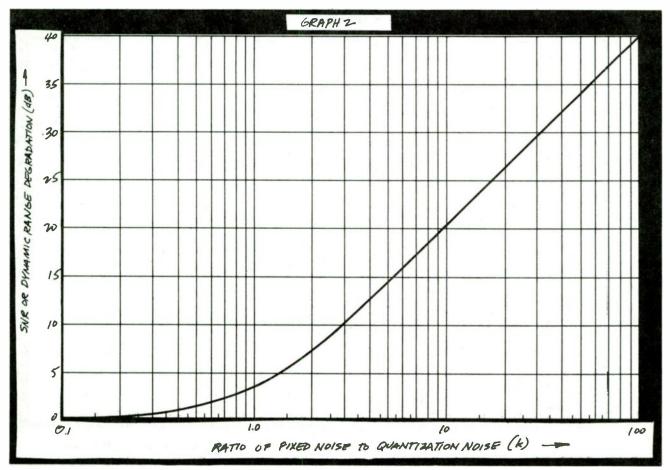

- 59. Graphs aid selection of a-d converters

- 61. Convert coordinates and find SWRs graphically

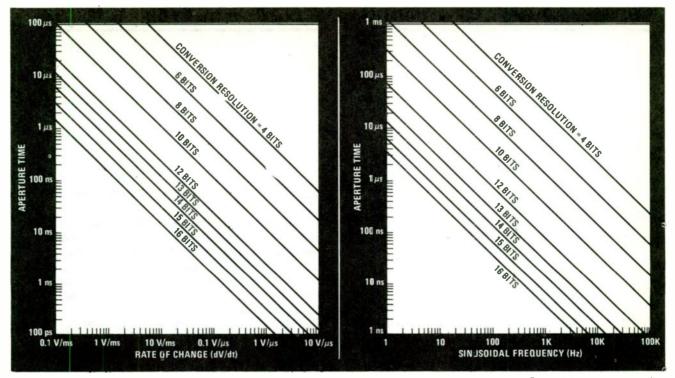

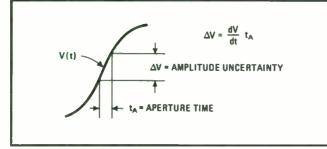

- 62. Graphs give aperture time required for a-d conversion

#### 9. Tabular aids to design

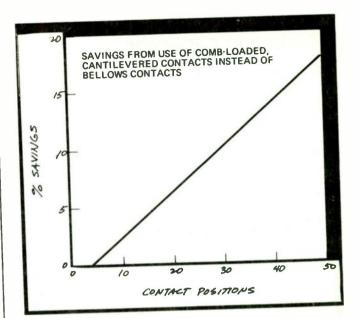

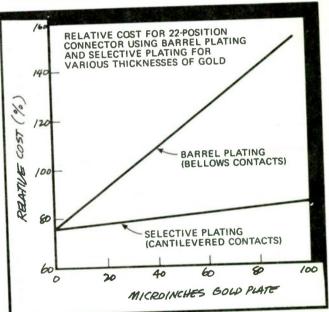

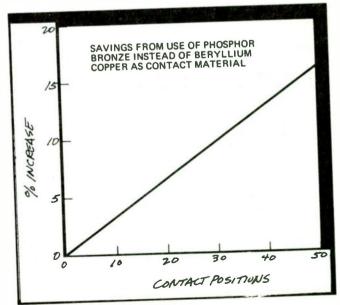

- 64. Charts calculate tradeoffs in pc edge connector costs

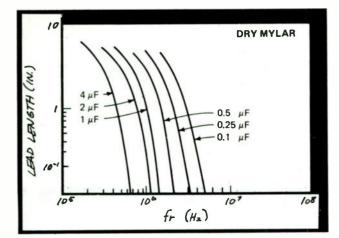

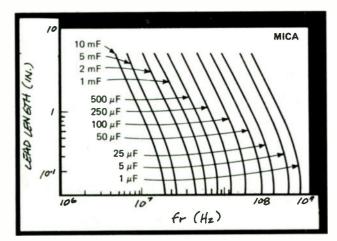

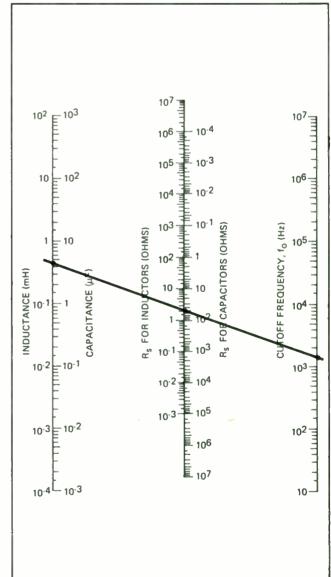

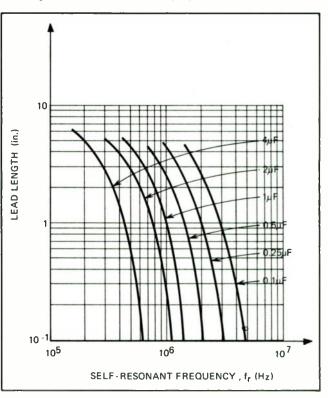

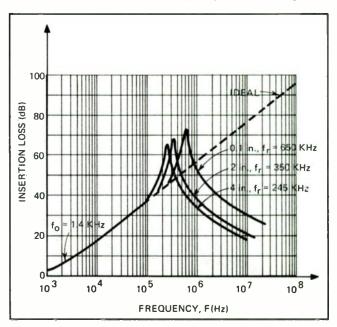

- 66. Charts find capacitor self-resonant frequency

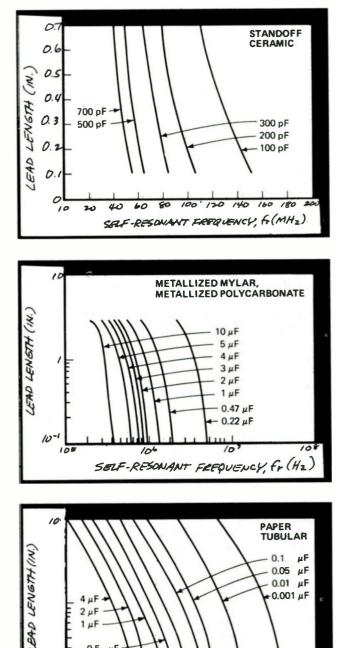

- 67. Equation table speeds design of symmetrical pi attenuators

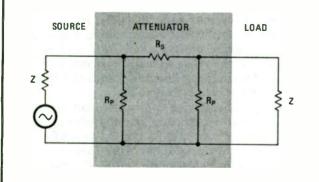

- 68. Comparing coaxial cable shielding effectiveness

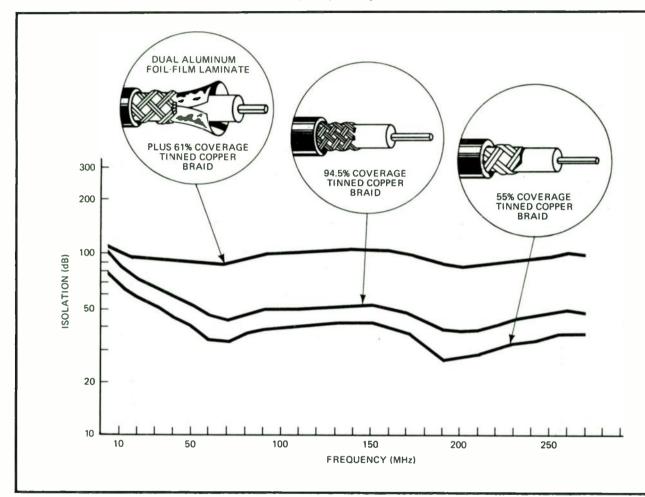

#### 10. Nomograph aids to design

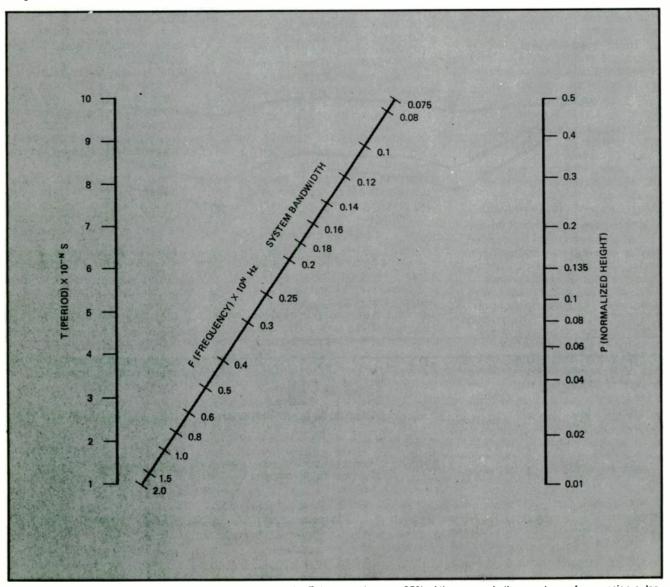

- 70. Nomograph shows bandwidth for specified pulse shape

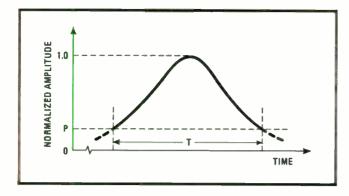

- 71. A quick solution to conductive heat transfer problems

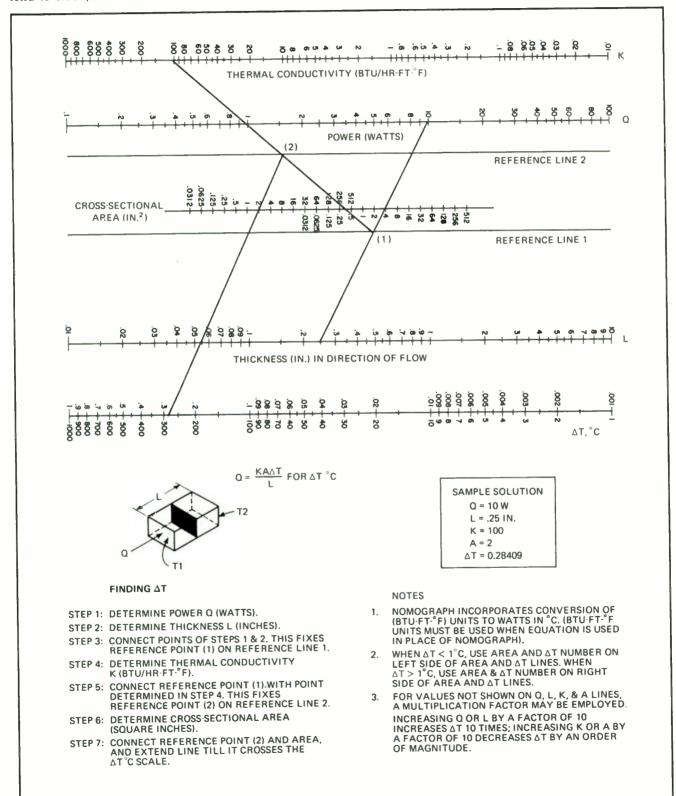

- 73. Graphic aids simplify low-pass filter design

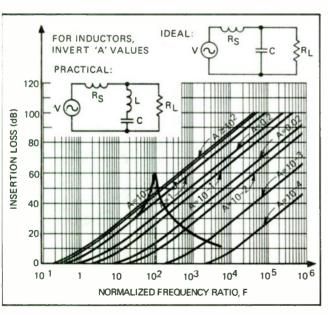

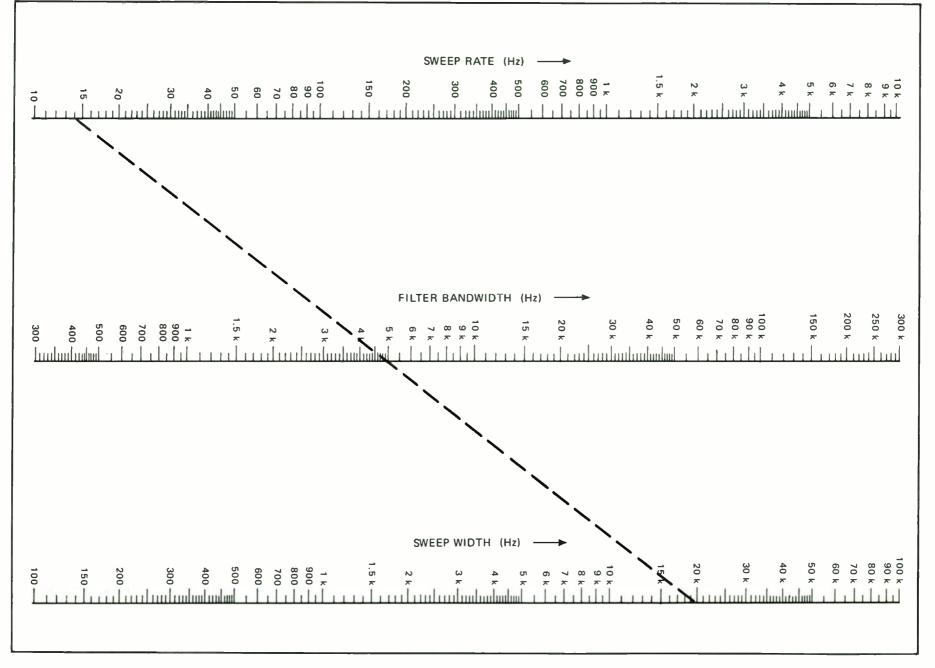

- 75. Filter bandwidth nomograph gives sweep-rate limits

#### 11. Quick calculation of circuit elements

- 78. Quick calculation gives filter-capacitor value

- 79. Power rating calculations for variable resistors

- 80. Calculating resistance for sum and difference networks

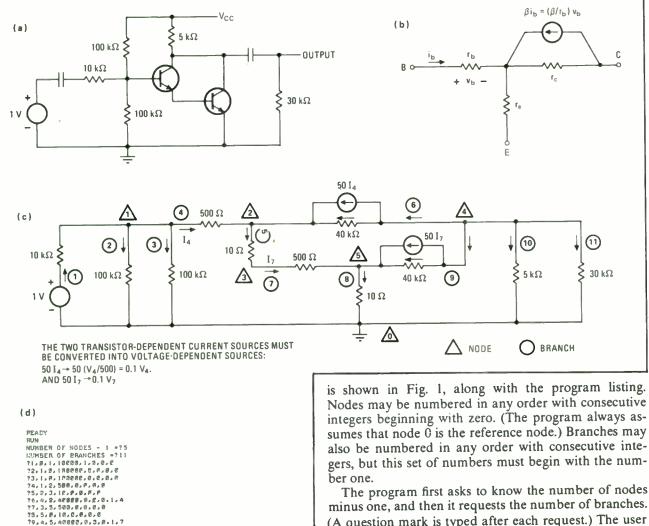

#### 12. Calculator-aided designs

- 82. Programable calculator performs spur analysis

- 83. Programable calculator analyzes filter designs

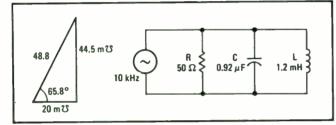

- 85. Short program computes response of RLC networks

- 87. Program analyzes all-resistive dc circuits

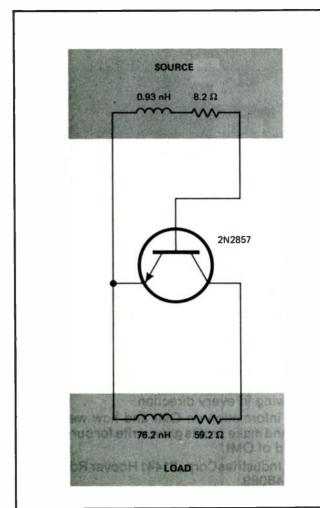

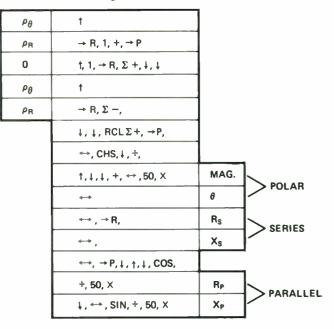

- 89. HP-45 calculator speeds rf amplifier design

#### 13. Circuit aids to calculation

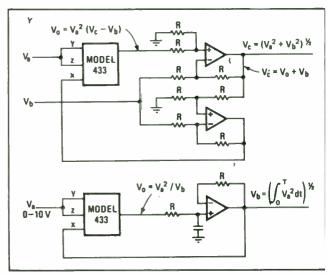

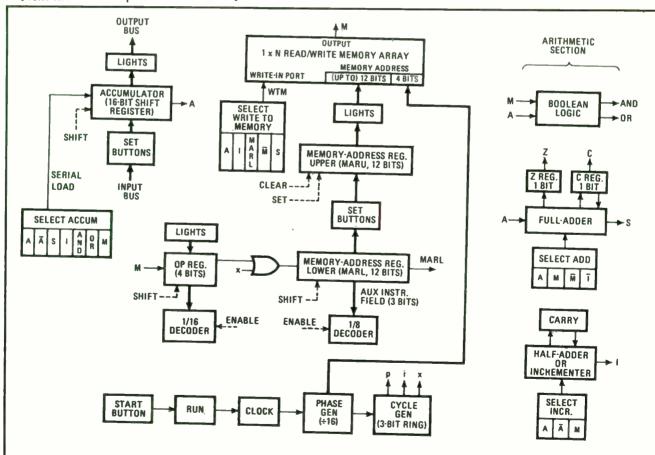

- 91. Computational module stresses applications versatility

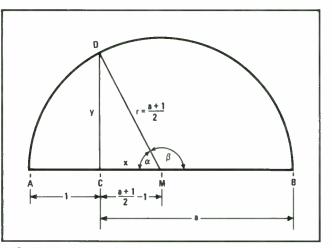

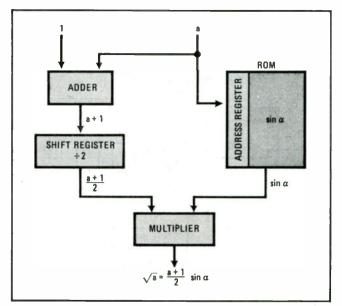

- 92. ROM-stored sine functions yield square roots

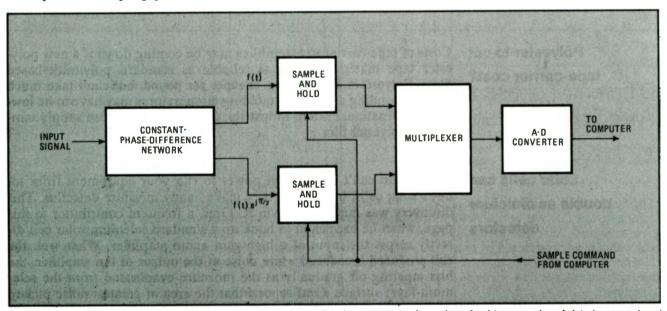

- 93. Differential phase shifter speeds calculation of FFT

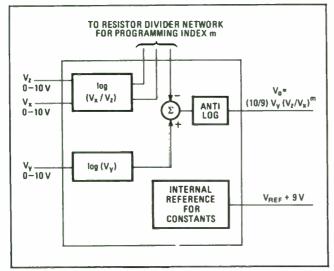

- 95. Module converts voltage to inverse square

#### **14. Trouble detectors**

- 97. Self-powered comparator warns when signal exceeds limits

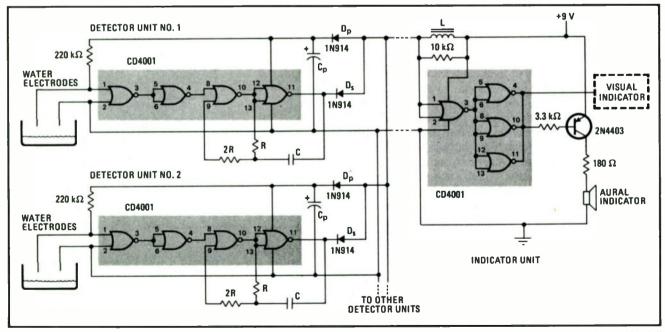

- 98. Multiplexed detectors isolate water leaks

- 99. Flashing lamp reminds you to turn off equipment

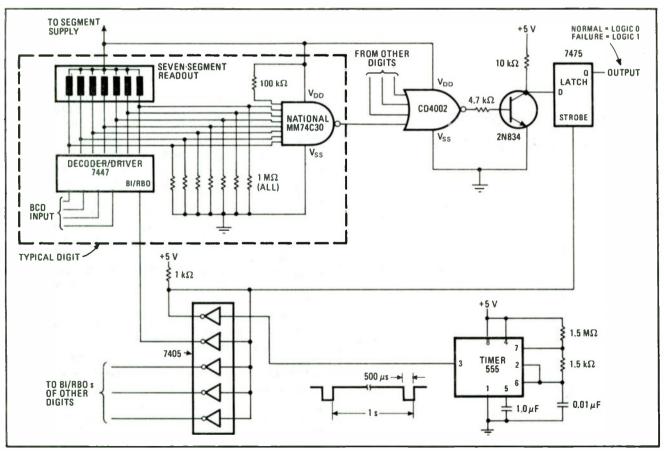

- 100. Continuous monitor for seven-segment displays

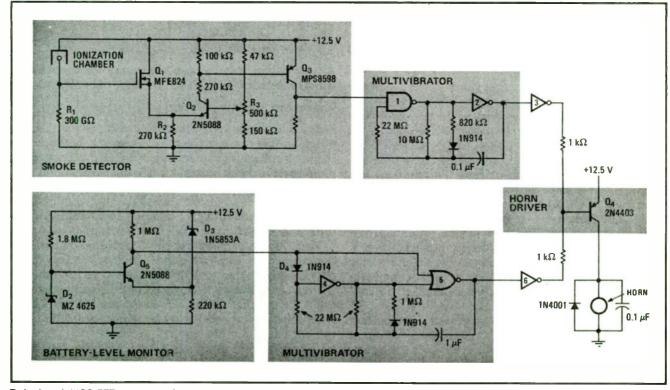

- 101. Gas and smoke detector uses low-leakage MOS transistor

#### 15. Five noise beaters

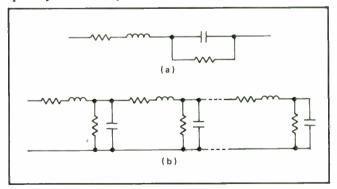

- 103. Choosing the best suppression network for your SCR converter

- 104. Ten ways to reduce noise pickup in ICs.

- 105. Eliminating stray signals in remotely gain-switched op amps

- 107. Circuit layouts minimize noise in digital systems

- 109. Coaxial buses help suppress power supply transients

#### 16. Easy amplifier circuitry

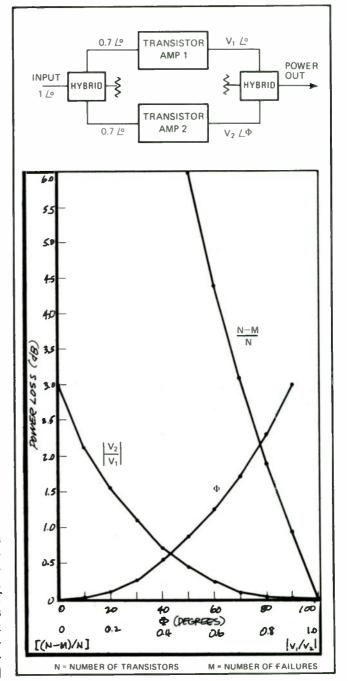

- 110. Charting power losses for hybrid-combined amplifiers

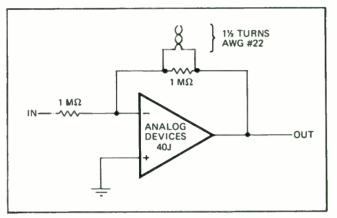

- 111. Capacitance of twisted wire trims fast FET op amps

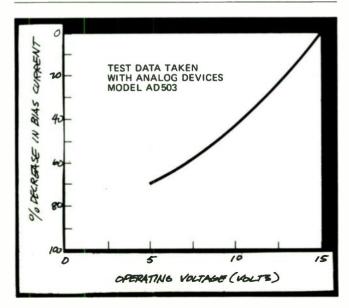

- 111. Reducing IC FET op amp input bias currents

- 112. Choosing MOSFET bias for minimum temperature drift

#### 17. Novel use of timers

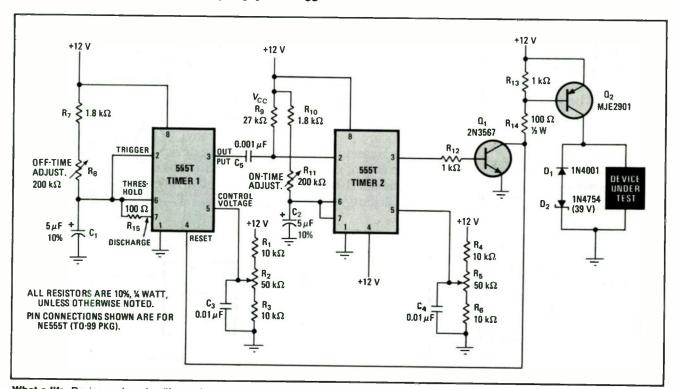

- 113. Timer ICs control life-test cycling

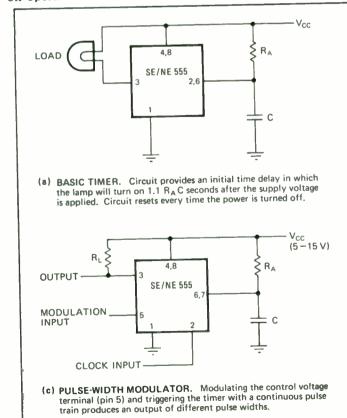

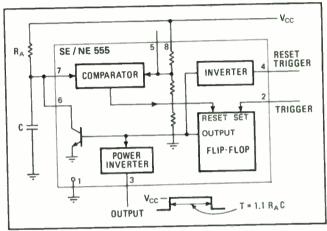

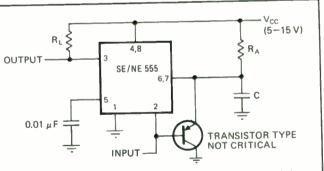

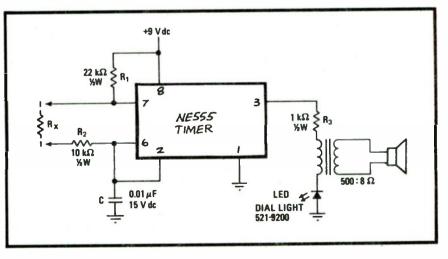

- 114. Low-cost IC timer handles a lot of jobs

- 115. IC timer's duty cycle can stretch over 99%

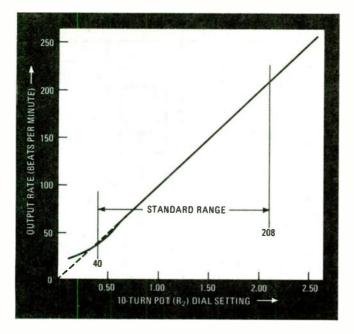

- 116. All-electronic metronome provides accurate beat rate

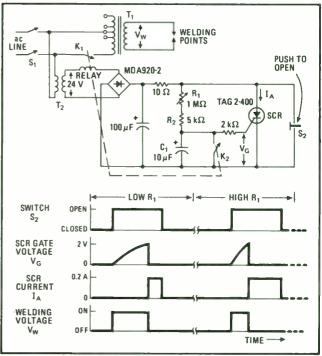

- 117. Electronic timer circuit improves welder performance

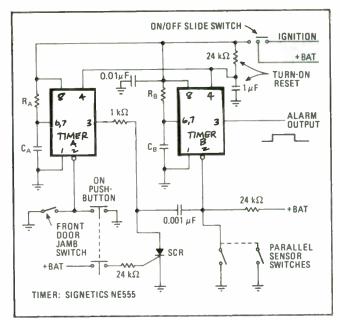

- 118. Pair of IC timers sounds auto burglar alarm

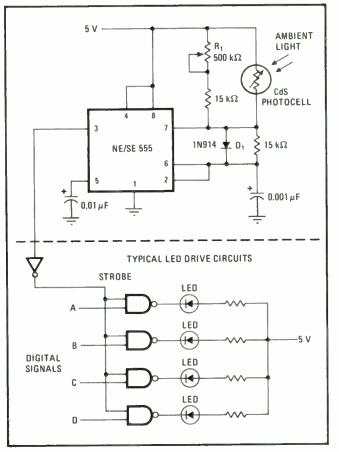

- 118. Timer IC and photocell can vary LED brightness

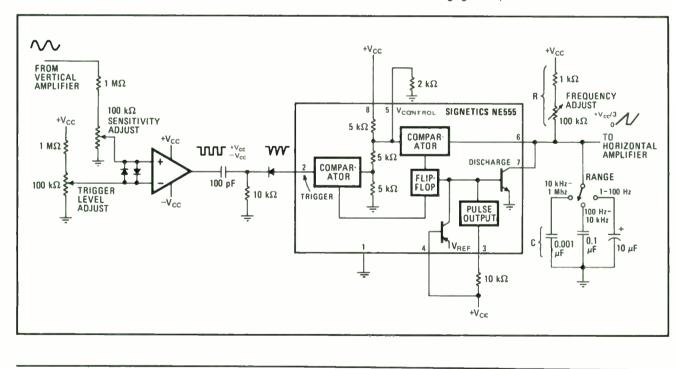

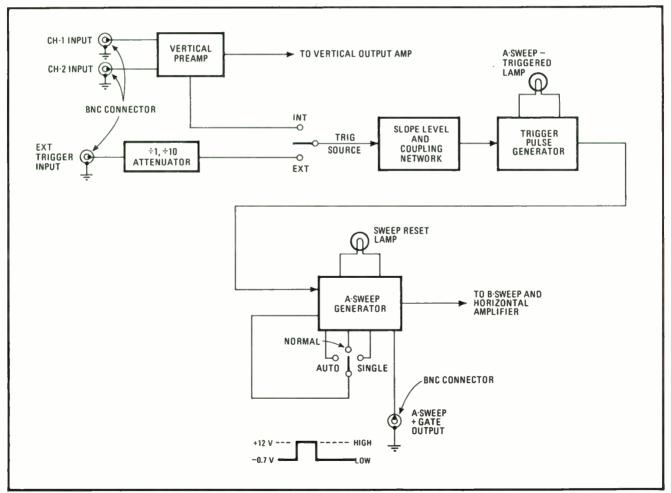

- 119. Oscilloscope triggered sweep; another job for IC timer

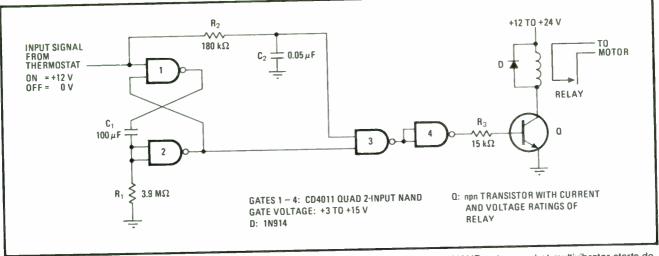

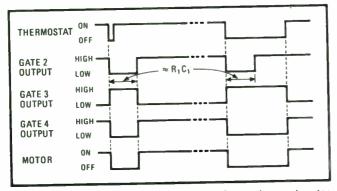

- 119. Adaptive motor starter delays when necessary

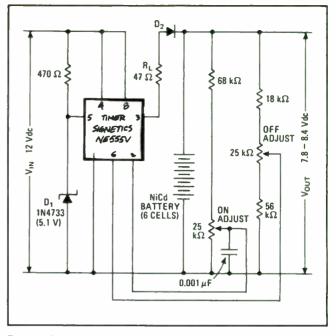

- 121. IC timer automatically monitors battery voltage

- 121. IC timer drives electric fuel pump

#### 18. Special timing circuits

- 122. Multiplying scheme offers alternative to count-down timers

- 123. Building timing circuits for noisy environments

### **19. Techniques of coding, modulation, and detection**

- 125. Design chart identifies intermodulation products

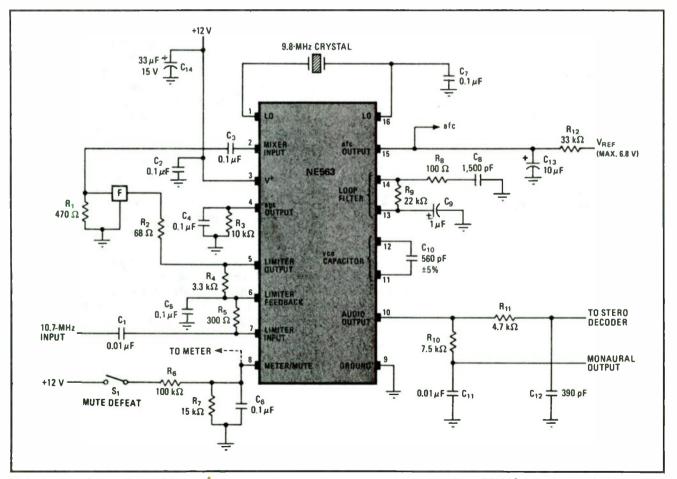

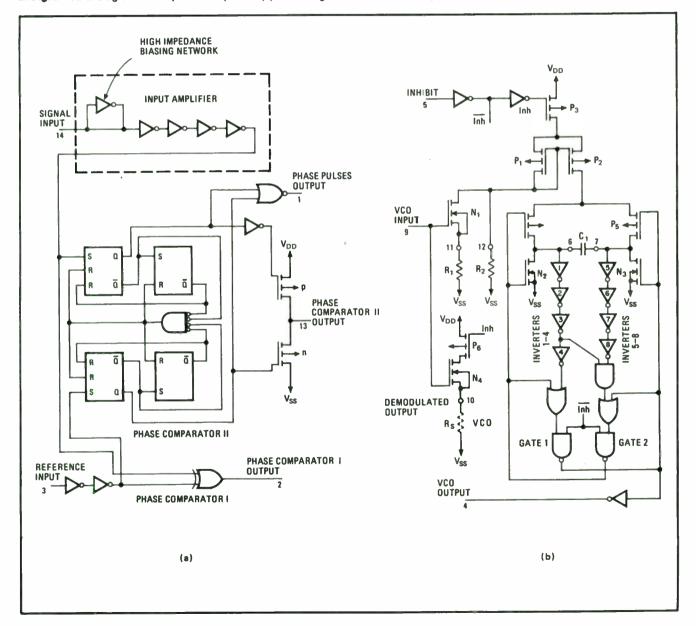

- 127. One-chip fm demodulator needs no alignment

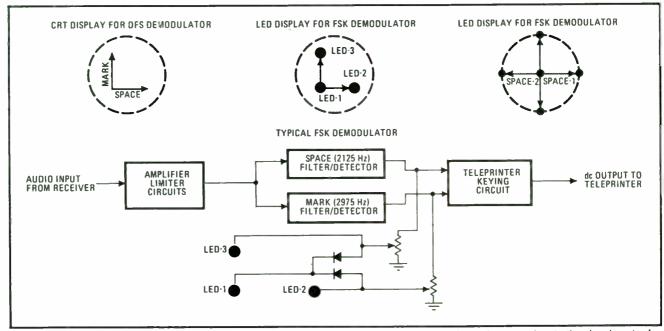

- 129. LEDs help tune FSK demodulators

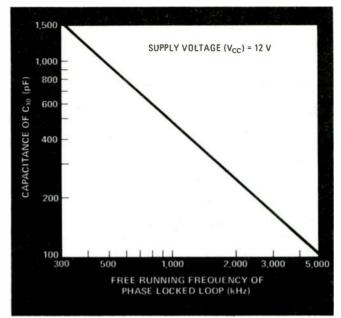

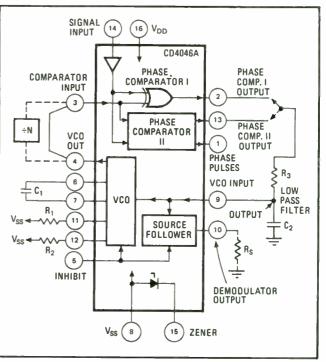

- 130. Micro-power phase-locked loop widens designer's choice

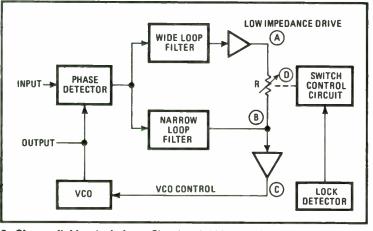

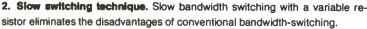

- 132. Dual-bandwidth loop speeds phase lock

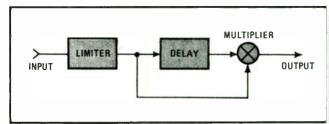

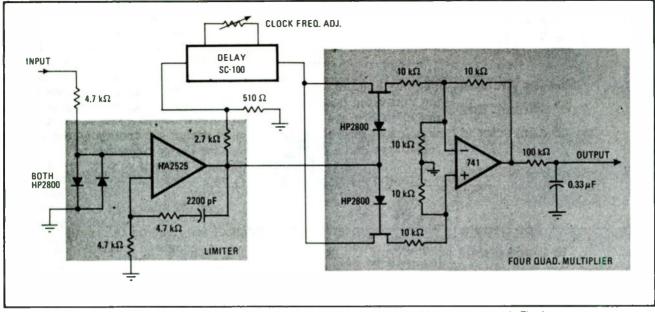

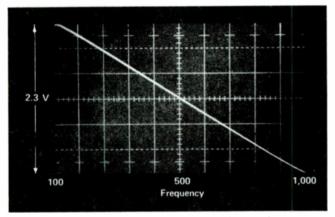

- 133. Low-frequency discriminator utilizes analog delay

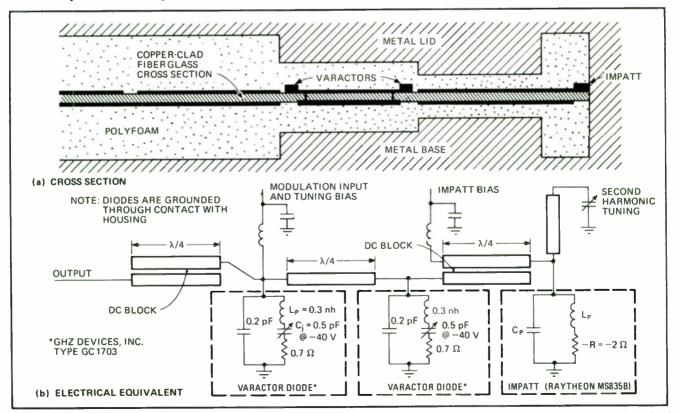

- 135. Varactor pair in new stripline circuit improves modulation

- 136. Data transmission is faster with ternary coding

#### 20. Converting between analog and digital

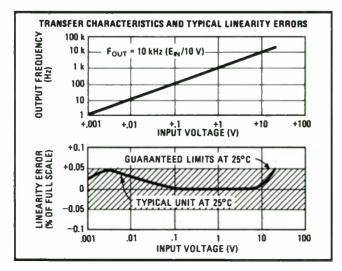

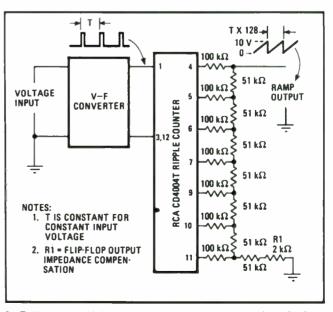

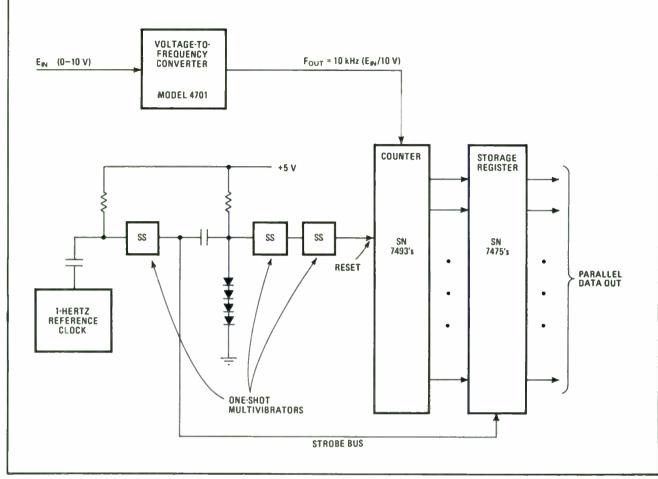

- 138. Voltage-to-frequency module serves diverse applications

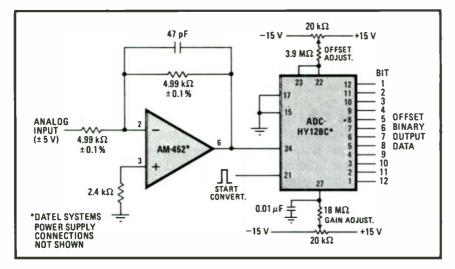

- 139. Op amp complements a-d converter output code

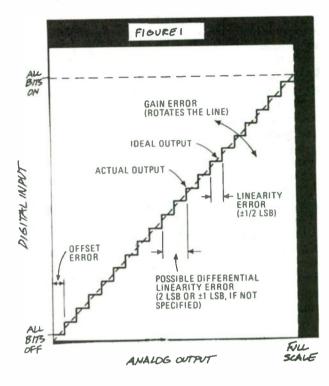

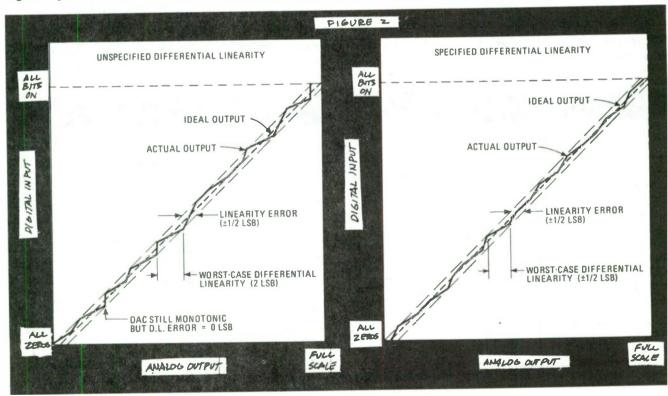

- 141. DAC differential linearity: it makes a difference

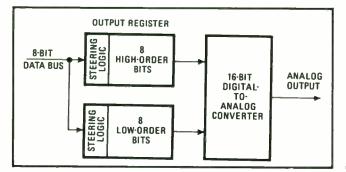

- 142. Economical approaches to 16-bit d-a conversion

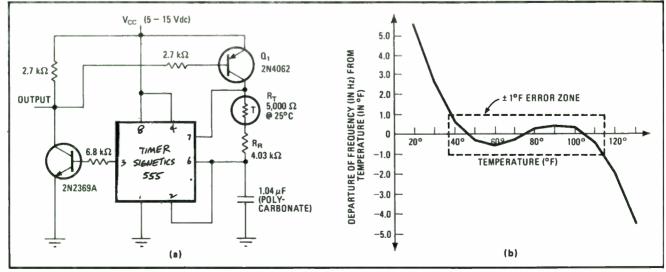

- 143. IC timer converts temperature to frequency

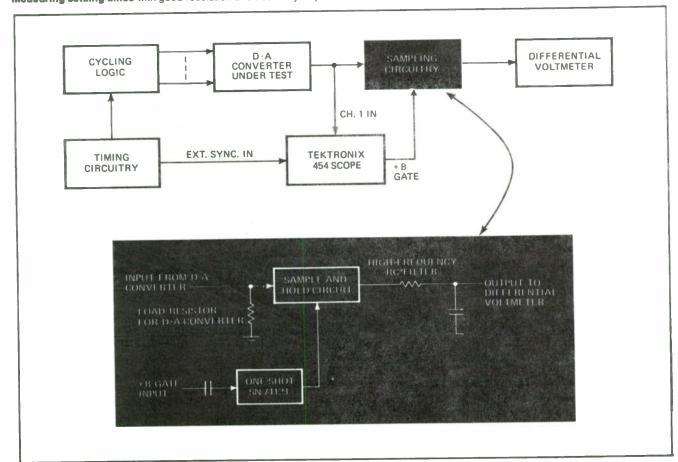

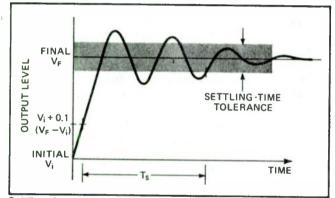

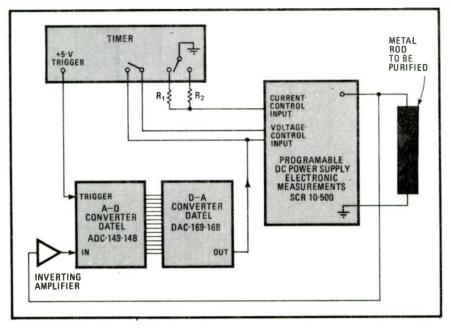

- 144. Time-delay sampling simplifies settling-time measurements

- 146. Precision sample-and-hold stores voltage for a week

#### 21. Remembering and recording

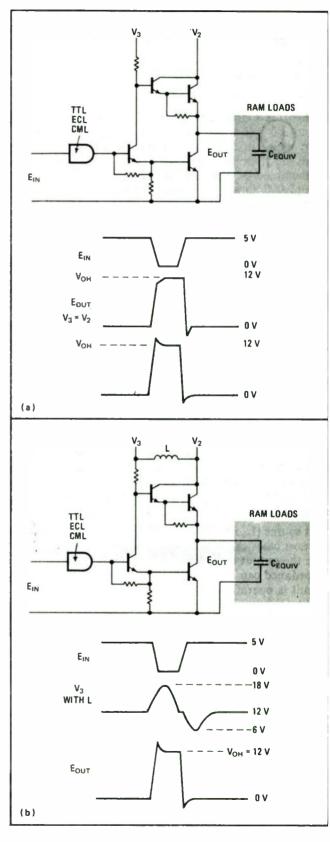

- 147. Inductor simplifies memory-driver circuit

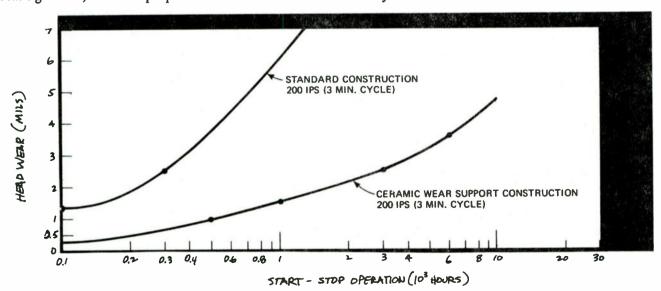

- 148. Extending the life of digital recording heads

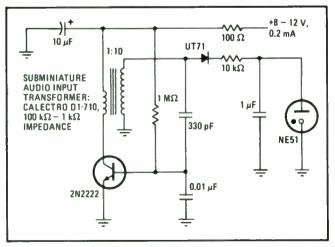

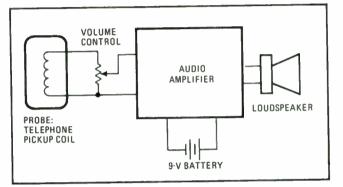

- 150. Listening to magnetic fields can be useful, as well as fun

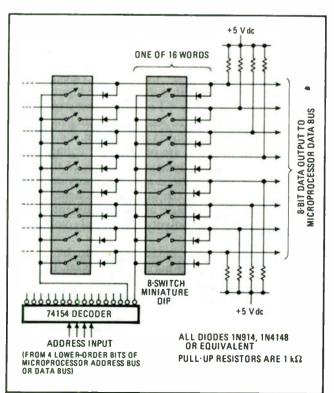

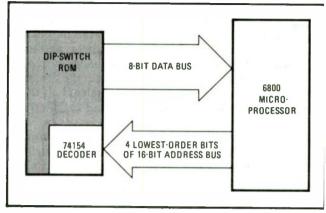

- 151. DIP switches and diodes form programable ROM

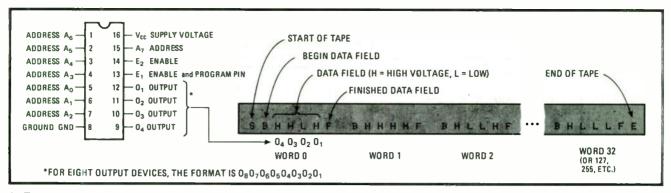

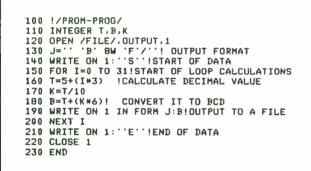

- 152. Computer program reduces fusible-PROM errors

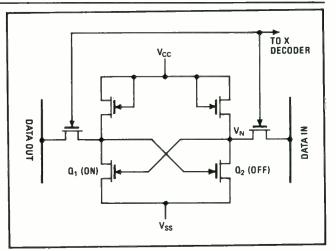

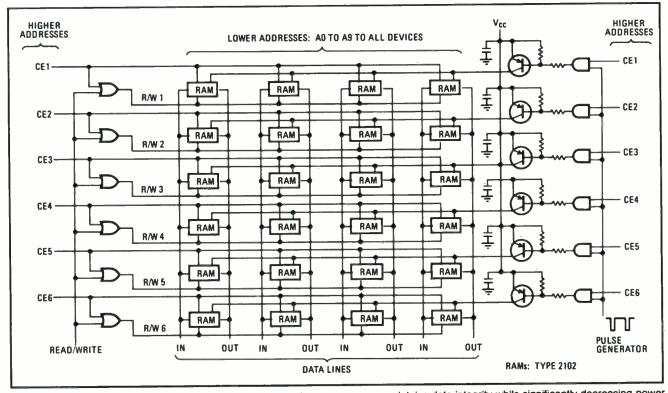

- 154. Reducing the power drain of semiconductor static RAMs

#### 22. Generating wave shapes to order

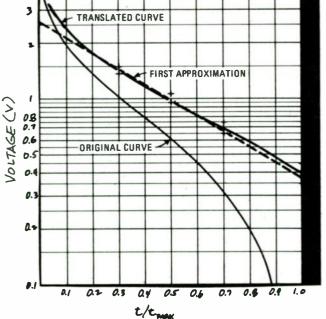

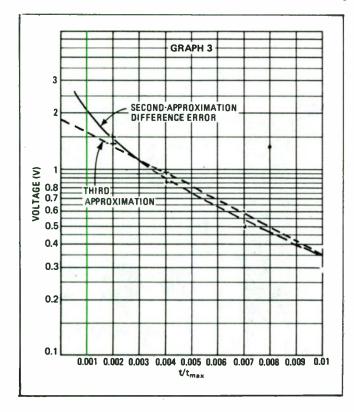

- 156. Approximating waveforms with exponential functions

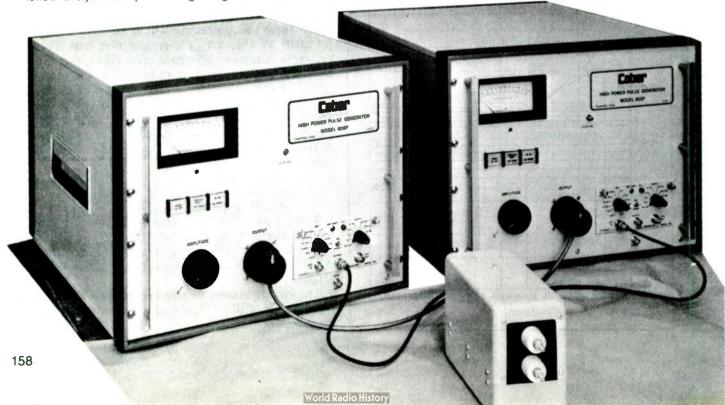

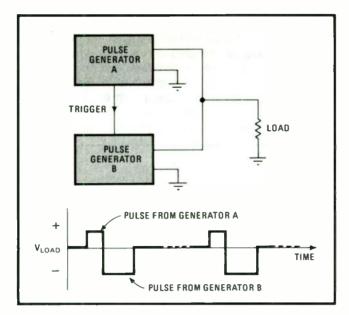

- 158. Two tandem pulse generators provide waveform flexibility

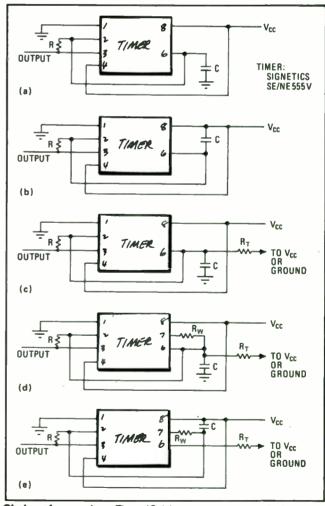

- 159. IC timer plus resistor can produce square waves

- 160. Simple step-function generator aids in testing instruments

- 161. Jitter generator tests bit synchronizer

- 163. Waveform generator chips help the circuit designer

#### 23. Logiic techniques

- 165. DIPs verify strobe within time window

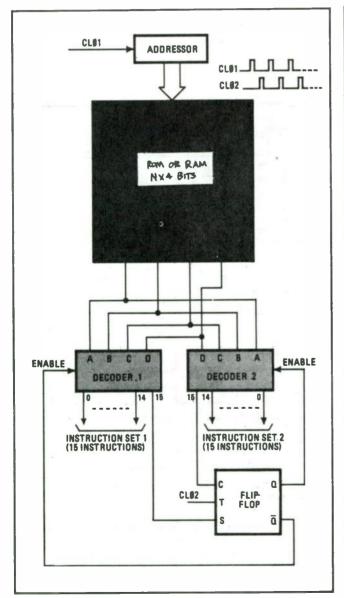

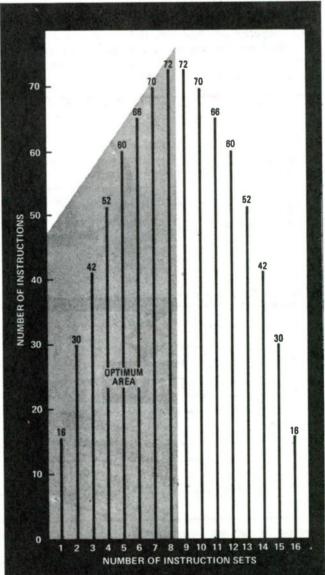

- 166. Increasing an instruction set without increasing word length

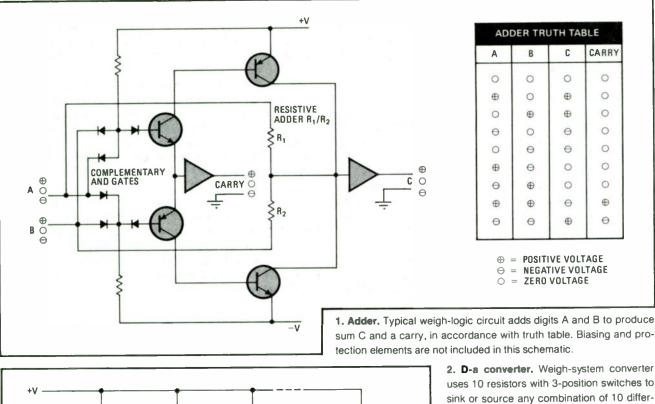

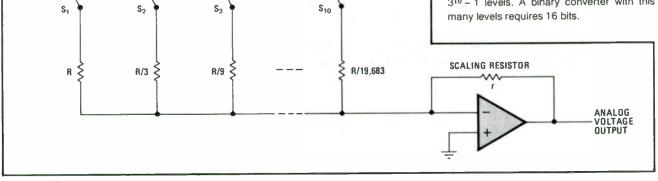

- 167. Weigh-counting technique is faster than binary

- 169. Capacitance-coupled logic fills unusual jobs

- 170. One's complement adder eliminates unwanted zero

- 172. Nonsequential counter design makes use of Karnaugh maps

- 174. New ECL-compatible logic uses less power from a single supply

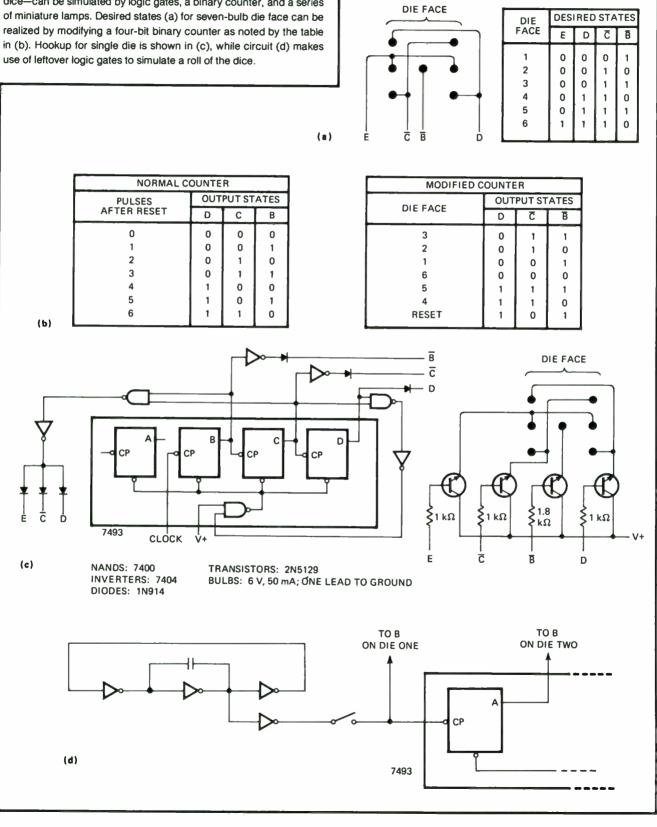

- 175. Electronic dice ease tough decisions

#### 24. Interfacing to logic circuits

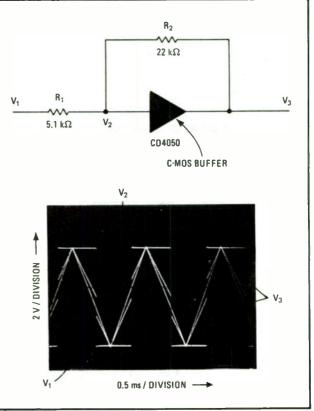

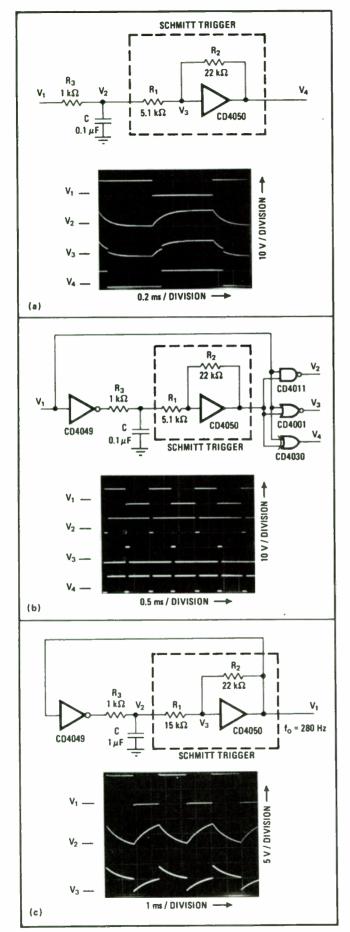

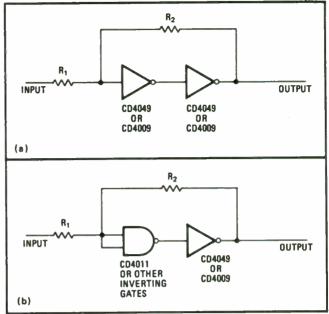

- 177. C-MOS Schmitt trigger can be more than an interface

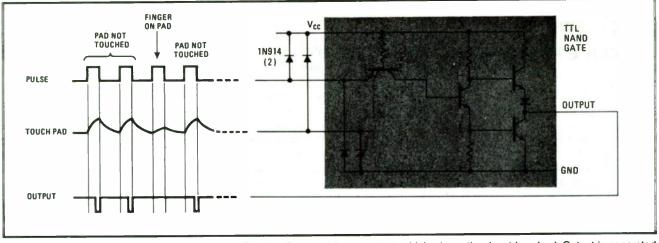

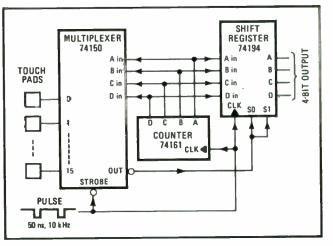

- 179. Touch switch enters data without extra components

- 179. TTL IC serves as touch keyboard

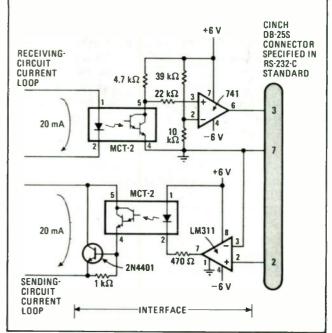

- 181. Opto-isolators couple CRT terminals to printer lines

- 181. IC timer can function as low-cost line receiver

- 182. Pocket calculator converts to keyboard entry station

#### 25. A clutch of logic probes

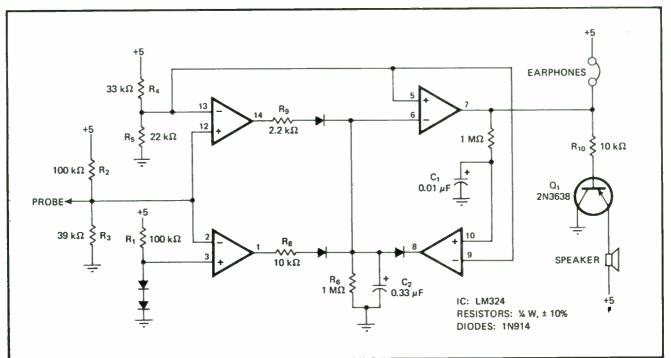

- 184. Low-priced logic probe indicates levels with tones

- 185. TTL level tester identifies logic levels by audible tone

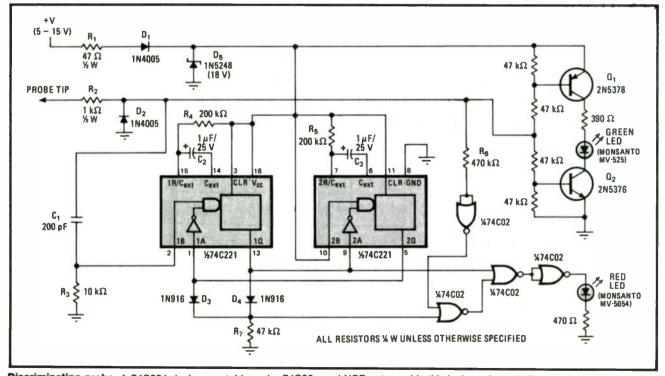

- 186. Versatile logic probe displays four modes

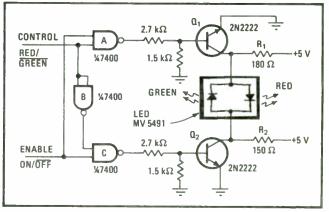

- 187. Two-color LED pair is digital status indicator

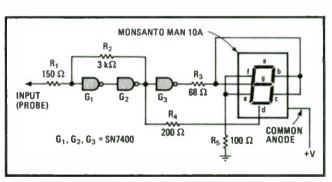

- 187. Adding numeric readout to logic probe displays

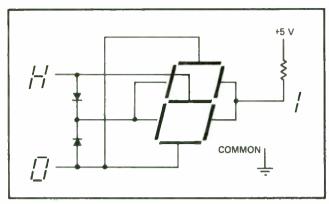

- 188. TTL logic tester displays H or L

#### 26. Offbeat measurement techniques

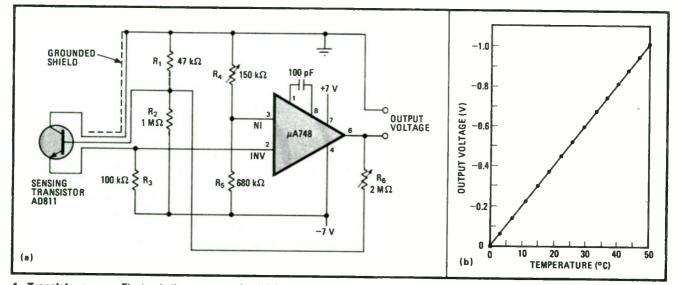

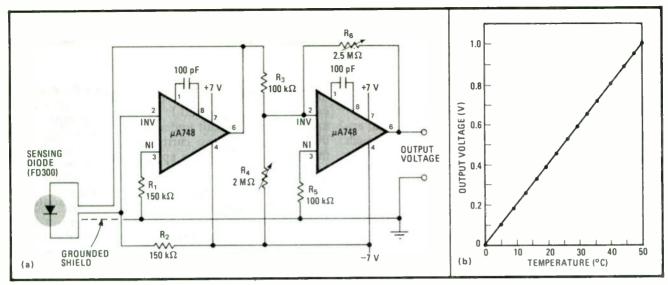

- 189. Diode or transistor makes fully linear thermometer

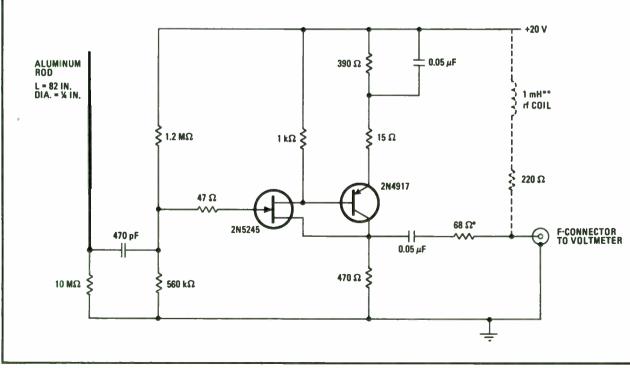

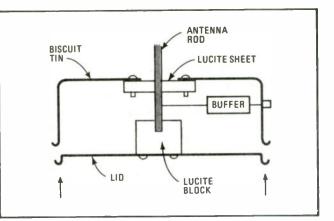

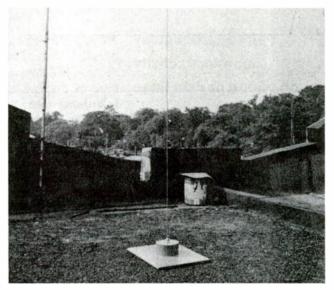

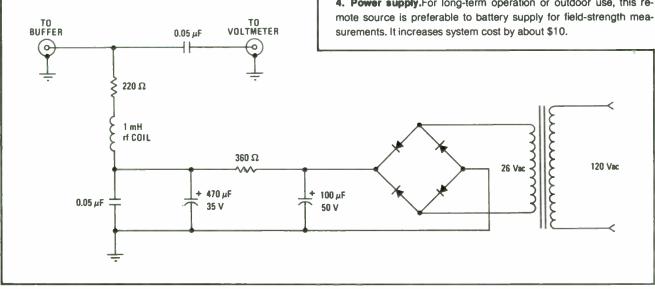

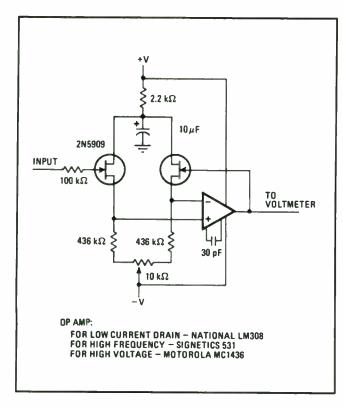

- 191. Low-cost field-strength unit uses simple buffer

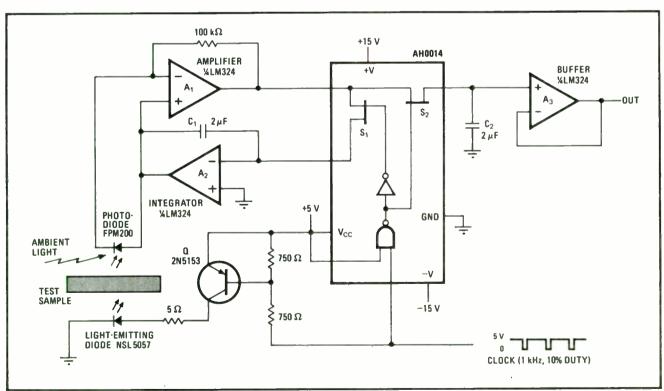

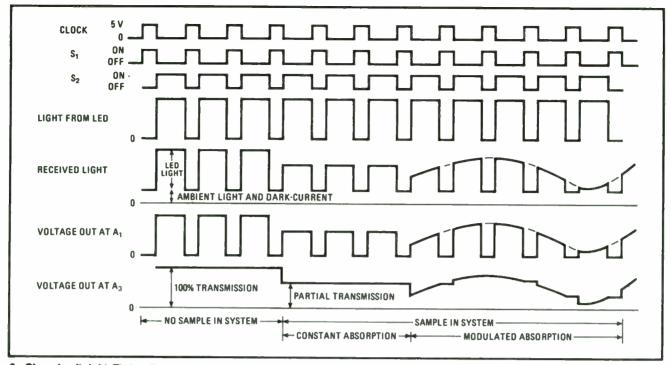

- 193. Low-cost optical sensor overcomes ambient light

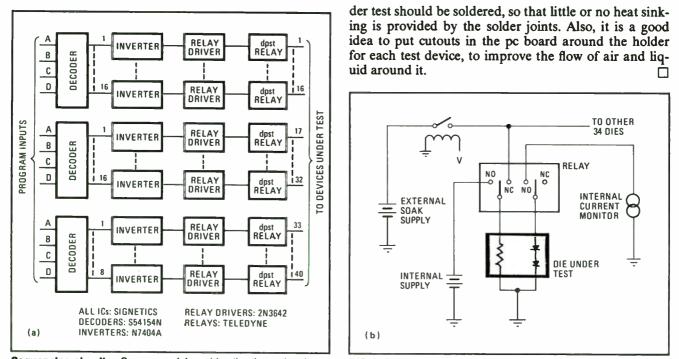

- 195. Automatic test setup checks thermal resistance

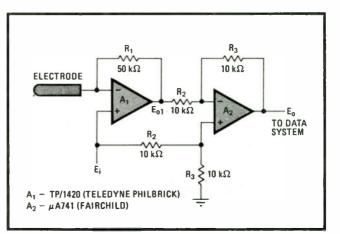

- 196. Op amp improves plasma probe's sensitivity

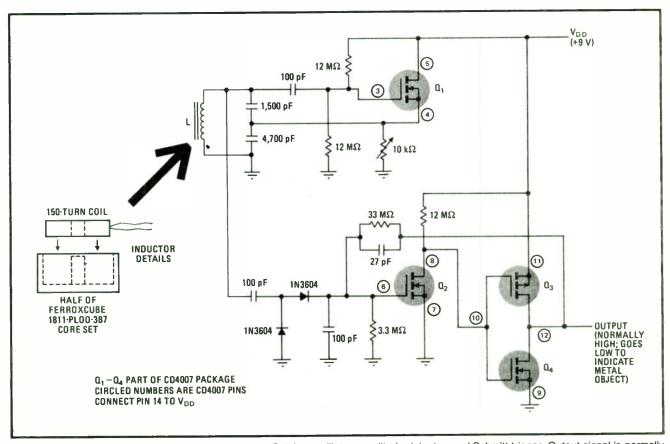

- 197. Inductive proximity detector uses little power

#### 27. Novel measurements with a scope

- 198. Scope detects narrow pulses with its triggering system

- 199. Picking the right film for better oscilloscope pictures

- 201. Oscilloscope probes can do many jobs

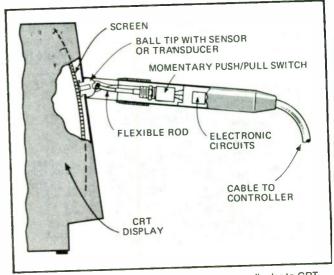

- 201. Self-orienting probe tip eases light pen use with CRTs

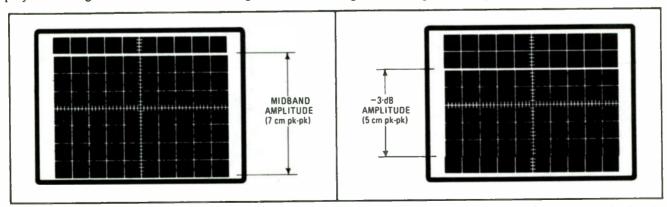

- 202. Scope-face graticule highlights 3-dB signal points

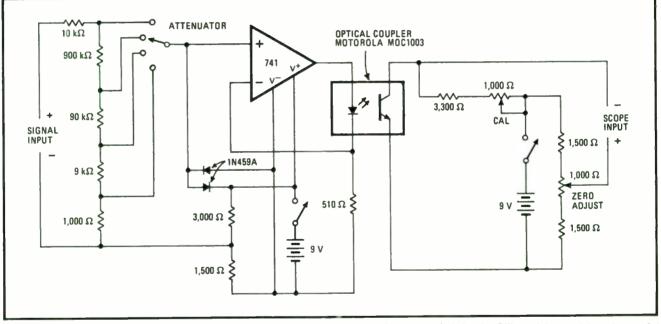

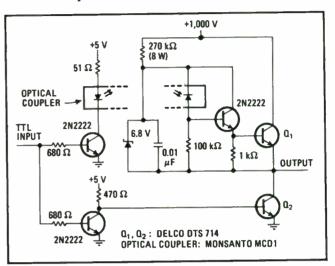

- 203. Isolator circuit permits scope to check ungrounded voltages

#### 28. R, L, and C measurements made easy

- 204. Using a frequency counter to measure capacitance

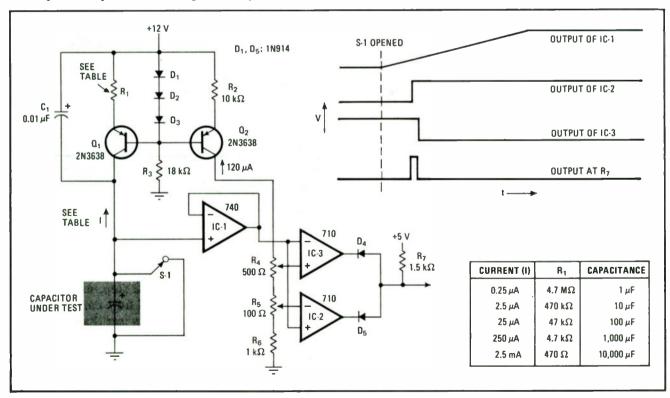

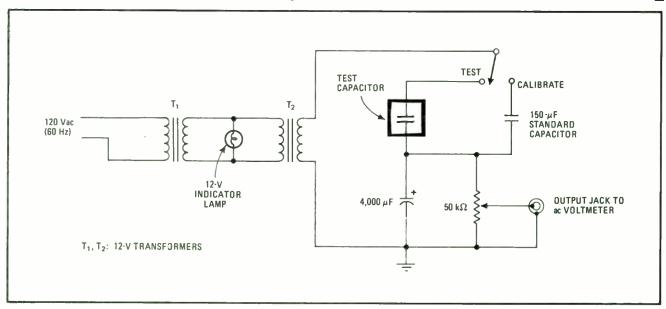

- 205. Test circuit enables voltmeter to check electrolytic capacitors

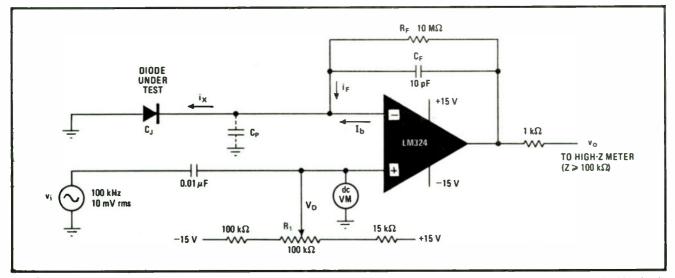

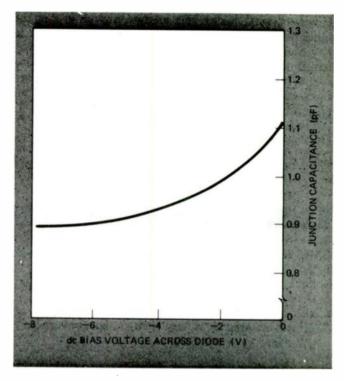

- 206. Op-amp circuit measures diode-junction capacitance

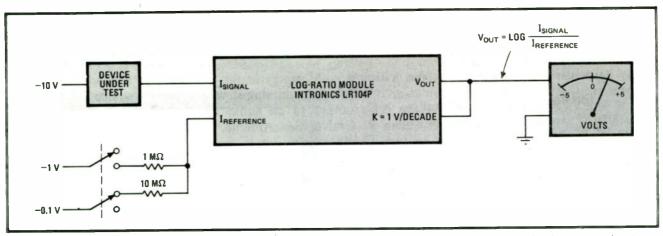

- 207. Log-ratio module measures high resistances

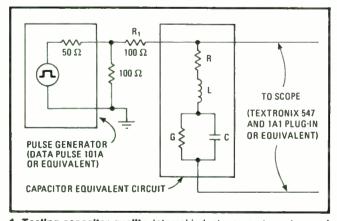

- 209. Single time measurement determines capacitor R and L

- 210. Simple a-d converter circuit measures resistance digitally

- 212. Audio continuity tester indicates resistance values

- 213. Measuring inductances below 100 nanohenries

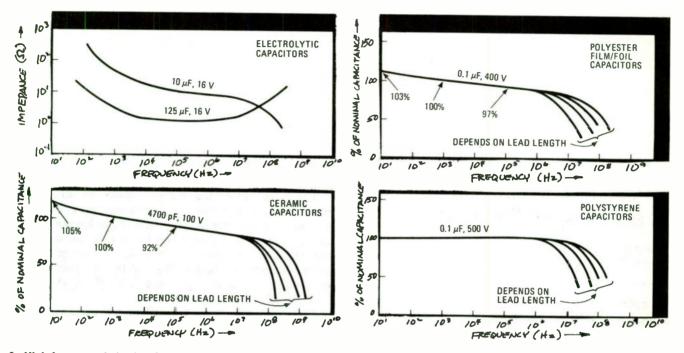

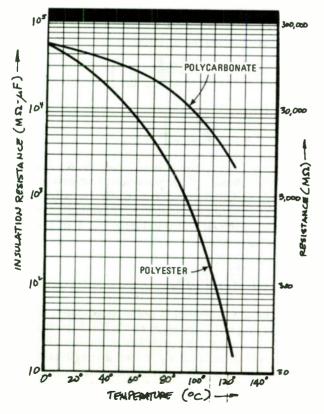

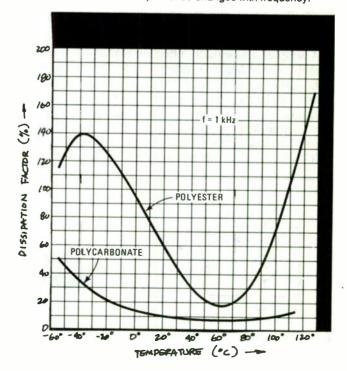

- 214. Charting capacitor frequency and temperature performance

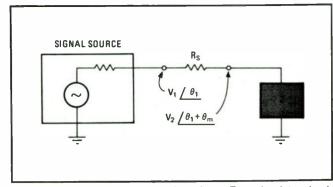

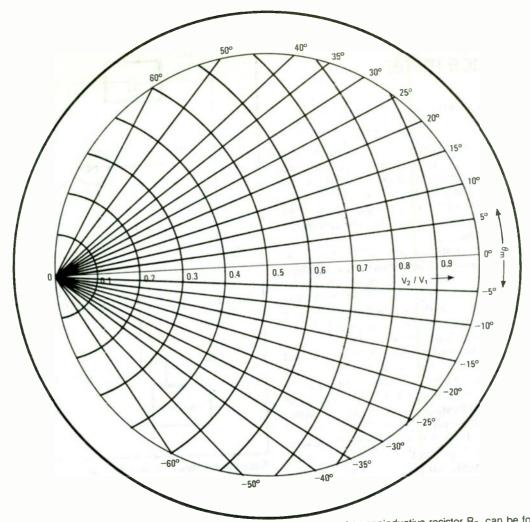

- 216. Measuring complex impedances at actual operating levels

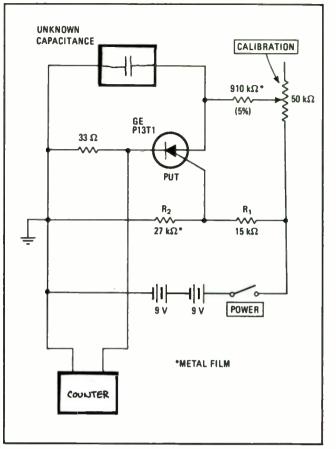

- 218. Oscillator converts counter to capacitance meter

- 219. Direct-reading ohmmeter needs no calibration

#### 29. Finding active-device characteristics

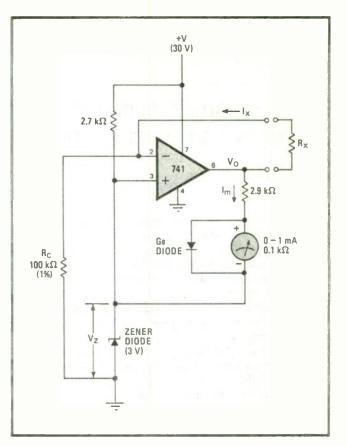

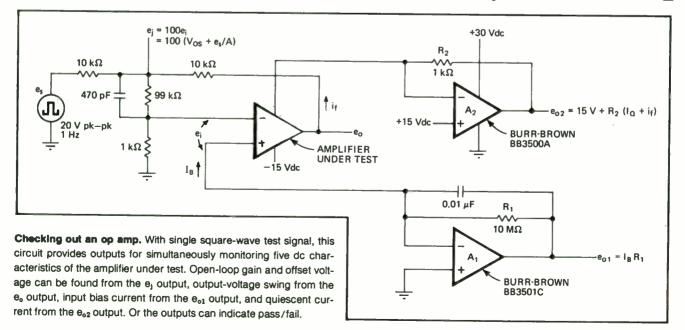

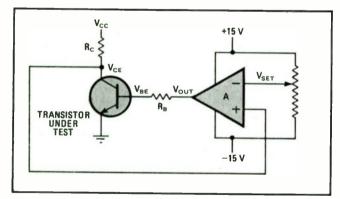

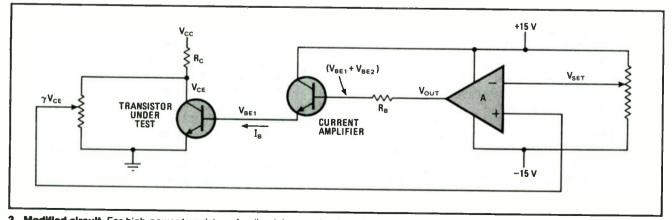

- 220. Single op-amp test circuit makes five dc checks at once

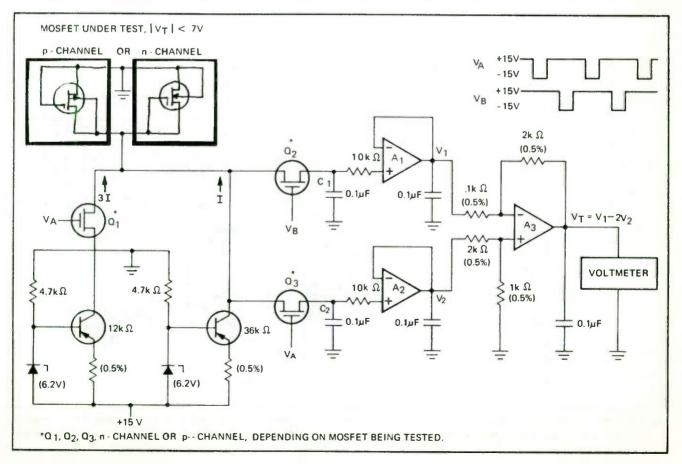

- 221. Finding MOSFET threshold with one measurement

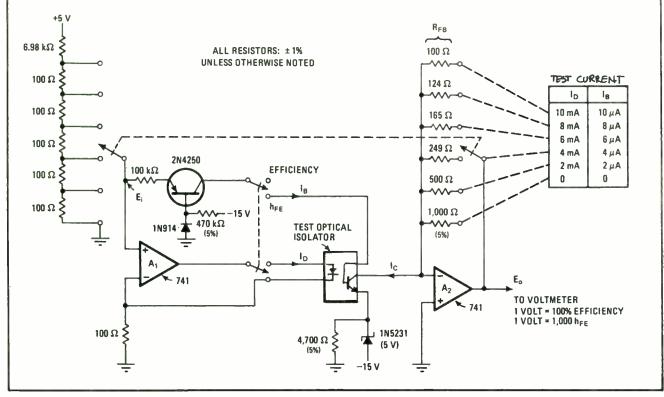

- 222. Test circuit checks optical isolators

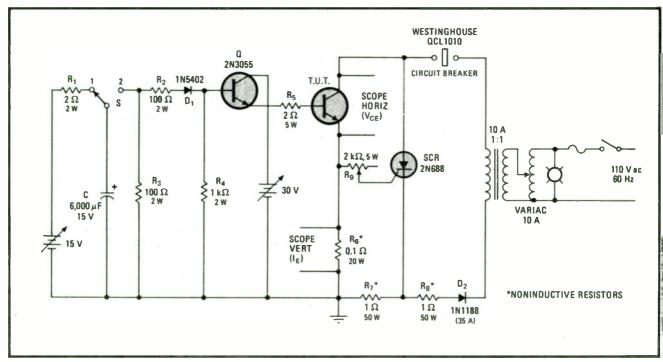

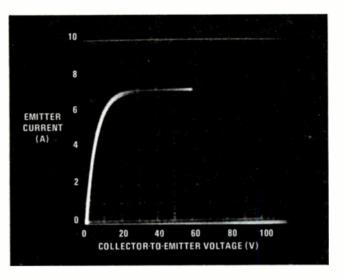

- 223. Pulsed transistor test simulates linear operation

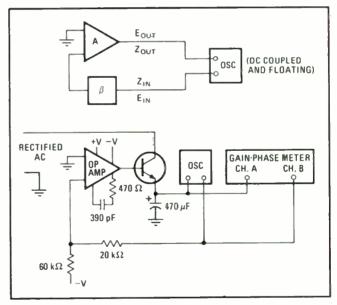

- 224. Finding open-loop gain without opening the loop

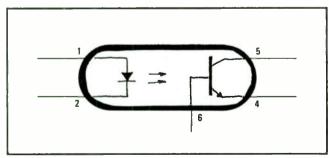

- 225. Curve tracer can check optoisolator performance

- 226. A simple way of measuring high-frequency transistor gain

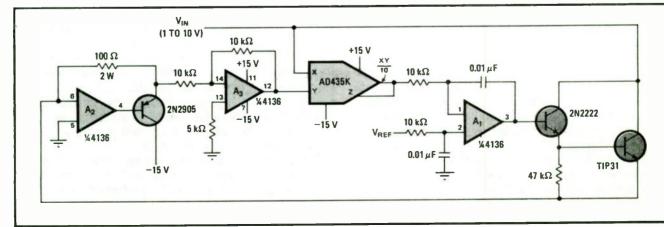

- 228. Feedback circuit measures beta at constant power dissipation

- 229. Adjustable active load maintains constant dc power dissipation

- 230. ROMs in microprocessors can test themselves

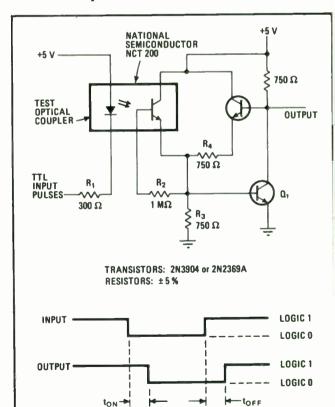

- 231. Test circuit measures optical coupler's speed

- 232. Multimeter measurements yield device-model parameters

#### 30. Fm and phase measurements

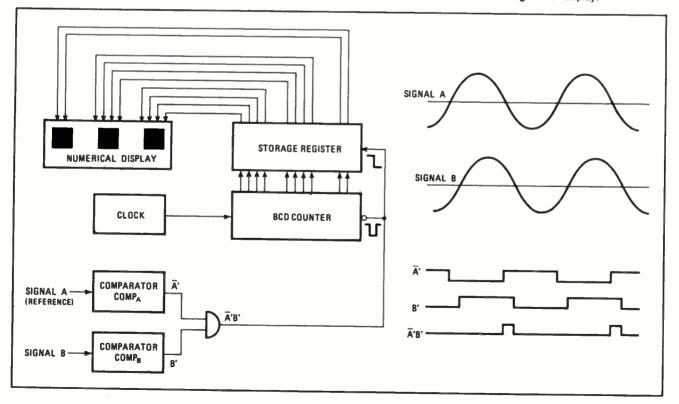

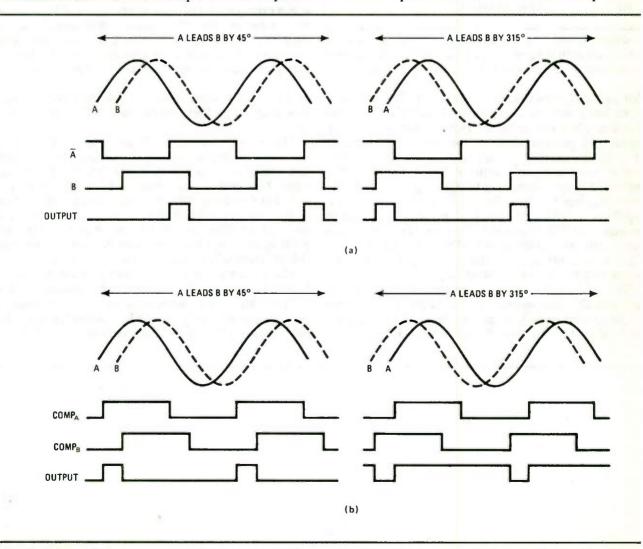

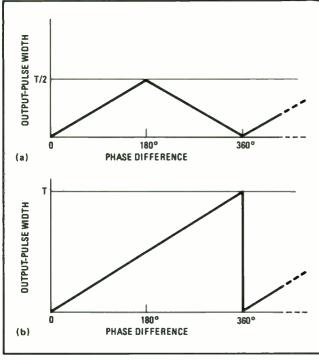

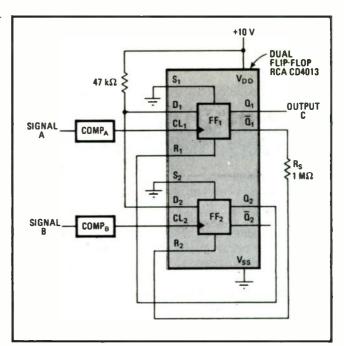

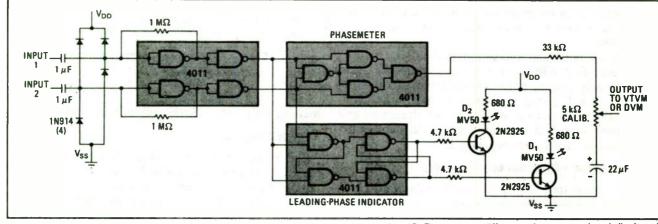

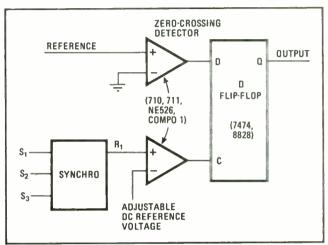

- 234. Digital logic circuit reads phase difference

- 235. Edge-triggered flip-flops make 360° phase meter

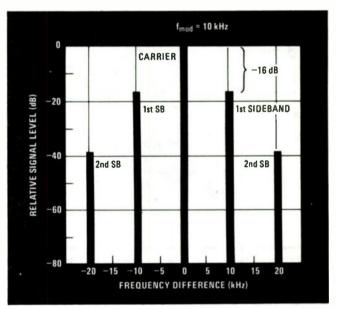

- 237. Spectrum analyzer aids fm deviation measurement

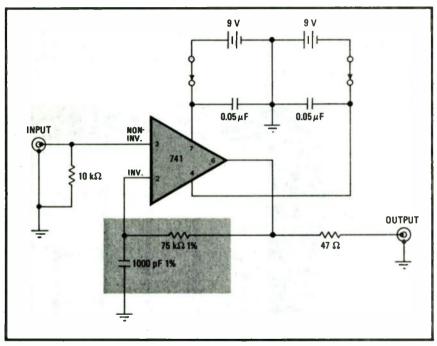

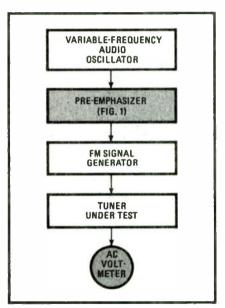

- 238. Pre-emphasizer speeds fm-tuner measurements

- 239. C-MOS phasemeter can be built in lab

#### 31. Pulse effects and measurements

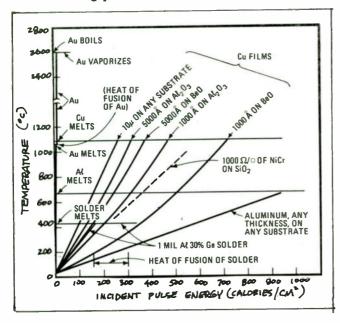

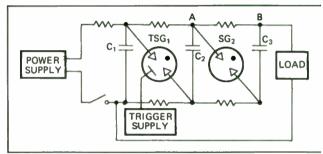

- 240. Evaluating high-energy pulse effects on materials

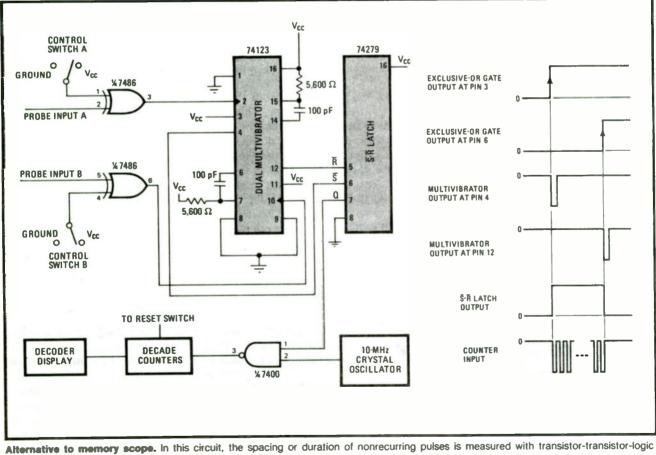

- 241. ICs replace memory scope for pulse measurements

#### 32. Frequency and time measurements

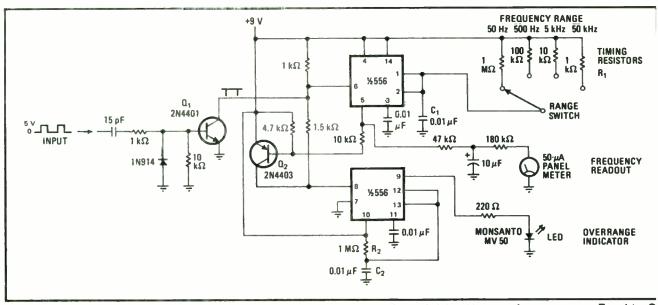

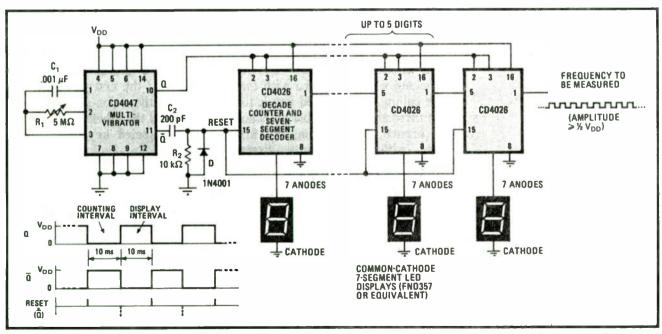

- 243. Overrange indicator can enhance frequency meter

- 244. Frequency-counter design minimizes number of parts

- 245. Color-TV set calibrates standard oscillators

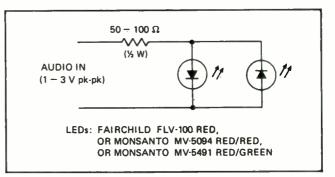

- 246. Visual zero-beat indicator uses reverse-polarity LEDs

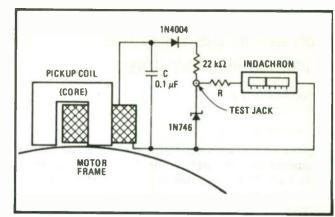

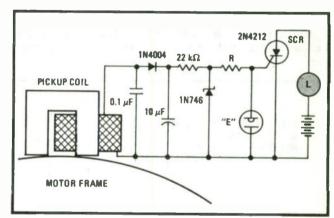

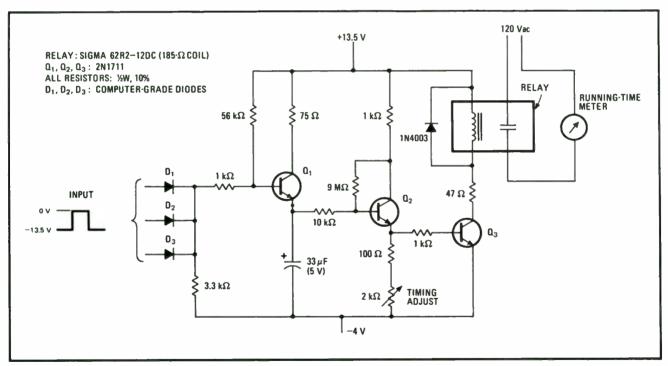

- 247. Induction pickup drives elapsed-time indicators

- 248. Measuring the use time of interactive terminals

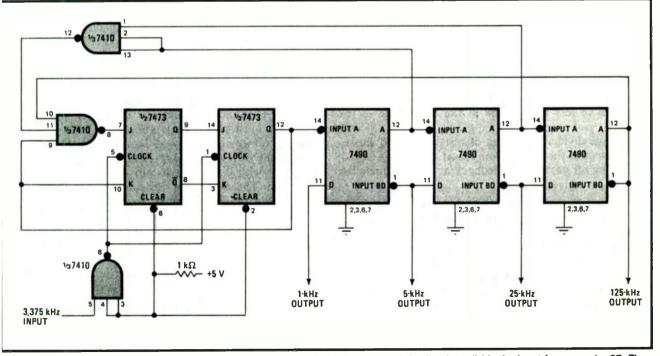

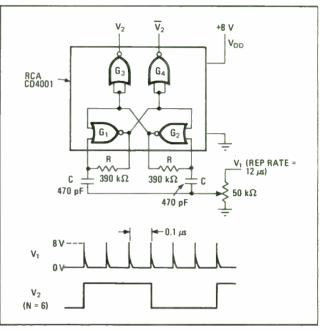

- 249. C-MOS gate package forms adjustable divider

#### 33. CRT image-display techniques

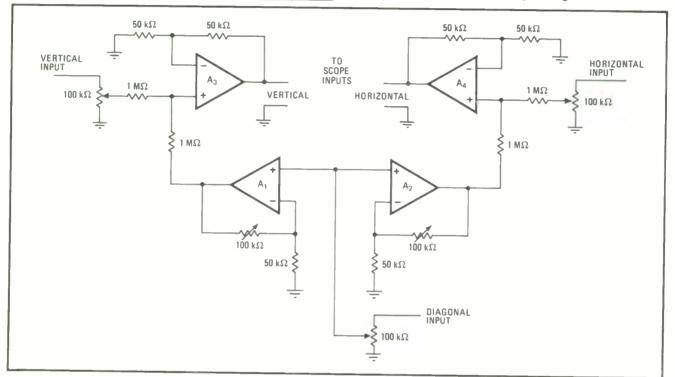

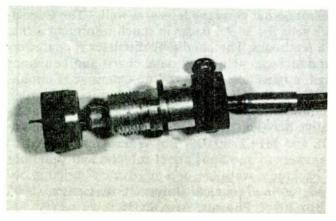

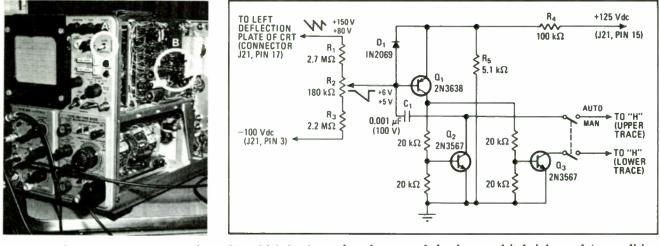

- 250. Circuit adds diagonal axis to any scope

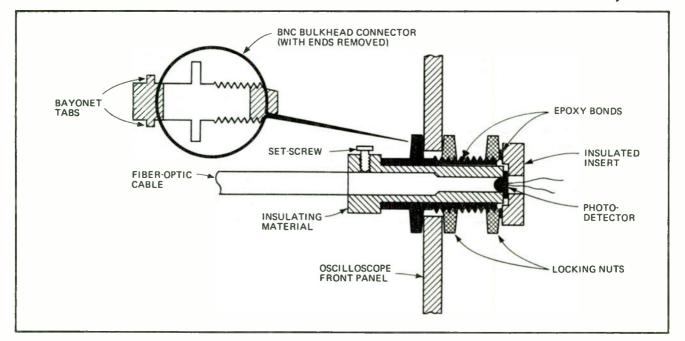

- 252. Optical trigger for scope reduces rf interference

- 254. Varying beam thickness in CRT display systems

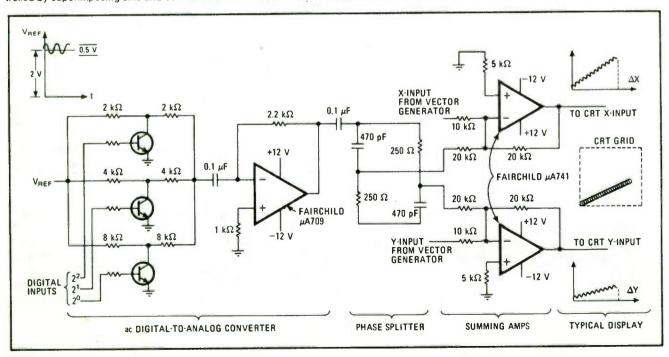

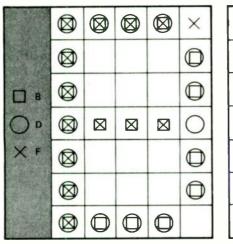

- 255. Displaying gray-scale images on bistable storage tubes

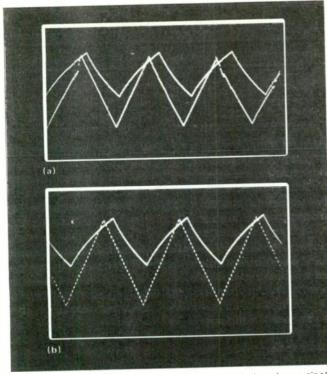

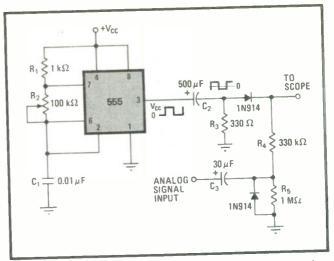

- 256. 555 timer tags waveforms in multiple scope display

- 257. Adding automatic erasure to storage oscilloscopes

- 258. Scanning only bright spots generates CRT characters fast

#### 34. Checking binary data with a scope

- 261. Oscilloscope displays contents of RAMs and ROMs

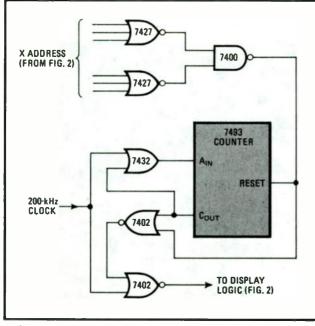

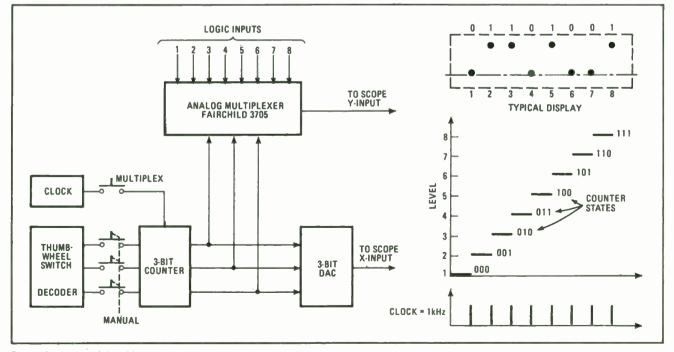

- 263. Circuit lets regular scope monitor eight logic inputs

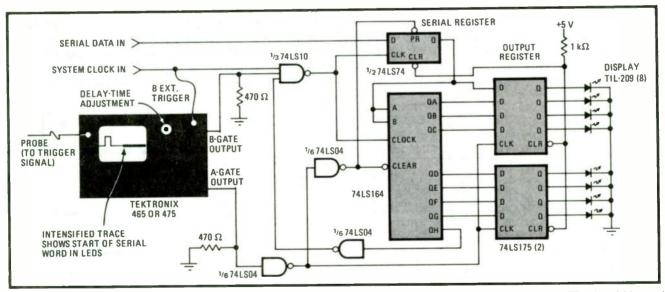

- 264. Scope-triggered register freezes serial data

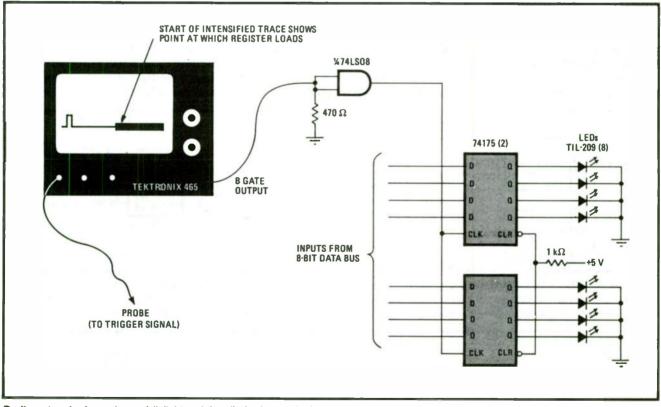

- 265. Scope-triggered register freezes data for display

#### 35. A potpourri of controls

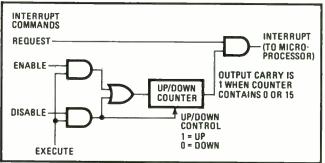

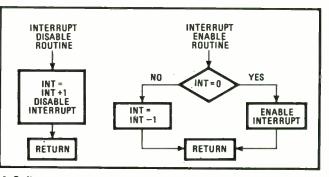

266. Counter keeps track of microprocessor interrupts

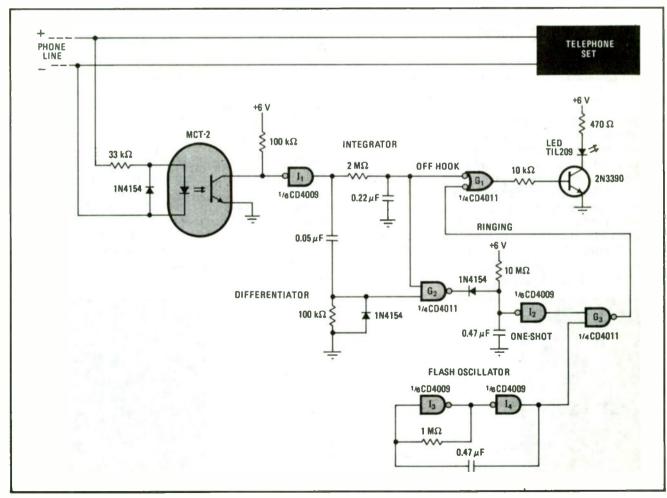

- 267. Optical isolator circuit shows phone-line status

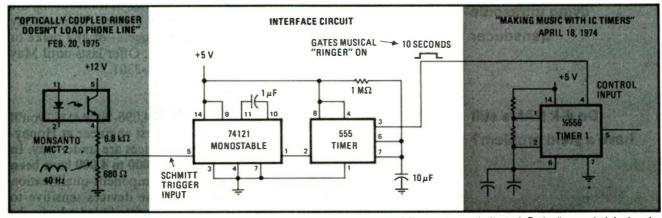

- 268. Ringer enables telephone to play simple tune

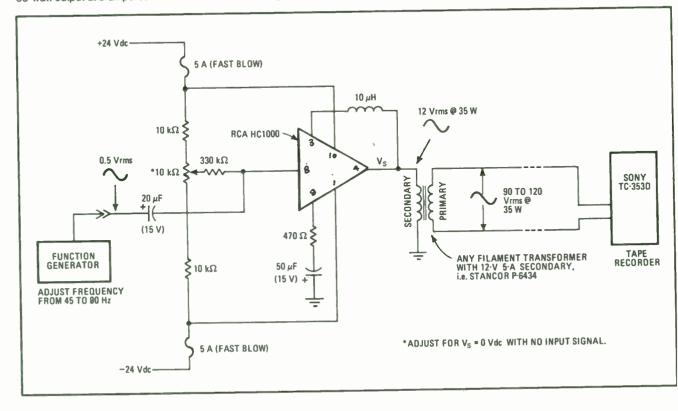

- 269. Power hybrid circuit controls tape-recorder speed

- 270. Guidelines for design of front panels

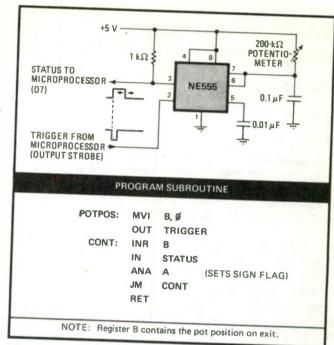

- 271. Microprocessor converts pot position to digits

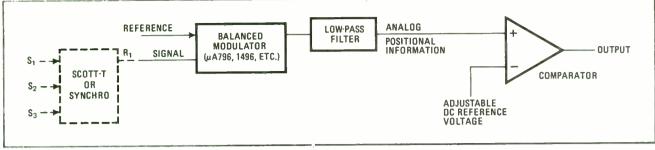

- 271. Two circuits indicate synchro shaft position

- 272. Minicomputer controller is inexpensive

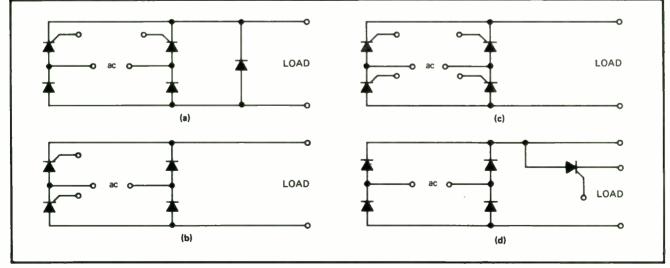

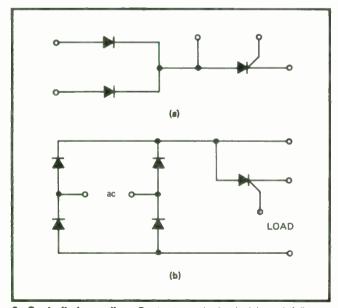

- 274. Packaged power circuits satisfy control applications

#### 36. Switching made easy

- 276. Comparator circuit makes versatile Schmitt trigger

- 277. Reed-relay switch turns on calculator chip fast

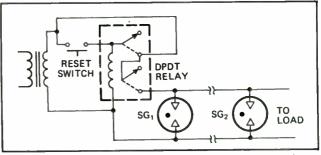

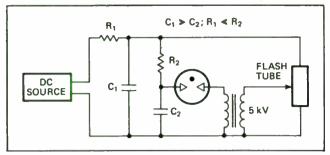

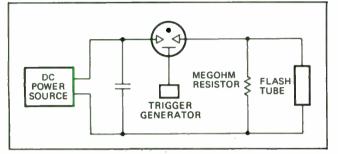

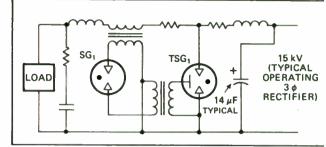

- 278. Spark gaps can switch as well as protect

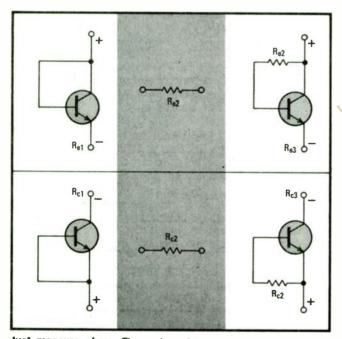

- 280. Simulating an npn/pnp pair for high-voltage switching

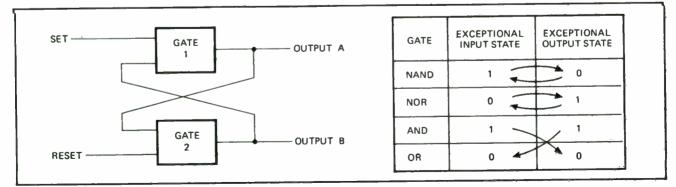

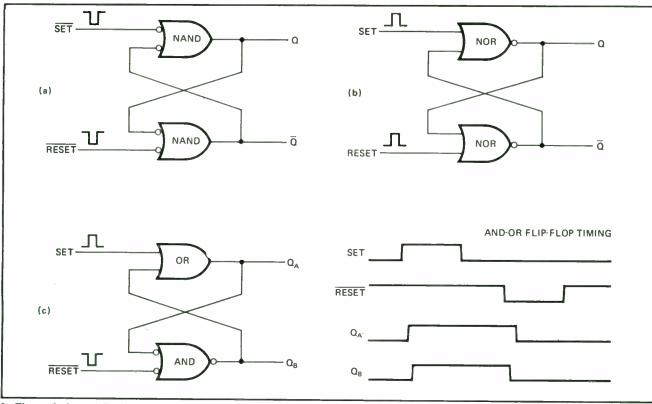

- 280. Another way to build a two-gate flip-flop

- 281. Operating a logic gate as a flip-flop

#### 37. Regulating temperature on circuit boards

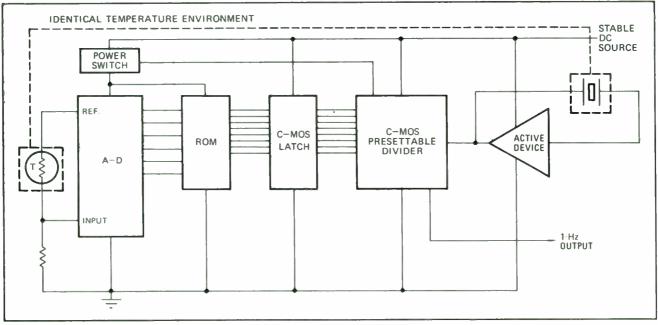

- 283. Digital ICs set temperature compensation for oscillators

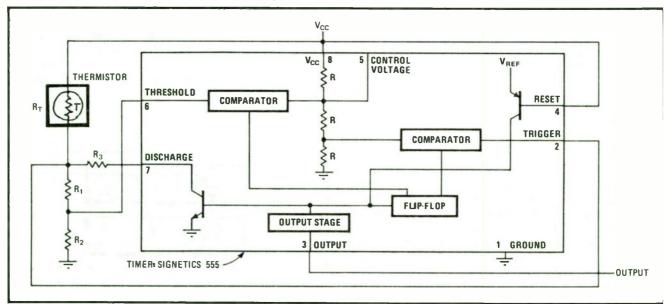

- 285. IC timer plus thermistor can control temperature

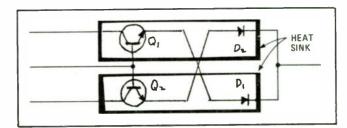

- 286. Thermally adjacent diodes balance transistor conduction

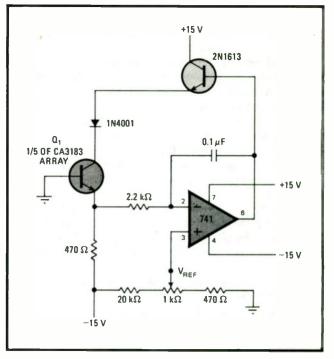

- 287. One transistor senses and heats in temperature regulator

- 287. Single thermistor can serve as simple temperature regulator

#### 38. Rf, microwave, and noise measurement

- 289. Choosing the right detector for rf power measurements

- 290. Compensating couplers improve measurement accuracy

- 291. Probing system noise from hertz to mergahertz

- 293. Microwave leakage monitor is economical but sensitive

- 295. Compact rf wattmeter measures up to 50 watts

#### 39. How to test ICs

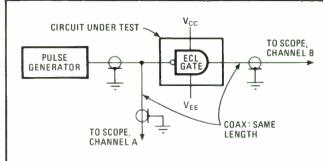

- 296. Checking wired-AND gates in just one test setup

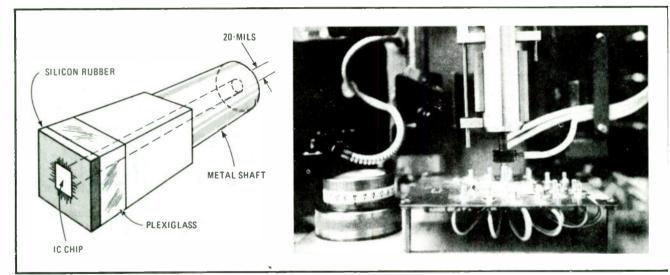

- 297. How not to destroy beam leads in testing IC chips

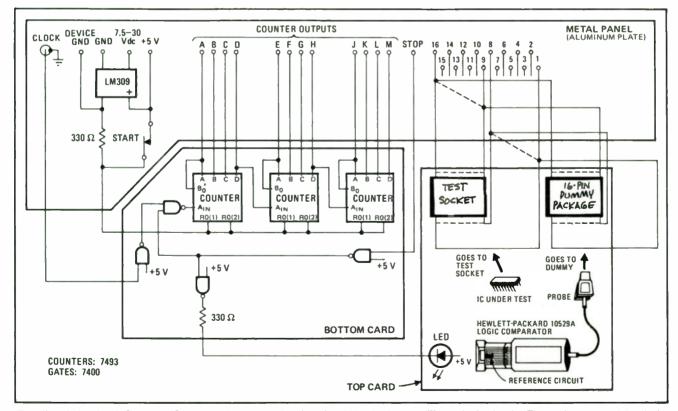

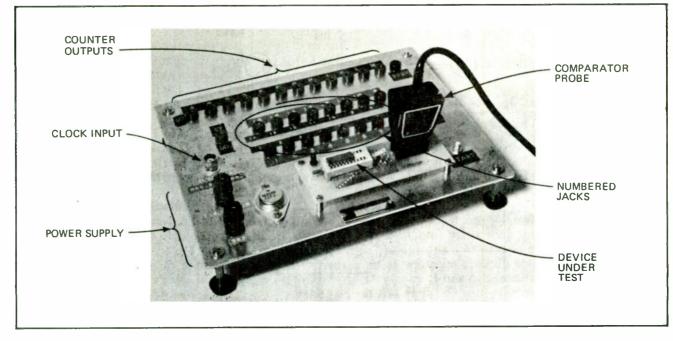

- 298. Production logic tester checks a variety of ICs

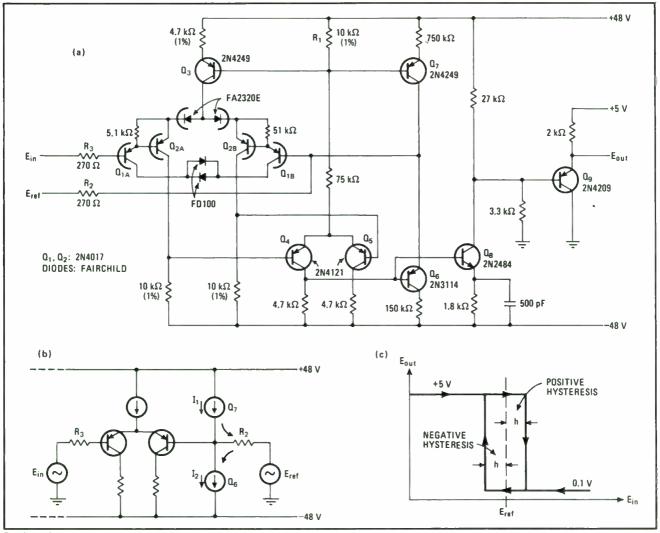

- 299. Precision comparator circuit satisfies LSI testing needs

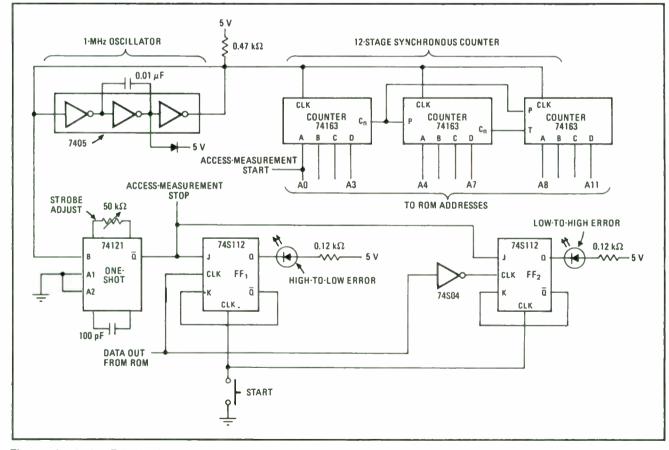

- 301. Measuring the access time of bipolar read-only memories

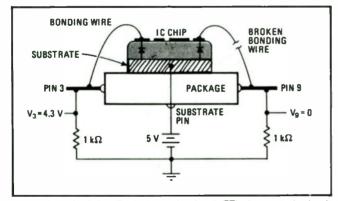

- 302. Back-bias continuity checks TTL wire bonds

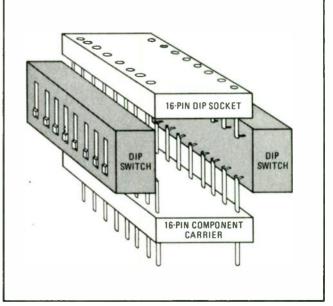

- 303. DIP switch isolates faults in system

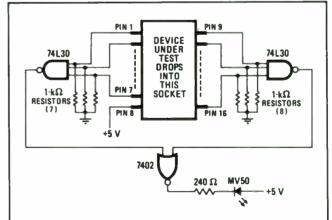

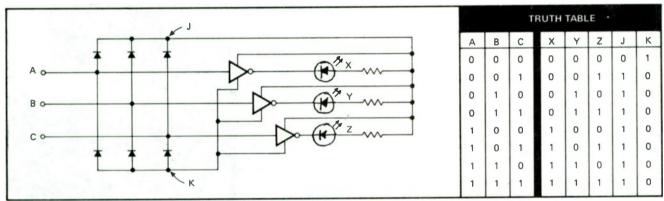

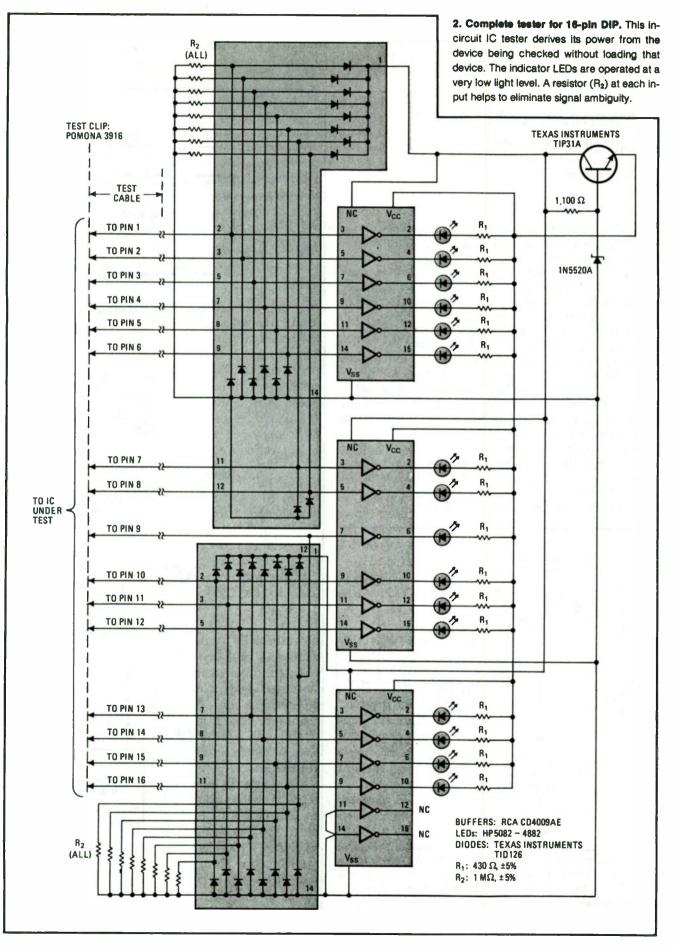

- 304. In-circuit IC tester checks TTL and C-MOS

#### 40. Testing that cable assembly

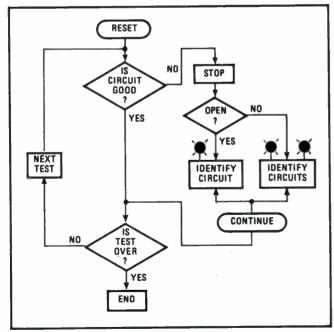

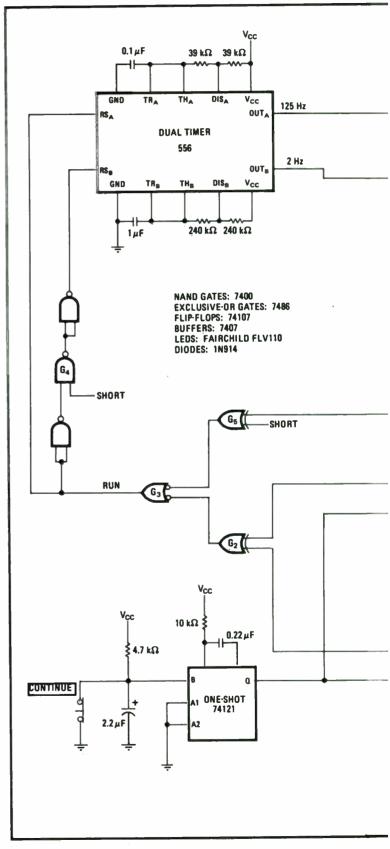

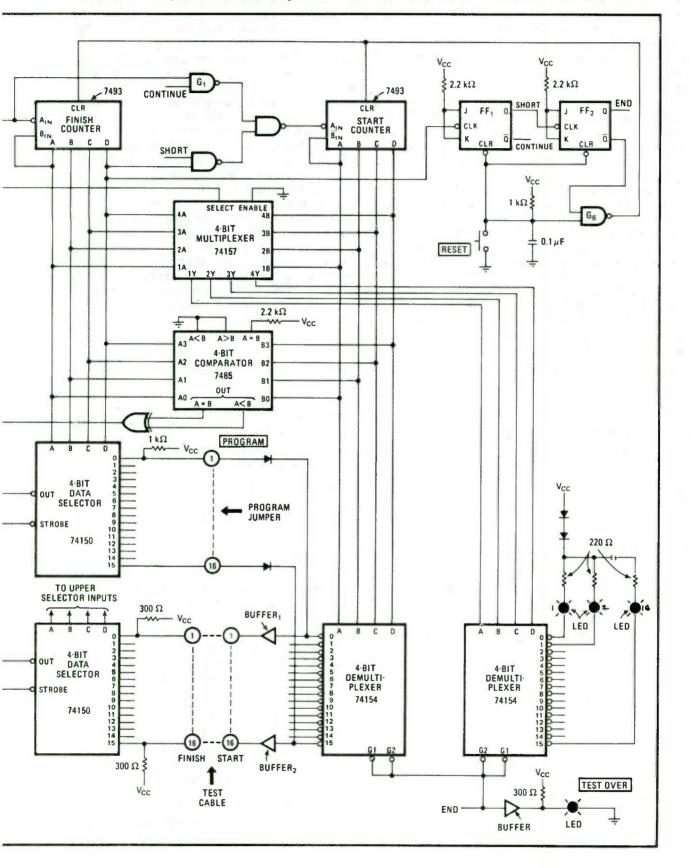

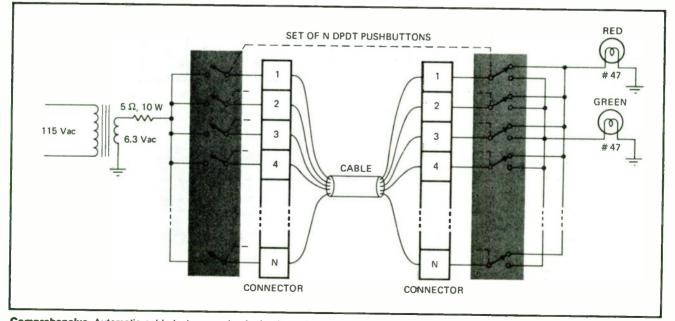

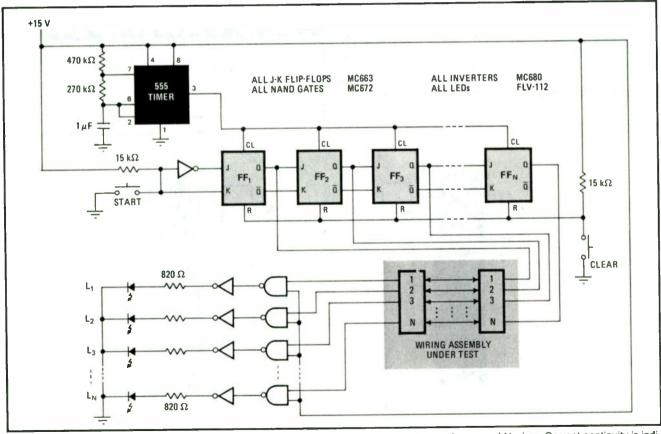

- 306. Programmable cable tester spots opens and shorts

- 308. Three measurement points give coax loss equation

- 309. Simple cable tester spots faults, identifies repairs

- 310. Logic circuit tests wiring assemblies

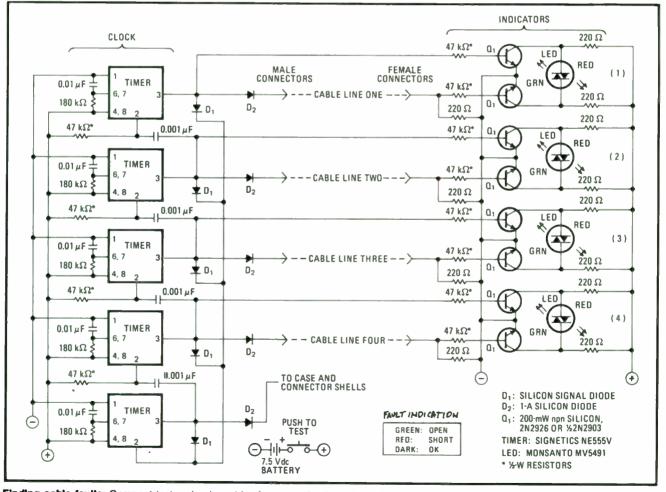

- 311. Timer ICs and LEDs form cable tester

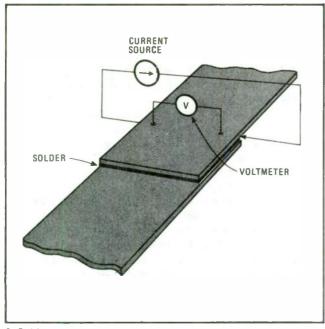

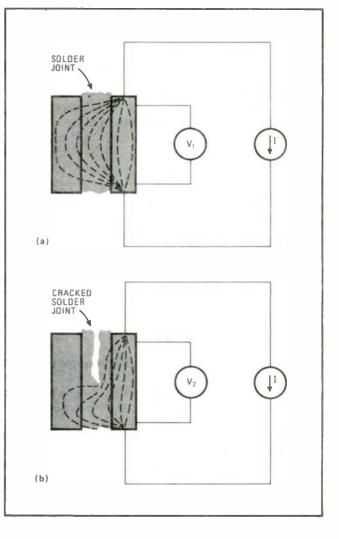

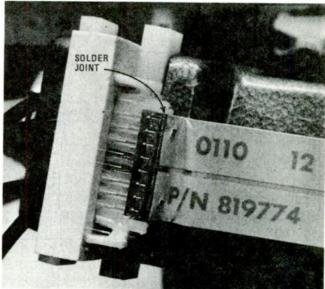

- 312. Four-point method tests solder joints

#### 41. Testing your power supply

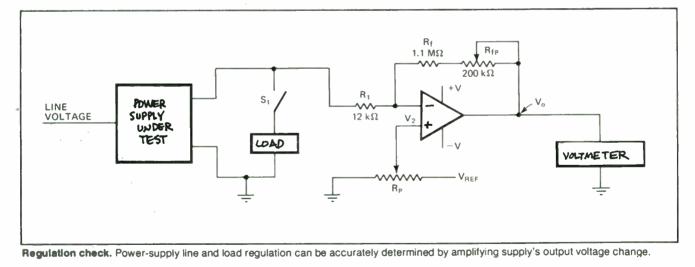

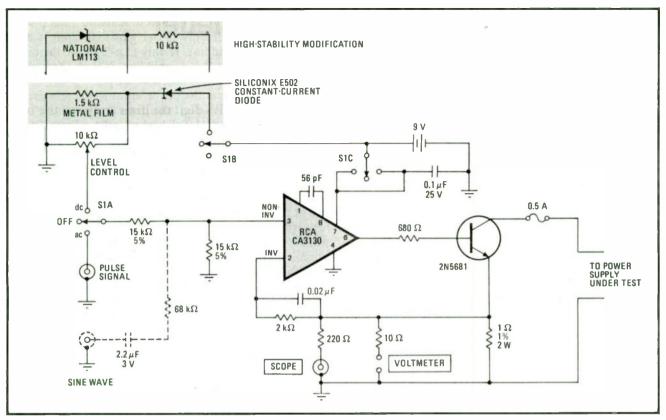

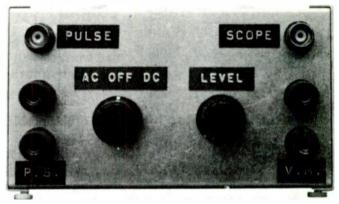

- 314. Testing power supplies quickly and cheaply

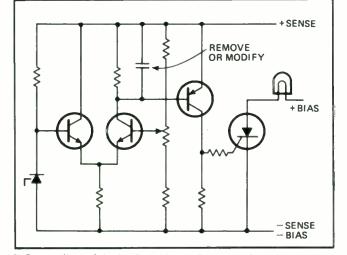

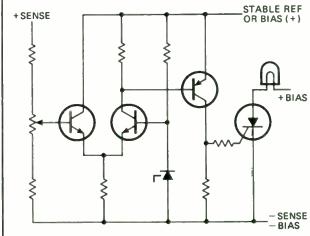

- 314. Electronic load aids power-supply testing

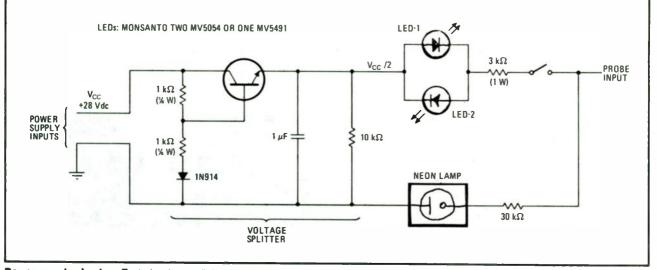

- 316. LED test circuit checks power-supply connections

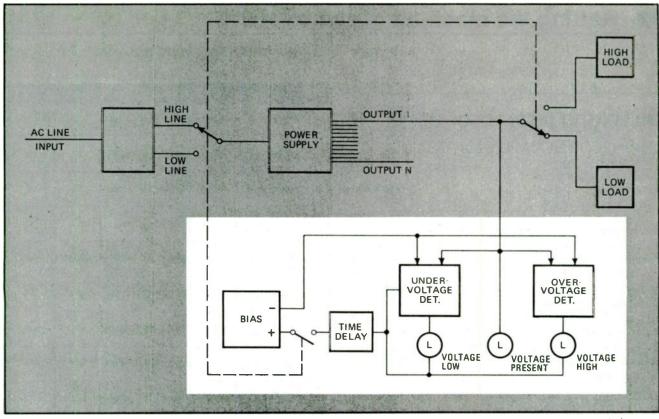

- 316. Simple production testing of multioutput dc power supplies

#### 42. Getting the most out of your meters

- 318. Multiplying factors correct power for ac waveforms

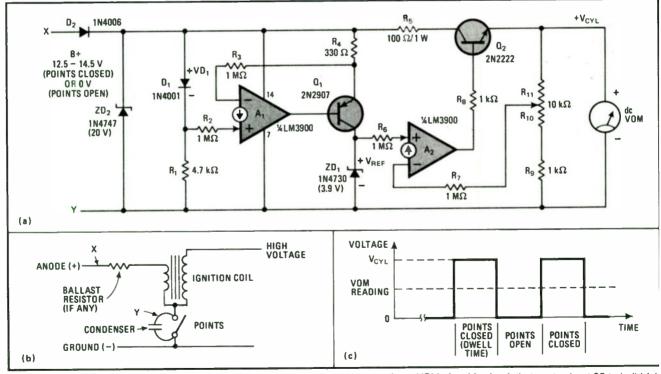

- 319. VOM with calibration circuit measures ignition dwell angle

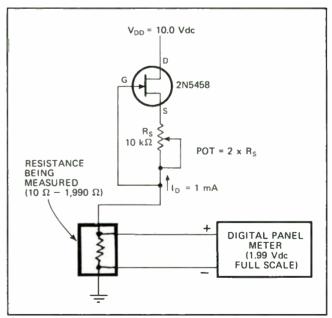

- 320. Converting a digital panel meter into a linear ohmmeter

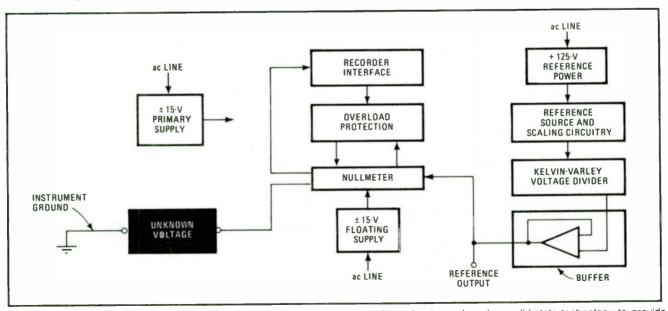

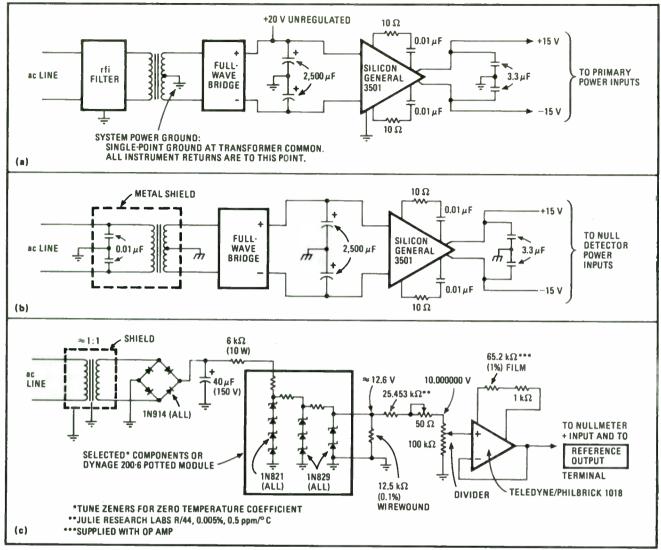

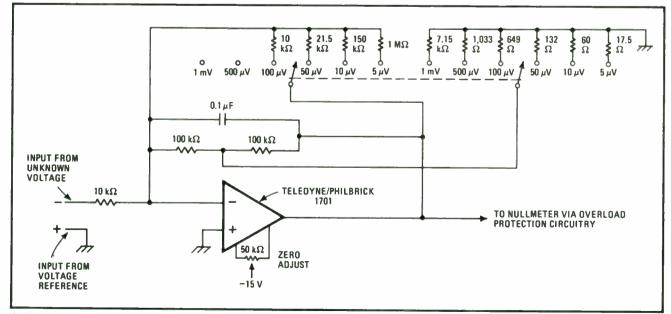

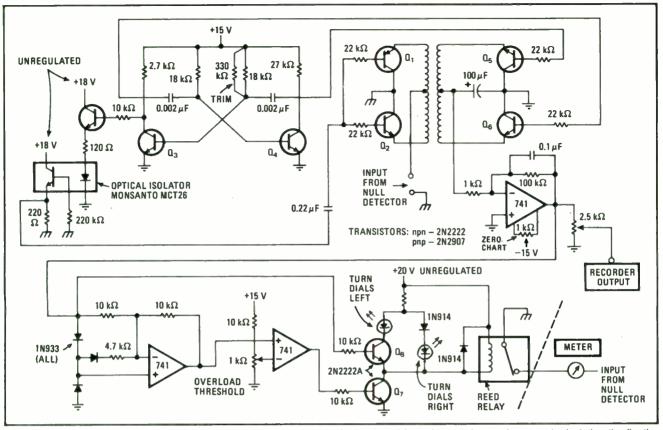

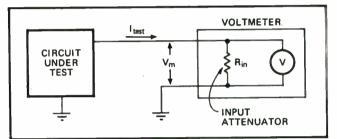

- 321. Dc differential voltmeter resolves 1 microvolt

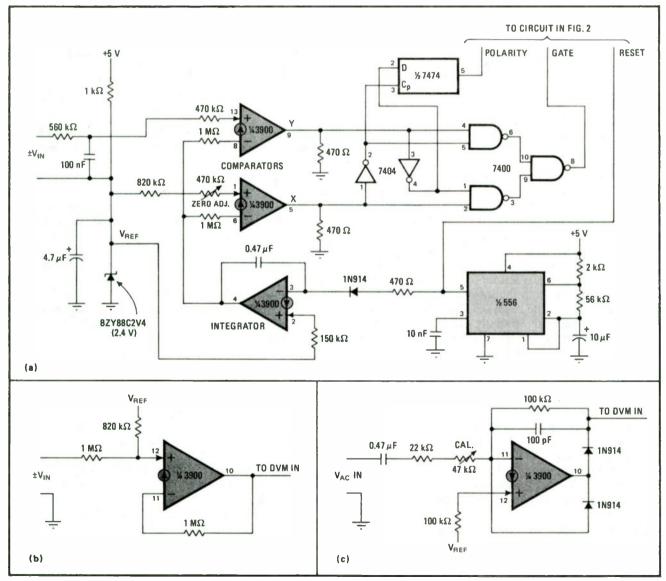

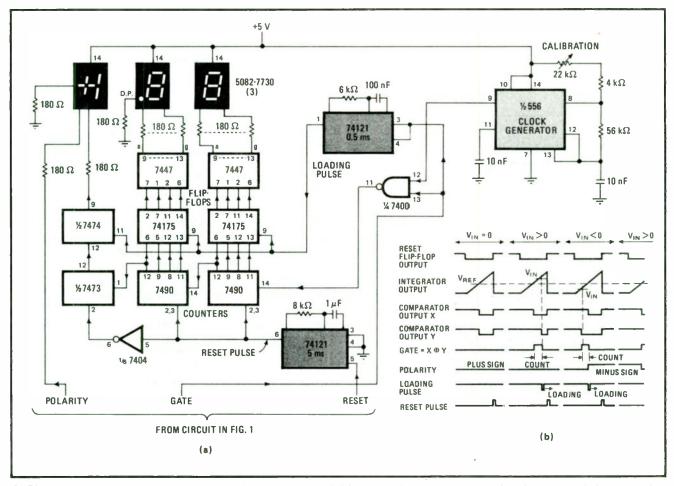

- 324. 21/2-digit DVM uses quad Norton op amp

- 326. Measuring small currents with an ordinary voltmeter

- 326. Table of conversion factors for ac waveform values

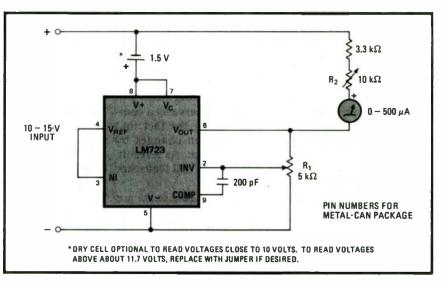

- 328. Voltage-regulated IC biases expanded scale meter

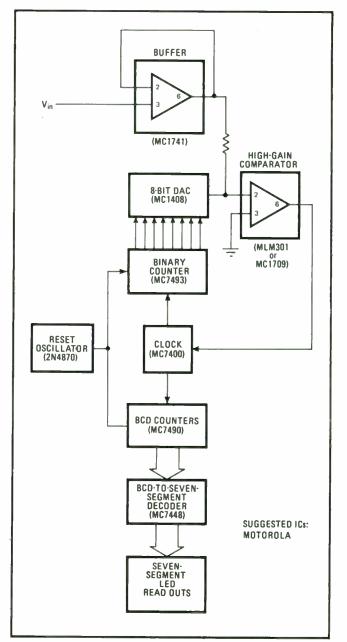

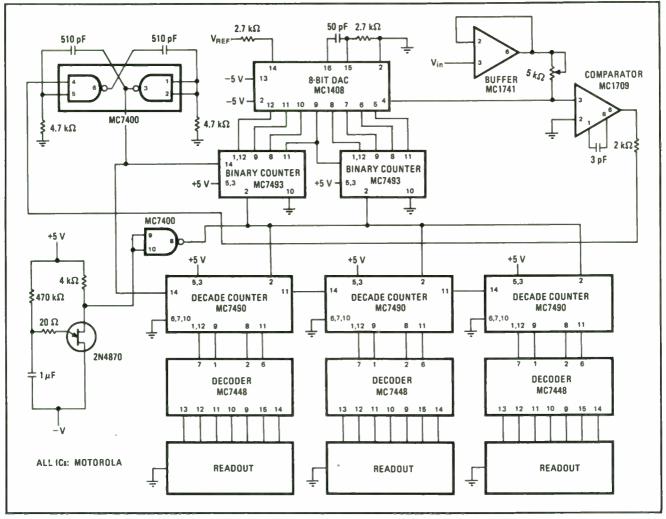

- 329. Building your own digital voltmeter

- 330. Increasing voltmeter input imnpedance to 1012 ohms

- 331. Getting the most out of the digital multimeter

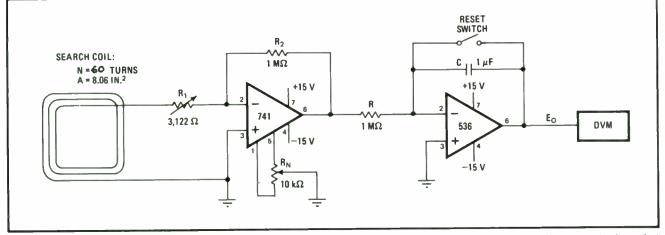

- 332. Op amp converts DVM to fluxmeter

#### 43. Pocket-calculator shortcuts

- 333. Using pocket calculators to square numbers directly

- 333. Three-step shortcut for finding square roots

- 334. Fast number conversion from any base to base-10

- 334. Calendar computations: past, present, and future

- 335. Storing two constants instead of just one

- 335. Doing statistical analysis with a single data entry

- 336. Calculator totals two sets of numbers simultaneously

- 336. Fast method converts numbers from base 10 to any other

- 337. Finding reciprocals easily with pocket calculators

#### 44. Calculator versatility

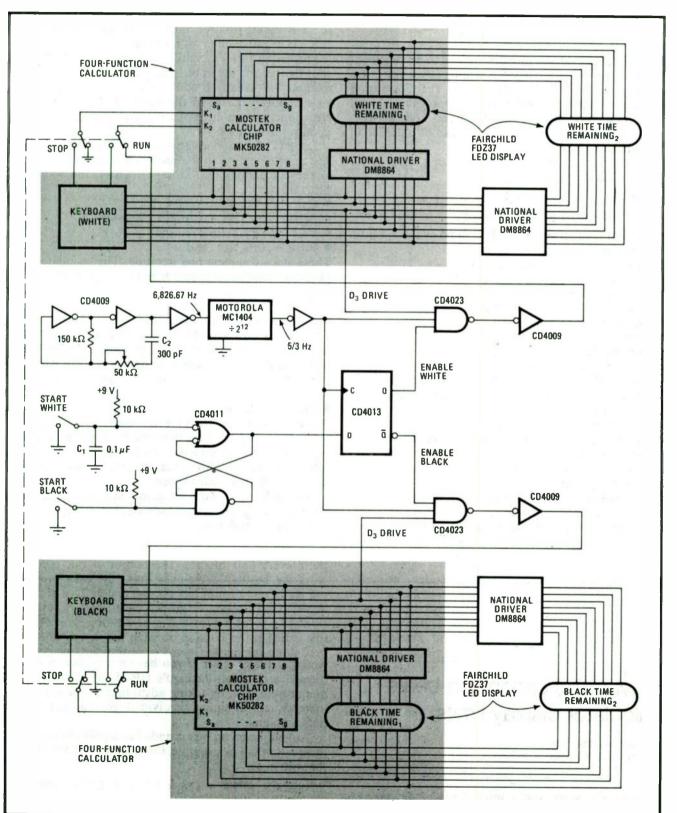

- 338. Four-function calculators time chess matches

- 340. Evaluating polynomials and finding their roots

- 340. Polynomial expansion beats calculator display limits

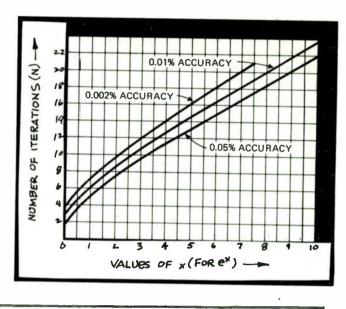

- 342. Evaluating e\* with constants

- 342. Chain operation for finding ex

- 343. Counting keystrokes to get results

- 343. Evaluating logarithms by counting keystrokes

- 344. Another way to compute ex

- 344. Computing sine and cosine with linear interpolation

- 345. Polynomial evaluations can be fast and accurate

#### 45. Programmable calculator techniques

- 346. Programming an SR-56 to serve as stopwatch

- 347. HP-25 calculator serves as clock

- 347. Program provides card storage of SR-52 data-memory contents

#### 46. Curve-fitting programs

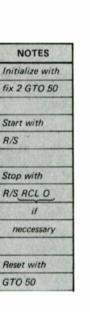

- 349. Curve-fitting program matches measured data

- 350. Weighted averaging simplifies curve fitting

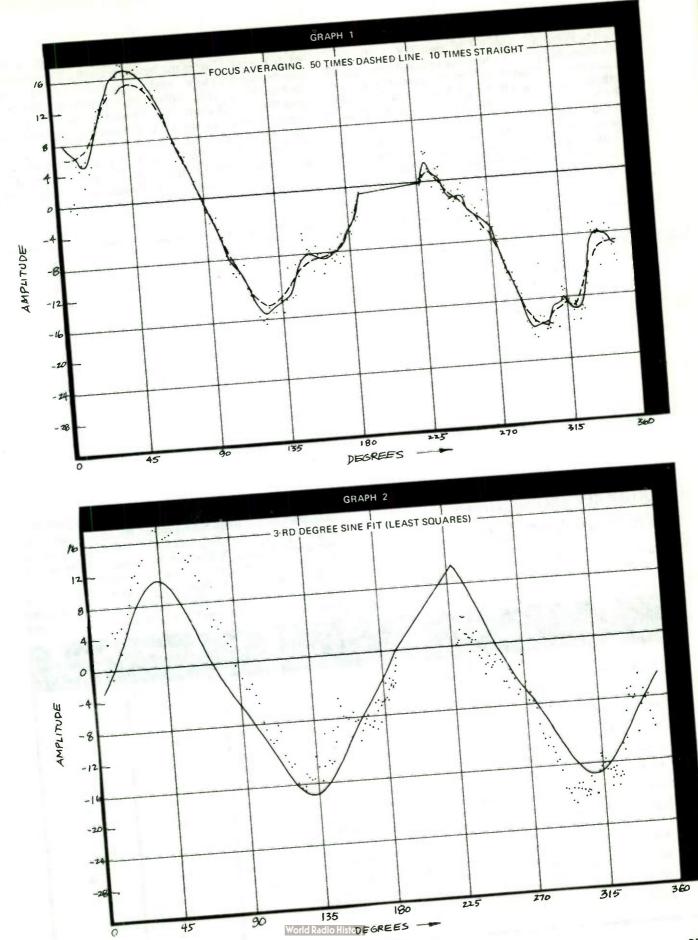

- 352. Computer plots curves on standard printer

#### 47. A variety of power supplies

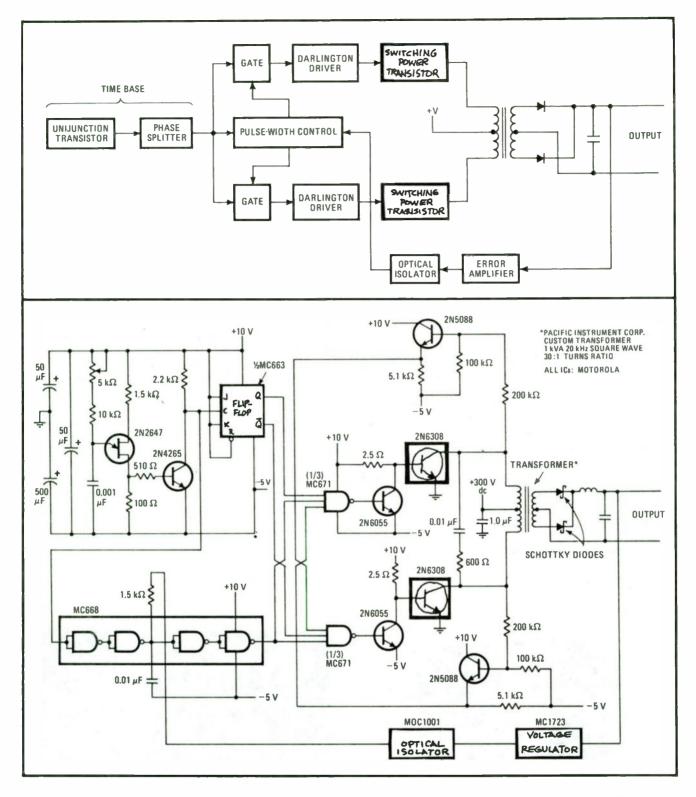

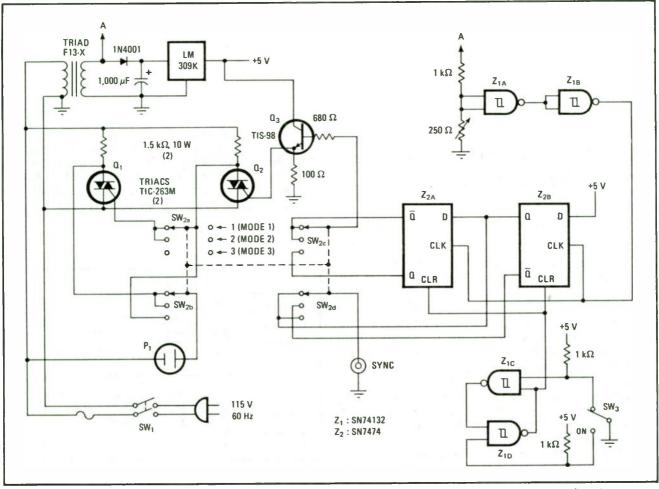

- 355. Doubling the frequency of switching regulators

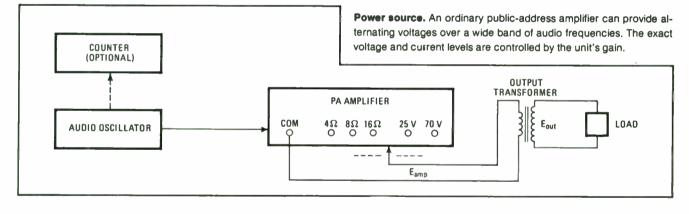

- 357. Public-address amplifier serves as variable ac-power source

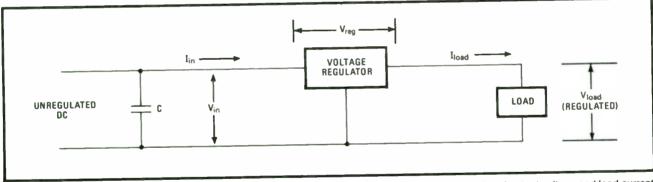

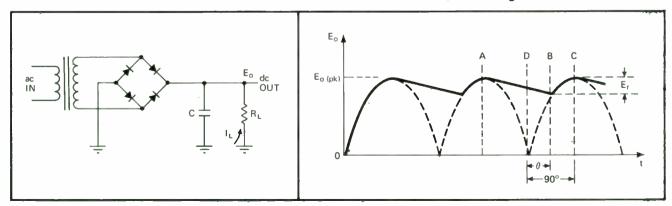

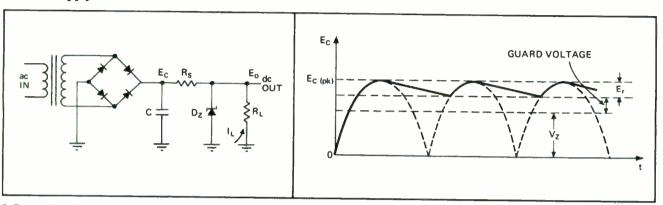

- 357. Power supply's VC product sets interrupt capability

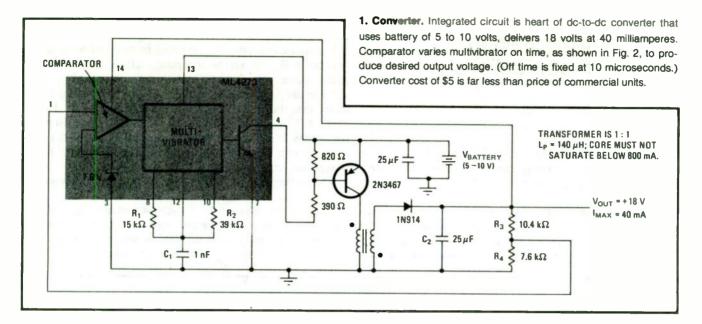

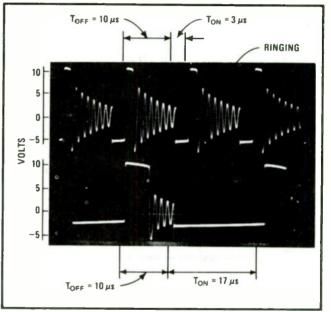

- 358. Monolithic IC simplifies dc-to-dc converter design

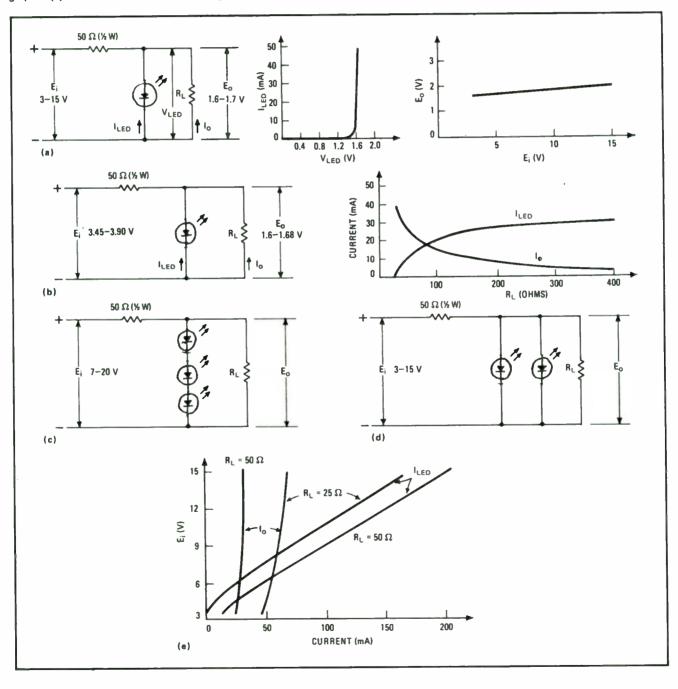

- 360. LEDs regulate voltage for C-MOS applications

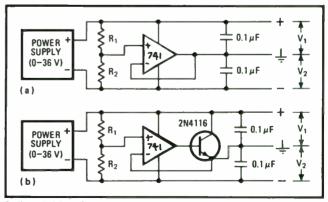

- 361. General-purpose op amp forms active voltage divider

- 362. Power supply transients kept under control

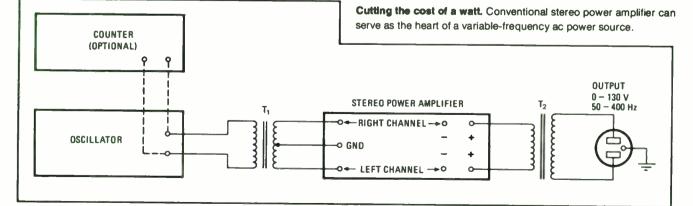

- 363. Regular stereo amplifier can be variable ac source

- 364. Power supply design made fast and simple

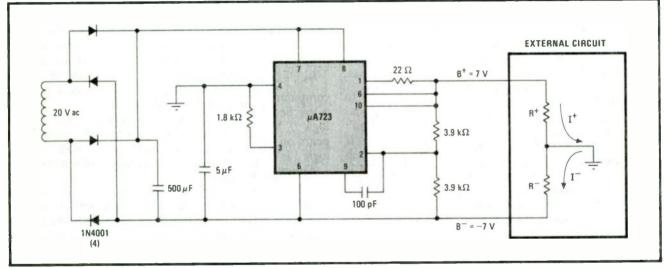

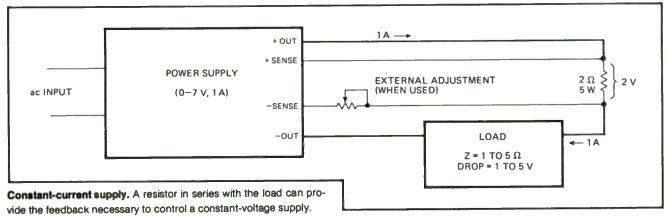

366. Voltage-regulated power supply delivers constant current

#### 48. Glossaries of electronics terminology

367. An abbreviated guide to electronics abbreviations 369. Digital-testing glossary reflects industry usage

# Preface

As every electronics engineer knows, there's more to designing a circuit or a system than just coming up with a circuit diagram and plugging in components of the right value. Engineering a product that works entails a whole raft of associated techniques—making measurements, interpreting data, making calculations, choosing materials, controlling environment, laying out and packaging the right components, and interconnecting them swiftly and without error. All of these steps take time and money—the two traditional enemies of engineers trying to make a contractual deadline or answer a marketing department's cry for help.

This book is intended to help electronics engineers save time and money in accomplishing the many adjunct tasks that comprise design. It is a compilation of articles from Engineer's Notebook, a regular and highly popular feature in *Electronics* magazine. There are 48 chapters containing 293 articles with a wealth of valuable tips that can shorten design time, increase engineering productivity, and free engineers from routine tasks for more creative work. It takes a how-to approach that is generously illustrated with charts, diagrams, calculator programs, tables and nomograms.

Representing the accumulated experience of hundreds of design engineers, this volume is an invaluable resource that can be called upon again and again.

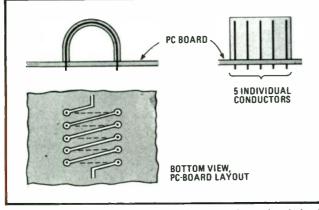

### Ribbon cable makes coils for printed-circuit boards

by Jim Edrington and F.E. Hinkle Jr. Applied Research Laboratories, University of Texas at Austin

A microhenry inductor loop made from flexible ribbon cable is easy to mount on printed-circuit boards, and its inductance value is easy to control. This loop is a cross between the familiar wire-coil inductor and a printedcircuit inductor. Since the ribbon-cable loop is three-dimensional, a larger amount of inductance is possible for a given area than a printed-circuit coil can provide. Moreover, the ribbon inductor is much easier to manufacture and control than the usual wire-coil inductor.

Figure 1 illustrates the technique of bending the flexible cable into a semicircle and soldering the ends into a pc board so that the conductors interconnect to form a multiturn coil with a "D" cross section.

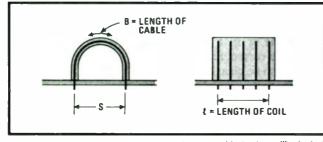

The inductance of a "D" cross-section coil may be calculated from the formula for a circular coil, with the

1. Loops good. Flexible ribbon cable is mounted on printed-circuit board, with individual conductors cross-connected in series, to form an inductance coil. One loop can be nested inside another to form a transformer, and individual turns of the loop can be tapped. These coils have the amounts of inductance needed for rf tuning.

**2. Sizing it up.** Definitions of dimensions used in text are illustrated. A given ribbon has a fixed number of conductors per inch of ribbon width (coil length), so n and I are equivalent quantities.

effective radius of the "D" coil substituted for the actual radius of a circle. For a single-layer n-turn circular coil with radius a and length l, the inductance in microhenries is

$$L = n^2 a^2 / (9a + 10l)$$

where a and l are in inches.

For a "D" coil with the dimensions shown in Fig. 2, the effective circumference, C, is the length of the ribbon cable, B, plus the pc-board spacing, S. The effective radius can be calculated from

$$r_{\rm eff} = C/2\pi = (B+S)/2\pi$$

Thus, the inductance in microhenries of the coil made with ribbon cable is

$$L = n^{2}[(B+S)/2\pi]^{2}/[9(B+S)/2\pi + 10l]$$

where all dimensions are in inches.

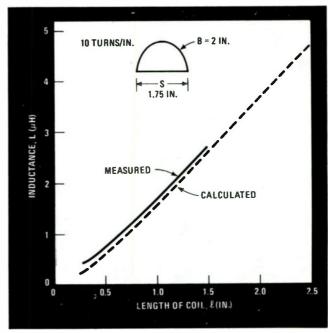

The measured and calculated inductances of an actual "D" coil are plotted versus the length (l) of the coil in Fig. 3. The coil for this test was made of a 2-inch length of Ansley Flexstrip with a pc-board spacing of 1.75 in. With 10 conductive strips per inch, the Flexstrip forms a coil with 10 turns per inch. The calculated values of inductance proved to be close to the measured values over a range of coil lengths from 0.5 to 3.0 in. (n = 5 to n = 30).

Since flexible cable of this type can be purchased in precut sizes, the manufacture of highly repeatable inductors can be simplified. An impedance transformer can be made by adding a second coil inside the first. A

3. Microhenries. Inductance of ribbon-cable inductor is shown as a function of coil length, I. Since ribbon has 10 conductors per inch of width (coil length), abscissa represents 0 to 25 turns.

multiple tapped inductor is easily formed by bringing out any of the turns on the printed-circuit board. Since every turn is terminated on the board, other electrical components may be wired with the coil. For example, capacitors may be paralleled with the coil to form tuned rf circuits.

## Etching your own pc boards quickly and accurately

by Herman Levin and G. Thomas Oppenheimer Colorado State University, Fort Collins, Colo.

Putting together an efficient etching tank for laboratory or prototype production of printed circuits is relatively simple. There's no need to buy a commercial kit for a tank that will require constant stirring and either takes at least half an hour to etch one board or, if large enough to work faster and ensure no undercutting, becomes very costly.

This froth etcher is designed for fast turnaround of both single- and double-sided boards on which fine resolution is also important. It produces uniformly etched pc boards in about four minutes with very little undercutting. As a bonus, the process automatically aerates the etchant, greatly extending its life.

Constructing the etcher is quite simple. All that you need is a heat-resistant glass dish with cover, a tungsten-carbide hacksaw blade for notching the dish cover, some two-part epoxy adhesive, a holder for the boards being processed, three ceramic aquarium aerators, some rubber air tubes for holders, and a thermometer. You cement the aerators to the bottom of the glass dish, and

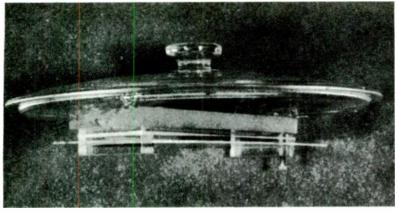

**Observing the etching process** is easily done by lifting the heatresistant glass etcher cover to which the printed-circuit board is attached. Before the cover is removed, the air supply must be turned off to prevent any spattering of the etchant.

a quick-change pc-board holder to the cover. Then you cement the thermometer and tube holders to the side of the dish and notch the cover to provide egress for them. Mix up a batch of ferric chloride in a concentration of 1¼ pounds of FeCl to every quart of water at a temperature between 100°F and 110°F, and you're ready to start etching.

To etch, you simply:

• Place the etcher on a hot plate and fill it with etchant to a level that just reaches the bottom of the copper-clad pc board.

Heat the etchant to its lower operating temperature

The continuous air flow through the aerators creates a surface froth that scrubs the board with constantly agitated etchant. The sliding clamp holder which is attached to the cover dish permits rapid insertion or reversal of the printed-circuit board.

Aquarlum aerators are cemented into the bottom of the heatresistant dish, along with sections of plastic tubing to support the rubber tubing and thermometer. The tubes are connected by T-fittings to a single tube connected to the main air supply.

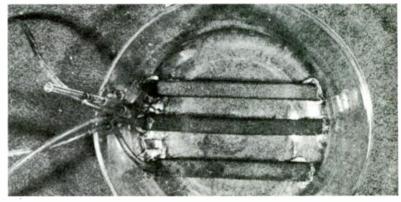

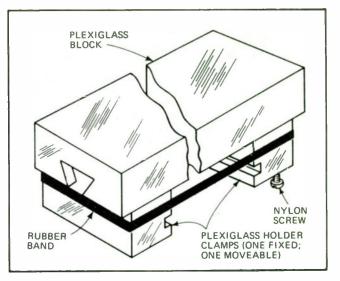

Plexiglass holder clamps grip the edge of the pc board, assuring uniform etch of the entire surface. One clamp is threaded and fitted with a nylon screw to accommodate boards of various sizes. A rubber band around the clamps provides tension.

#### $(100^{\circ}F)$ and turn the hot plate off.

Place the board to be etched in the holder, cover the dish, and turn the air supply on, adjusting it to create a continuing vigorous froth over the total surface of the etchant.

• After a few minutes—anything from three and a half to eight minutes, depending on the freshness of solution—inspect the board, if you want to, by raising the cover (the air supply must be turned off first to prevent

splattering of the etchant).

This system is also easily adapted to etching outsized boards that don't fit the glass dish. For these, you replace the glass dish with a covered polystryene box, of a type sold for household storage. You then place the etchant container in very hot water, so as to heat the etchant before pouring it into the etcher. The etchant, of course, could be used at room temperature at some sacrifice in speed.

### Soluble masks protect pc boards from solder

by H. G. Peters and K. Romano IBM Corp., Owego, N.Y.

Two kinds of water-soluble solder masks can, when applied to a circuit board before wave-soldering, keep solder out of plated-through holes. These holes must be kept open to permit dry components—thermally sensitive electrical devices—to be hand-soldered to the circuit board after the wave-soldering operation. Most previously known solder-mask or resist materials must be removed with solvent cleaning, which is expensive, or they leave questionable residues that impede hand-soldering. (Although a fluffy white residue appears when one of the two new materials is applied in excess, if allowed to dry for several days, it is easily brushed or blown off.)

Water-soluble masks are also useful for protecting large tab areas or other large areas of copper that are not to be soldered. Masking prevents solder from bridging between circuit lines on a printed-circuit board, even when hand-soldering or non-wet components are not involved. And, when parts of a board are to be coated with something, water-soluble masks can protect the areas that are not to be coated when the coating itself is not water-soluble; otherwise its application would wash off the mask material.

However, water-soluble masks do not work well on tin-lead plated parts, especially when large areas have to be masked, because the alloy reflows and lifts the mask from the circuit board.

The two new materials are based on sodium silicate and gum arabic, or acacia, both in water solution and both with small quantities of other materials added. The materials have different characteristics and react differently in any production process. However, both meet the primary objective—to prevent solder from wetting the masked areas, whether soldered as soon as the mask has dried, or days or weeks later. And neither material hampers any subsequent production process, nor permits solder reflow, which could cause bridging between masked circuit lines.

Like most other water-soluble masking materials, the new ones meet current regulations of the U.S. Occupational Safety and Health Administration and state agencies; they are, in fact, pollution-free. Even if large quantities of mask materials were accidentally spilled, no pollution limits would be exceeded because all of the ingredients have extremely high tolerance levels in waste water. They are also relatively nontoxic; continued exposure of production workers to either of the two

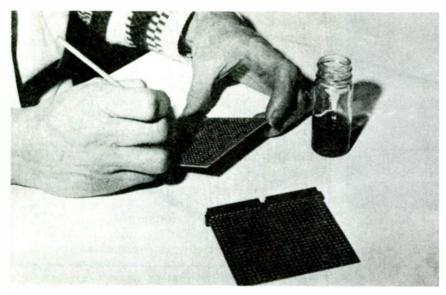

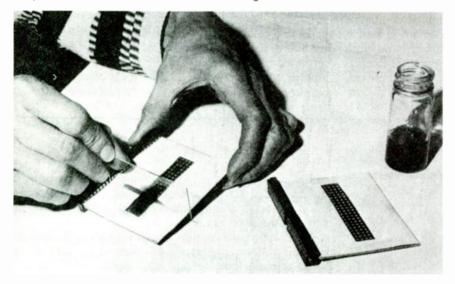

**Mask-maker.** Brushing and screening are two of several methods by which new water-soluble masking materials can be applied to printed-circuit boards. The materials keep solder away from selected areas as the board moves through a wave-solder machine.

materials has no serious or long-lasting effects.

A good solder mask must be pliable to permit normal handling after masking, and it must adhere to the substrate throughout any subsequent processing steps. In previous evaluations of gum arabic as a masking material, it has adhered poorly after extended shelf life. However, the new formulation contains a humectant—a substance such as ethylene glycol—that promotes moisture retention, so that there is no loss of adhesion from physical abuse, from successive mechanical handling processes after masking, or from extended exposure to temperatures as high as 150°F.

The new water-soluble masks can be left on the surface for several months at ambient or elevated temperatures without corroding, as some materials do. Furthermore, they actually improve the insulation-resistance, which on a series of test boards averaged an order of magnitude higher than on boards made with the IBM standard mask. The lower resistance encountered with the standard mask—still well up in the thousands or even millions of megohms—is caused by minute traces of the mask material, too small to affect soldering, but nevertheless sufficient to establish a tiny current path.

The constituents of both materials, which can be purchased from any chemical supply house at a low price, are easily mixed in a laboratory. The total costs will depend on production levels, mask-preparation time, and operator technique.

Water-soluble masks can be applied by any of several methods, such as by brushing, spraying, dipping, or screening. All application methods are relatively simple. However, when the gum-arabic mask is silk-screened, long fine strings or webs of material sometimes form when the screen is lifted off the substrate. As these webs break and fall to the substrate, they mask areas that should not be masked. This webbing apparently occurs only with samples of gum that have not been stored for a long time in a warehouse; natural aging of the gum eliminates the webbing.

Accelerated aging—heating at 75°C for one week—gives the same effect by driving off interstitial or bound water from the gum molecules. If a gum of any age is aged further by heating, a mask material made from it leaves no web. Webbing is also eliminated immediately by adding a small amount of potassium chloride to gum of any age; the chloride eliminates the forces that cause webbing. Because chloride addition is minimal, negligible

residues are left after mask removal.

The mask material must not dry while being applied, but, once on the substrate, the film must dry quickly to prevent flow of material into non-masked areas. Gum arabic in water solution satisfies these requirements, but sodium silicate, if dried too fast, leaves a residue after soldering and cleaning. Adding a humectant to the mask formulation makes it dry to a non-flowing tacky film in three to five minutes and dry completely within 10 minutes.

Water-soluble masks can be used effectively on plated-through holes as large as 0.25 inch in diameter, small and large surface areas, and even large tinned surfaces, although the tin should be precleaned to increase adhesion. The masks can be adapted to nearly any production process by varying the chemical constituents of the material.

## Versatile breadboard checks out designs quickly

by M.J. Salvati Sony Corp. of America, Long Island City, N.Y.

At a cost of only around \$25, a breadboard system can be put together that is both versatile and convenient to use. Nearly any type of component, including integrated circuits and discrete semiconductors, can be interconnected rapidly with ordinary hookup wire. And since the parts are not soldered and need no special adaptors, they remain undamaged and can be used again. The breadboard, of course, can be tailored to suit specific needs or outfitted with an adjustable power supply and different connectors for added flexibility.

The heart of the breadboard is its socket, which is manufactured by El Instruments, Inc. of Derby, Conn. (A similar socket, which is known as Superstrip, is available from AP Instruments in Painesville, Ohio.) Although relatively expensive—approximately \$17 when ordered singly—the socket is well worth the investment.

It has 64 rows of plug-in contacts along its length. Each row contains two groups of contacts, one on either side of the socket's midpoint. There are five tie points for each contact group. Component leads, input and output wires, and test probes can be simply inserted into the desired tie point.

Dual in-line packages snap right into the socket be-

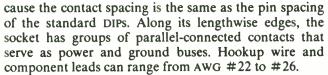

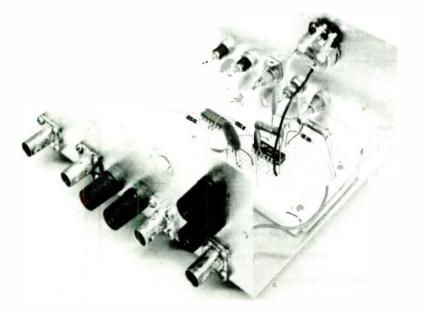

**1. Basic breadboard.** Oscilloscope sweep circuit (on right) can be rapidly laid out and tested with easy-to-use breadboard. Because components are plugged in, they can be used again. A circuit can be breadboarded almost as quickly as it can be drawn.

A basic version of the breadboard is depicted in Fig. 1, with a design for an oscilloscope sweep circuit already laid out. The socket is mounted in a minibox on a 3/32-inch-thick Lucite sheet. This increases the separation between the socket's contacts and the minibox so that the breadboard's capacitance to ground is reduced.

Since the minibox is made of two U-shaped pieces of aluminum that fit together as a closed box, it completely shields the circuit being checked and makes it easy to mount potentiometers, coils, and other components that are too large to be plugged directly into the socket. Connections to these components are made with 3-inch lengths of #22 wire having miniature alligator clips attached at one end.

Five binding posts on the back panel are provided for power input, and several sets of suitable input and output signal connectors are located on the front panel. Short lengths (2 to 3 inches) of #22 wire are soldered to the connectors for carrying the signal to and from the socket. With this arrangement, even many lead changes or jiggling will not upset the breadboarded circuit.

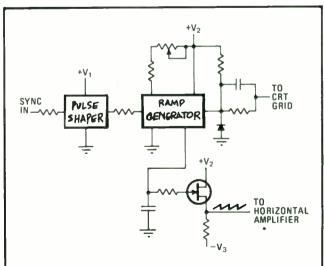

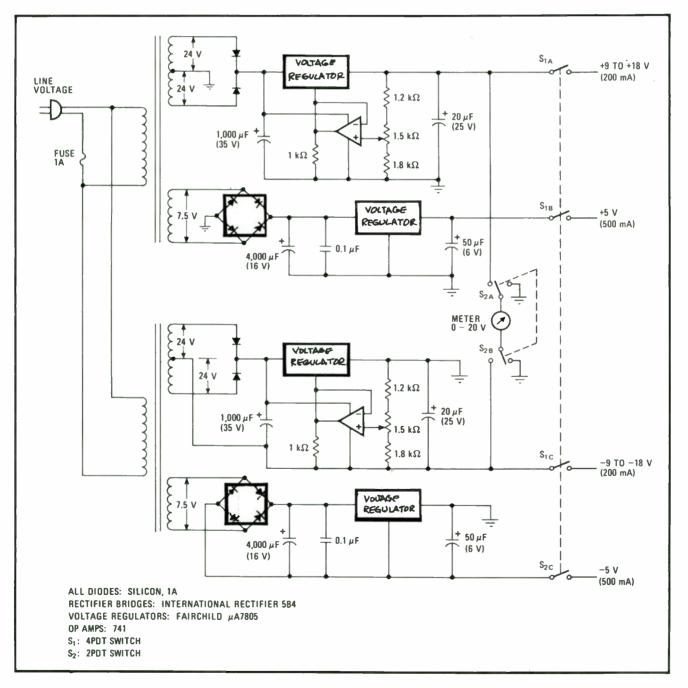

For the ultimate in breadboarding convenience, two miniboxes can be fastened together, and the lower minibox used to house one or more regulated power supplies, as shown in Fig. 2. This deluxe version, which costs about \$75 to build, offers two sockets, a choice of supply voltage, and a meter for reading out the level of the supply voltage. It is built with a pair of miniboxes measuring 8 by 6 by 3½ inches and outfitted front and back with BNC connectors.

The breadboard has fixed positive and negative 5volt supplies, as well as variable positive and negative supplies that can be adjusted from 9 to 18 v. (The schematic for these supplies is also shown in Fig. 2.) The terminals for the regulated voltages are located between the two sockets, and the meter can be switched between the two variable supplies. A slide switch at the bottom of the front panel allows the supplies to be set before they are applied to the breadboarded circuit.

Fairchild's 7800-series voltage regulators are recommended for this application because they are compact, easy to use, and can handle almost all the power requirements needed by this type of breadboard. Moreover, the internal overload protection of the regulators is excellent for breadboard purposes.

Naturally, the number and nature of the regulated voltages should satisfy the user's most frequent requirements. Similarly, the type of input and output connectors, the size and location of the panel holes, and the number of sockets depend on specific needs.

2. Super breadboard. A choice of regulated supply voltages gives the breadboard additional flexibility. Here the supply circuit shown is housed in the bottom minibox. The supply provides fixed ±5-volt outputs and variable (from ±9 to ±18 v) outputs with a meter readout.

### Laminated bus strips ease pc-board layout

by Ray Jodoin Rogers Corp., Chandler, Ariz.

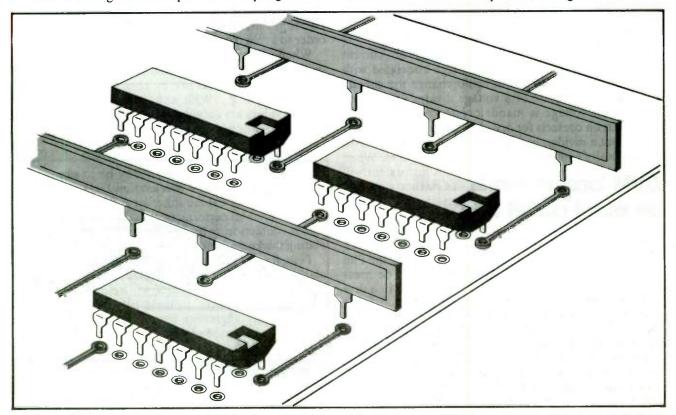

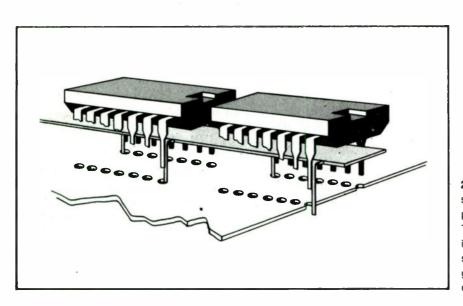

Laminated pc-board bus bars can increase the effective ground-plane area of any two-sided printed-circuitboard layout and reduce layout time for the circuit. Two basic types of these bus bars are vertical bus strips (one, two, or three layers) that mount between rows of integrated circuits, and under-the-DIP strips (two or three layers) that mount underneath every IC in a row. Both of these types (shown in the figures) are sold commercially in standard lengths.

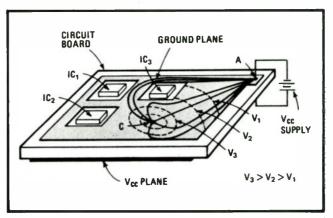

In the layout of a two-sided circuit board, one side is normally dedicated to the ground plane, and the other side is used for logic interconnections and voltage distribution. The use of a ground plane with any high-speed system is desirable for several reasons. Because the ground plane provides a low-inductance path for supply currents, it helps minimize noise on the power supply lines. Also, since this configuration of the pc board minimizes the signal-line impedance, coupling that results in cross talk is decreased. Moreover, a ground plane allows signal lines to have a constant characteristic impedance so that termination techniques can be used to eliminate ringing.

With today's complex integrated circuits, however, it is difficult to accommodate both signals and voltage lines within the confines of a single layer; therefore, the ground plane is sometimes broken up, and short signal lines, crossovers, and voltage bus are put on the groundplane side of the board. As much as 40% of the groundplane side of the board can be used for signal lines, but isolation of large areas of the ground plane must be avoided to prevent "current crowding" and inductive problems.

To further conserve space on the board, power can be distributed by the laminated bus bars. By this technique a large area of board is freed for line layout, and routing of lines becomes less complex.

Of course, a ground plane is easily maintained by using multilayer pc boards, although this approach is inevitably more costly and slower to implement than a system that utilizes a two-sided board. But the use of bus bars offers several other advantages over the multilayer approach:

Vertical bus strips act as board stiffeners, often eliminating the need for separate mechanical stiffeners.

Under-the-DIP bus strips offer a large thermal mass

1. Off-boarding the bus. Laminated insulated bus bars save space and simplify layout on printed-circuit boards. Vertical bus strips shown here mount between rows of integrated circuits and have extra advantage of serving as board stiffeners.

#### **World Radio History**

2. Under-the-DIPs. Laminated bus-bar strips that mount directly under the IC also provide large thermal mass for heat-sinking. These off-the-board buses, like those shown in Fig. 1, are available in a variety of sizes, shapes, and numbers of layers. They are of greatest importance in compact high-speed circuits such as those using ECL ICs.

and act as heat sinks for the integrated circuits.

• Distributed capacitance of up to 1,800 picofarads per square inch of bus-conductor area is attainable, thereby reducing significantly the number of bypass capacitors required for filtering out high-frequency noise.

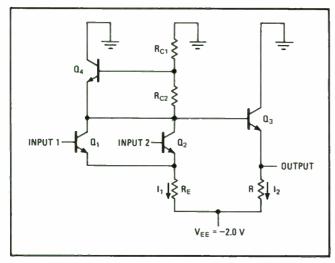

Today's high data rates and fast switching characteristics make these advantages even more important when emitter-coupled-logic ICs are used. Two-sided boards are definitely compatible with ECL systems if proper design rules are followed. An ECL system performs best in a terminated-transmission-line environment. This requires the use of a -2.0-volt termination supply ( $V_{TT}$ ) in addition to the -5.2-V V<sub>EE</sub> supply. Both voltages can be distributed on the printed-circuit board by laminated bus bars.

Series 10,000 ECL can be used with or without a ground plane. When there is no ground plane, the  $V_{CC}$

bus line must be a minimum of 0.1 inch wide per row of packages and should be pinned out to several connector pins if an edge connector is used.  $V_{EE}$  should be bused to pin 8 of each device (pin 12 of a 24-pin package). Each device should be bypassed between  $V_{CC}$  and  $V_{EE}$  with a low-inductance 0.01-microfarad capacitor. To minimize ringing, logic-line interconnects should not be longer than 6 inches.

When a ground plane is used, it should be pinned to every seventh connector of the edge connector (if any).  $V_{EE}$  should be bused to pin 8 of each device (pin 12 of a 24-pin package). A low-inductance  $0.01-\mu F$  bypass capacitor should be provided for every two to six devices. Keep logic line interconnects to six inches or less for unterminated lines. A 510-ohm resistor to the  $V_{EE}$  bus should be used. For best results, eliminate ringing with a terminated -2-V transmission-line system.

### DVM locates short circuit on wired circuit board

by Richard A. Rosner Perkin-Elmer Corp., Danbury, Conn.

A microvoltmeter or digital voltmeter can be a great time saver in finding a short circuit on a circuit board that is wired with a large number of integrated circuits and bypass capacitors. The situation arises when the engineer sets his bench power supply to the proper  $V_{\rm CC}$ voltage, plugs in the board, and watches the voltmeter drop to zero while the ammeter reads full current at the current-limiter value—the  $V_{\rm CC}$  supply is shorted to ground.

If visual inspection does not reveal the short and none

1. Short subject. A short circuit between the power and ground planes at point C causes currents to flow along the ground plane to point A. Since equipotentials have highest values near point C, a probe that measures voltages on the ground plane relative to point A indicates the location of the short.

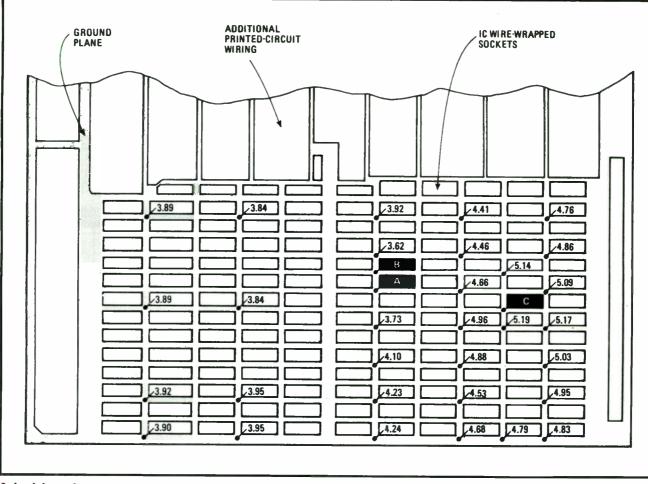

2. Look here. On this circuit card, signals are carried by 600 wrapped wires above the ground-plane side of the board. A short circuit from an IC pin to the ground plane at point C was located by measuring ground-plane voltages (shown in millivolts) relative to the negative supply connection at point A. The positive side of the supply is connected to the power plane below point B.

of the ICs feels hot to the touch, measurement of the potential between the power-supply ground connection and other points on the ground plane will indicate the location of the short-circuit point in a few minutes.

This technique is effective because a potential difference of several millivolts can exist from one end of the ground plane to the other as current flows through it. If current enters the ground plane at the location of the short circuit and leaves at the power-supply return, as shown in Fig. 1, the voltage difference is greatest between these two points.

Figure 2 shows the voltages measured at several points on part of a shorted board. The short turned out to have been caused by a 0.5-millimeter ball of solder splatter that was held in place (and out of view) by a bundle of wires.

### Liquid crystals isolate electrical short circuits

by Roger Anderson Honeywell Information Systems, San Liego, Calif.

Isolating a short circuit on a circuit board or back panel is relatively simple when only single-circuit paths are involved. But it grows progressively more difficult as the number of common voltage and ground paths is increased.

Surprisingly, encapsulated liquid crystals can greatly simplify finding short circuits in this situation. Besides saving money and parts, testing with liquid crystals can also significantly reduce trouble-shooting time. Other techniques for isolating electrical shorts call for unsoldering or clipping component leads, or increasing the current through the unit being tested until a hot spot or smoke is detected.

Sheets of encapsulated liquid crystals have been used successfully to detect: solder bridges on printed-circuit and wire-wrapped boards; wire shorts on wire-wrapped boards and back panels; internal shorts of such components as capacitors and delay lines; and internal shorts on multilayer boards from a pin to an etch, from a pin to a voltage or ground bus, and from one etch to another etch. Encapsulated liquid crystals can also be used for detecting shorts in cables or harnesses, or wherever multiple- or common-circuit paths exist.

Liquid crystals are usually derivatives of cholesterol that exhibit the mechanical properties of a liquid and certain optical properties of a solid. They have a rather unusual characteristic—the capacity to reflect different wavelengths of light with variations in temperature so that they visibly change color. Liquid crystals have a reproducible color range within specified temperature limits.

Since the colors are derived from scattered incident light, they are most visible when observed against a dark background, like black ink. The black ink can absorb any light transmitted through the liquid crystals and allows the selectively (determined by temperature) reflected light to be viewed.

Encapsulated liquid crystals can be supplied as Mylar sheets, and the colors can be seen through the Mylar.

(The capsules containing the liquid crystals are actually too small, between 20 and 40 micrometers in diameter, to be seen with the naked eye.)

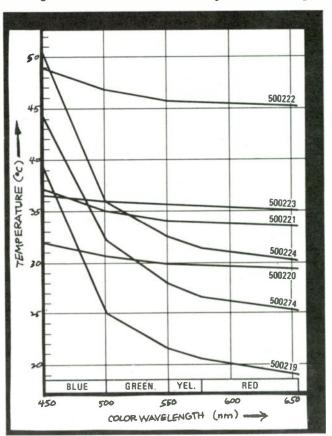

The sheets have very definite temperature and color ranges, as shown by the graph in the figure. These particular sheets can be bought from Edmund Scientific Co., Barrington, N.J.

All the liquid-crystal sheets exhibit the total spectrum of colors as temperature changes. Blue colors are associated with warmer temperatures, reds with cooler. Because the colors result from scattered (reflected) incident light, they will be more intense if a bright light source is used. The number 500274 sheet is best for indicating electrical shorts because it produces a bright

Sample lot. Every sheet of encapsulated liquid crystals has its own color response over a given temperature range. The sheets shown here are sold by Edmund Scientific. The one numbered 500274 is a good choice for isolating electrical short circuits.

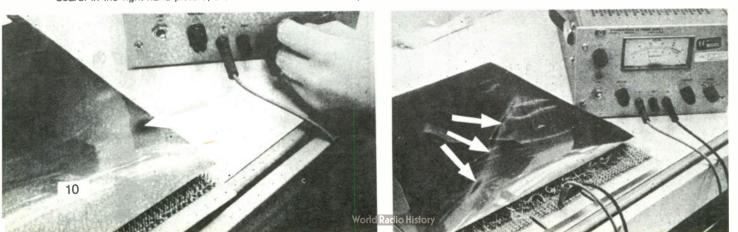

Making shorts colorful. In left photo, a bright blue spot of the liquid-crystal sheet pinpoints a shorted capacitor on a wire-wrapped circuit board. In the right-hand picture, a shorted wire traces its own path as a blue streak of color across the liquid crystals.

blue spot that shows up well against a dark brown background at the start.

The liquid-crystal sheet must be placed directly on the circuit under test. The closer the liquid crystals are to the faulty part, the more readily the short will be detected. To locate faults in hard-to-reach places, the sheet can be cut into narrow strips that are laid directly on the suspect components.

By carefully controlling the amount of current applied to the circuit, it's possible to locate the short without damaging wires or good components. The current flow is concentrated through the shorted device and/or

### Current tests ensure IC-package orientation

by Sylvan E. Shulman Hughes Aircraft Co., Fullerton, Calil

The symmetry of integrated-circuit packages makes it all too easy to orient them incorrectly in fixtures of automated testing systems or on circuit boards. Even though dual in-line packages may accidentally be rotated 180° from their correct mounting positions and flat-packs may be rotated or flipped over, they may fit into a jig or board. Such misalignments cost time and money to trouble-shoot and rework, but faulty orientation of most transistor-transistor-logic circuits can be detected routinely by a nondestructive automated measurement.

These measurements are important because, at incoming inspection, the IC packages are loaded into a chute that feeds them to an automatic tester. If the package emerges in the wrong position, voltages applied to the wrong terminals cause wrong results and may damage the IC.

To realize the importance of testing a stuffed board,

path, and the liquid-crystal sheet changes color precisely at the location of the short because of the heat the short generates, as shown by the left photograph.

As little as 12 milliwatts of dissipated power at a shorted junction will cause a color change in the sheet. The greater the current that can be safely applied, the easier it will be to find the short because of the increased heat generated. Even a shorted wire on a back panel is generally easy to identify, since its position is traced in color across the entire sheet, as the other photograph indicates. Special care should be taken not to exceed the rated current capacities of the wires.

it's only necessary to remember that the possibility of an insertion error on a board rises exponentially with the number of ICs. If a board contains 40 ICs and the insertion error per IC is 1%, then the yield of good boards is  $(99\%)^{40}$ , or 66.8%. Therefore 33.2% of the boards contain an incorrectly inserted IC.

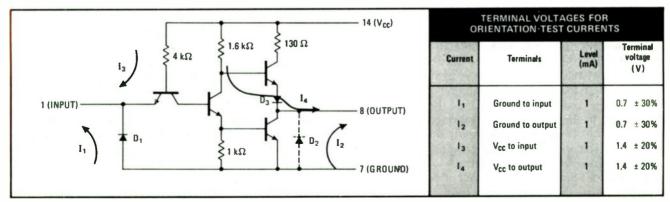

The technique for measuring IC orientation is based on the current paths furnished by the input clamp diode in more than 95% of all TTL circuits or the substrate diode between every transistor collector and ground. These diodes are shown as  $D_1$  and  $D_2$  in the typical TTL gate of Fig. 1. They can carry currents of not more than 100 milliamperes.

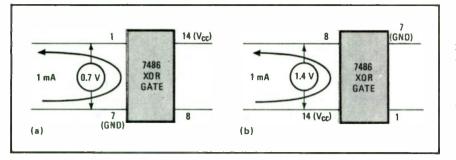

In Fig. 1, the integrated-circuit gate is not connected to any power supplies except a constant-current source. If the current source drives a 1-milliampere current through the IC from the ground terminal to an input terminal such as terminal 1, the voltage drop across those terminals is about 0.7 volt. This ground-to-input current flows through clamp diode  $D_1$  and is shown as  $I_1$  in Fig. 1. Similarly, if 1 milliampere is driven through the IC from the ground terminal to an output port, the voltage across the terminals is about the same. This current flows through the substrate diode  $D_2$  and is  $I_2$  in Fig. 1.

By contrast, if the constant-current source is connected to drive 1 milliampere from the  $V_{CC}$  terminal to the input, that current,  $I_3$ , flows through a silicon-diffused re-

**1. Current situation.** Current flow from supply terminal to input or output terminal of a typical TTL gate produces a voltage that is different from the voltage that is produced when current flows from ground to input or output, and this difference can be used to check IC orientation. The forward voltage drop across a base-to-emitter junction is about 0.7 volt; across a diode, it is about 0.55 V; and across a diffused resistor, it depends on current. One milliampere through the 4-k $\Omega$  resistor produces 0.7 V, but through the 1.6-k $\Omega$  resistor, 1 mA produces only 0.1 V.

#### World Radio History

2. Single IC. Test set sends 1-mA current through left-corner terminals and monitors resulting voltage. If IC is positioned correctly, as at (a), terminal voltage is in range 0.49–0.91 V. If IC is incorrectly positioned, as at (b), the range is 1.12–1.68 V, so test station ejects unit without applying possibly damaging test voltages.

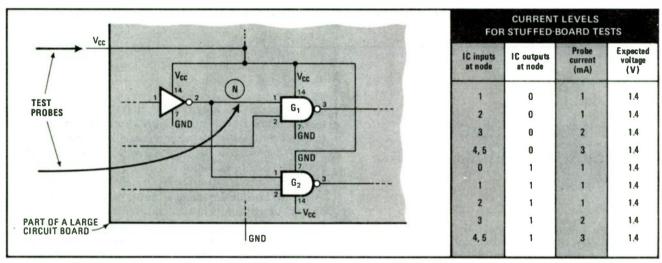

3. Stuffed board. To check orientation of IC mounted on circuit board, probes connect current source to  $V_{CC}$  terminal of board and to any node on the board. Voltage across probes is 1.4 V (±20%) if all packages are mounted properly. A lower voltage indicates that some IC is turned around or upside down—here, gate G<sub>2</sub> has its ground pin where its  $V_{CC}$  pin should be, so voltage at probes is only 0.7 V. Table shows current-source levels that should be used in testing orientation of standard TTL integrated circuits; high-power TTL requires more current.

sistor as well as a base-to-emitter junction. Although the diffused resistor is labeled as 4 kilohms in the circuit diagram, its resistance is strongly dependent on the current level. At 1 mA, the drop across the resistor is about 0.7 v; this value is added to the 0.7-V drop through the baseemitter junction to make the voltage between the  $V_{CC}$  and input terminals about 1.4 v.

Likewise, if the current  $I_4$  from the V<sub>CC</sub> terminal to an output terminal is 1 mA, the voltage across the terminals is again about 1.4 v. In this case, the drop across the diffused resistor is on the order of 0.1 v. The baseemitter drop and diode drop add up to 1.3 v. (All of these voltage values are experimental results.)

For incoming inspection of ICs, when a unit slides out of the loading chute into an automated test fixture, the orientation of the package can be checked as shown in Fig. 2. The 1-mA current source is connected between the lower left terminal and the upper left terminal of the package, and the voltage across these terminals is measured. If the package is positioned properly, the current flow is from ground to input, and the voltage is 0.7 v. The test station can then power up the chip and measure performance characteristics.

If the IC has been loaded  $180^{\circ}$  out of position, the current flows from the power-supply terminal to an output, and the voltage is 1.4 v. When this too-high voltage is sensed, the tester ejects the IC into a bin for reloading.

A similar sort of test can ensure correct orientation of all the ICs mounted on a circuit board. The test fixture for this stuffed-board test must be a bed-of-nails arrangement that makes contact with every circuit node on the board. No power is applied to the board except a current source that drives current from the common  $V_{CC}$  terminal to one or another node. The amount of current that the source must supply depends on how many inputs and/or outputs are connected to that node, as listed in the table of Fig. 3. The tabulated values are for conventional TTL ICs; high-power TTL requires larger currents. Correct orientations produce 1.4 v across the current-source terminals; if a package is misoriented so that current flows into its ground pin, the voltage is only 0.7 v.

Figure 3 shows a portion of a circuit board that contains a number of ICs, with the current source connected between  $V_{CC}$  and node N. This node connects one output and two inputs, so the test current is 1 mA in accordance with the table, and the voltage drop from the  $V_{CC}$ terminal to node N should be 1.4 v. However, gate 2 has been mounted incorrectly, with its ground pin and supply pins reversed. In this position, current flows from ground to the node, the voltage is only 0.7 v, and the go/no-go tester rejects the board.

Although the discussion here has been limited to TTL devices, the testing technique is also applicable to metal-oxide-semiconductor devices.

### Make your own small switches for pc boards

by Ralph Wilbur West Engineering Co., Santa Monica, Calif.

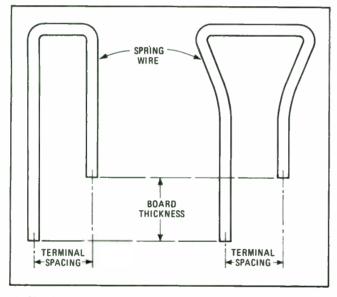

Testing and troubleshooting both breadboard and production circuit boards can often be simplified by permanently installing good-quality switches on the boards at strategic locations. Such switches, inexpensive and simple to make, take up little room on the boards. To build them, you'll need only a few standard terminals and a piece of spring wire.

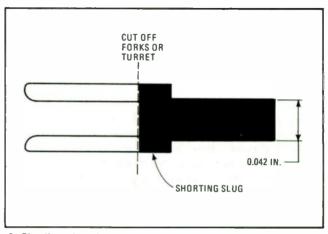

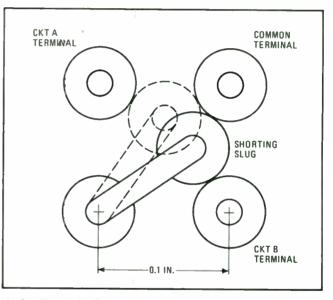

A single-pole double-throw switch is constructed on prepunched or drilled circuit board by using five standard hollow gold-plated staked terminals and a section of spring wire. Four of the terminals are arranged in a square (say, 0.042-inch centers) and staked to a board. A piece of spring wire is then bent into an appropriate loop (see Fig. 1). A fifth terminal is trimmed to the base, as shown in Fig. 2, and sleeved over the short end of the spring wire. The long end of the wire is then inserted into one of the staked terminals and soldered into

**1. Shaping up.** The shape of the spring wire is less important than the terminal-spacing and board-thickness dimensions.

place. This becomes the shorting slug.

The result of all this is a movable shorting slug spring-loaded against two other adjacent terminal bases. Twisting or pushing the wire loop causes the shorting slug to snap into the detent formed by the other adjacent terminal base (Fig. 3). Connections can be made from either side of the board to wire or etched connectors.

2. Shorting slug. Any type of hollow terminal will do, since only the bottom is used; gold plating stands up guite well.

3. Small switch. Pushing the spring-loaded wire loop moves the shorting slug from one set of terminals to the other set.

### Estimating substrate area and density for hybrid microcircuits

by Lyle F. Pittroff Helipot Division, Beckman Instruments Inc., Fullerton, Calif.

When converting discrete circuits to their hybrid counterparts, the engineer usually must face either of two basic questions: how much substrate area will be needed to accommodate the circuits, or will it fit when the package and circuit designs have been finalized before the inquiry or layout-design phase? What's needed is a shortcut technique for easily estimating substrate area and determining component density so that at least you know you're in the right ball park. A technique that Beckman Instruments calls the unit system not only answers these questions, but, in addition, provides a yardstick for estimating yield factors in high-density applications.

The unit system consists of assigning a number of units of area to each circuit component and then adding up the total number of units to determine the required area. One unit is defined as the substrate area required for one general-purpose, thick-film resistor, rated at 100 milliwatts after trimming to  $\pm 2\%$  tolerance. The table shows the number of units normally allocated for other types of conventional circuit elements. In each case, the number of units specified includes whatever additional area is required for terminations, resistor trimming, wire-bonding pads, and spacing between adjacent components.

If the circuit has been defined, but the package has not been chosen, the substrate area can be estimated. Start with an optimum one-unit resistor area of 0.015 square inches. Assign the proper number of units to each component in the circuit, according to the table, and total the number of units for the circuit. Determine the substrate area required as follows:

$A_s = (0.015 \text{ in.}^2) \tilde{U}_T$

where  $A_s$  is the required substrate area, and  $U_T$  is the total number of units. A potential package choice, based on available substrate area, can then be made from the many different styles available.

When the circuit and package designs are both firm, the component density in square inches per unit can be estimated. Add up the total number of units for the circuit, according to the table. Determine the available substrate area in the package size you intend to use. Calculate the component density as follows:

$D = A_s/U_T$

A component density of 0.015 in.<sup>2</sup>/unit is considered a moderate density level if the supplier of your final package has the freedom to make pin assignments. Using more specialized fine-line screening techniques, densities to 0.006 in.<sup>2</sup>/unit have been achieved. Note that component density is appraised in area per unit, instead of units per area. Area per unit is more directly correlated to layout dimensioning.

Some components require special consideration because of their large size or an unusually large number of leads. Since the unit system is strictly a shortcut method, a considerable amount of good judgment and common sense must be applied. The following general guidelines should be considered:

• It may be easier to deduct the area required for large capacitor chips before applying the unit system.

• High component densities are easier to achieve in smaller packages because of proximity to pins.

• Some circuits naturally flow from input to output without complex feedback interconnections.

■ Packaging efficiency is usually greater in larger hybrid packages, but yield and testing help set the limit.

| Component type                                                                             | Units per<br>component |

|--------------------------------------------------------------------------------------------|------------------------|

| RESISTORS (CERMET, THICK FILM)                                                             |                        |

| General purpose (up to 100 mW) .<br>Precision, ratio tracking<br>aspect ratio < 4:1, < ±1% |                        |

| CAPACITORS                                                                                 |                        |

| Screened (cermet)<br>Chip capacitors 0.1" x 0.1"                                           |                        |

| DIODES, PASSIVATED CHIP                                                                    |                        |

| Signal/switching                                                                           | 0.5 units              |

| Zener/reference                                                                            | 0.5 units              |

| Schottky/hot carrier                                                                       | 0.5 units              |

| TRANSISTORS, PASSIVATED CHIP                                                               |                        |

| Bipolar small signal                                                                       | 0.5 units              |

| Bipolar low/medium power                                                                   | 1.0 units              |

| JFET                                                                                       | 0.5 units              |

| INTEGRATED CIRCUITS, PASSIVATED                                                            |                        |

| Linear (741, 710, 107, etc.)                                                               | 2.0 units              |

| Digital (935, 946, 7400, etc.)                                                             | 4.0 units              |

| MOS arrays (3101, etc.)                                                                    |                        |

| MSI devices (74145, etc.)                                                                  | 0.5 units/lead         |

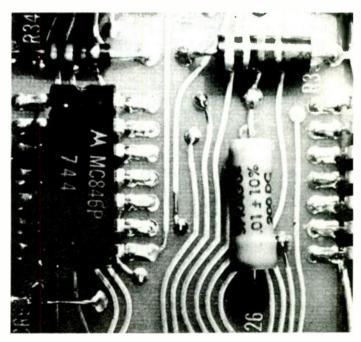

## Hand-soldering DIP circuits can save testing dollars

by William Mansfield and Herbert Perkins Datatron Inc., Santa Ana, Calif.

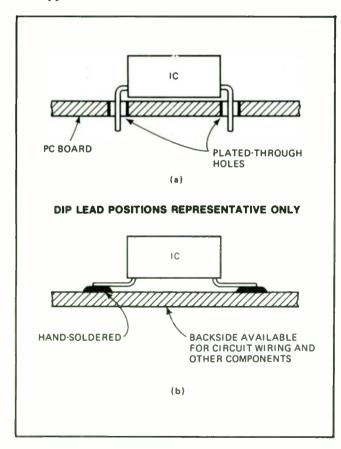

Nowadays, integrated circuits are frequently mounted on printed-circuit boards by dropping their leads through plated-through holes and then flow-soldering. Although this method may yield the shortest assembly time, it is not necessarily the least expensive because the costs of product inspection and production testing can run high. Also, isolating faults on defective devices is extremely difficult, and removing installed devices risks the possibility of damage to both part and board.

Surprisingly, a return to hand-soldering leads on only one side of the board can mean substantial savings in nonrecurring engineering costs, as well as the costs of inspection and production testing. Since most ICs are supplied in dual-in-line packages, device leads can simply be bent away from the DIP body by 90°, so that the resulting flattened package can be easily attached to the board, as shown in the figure.

Abandoning plated-through holes, moreover, releases the opposite side of the board for other circuit func-

tions. All the real estate on the bottom becomes available for circuit paths, permitting increased density of both wiring and components. This additional real estate also enhances reliability because wider line spacing can be employed to reduce the likelihood of solder bridging.

The cost penalty of hand-soldering a board containing 50 ICs—an increase in assembly time of approximately 15 minutes—can be offset by a saving of about \$1.75 a board that results from fewer plated-through holes. And because layouts are more flexible, charges for engineering time can be cut by as much as 30%.

All IC leads are easily accessible for probing so that production testing and debugging is simpler. And any single IC lead can be unsoldered and lifted for fault isolation. With plated-through holes, removing an IC from the board risks debarrelled holes and raised wiring. Since repair is often unsuccessful, and the entire board must be scrapped, losses can run as high as \$500 to \$1,000 for a single ruined board. The savings from avoiding a scrapped board offset the cost penalty for hand-soldering some 100 boards.

Furthermore, plated-through holes are the historically weak link in the soldering operation, since they can introduce contaminants or open up during thermal cycling. Hand-soldering avoids these difficulties, in addition to providing a secure mechanical connection that can withstand the stress of exposure to shock, vibration, and direct pull.

Hand-soldering has advantages. Plated-through holes (a) require space on both sides of printed-circuit board and make fault isolation difficult. By bending IC leads and hand-soldering (as in b), back of board becomes free for other circuit wiring, and single lead is easily unsoldered for testing. (Photo shows some mounted devices.) Cost penalty of hand-soldering is offset by savings in other operations.

## Evaluating power dissipation in microcircuit design

#### by Lyle F. Pittroff

Microcircuit Operations, Helipot Div., Beckman Instruments, Fullerton, Calif.

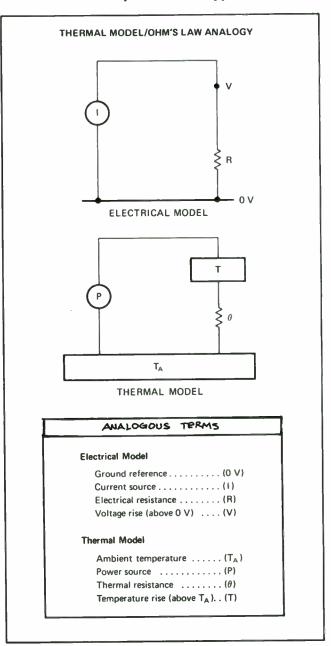

Converting a circuit from the discrete-component concept into a single miniaturized microcircuit is analagous to the design and development of a larger system. Although specific design problems must be handled on an individual basis, several key areas must be considered early in the game.

This Engineer's notebook covers package-temperature rise, component ratings, and component compatibility; a later notebook will focus on a shortcut technique for estimating the substrate area required for any given circuit. This latter article will also discuss component density and hopefully answer the question, "Will it fit?" when circuit designs have been finalized.

Microcircuits shrink the package size, but package power remains the same, and the power density can be increased significantly. An estimate of the temperature rise in a new microcircuit design can be a critical step in the package-selection process. Two specific areas must be evaluated:

• Substrate/package temperature rise above the ambient or heat-sink maximum operating temperature.

Individual component/junction temperature rise above the substrate/package temperature.

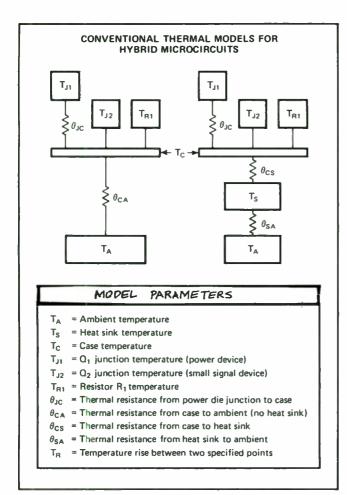

A simple review of the thermal model for the package and those components dissipating significant power will quickly reveal whether or not the design is in the right ball park for most hybrid-circuit configurations. With the fundamental thermal model shown in the first figure, a steady-state Ohm's law network analogy can be used to evaluate component temperature rise.

For the initial approximation, transistors and diodes dissipating less than 100 milliwatts, resistors, and most ICs are assumed to be operating at the case temperature. It is also assumed that all of the heat generated by internal circuit elements is being conducted away by the case (there is no radiant energy).

Conventional thermal model designations for a hybrid microcircuit are outlined in the second figure. The package temperature rise is a function of the total power dissipation ( $P_T$ ) of all internal circuit elements:

$T_{R} = T_{C} - T_{A} = P_{T}\Theta_{CA}$

where  $T_R$  is the temperature rise between two specified points,  $T_C$  is the case temperature,  $T_A$  is ambient temperature, and  $\Theta_{CA}$  is the thermal resistance from the case to ambient without a heat sink.

As a rule of thumb, the thermal resistance,  $\Theta_{CA}$ , of a package in free air (no forced cooling and minimum pin conduction) causes a temperature rise of about 35°C per watt of power dissipation per square inch of package

area  $(35^{\circ}C/w/in.^2)$ . For example, the temperature of a circuit dissipating 1 w would rise approximately  $35^{\circ}C$  above ambient in a 1-inch-square package or  $70^{\circ}C$  above ambient in half that package area. This general rule is conservative and should prove a safe first approximation for most pc-board applications.

The individual component temperature rise above the substrate temperature is a function of the component's power dissipation and thermal resistance. Although significant temperature rises are usually limited to the larger devices, some typical values of chip thermal resistance for smaller semiconductors are given.

The maximum allowable junction temperature  $(T_J)$  for silicon devices depends on the application, and in

| TYPICAL SEMIC | TYPICAL SEMICONDUCTOR OHIP THERMAL RESISTANCE |                           |  |  |  |

|---------------|-----------------------------------------------|---------------------------|--|--|--|

| Category      | Typical Device Types                          | Typical $\theta_{\rm JC}$ |  |  |  |

| Small signal  | 2N2484, 2N2605                                | 150°C/W                   |  |  |  |

| Low power     | 2N2219, 2N2905                                | 60°C/W                    |  |  |  |

| Medium power  | 2N3724, 2N4030, 2N2194                        | 44°C/W                    |  |  |  |

some cases, it is limited by system specifications. The seat-of-the-pants rule is to never allow a junction to exceed 200°C in general utility applications. High-reliability applications often further limit  $T_J$  to 150°C or 175°C.

Component compatibility is yet another design consideration that must not be overlooked in building hybrid microcircuits. Realistically, it is sometimes more economical or better design practice to leave certain devices in discrete form outside of the microcircuit package. Large capacitors, for instance, as well as large power transistors and diodes, large inductive devices, and special parts head the list of discretes requiring individual attention.

To judge component compatibility, usually both performance and packaging objectives must be surveyed in the context of the over-all system. Each application imposes its own unique combination of economical, electrical, mechanical, and environmental circumstances.

Even conductors and crossovers are sometimes subject to the considerations of component compatibility. Fine-line screening techniques permit very narrow line widths to be realized, but Ohm's law still prevails and halving the line width doubles the line resistance between two points. Consequently, the layout of high-current paths and low-impedance lines may require special attention.

## Mixed dielectrics improve capacitor stability

by George Breindel Ross Laboratories Inc., Seattle, Wash.

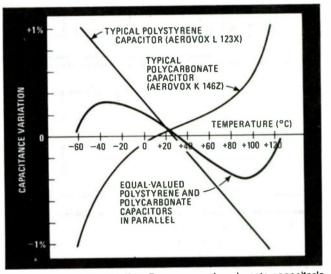

Temperature characteristics of circuits like integrators, RC-dependent timers, free-running oscillators, and many others depend directly on the temperature stability of capacitors. It's well known that the capacitance of either polycarbonate or polystyrene capacitors over a range from  $-55^{\circ}$ C to  $+125^{\circ}$ C often varies more than system specifications can tolerate. But improved stability can be achieved if a polycarbonate is used in parallel with a polystyrene.

The figure shows that a typical polycarbonate capacitor has a positive temperature coefficient and a typical polystyrene capacitor has a negative coefficient of about the same magnitude. If a 1-microfarad capacitor is needed in a long-term integrator, then a 0.47- $\mu$ F polystyrene in parallel with a 0.47- $\mu$ F polycarbonate provides greatly improved temperature stability.

A further gain in stability can sometimes be realized by carefully matching the capacitor values to the respective temperature curves. For example, if a particular polystyrene capacitor has twice the stability of a particular polycarbonate, a  $0.68-\mu$ F polystyrene can be used in parallel with a  $0.33-\mu$ F polycarbonate to get 1  $\mu$ F with a flatter temperature curve.

**Temperature compensation.** Because a polycarbonate capacitor's temperature coefficient is positive and a polystyrene capacitor's is negative, the two in parallel do better than either one alone at providing temperature stability in capacitance-dependent circuits such as RC tuners, oscillators, and integrators.

### Designing with preferred component values cuts costs

by Nathan O. Sokal Design Automation Inc., Lexington, Mass.

Designing with a minimum number of component values—so-called "preferred" values—can reduce materials and administrative costs for both manufacturing and engineering functions. The practice is no longer as common as it used to be, but it deserves to be revived now in updated form.

The accompanying tables suggest an order of preference to be followed in selecting values of resistance, inductance, capacitance, zener-diode voltage, field-effect diode current, and the like. Such components are available in sets of values that result from rounding to two (or three) digits the values obtained from  $10^{n/24}$  (or  $10^{n/96}$ ), where n ranges from zero to 23 (or 95) for each decade.

Tables 1 and 2 show the values in each of these series arranged into four columns to indicate the preferred order of component selection. Column one contains the first value and every eighth succeeding value. Column

| TABLE 1: TWO-DIGIT                                | SERIES (24 VALUES F               | ER DECADE)                        |

|---------------------------------------------------|-----------------------------------|-----------------------------------|

| 20% SERIES<br>First Second<br>Preference Preferen | 10% SERIES<br>Third<br>Preference | 5% SERIES<br>Fourth<br>Preference |

| 10                                                |                                   |                                   |

|                                                   | 12                                | 1.1                               |

|                                                   | 1.2                               | 1.3                               |

|                                                   | and the second                    | 1.6                               |

|                                                   | 1.8                               | 2.0                               |

|                                                   |                                   | 2.4                               |

|                                                   | 2.7                               | 3.0                               |

| 3.3                                               |                                   | 3.6                               |

|                                                   | 3.9                               | 4.3                               |

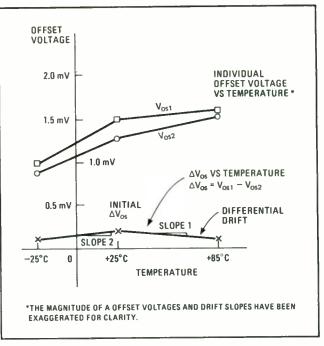

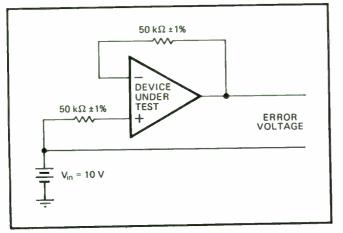

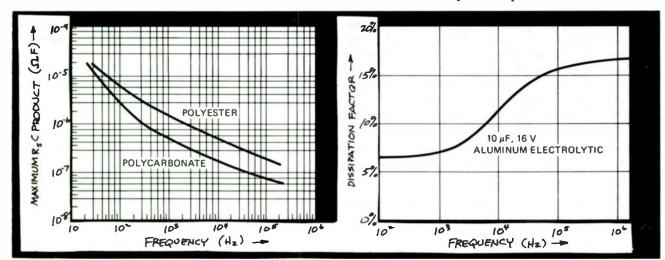

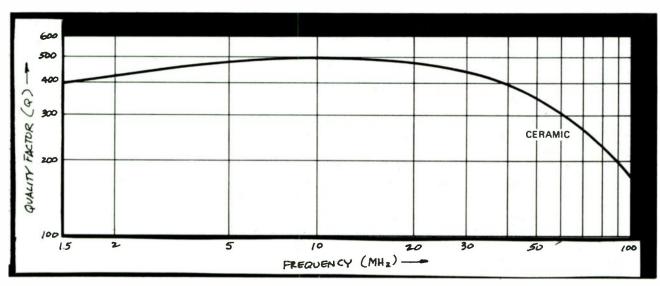

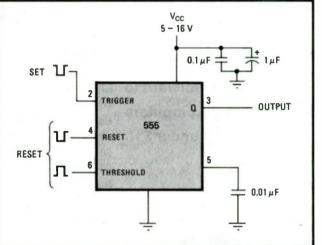

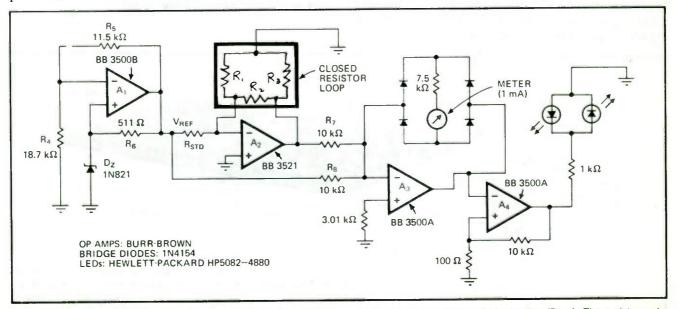

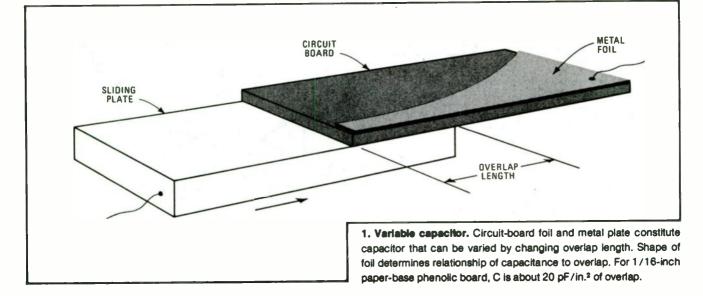

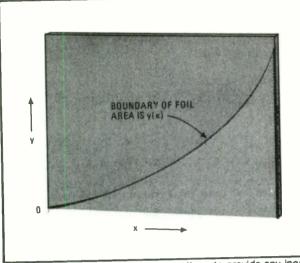

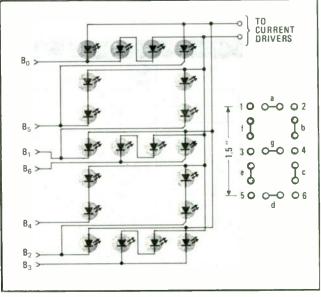

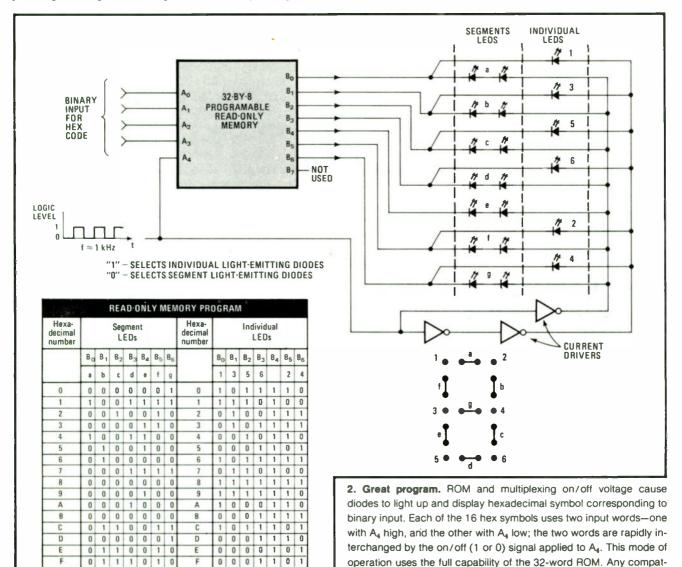

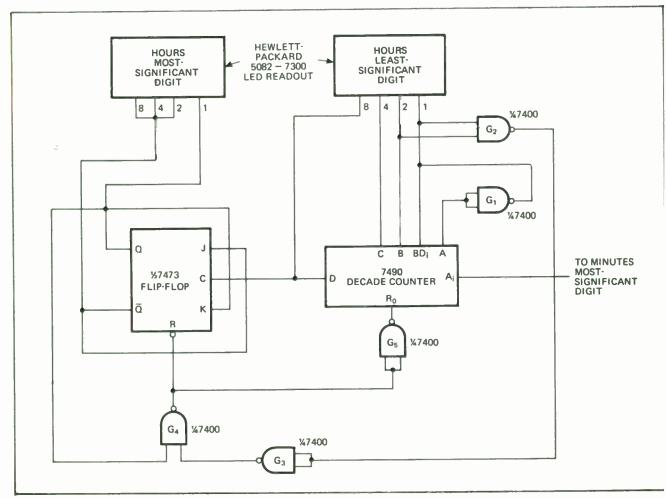

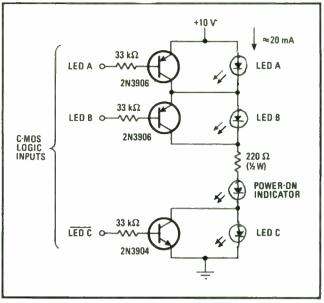

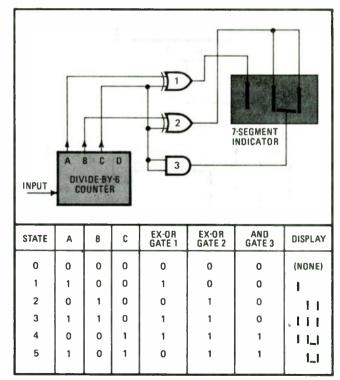

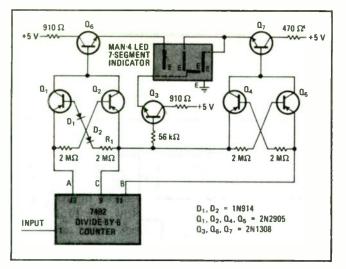

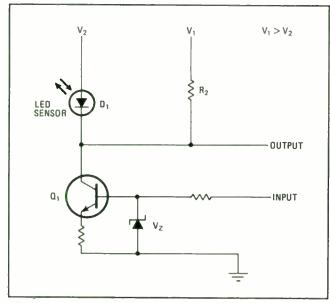

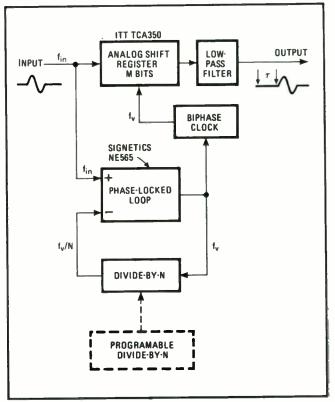

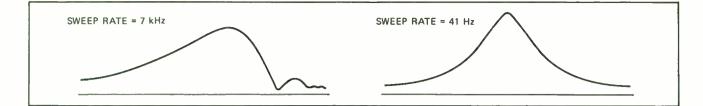

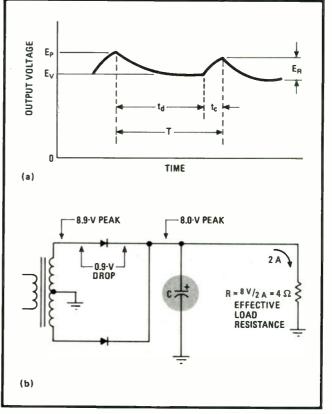

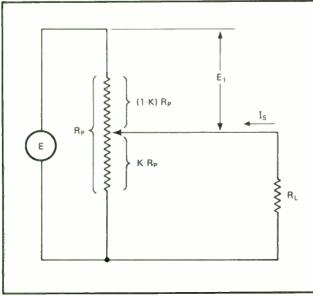

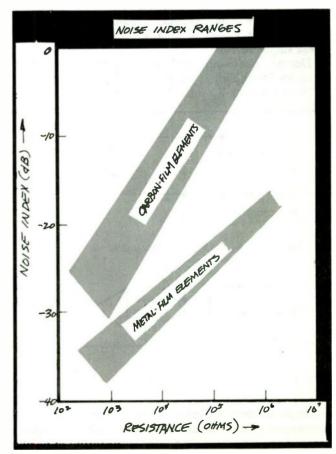

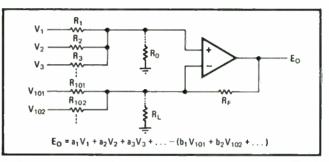

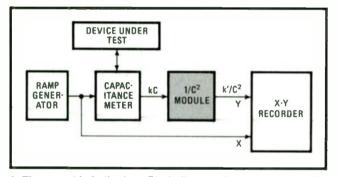

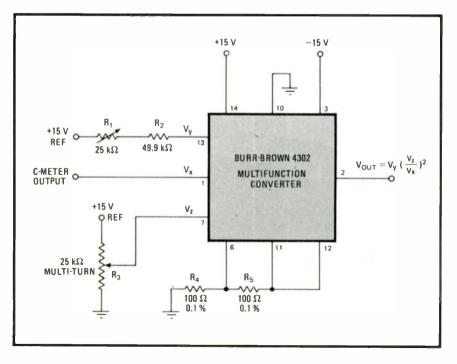

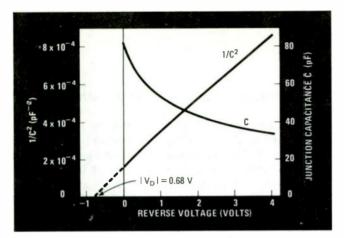

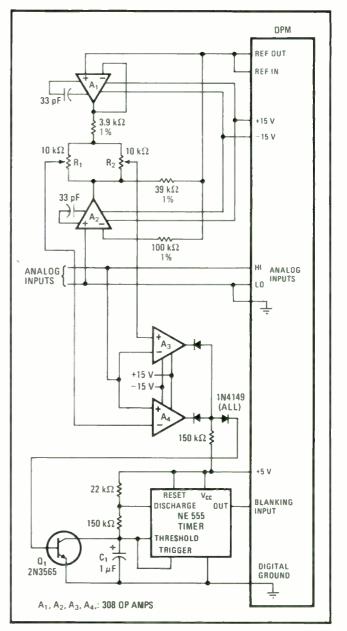

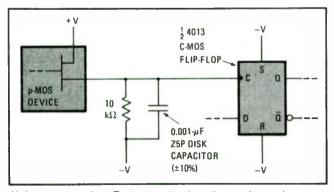

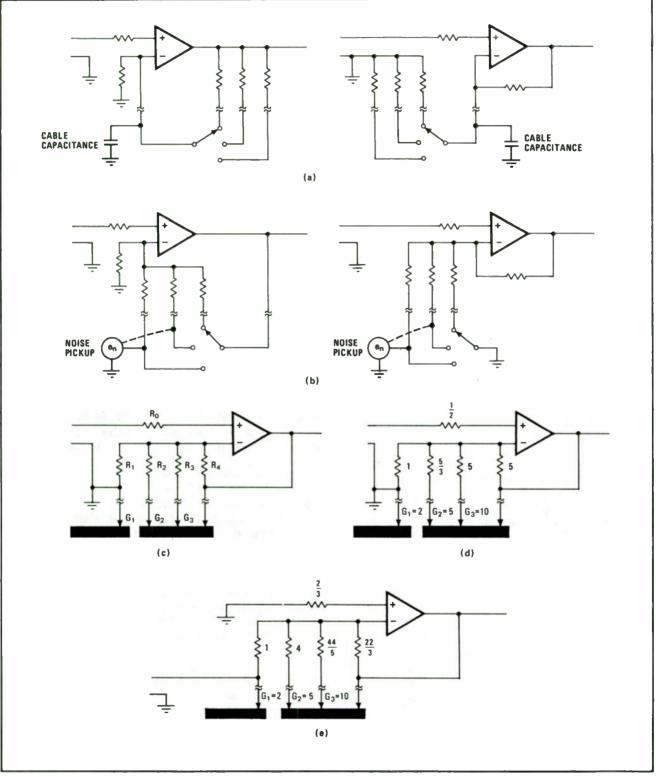

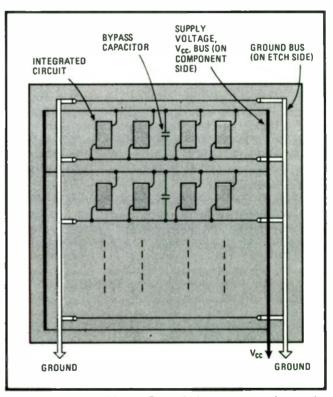

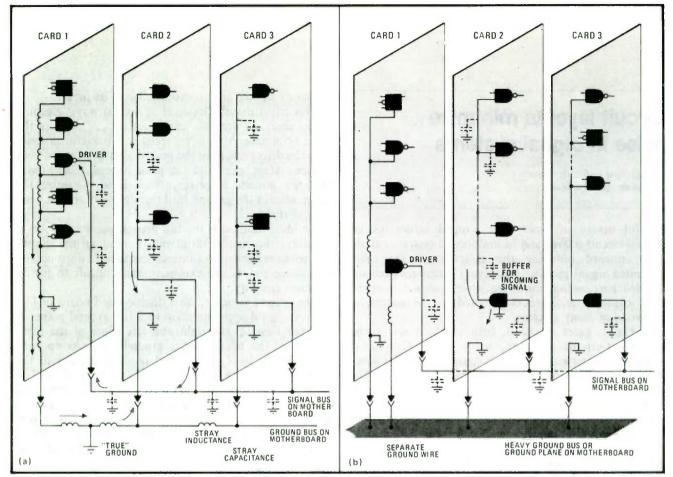

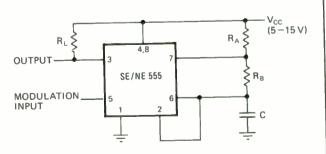

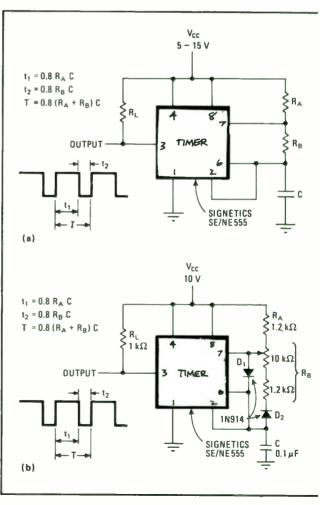

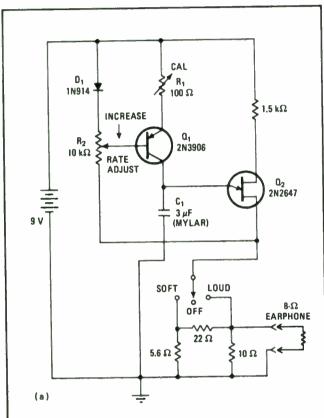

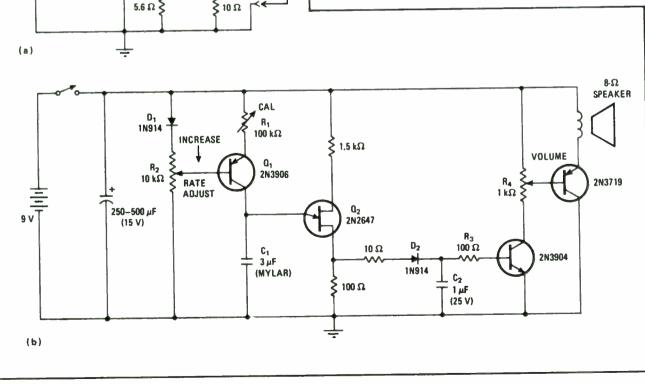

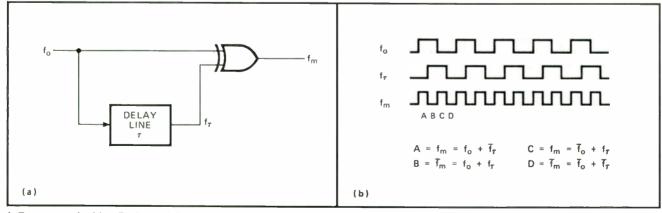

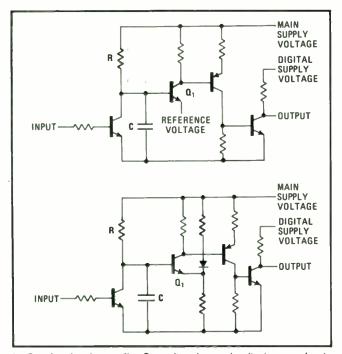

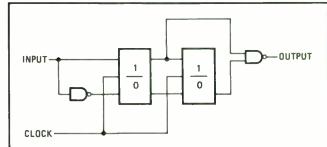

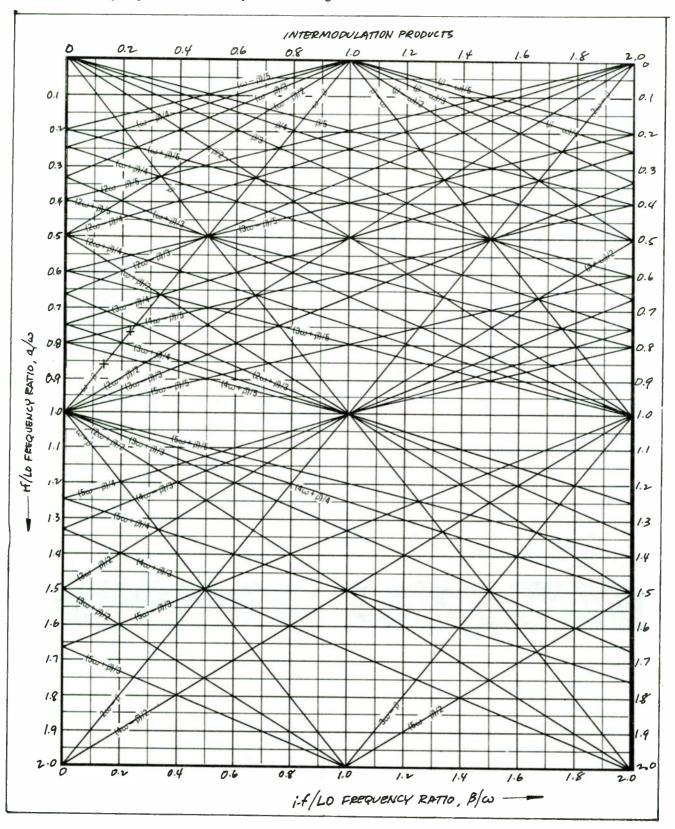

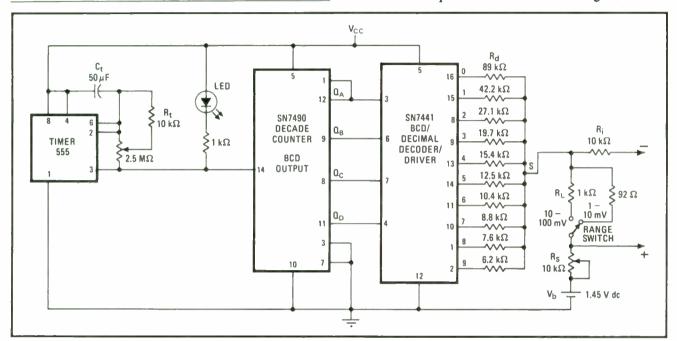

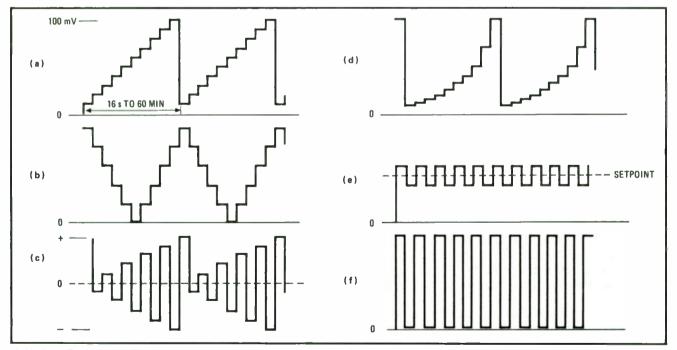

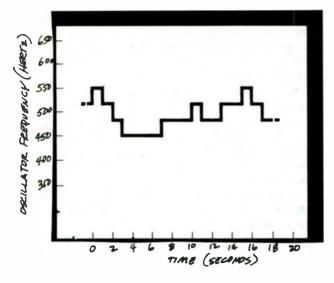

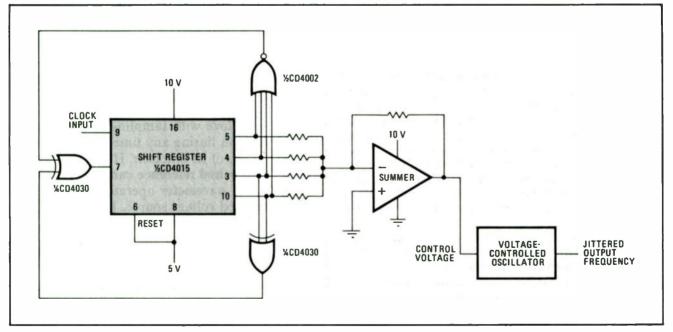

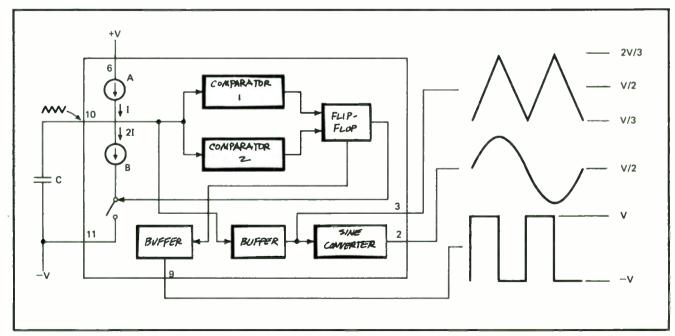

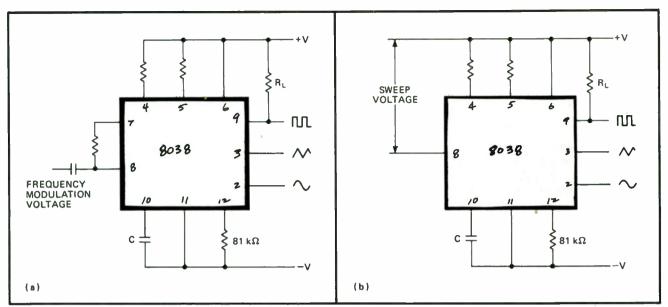

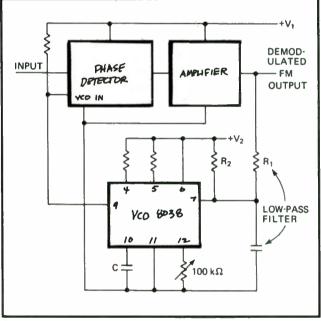

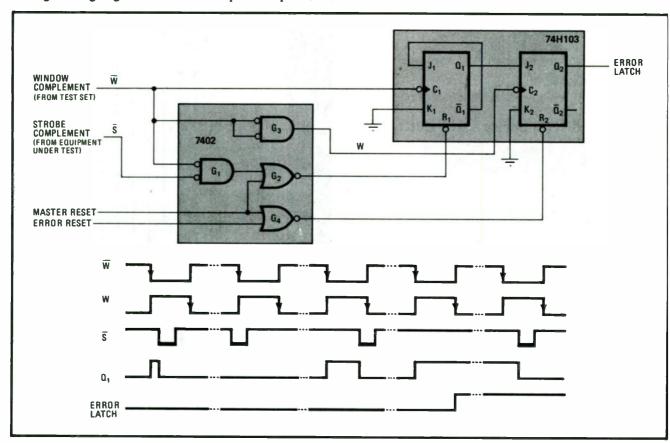

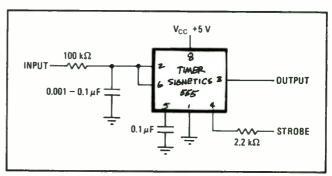

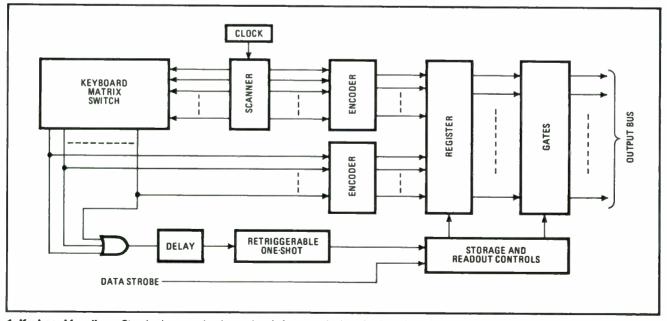

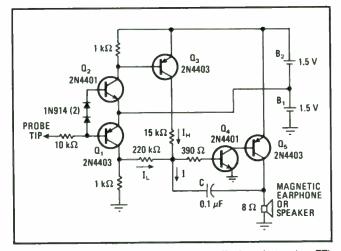

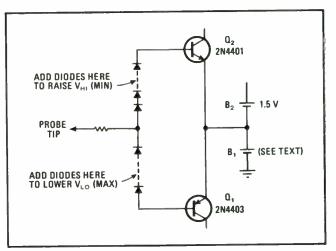

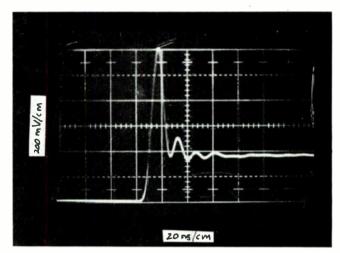

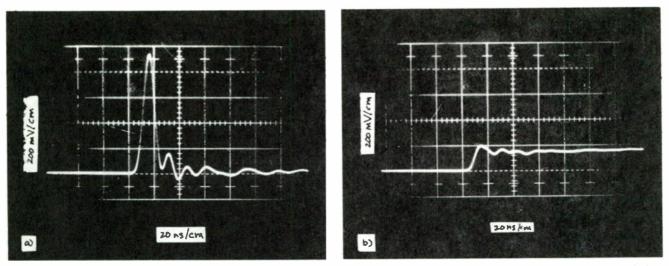

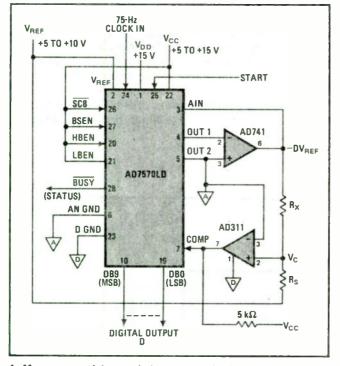

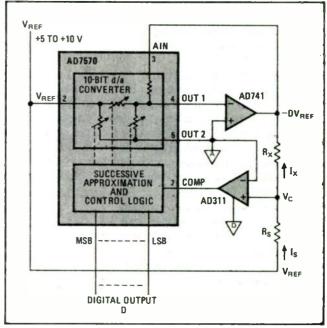

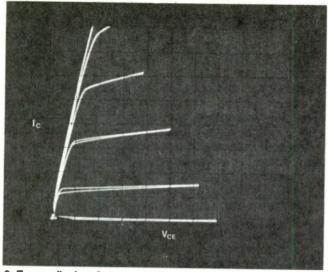

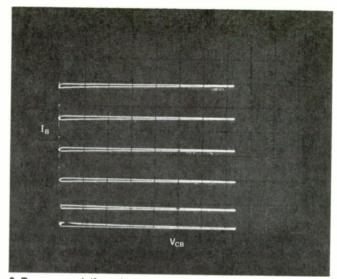

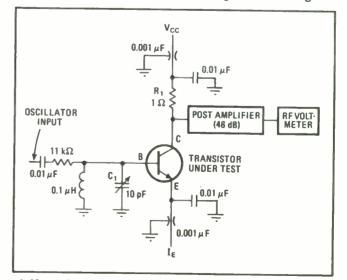

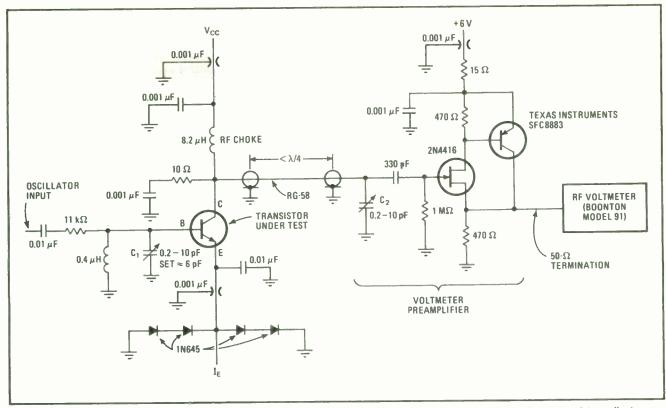

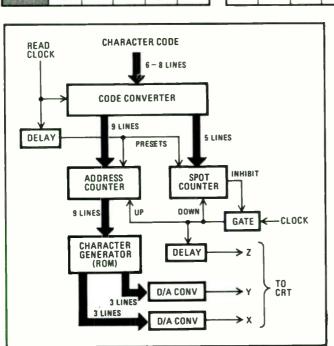

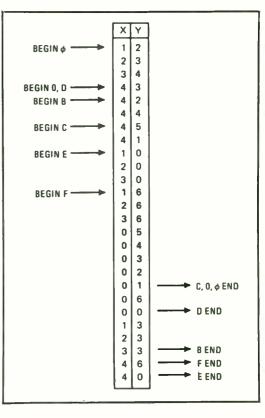

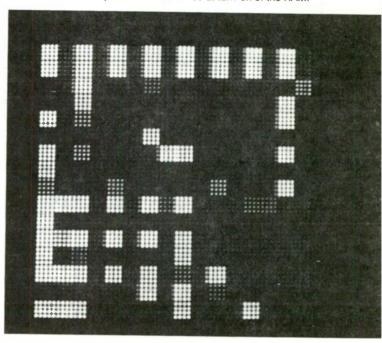

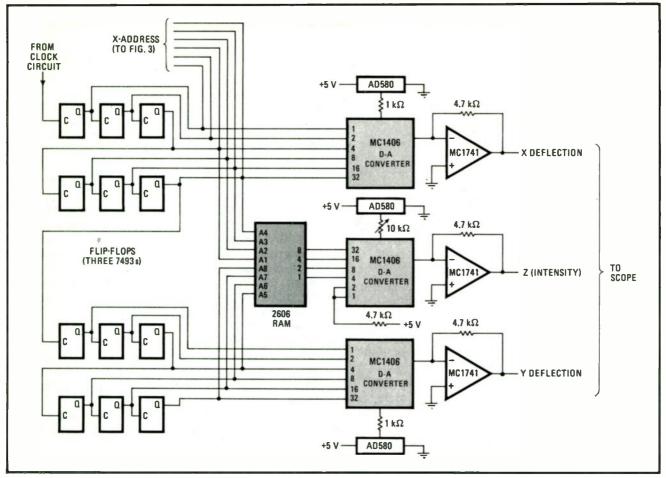

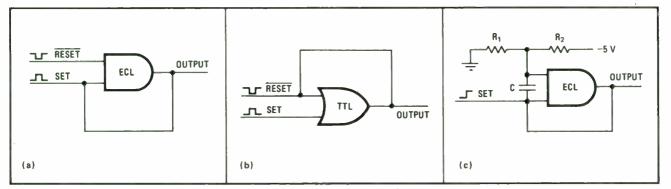

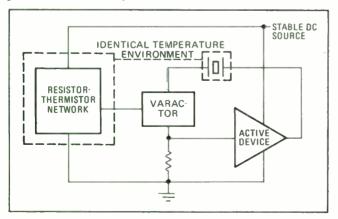

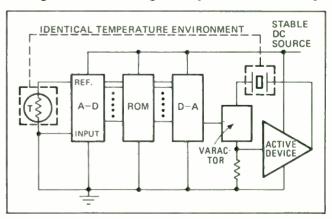

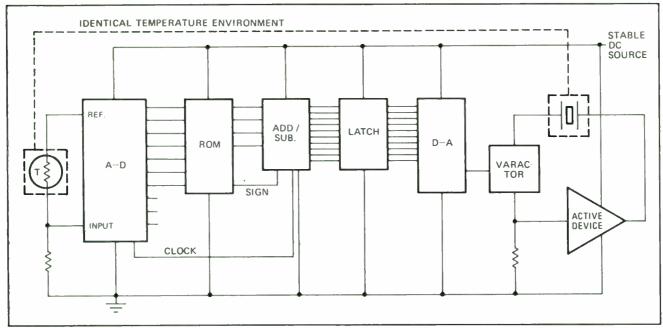

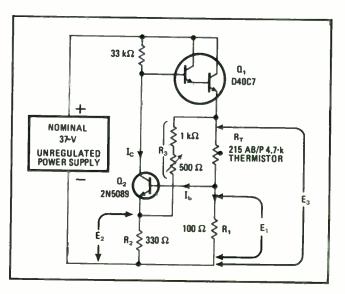

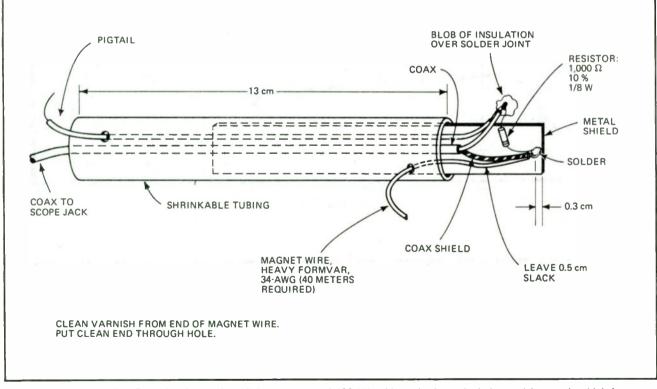

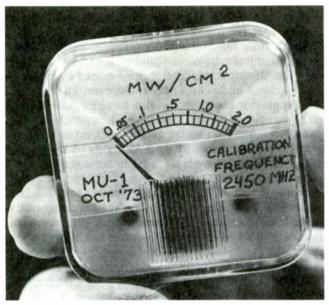

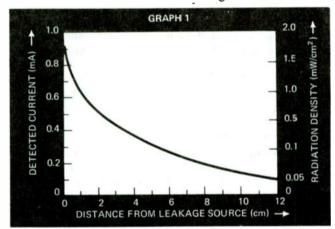

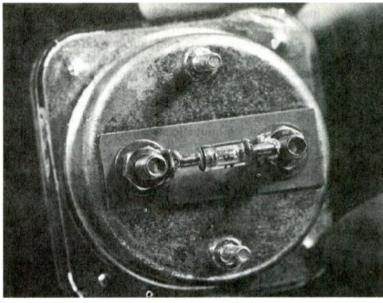

| 4.7                                               |                                   | 5,1                               |