M. L. WILLIAM

# Designer's Cosebook

#### PREPARED BY THE EDITORS OF **Electronics**

Third in a continuing series of selected Designer's Casebook sections of Electronics magazine. This edition includes Electronics issues from February 16, 1978 through January 4, 1979. Also included are feature articles and items from Engineer's Notebook of particular interest to the circuit designer.

Price: \$5,00 North America \$12.00 outside North America Printed in U.S.A.

All material copyrighted by

#### **Electronics**

McGraw-Hill, Inc. 1221 Avenue of the Americas New York, New York 10020

### **CONTENTS**

| AUDIO AND ANALOG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| Programmed module automates transducer's linearization  Delay lines help generate quadrature voice for SSB  Unity-gain buffer amplifier is ultrafast  Bootstrapping a phototransistor improves its pulse response  Op amps and counter form low-cost transistor curve tracer  Multiplier, op amp generate sine for producing vectors  Demand-switched supply boosts amplifier efficiency  Removing the constraints of C-MOS bilateral switches  Three LED's display response of null-detector circuit  Go/no-go tester checks optocoupler's transfer ratio  Low-level-light detector checks optical cables fast  Tester determines solar cell's sunlight gathering efficiency  Optically isolated scope probe eliminates ground loops | 11                                     |

| CONTROL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                        |

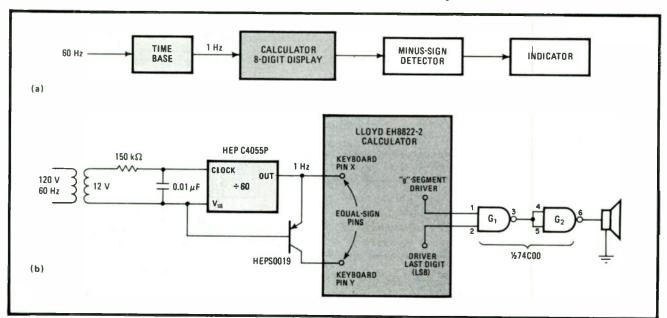

| Diodes and integrator brake small motors dynamically  Switching-mode controller boosts dc motor efficiency  Four-function calculator times long intervals accurately  Up-down ramp quickens servo-system response  Vehicle-intruder alarm has automatic set/reset switching  Controller selects mode for multiphase stepping motor  Open-collector logic switches rf signals  Optoisolators slash cost of three-phase detector  One button controller issues step, run and halt commands  Opto-isolated detector protects thyristors  Pilot-lamp controller stabilizes crystal oven  Synchronous pulsing cuts three-phase motor's dissipation                                                                                         | 21<br>33<br>36<br>45<br>52<br>57<br>68 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                        |

| DESIGN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| What happens to semiconductors in a nuclear environment?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1<br>5<br>8      |

| FILTERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                  |

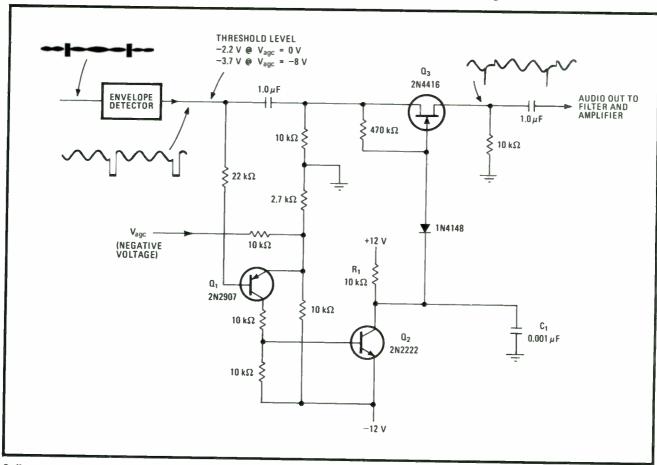

| Audio blanker suppresses radar-pulse and ignition noise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0                |

| LOGIC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                  |

| EPROM achieves nonuniform data sampling  D-flip-flops sense locked state of PLL  PROM adds bootstrap loader to Intellec-8 development system  RAMs reduce chip count in programmable delay lines  PROM converts push-button command to binary number  In-range frequency detector has jitter-free response  Zimer's built-in delay circumvents false alarms  Digital logic multiplies pulse widths  Zero-sensing counter yields data's magnitude and sign  Prescaler and LSI chip form 135-MHz counter  Smoke-detector chip generates long time delays  Industrial counter handles widely-varying intervals  Biaxial modulators double data-system transfer rate  Toigital sample and hold speeds a-d conversion time  9900 simplifies design of bidirectional I-O module  Small interface simplifies processor interrupt routine  8 Badge reader checks for production defects  8 Single wire pair multiplies power and data for display | 0469393447910178 |

| Single-wire pair multiplies power and data for display                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5                |

| POWER SUPPLIES                                       |

|------------------------------------------------------|

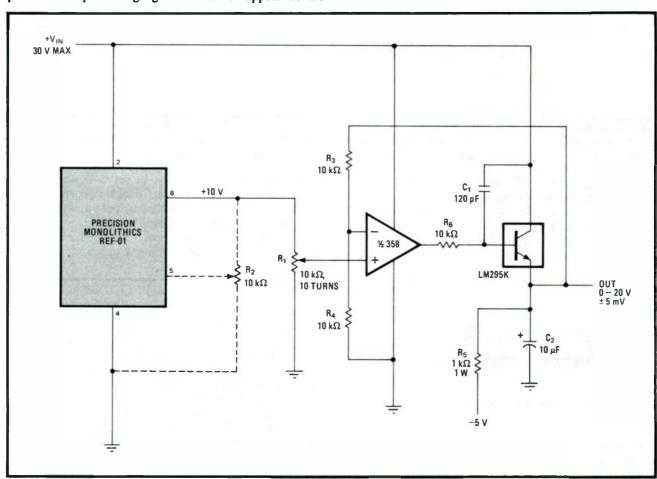

| DC-dc power supply has reference-unit stability      |

| SIGNAL CONVERSON                                     |

| RC-discharge clock makes a-d encoder logarithmic     |

| SIGNAL SOURCES                                       |

| Phase-locked generator converts, filters most inputs |

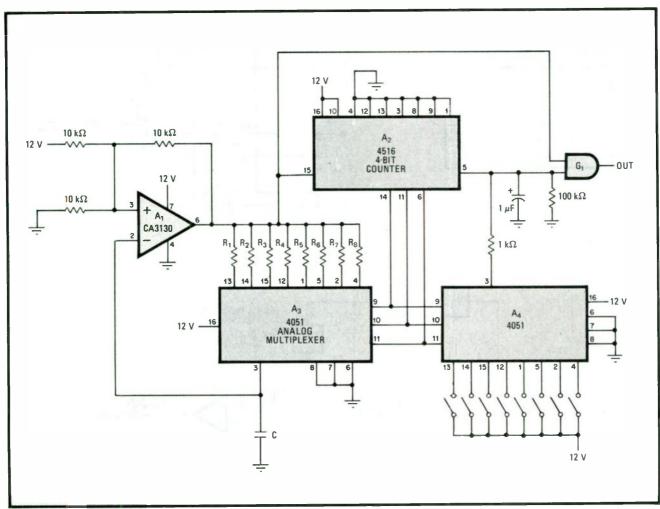

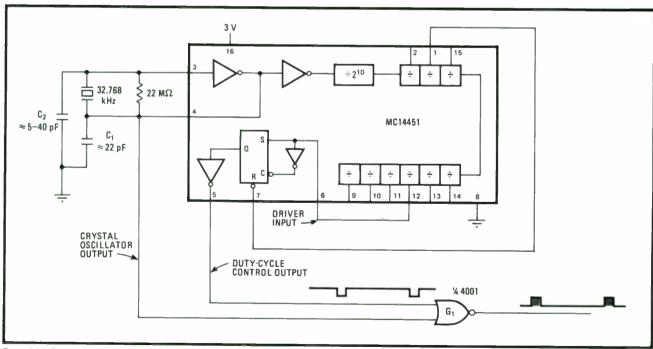

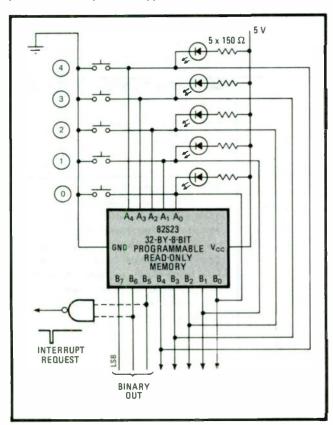

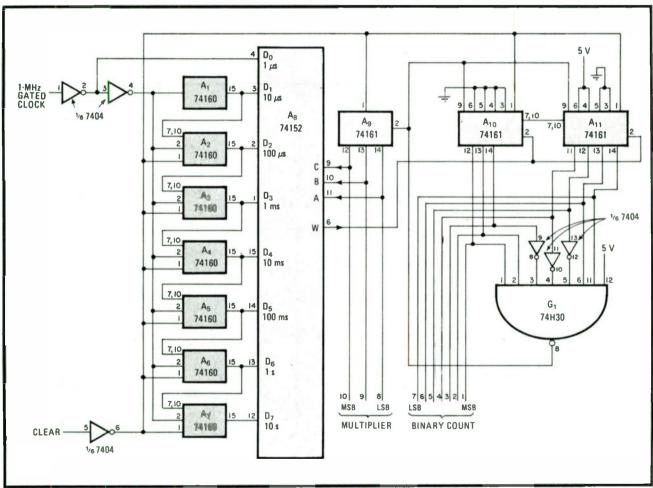

# EPROM achieves nonuniform data-channel sampling

by B. Bowles and T. U. Nelson Chamber of Mines of South Africa, Johannesburg

In some multiplexed data-acquisition systems, adequate bandwidth is not always available for transmitting every channel at the rate required by the fastest channel. It is therefore necessary to sample some channels at a higher speed than others, each at a rate equal to at least twice its highest frequency. A nonuniform sampler circuit is thus required.

A circuit built with an erasable programmable readonly memory forms an effective nonuniform sampler. The erasable PROM is programmed so that a sequential scan of its memory locations results in the selection of a channel sequence determined by the bandwidth requirements of each channel. In this way, the transmission rate

of any channel is made proportional to its bandwidth. Using the erasable PROM and the associated circuitry to generate the sequence is more practical than using the usual array of analog switches or the well-known shift-register-diode-matrix circuit, especially when the number of channels is large or the sequence is complex.

To understand the design problem, first consider the channel format for a typical multiplexed pulse-codemodulation system as shown in Fig. 1a. Each analog channel of this 20-channel system requires 10 clock periods—8 clock periods for quantizing a data word, plus 2 clock periods preceding the word that are required for internal timing in the circuit processing the data. Any 7 of the 20 channels are periodically multiplexed as a block, or subframe. Twelve such subframes form one main frame, as shown. Since each subframe, except the first, is preceded by a synchronization pulse 16 clock periods long, and if the clock frequency is assumed to be 50 kilohertz (period of 20 microseconds), the sync time will be 320  $\mu$ s. The mainframe sync pulse occurring before subframe 1 is 32 clock periods, or 640 µs, long. It takes 200 us to sample each channel or, equivalently, 1,400  $\mu$ s to sample each subframe.

In this case, each channel has the following bandwidth: channels 1 through 4, 163 Hz; channels 5 through 14, 47 Hz; and channels 15 through 20, 16 Hz. Note that the total frame time, about 21 milliseconds, is three times greater than the highest bandwidth of any channel sampled, to prevent fold-over distortion (from sampling theory, 2 is the minimum ratio required). With this arrangement, the sampling rate of channel 1 through channel 4 will be 4 times that of channels 5 through 14 and will be 13 times that of channels 15 through 20, as shown in Fig. 1b.

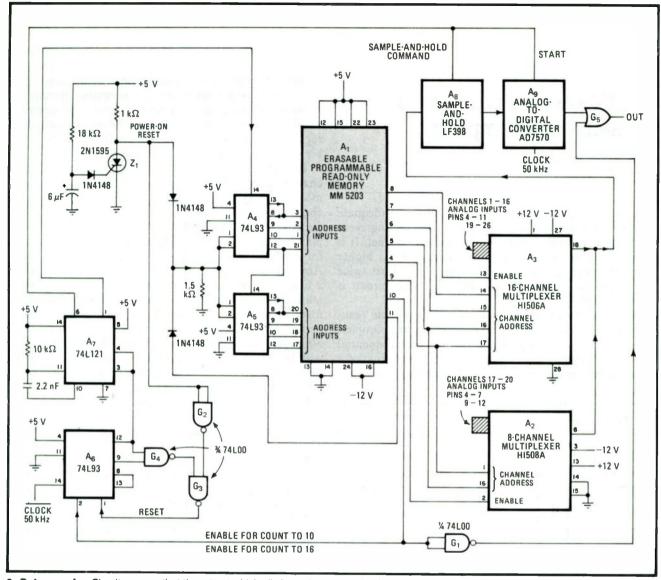

The format can be realized by the circuit shown in Fig. 2 if the PROM is programmed, beginning at location 3, with the channel numbers shown in Fig. 1b. Programming proceeds from left to right, subframes 1 to 12. Both locations 1 and 2 of the PROM, each representing a subframe, and the programming of certain nondata bits are subject to special considerations, which will be discussed shortly.

Circuit operation is easily explained. Basically, any of 20 channels is selected by sending the channel number from the 256-word-by-8-bit erasable PROM  $(A_1)$  to the address inputs of an 8- and a 16-channel multiplexer  $(A_2$  and  $A_3$ , respectively). The contents of each channel are then passed to the output of the circuit in prescribed order. The first 16 channels are handled by  $A_3$ , the remaining four by  $A_2$ .

1. Data format. Typical requirements for a multiplexed PCM system are shown. Any 7 channels of this 20-channel system are multiplexed in 12 subframes, such that the sampling rate of each channel is proportional to its bandwidth (a). Transmission format for this system (b) can be found once the channel bandwidths are known (see text). Data sampler can generate this or any other format desired.

2. Data sampler. Circuit ensures that the rate at which all channels are sampled is proportional to the bandwidth of each, in accordance with the requirements of sampling theory. The erasable PROM can be programmed so that any desired channel sequence can be transmitted via the 16-channel multiplexer; the transmission rate for each channel will in this way be easily controlled.

On power up, thyristor  $Z_1$  resets counters  $A_4$  through  $A_6$ , thereby selecting the first PROM location.  $A_4$  and  $A_5$  will be placed in the standby mode and  $A_6$  will be placed in the count-to-16 mode, because the PROM is programmed to generate a logic 0 at pin 10 of  $A_1$ . When  $A_1$ 's anode voltage drops to zero,  $A_6$  begins to count, and this initiates the master sync cycle.

After 16 counts, the one-shot  $(A_7)$  fires and increments  $A_4$ , and therefore the second memory location of the PROM is selected. The second location is programmed so that its contents are identical to that of location 1, and consequently, 16 counts later, the third memory location is selected. This location contains the address of the first multiplexer channel.

Pin 10 of  $A_1$  has moved high, thereby enabling  $G_5$ , and setting  $A_6$  into its count-to-10 mode. Note that the multiplexers are addressed by 6 bits of  $A_1$ , not 8; the remaining 2 bits are required for the system sync-control circuit comprising  $G_1$ ,  $G_5$ , and pin 10 of  $A_6$ .

Meanwhile the one-shot initiates the sample-and-hold command and resets  $A_9$ . The contents of channel 1 then appear at the input of  $A_9$ . At the second positive clock edge after the cessation of the pulse emanating from  $A_7$ , the most significant bit of data appears at the output of  $A_9$  and thus at the circuit output.  $A_3$  is now in the count-to-10 mode (caused by pin 11 being high).  $A_4$  and  $A_5$  are again incremented by  $A_7$  after the monostable is triggered by pulse 10 of  $A_1$ .  $A_5$  and  $A_6$  select the next PROM address, which is 2 in this case. This process is repeated until all seven channels have been selected.

At the next memory location, the PROM must be programmed so that a 0 once again emanates from pin 10, to set  $A_6$  into the count-to-16 mode once more and to generate a logic 1 at the system output by means of  $G_1$  and  $G_3$ . Triggering A in this way sets the stage for the generation of a subframe sync pulse and the selection of the first channel in the second subframe after 16 pulses have been counted by  $A_1$ . The selection process continues

until all the subframes have been scanned.

The location representing subframe 12 should be programmed so that a logic 1 appears at pin 11. This

resets the counters and selects the first memory location in  $A_1$ , as before. The system generates the main-frame sync pulse again and the entire process is repeated.

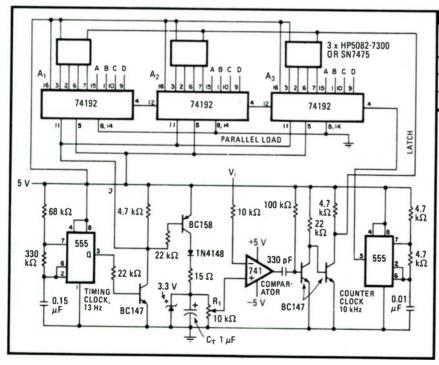

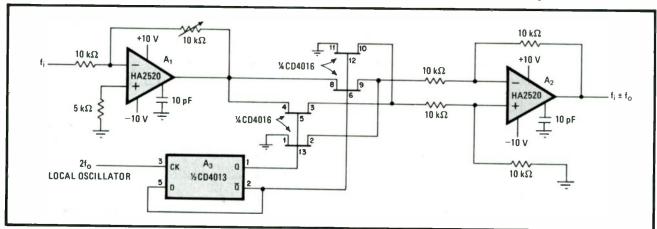

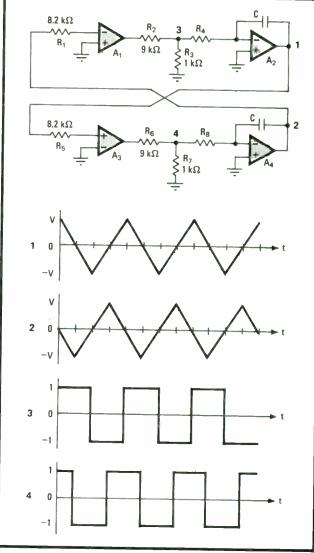

# Phase-locked generator converts, filters most inputs

by Peter Reintjes

Research and Design Ltd., Morehead City, N. C.

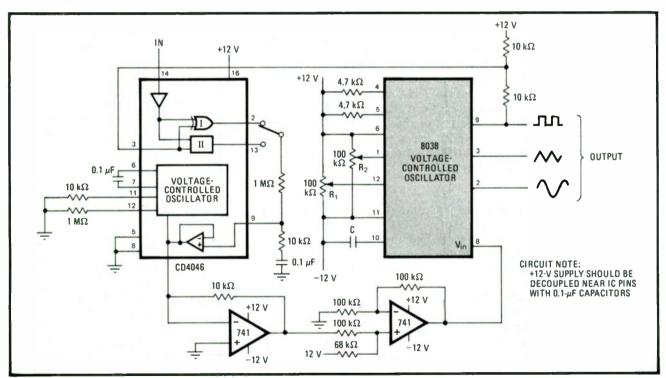

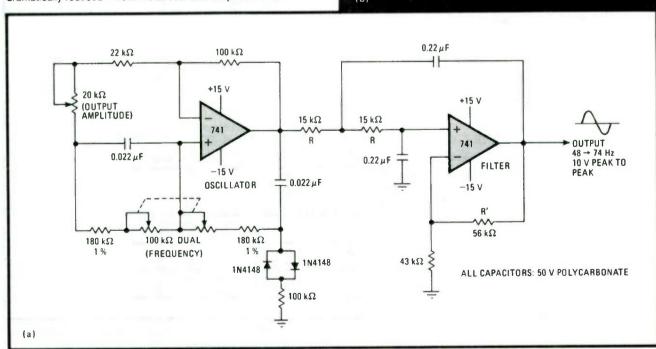

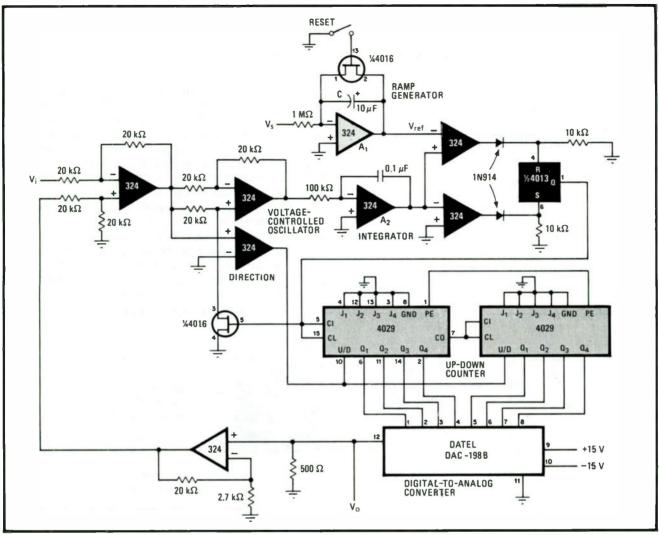

Replacing the voltage-controlled oscillator in the RCA 4046 phase-locked loop with the popular Intersil 8038 waveform generator forms a circuit that produces sine, square, and triangular wave voltages capable of tracking almost any input signal. Besides performing its prime function of waveform conversion, the circuit serves as a high-Q filter. With a harmonic distortion of only 0.5%, it finds the fundamental frequency of any signal.

The performance of this circuit far exceeds that of a conventional filter, which always adds a phase shift to the incoming signal. Also, traditional filtering methods are often of little use when the fundamental frequency must be recovered from an unpredictable input signal.

Connecting the 8038, which is itself a voltagecontrolled oscillator, to the 4046 as shown in the figure does not affect the normal operation of the phase-locked loop. The only difference in the basic PLL circuit is that the 8038 generates sine, triangular, and square waves and drives the 4046 in place of the loop's internal vco. The output waveshapes are unaffected by the harmonic distortion present on the input signal. Capacitor C sets the center frequency of the 8038 (a value of 0.047 microfarad corresponds to a frequency in the audio range). The frequency-capture range of the circuit, which is determined by the 4046, remains 1,000 to 1. The generator's maximum operating frequency is about 700 kilohertz.

To secure precise locking, the comparators in the 4046 should be driven by the square-wave output of the 8038. If the input waveform is a pulse, phase comparator I should be used. For unpredictable or high-noise signals, phase comparator II is more suitable.

Any phase difference between the square-wave output of the 8038 and the input signal is amplified by two 741 operational amplifiers and then fed back to the VCO to increase or decrease its frequency, as the case may be. Although the internal VCO of the 4046 is not used, it must be enabled by grounding pin 5 of the device so that its voltage-follower will be active. If matched resistors are used at pin 4 and 5 of the 8038, the sine-wave output distortion can be reduced to 0.5%. Potentiometers R<sub>1</sub> and R<sub>2</sub> aid in minimizing the distortion.

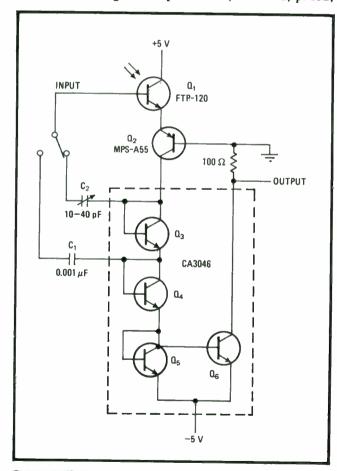

Tracking waveforms. ICL 8038 and two op amps replace internal VCO in 4046 to form phase-locked-loop waveform generator that can be used to recover fundamental frequency of any input signal or to convert the control signal to sine, square, and triangular waves. The generator's maximum output frequency is about 700 kHz. R₁ and R₂ are adjusted for minimum output distortion.

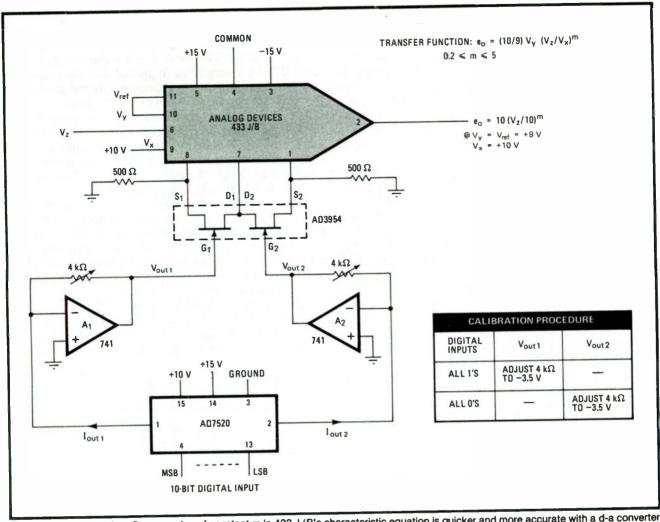

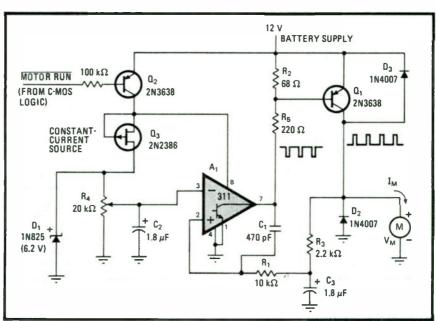

## Programmed module automates transducer's linearization

by C. Viswanath Indian Institute of Science, Bangalore, India

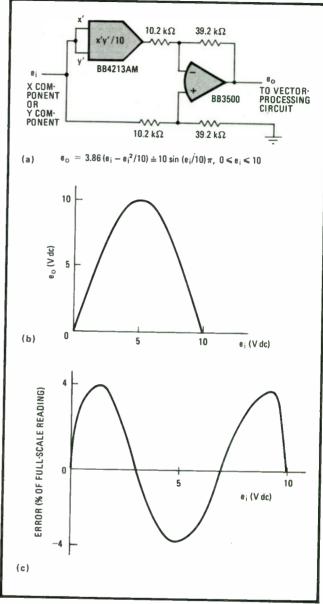

As a consequence of its unusual transfer function, the Analog Devices 433 J/B programmable multifunction module finds wide use in performing vector operations, generating trigonometric functions, raising a number to an arbitrary power, and linearizing the response of transducers used in medical and industrial electronics.

The module's transfer function is:

$$e_o = \frac{10}{9} V_y \left( \frac{V_z}{V_x} \right)^m = P$$

$0.2 \le m \le 5.0$

Programming of the exponent, m, contained in the transfer function, which is necessary to generate the required operations, is done more quickly and accurately with a digital-to-analog converter and two field-effect transistors than with a potentiometer, the component most often used. Digital selection of the exponent is particularly useful where an automatic test sequence must be generated from a microprocessor to multiplex several transducers, each requiring a different m. With this circuit, the value of m may be adjusted throughout the entire specified range, in increments of 0.1.

A circuit used for transducer linearization is shown in the figure. The technique used for linearizing a transducer's transfer function (Q) is to control m so that it varies inversely with the known exponent (n) contained within the transducer's characteristic equation. Thus, when the output voltage from the transducer  $(V_z)^n$  has been processed by the 433 J/B, the effects of m and n on the output voltage will cancel each other (as a result of multiplying P and Q to obtain  $e_o$ ), and the entire transfer function is then simply expressed by:

$$e_o = K V_z$$

The value of m is programmed by controlling the resistance between pins 1, 7, and 8 of the 433 J/B by means of the AD3954 dual-FET stage and the 10-bit AD7520 d-a converter. The combination of the converter and the dual FETs is thus intended to serve as a digitally controlled potentiometer.

Two binary-weighted current sources, the magnitudes of which are dependent on the 10-bit input and the sum of which is constant (equal to  $I_{out\,1}$  plus  $I_{out\,2}$ ), drive operational amplifiers  $A_1$  and  $A_2$ . The magnitude of  $I_{out\,1}$  and  $I_{out\,2}$  are determined by the reference voltage at pin 15 of the converter.

$A_1$  and  $A_2$  convert the currents to voltages  $V_{out\,1}$  and  $V_{out\,2}$ , respectively, and drive the gates of the dual FET. The FETs operate as voltage-controlled resistors and are

| M         DIGITAL INPUT<br>MSB         LSB           0.2         00000000000         0.000000000           0.3         0000010100         0.4           0.0         0.6         0001000000           0.6         0001010100           0.7         0001101010           0.8         0010000000           0.9         0010010100           1.0         0011010100           1.2         0011010100           1.3         0011101010           1.4         0100000000           1.5         0100010100           1.6         0100101010           1.7         0101000000           1.8         0101010100           2.0         0110000000           2.1         0110010100           2.2         0111010100           2.3         0111001000           2.4         0111010100           2.5         0111101010           2.6         100000000           2.7         1000010100           2.8         1001000000           3.0         1001010100           3.1         1001000000           3.2         1010000000           3.3         1            | PROGRAMMING OF EXPONENT M |               |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|---------------|--|--|

| M                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                           | DIGITAL INPUT |  |  |

| 0.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | М                         |               |  |  |

| 0.3         0000010100           0.4         0000101010           0.5         0001000000           0.6         0001010100           0.7         0001101010           0.8         001000000           0.9         0010010100           1.0         0010101010           1.1         001100000           1.2         0011010100           1.3         0011101010           1.4         010000000           1.5         0100010100           1.6         010010100           1.7         0101000000           1.8         0101010100           2.0         0110000000           2.1         0110010100           2.2         0110101000           2.3         0111001000           2.4         0111010100           2.5         0111101010           2.6         100000000           2.7         1000010100           2.8         1001000000           3.0         1001010100           3.1         1001000000           3.2         1010000000           3.3         1010010100           3.4         1010000000                                       | 0.2                       |               |  |  |

| 0.4         0000101010           0.5         0001000000           0.6         0001010100           0.7         0001101010           0.8         001000000           0.9         0010010100           1.0         0010101010           1.1         0011010100           1.2         0011010100           1.3         0011101010           1.4         0100000000           1.5         010010100           1.6         0100101010           1.7         0101000000           1.8         0101010100           2.0         0110000000           2.1         0110010100           2.2         0110101000           2.3         0111001000           2.4         0111010100           2.5         0111101010           2.6         100000000           2.7         1000010100           2.8         1000101010           2.9         1001000000           3.0         1011010100           3.1         1011010100           3.2         1010000000           3.3         1010000000           3.4         1010101010 <tr< th=""><th></th><th></th></tr<> |                           |               |  |  |

| 0.5         0001000000           0.6         0001010100           0.7         0001101010           0.8         0010000000           0.9         001001010           1.0         001101010           1.1         001100000           1.2         001101010           1.3         0011101010           1.4         010000000           1.5         0100101010           1.7         0101000000           1.8         010110100           1.9         010110100           2.0         011000000           2.1         0110010100           2.2         0110101000           2.3         0111001000           2.4         0111010100           2.5         0111101010           2.6         100000000           2.7         1000010100           2.8         1000101010           2.9         1001000000           3.0         1001010100           3.1         1001101010           3.2         101000000           3.3         101000000           3.4         101000000           3.5         101101010                                               |                           |               |  |  |

| 0.6         00010101010           0.7         0001101010           0.8         001000000           0.9         0010010100           1.0         0011010100           1.1         0011000000           1.2         001110100           1.3         0011101010           1.4         010000000           1.5         010010100           1.6         0100101010           1.7         0101000000           1.8         0101010100           1.9         0101101010           2.0         0110000000           2.1         0110010100           2.2         0110101000           2.3         0111000000           2.4         0111010100           2.5         0111101010           2.6         100000000           2.7         1000010100           2.8         1000101010           2.9         1001000000           3.0         1001010100           3.1         1001000000           3.2         1010000000           3.3         101000000           3.4         101000000           3.5         1011000000                                        |                           |               |  |  |

| 0.7         0001101010           0.8         0010000000           0.9         0010010100           1.0         0010101010           1.1         0011000000           1.2         0011101010           1.3         0011101010           1.4         010000000           1.5         0100010100           1.6         0100101010           1.7         0101000000           1.8         0101010100           2.0         0110000000           2.1         0110010100           2.2         0110101000           2.3         0111000000           2.4         0111010100           2.5         0111101010           2.6         100000000           2.7         1000010100           2.8         1000101010           2.9         100100000           3.0         100100000           3.1         1001101010           3.2         1010000000           3.3         1010000000           3.4         101000000           3.5         1011000000           3.6         101101010           3.7         1011101010                                        |                           |               |  |  |

| 0.8         0010000000           0.9         0010010100           1.0         0010101010           1.1         0011000000           1.2         001101010           1.3         0011101010           1.4         010000000           1.5         0100010100           1.6         0100101010           1.7         0101000000           1.8         0101010100           2.0         011000000           2.1         0110010100           2.2         0110101000           2.3         0111000000           2.4         0111010100           2.5         0111101010           2.6         100000000           2.7         1000010100           2.8         1000101010           3.0         100100000           3.1         1001101010           3.2         101000000           3.3         101000000           3.4         1010101010           3.5         1011000000           3.6         101101010           3.7         1011101010           4.0         110010100           4.1         110010100                                            |                           |               |  |  |

| 0.9         00100101010           1.0         0010101010           1.1         001100000           1.2         001101010           1.3         0011101010           1.4         010000000           1.5         0100010100           1.6         0100101010           1.7         0101000000           1.8         0101101010           2.0         011000000           2.1         011001010           2.2         011010100           2.3         011100100           2.4         011100100           2.5         011110100           2.6         100000000           2.7         100001010           2.8         100010100           2.9         1001000000           3.0         1001010100           3.1         1001101010           3.2         101000000           3.3         101000000           3.4         1010101010           3.5         1011000000           3.6         101101010           3.7         1011101010           4.0         1100101010           4.0         1100101010           <                                    |                           |               |  |  |

| 1.0 0010101010 1.1 0011000000 1.2 0011010100 1.3 0011101010 1.4 0100000000 1.5 0100010100 1.6 0100101010 1.7 0101000000 1.8 0101101010 1.9 010110100 2.0 0110000000 2.1 01100100000 2.2 0110101000 2.2 0110101000 2.3 0111000000 2.4 0111010100 2.5 0111101010 2.6 100000000 2.7 1000010100 2.8 1000101010 2.9 1001000000 3.0 1001010100 3.1 100101010 3.2 101000000 3.3 1010010100 3.4 101010100 3.5 1011000000 3.6 1011000000 3.7 1011101010 3.8 1100000000 3.9 110000000 3.9 110000000 4.0 110010100 4.1 110101010 4.1 1101000000 4.2 1100101010 4.3 1110010100 4.4 1110000000 4.5 1110010100 4.6 1110010100 4.7 11110000000 4.7 11110000000 4.8 111110000000                                                                                                                                                                                                                                                                                                                                                                                     |                           |               |  |  |

| 1.1       0011000000         1.2       0011010100         1.3       0011101010         1.4       0100000000         1.5       0100010100         1.6       01001010100         1.7       0101000000         1.8       0101010100         1.9       01011010100         2.0       0110000000         2.1       0110010100         2.2       0110101000         2.3       0111000000         2.4       011101010         2.5       0111101010         2.6       100000000         2.7       1000010100         2.8       1000101010         2.9       1001000000         3.0       1001010100         3.1       1001000000         3.2       1010000000         3.3       1010010100         3.4       10110101010         3.5       1011000000         3.6       10110101010         4.0       1100101010         4.1       110000000         4.2       11010101010         4.3       11010101010         4.4       1110000000         4.5       111001010                                                                                            |                           |               |  |  |

| 1.2       0011010100         1.3       0011101010         1.4       0100000000         1.5       0100010100         1.6       01001010100         1.7       0101000000         1.8       0101101010         2.0       0110000000         2.1       0110010100         2.2       0110101000         2.3       0111000000         2.4       011101010         2.5       0111101010         2.6       100000000         2.7       1000010100         2.8       1001000000         3.0       1001000000         3.1       1001000000         3.2       1010000000         3.3       1010010100         3.4       1010000000         3.5       1011000000         3.6       101101010         3.7       1011101010         4.0       1100101010         4.1       110000000         4.2       1101010100         4.3       1100101010         4.4       1110000000         4.5       1110010100         4.6       1110000000         4.8       1111000000                                                                                                 |                           |               |  |  |

| 1.3       0011101010         1.4       0100000000         1.5       0100010100         1.6       0100101010         1.7       0101000000         1.8       0101101010         2.0       0110000000         2.1       0110010100         2.2       0110101000         2.3       0111000000         2.4       0111101010         2.5       0111101010         2.6       1000000000         2.7       1000010100         2.8       1000101010         2.9       1001000000         3.0       1001010100         3.1       1001010100         3.2       1010000000         3.3       1010010100         3.4       1010000000         3.5       1011000000         3.6       1011010100         3.7       1011101010         4.0       110010100         4.1       110000000         4.2       1101010100         4.3       1101010100         4.5       1110000000         4.6       1110000000         4.8       11110000000                                                                                                                            |                           |               |  |  |

| 1.4       0100000000         1.5       0100010100         1.6       0100101010         1.7       0101000000         1.8       0101010100         1.9       0101101010         2.0       011000000         2.1       0110010100         2.2       0110101000         2.3       0111000000         2.4       0111101010         2.5       0111101010         2.6       1000000000         2.7       1000101010         2.8       1001000000         3.0       10010101010         3.1       1001000000         3.2       1010000000         3.3       10100101010         3.4       10100101010         3.5       1011000000         3.6       10110101010         3.7       1011101010         3.8       110000000         3.9       11000101010         4.0       1100101010         4.1       1101000000         4.2       11010101010         4.3       1101010100         4.5       1110010100         4.6       1110000000         4.8       11111000                                                                                            |                           |               |  |  |

| 1.5       0100010100         1.6       0100101010         1.7       0101000000         1.8       01010101010         1.9       01011010100         2.0       0110000000         2.1       0110010100         2.2       0110101000         2.3       0111000000         2.4       011101010         2.5       0111101010         2.6       100000000         2.7       1000010100         2.8       1001000000         3.0       1001010100         3.1       1001000000         3.2       1010000000         3.3       1010010100         3.4       1010000000         3.5       1011000000         3.6       101101010         3.7       1011101010         3.8       110000000         3.9       1100010100         4.0       1100101010         4.1       1101000000         4.2       1101010100         4.3       1101010100         4.5       1110010100         4.6       1110000000         4.8       1111000000                                                                                                                             |                           |               |  |  |

| 1.6       0100101010         1.7       0101000000         1.8       0101010100         1.9       0101101010         2.0       0110000000         2.1       0110101000         2.2       0110101000         2.3       0111000000         2.4       0111101010         2.5       0111101010         2.6       100000000         2.7       1000101010         2.8       1001000000         3.0       1001010100         3.1       1001000000         3.2       1010000000         3.3       1010010100         3.4       1010000000         3.5       1011000000         3.6       101101010         3.7       1011101010         3.8       110000000         3.9       1100010100         4.0       1100101010         4.1       1101000000         4.2       1101010100         4.3       1101010100         4.4       1110000000         4.5       1110010100         4.6       1110101010         4.8       1111000000                                                                                                                              |                           |               |  |  |

| 1.7       0101000000         1.8       0101010100         1.9       0101101010         2.0       0110000000         2.1       0110101000         2.2       0110101000         2.3       011100000         2.4       011101010         2.5       0111101010         2.6       100000000         2.7       1000010100         2.8       1000101010         2.9       1001000000         3.1       1001101010         3.2       1010000000         3.3       1010010100         3.4       1010101010         3.5       1011000000         3.6       1011010100         3.7       1011101010         3.8       110000000         3.9       1100010100         4.0       110010100         4.1       1101000000         4.2       1101010100         4.3       1101010100         4.4       1110000000         4.5       1110010100         4.6       1110000000         4.8       1111010100                                                                                                                                                             |                           |               |  |  |

| 1.8       01010101010         1.9       0101101010         2.0       0110000000         2.1       0110010100         2.2       0110101000         2.3       011100000         2.4       011101010         2.5       0111101010         2.6       100000000         2.7       1000101010         2.8       1001000000         3.0       1001010100         3.1       1001010100         3.2       1010000000         3.3       1010010100         3.4       1010101010         3.5       1011000000         3.6       1011010100         3.7       1011101010         3.8       110000000         3.9       1100010100         4.0       1100101010         4.1       1101000000         4.2       1101010100         4.3       1101010100         4.4       1110000000         4.5       1110010100         4.6       1110000000         4.8       1111010100                                                                                                                                                                                        |                           |               |  |  |

| 1.9       0101101010         2.0       0110000000         2.1       0110101000         2.2       0110101000         2.3       0111000000         2.4       0111101010         2.5       0111101010         2.6       1000000000         2.7       1000101010         2.8       1001000000         3.0       1001010100         3.1       1001010100         3.2       1010000000         3.3       1010010100         3.4       1010101010         3.5       1011000000         3.6       1011010100         3.7       1011101010         3.8       110000000         3.9       1100010100         4.0       110010100         4.1       1101000000         4.2       1101010100         4.3       1101010100         4.4       1110000000         4.5       1110010100         4.6       1110000000         4.8       1111010100                                                                                                                                                                                                                    |                           |               |  |  |

| 2.0       0110000000         2.1       0110010100         2.2       0110101000         2.3       0111000000         2.4       0111101010         2.5       0111101010         2.6       100000000         2.7       1000010100         2.8       1001000000         3.0       100101010         3.1       100101010         3.2       101000000         3.3       101001010         3.4       1010101010         3.5       1011000000         3.6       1011010100         3.7       1011101010         3.8       110000000         3.9       1100101010         4.0       1101010100         4.1       1101010100         4.2       1101010100         4.3       1101010100         4.4       1110010100         4.5       1110010100         4.6       1110010100         4.7       1111000000         4.8       1111010100                                                                                                                                                                                                                        | 1.8                       | 0101010100    |  |  |

| 2.1       0110010100         2.2       0110101000         2.3       0111000000         2.4       0111010100         2.5       0111101010         2.6       1000000000         2.7       1000010100         2.8       1001000000         3.0       1001010100         3.1       10010101010         3.2       1010000000         3.3       1010010100         3.4       1010101010         3.5       1011000000         3.6       1011010100         3.7       1011101010         3.8       1100000000         4.0       1100101010         4.1       1101000000         4.2       1101010100         4.3       1101010100         4.4       1110000000         4.5       1110010100         4.6       1110000000         4.7       1111000000         4.8       1111010100                                                                                                                                                                                                                                                                           |                           | 0101101010    |  |  |

| 2.2       0110101000         2.3       0111000000         2.4       0111010100         2.5       0111101010         2.6       1000000000         2.7       1000010100         2.8       1001000000         3.0       1001010100         3.1       10010101010         3.2       1010000000         3.3       1010010100         3.4       1010101010         3.5       1011000000         3.6       101101010         3.7       1011101010         3.8       110000000         4.0       1100101010         4.1       1101000000         4.2       1101010100         4.3       1101010100         4.4       1110000000         4.5       111001010         4.6       1110101010         4.7       1111000000         4.8       1111010100                                                                                                                                                                                                                                                                                                           |                           | 0110000000    |  |  |

| 2.3       0111000000         2.4       0111101010         2.5       0111101010         2.6       100000000         2.7       1000010100         2.8       1001000000         3.0       1001010100         3.1       1001010100         3.2       1010000000         3.3       1010010100         3.4       1010101010         3.5       1011000000         3.6       1011010100         3.7       1011101010         3.8       1100000000         4.0       1100101010         4.1       1101000000         4.2       1101010100         4.3       1101101010         4.4       1110000000         4.5       1110010100         4.6       1110000000         4.7       1111000000         4.8       1111010100                                                                                                                                                                                                                                                                                                                                       |                           | 0110010100    |  |  |

| 2.4       01111010100         2.5       0111101010         2.6       1000000000         2.7       1000010100         2.8       1000100000         3.0       1001010100         3.1       1001101010         3.2       1010000000         3.3       1010010100         3.4       1010101010         3.5       1011000000         3.6       101101010         3.7       1011101010         3.8       110000000         3.9       110001010         4.0       1100101010         4.1       1101000000         4.2       1101010100         4.3       1101101010         4.4       1110000000         4.5       1110010100         4.6       1110000000         4.7       1111000000         4.8       1111010100                                                                                                                                                                                                                                                                                                                                        | 2.2                       | 0110101000    |  |  |

| 2.5       0111101010         2.6       1000000000         2.7       1000010100         2.8       1000100000         3.0       1001010100         3.1       1001101010         3.2       101000000         3.3       1010010100         3.4       1010101010         3.5       1011000000         3.6       101101010         3.7       1011101010         3.8       110000000         3.9       1100010100         4.0       1100101010         4.1       1101000000         4.2       1101101010         4.3       1101101010         4.4       1110000000         4.5       1110010100         4.6       1110000000         4.7       1111000000         4.8       1111010100                                                                                                                                                                                                                                                                                                                                                                      | 2.3                       | 0111000000    |  |  |

| 2.6       1000000000         2.7       1000010100         2.8       1000101010         2.9       100100000         3.0       1001010100         3.1       1001101010         3.2       101000000         3.3       1010010100         3.4       1010101010         3.5       101100000         3.6       101101010         3.7       1011101010         3.8       110000000         3.9       1100010100         4.0       1100101010         4.1       1101000000         4.2       1101010100         4.3       1101101010         4.4       1110000000         4.5       1110010100         4.6       1110000000         4.7       1111000000         4.8       1111010100                                                                                                                                                                                                                                                                                                                                                                        | 2.4                       | 0111010100    |  |  |

| 2.7       1000010100         2.8       1000101010         2.9       100100000         3.0       10010101010         3.1       1001101010         3.2       101000000         3.3       1010101010         3.4       1010101010         3.5       101100000         3.6       101101010         3.7       1011101010         3.8       110000000         3.9       110001010         4.0       1100101010         4.1       1101000000         4.2       1101010100         4.3       1101101010         4.4       1110000000         4.5       1110010100         4.6       1110000000         4.7       1111000000         4.8       1111010100                                                                                                                                                                                                                                                                                                                                                                                                     | 2.5                       | 0111101010    |  |  |

| 2.8       100010101010         2.9       1001000000         3.0       10010101010         3.1       1001101010         3.2       101000000         3.3       1010101010         3.4       101100000         3.5       101100000         3.6       101101010         3.7       1011101010         3.8       110000000         3.9       1100010100         4.0       1100101010         4.1       1101000000         4.2       1101010100         4.3       1101101010         4.4       1110000000         4.5       1110010100         4.6       1110000000         4.7       1111000000         4.8       1111010100                                                                                                                                                                                                                                                                                                                                                                                                                               | 2.6                       | 100000000     |  |  |

| 2.9     1001000000       3.0     1001010100       3.1     1001101010       3.2     101000000       3.3     1010101010       3.4     1010101010       3.5     101100000       3.6     101101010       3.7     1011101010       3.8     110000000       3.9     1100010100       4.0     1100101010       4.1     110100000       4.2     110101010       4.3     1101101010       4.4     111000000       4.5     111001010       4.6     1110101010       4.7     1111000000       4.8     1111010100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2.7                       | 1000010100    |  |  |

| 3.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2.8                       | 1000101010    |  |  |

| 3.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2.9                       | 1001000000    |  |  |

| 3.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3.0                       | 1001010100    |  |  |

| 3.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3.1                       | 1001101010    |  |  |

| 3.4 1010101010 3.5 1011000000 3.6 1011010100 3.7 1011101010 3.8 1100000000 3.9 1100010100 4.0 1100101010 4.1 1101000000 4.2 1101010100 4.3 1101101010 4.4 1110000000 4.5 1110010100 4.6 1110101010 4.7 1111000000 4.8 1111010100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3.2                       | 101000000     |  |  |

| 3.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3.3                       | 1010010100    |  |  |

| 3.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3.4                       | 1010101010    |  |  |

| 3.7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3.5                       | 1011000000    |  |  |

| 3.8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3.6                       | 1011010100    |  |  |

| 3.9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3.7                       | 1011101010    |  |  |

| 4.0 1100101010<br>4.1 1101000000<br>4.2 1101010100<br>4.3 1101101010<br>4.4 1110000000<br>4.5 1110010100<br>4.6 1110101010<br>4.7 1111000000<br>4.8 1111010100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 3.8                       | 110000000     |  |  |

| 4.1     1101000000       4.2     1101010100       4.3     1101101010       4.4     1110000000       4.5     1110010100       4.6     1110101010       4.7     1111000000       4.8     11110101000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3.9                       | 1100010100    |  |  |

| 4.2     1101010100       4.3     1101101010       4.4     1110000000       4.5     1110010100       4.6     1110101010       4.7     1111000000       4.8     1111010100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4.0                       | 1100101010    |  |  |

| 4.3     1101101010       4.4     1110000000       4.5     1110010100       4.6     1110101010       4.7     1111000000       4.8     1111010100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4.1                       | 110100000     |  |  |

| 4.4     1110000000       4.5     1110010100       4.6     1110101010       4.7     1111000000       4.8     1111010100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4.2                       | 1101010100    |  |  |

| 4.5     1110010100       4.6     1110101010       4.7     1111000000       4.8     1111010100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4.3                       | 1101101010    |  |  |

| 4.6     1110101010       4.7     1111000000       4.8     1111010100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 4.4                       | 111000000     |  |  |

| 4.7 1111000000<br>4.8 1111010100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 4.5                       | 1110010100    |  |  |

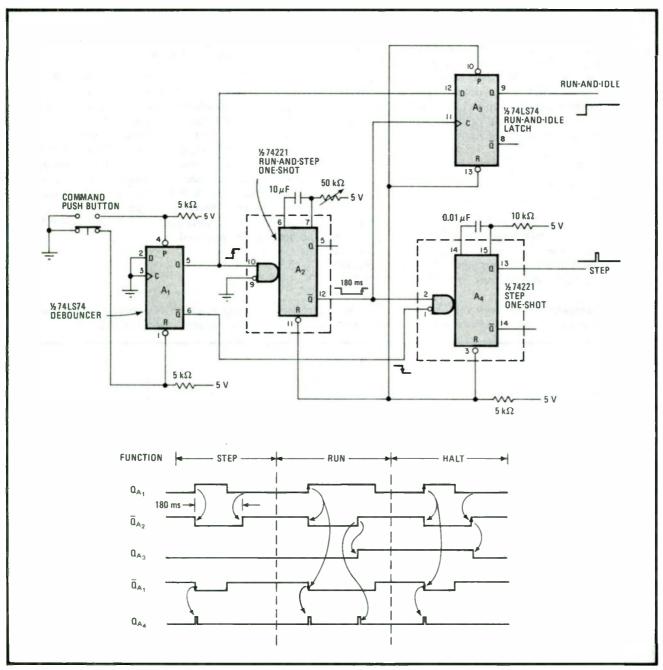

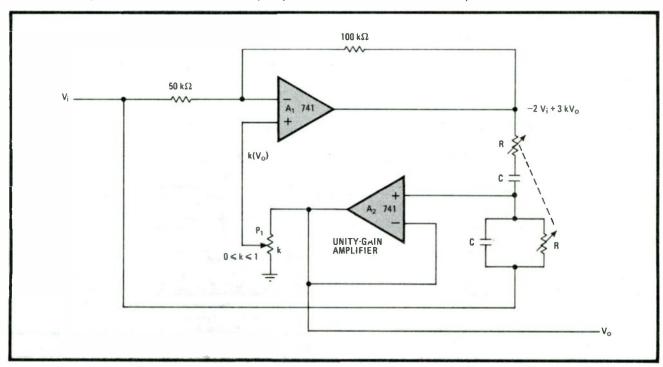

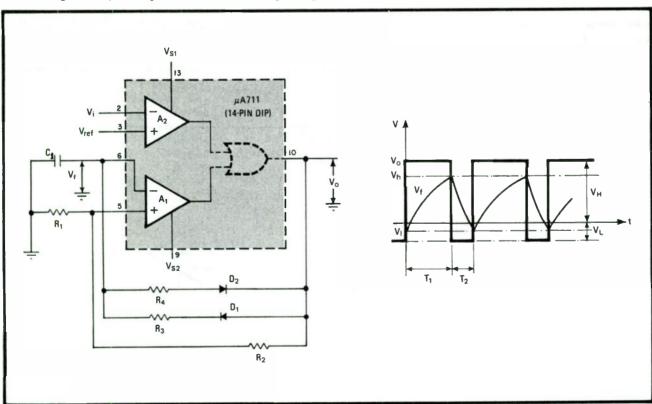

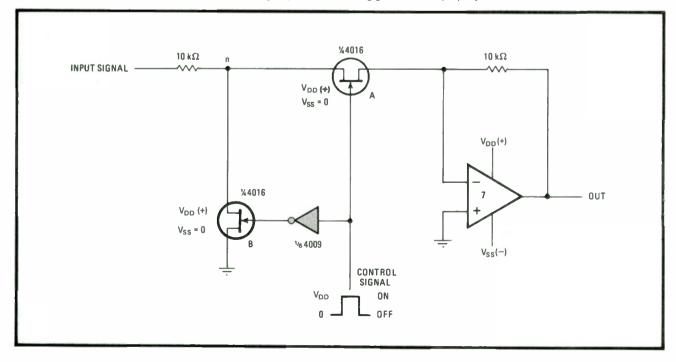

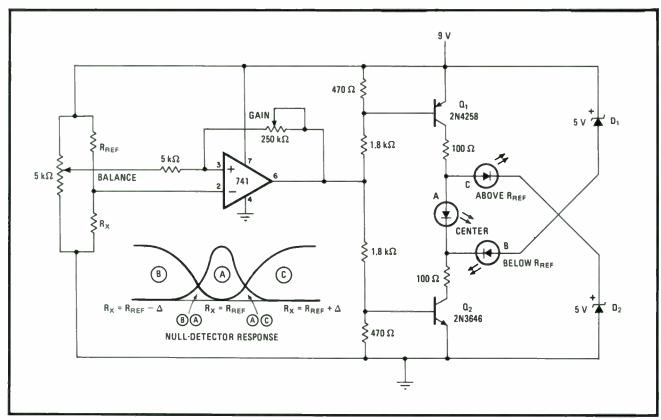

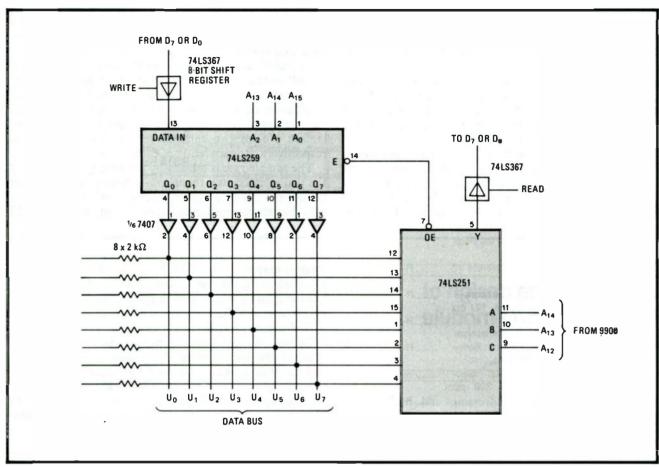

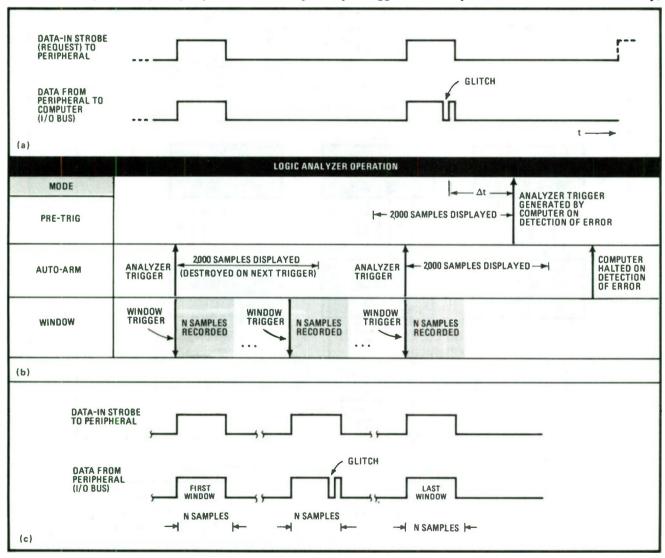

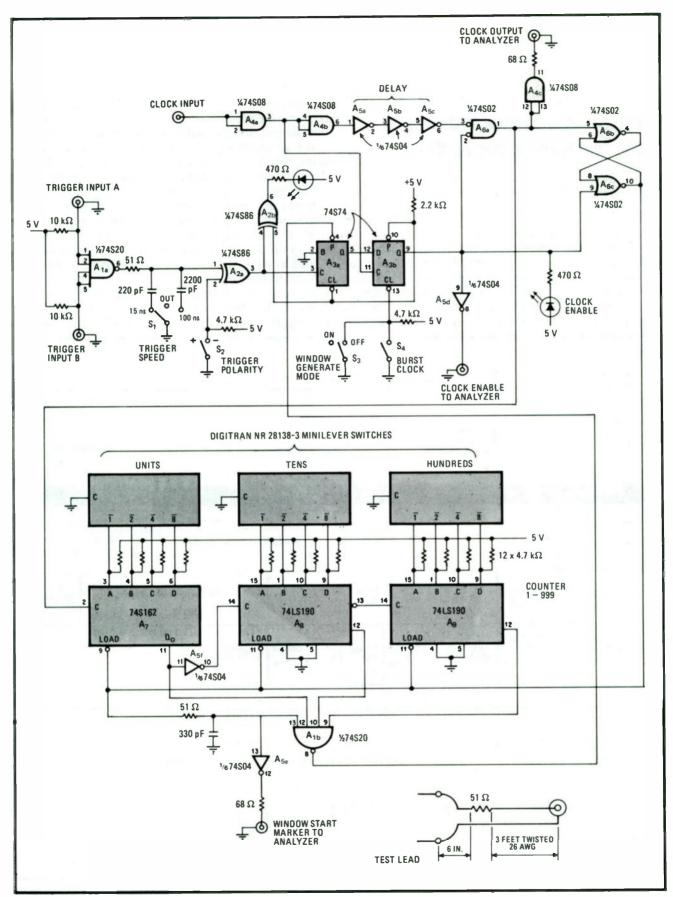

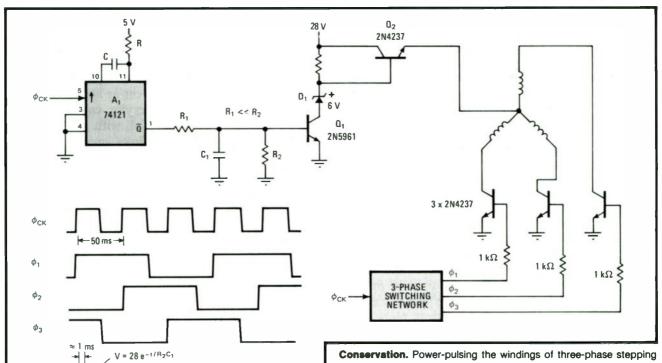

| 4.8 1111010100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 4.6                       | 1110101010    |  |  |