# Proceedings of the Second Annual WIRELESS Symposium

FEBRUARY 15-18, 1994 SANTA CLARA CONVENTION CENTER, SANTA CLARA, CA

Sponsored by Microwaves & RF Magazine

# Proceedings of the Second Annual WIRELESS Symposium

# FEBRUARY 15-18, 1994 SANTA CLARA CONVENTION CENTER, SANTA CLARA, CA

Sponsored by Microwaves & RF Magazine

Copyright c 1994 Penton Publishing All rights reserved

Penton Publishing 611 Route 46 West Hasbrouck Heights, NJ 07604 TEL: (201) 393-6289 FAX: (201) 393-6297

# ACKNOWLEDGMENTS

Doing something a second time does not necessarily make the task any easier. But in organizing the Second Annual WIRELESS Symposium, the final results certainly made for a more rewarding experience, especially with the help of the Program Chairpeople who gave so willingly of their time before and during the conference.

Special thanks is also in order for each and every WIRELESS author and presenter. In these demanding days of competitive business, time is precious, yet each of these authors made the extra effort to prepare presentations and travel—sometimes great distances—to the Santa Clara Convention Center. Their efforts will continue to fuel the growth of the many emerging wireless markets.

Jack Browne

Technical Program Chairman

# **Program Chairpeople**

Mark McDonald, Wireless Communications, National Semiconductor (Santa Clara, CA)

Robert Clarke, Analog Devices, Inc. (Wilmington, MA)

John Brewer, Tektronix, Inc., Microelectronics Div. (Beaverton, OR)

Ben Zarlingo, Hewlett-Packard Co., Lake Stevens Div. (Everett, WA)

David L. Sprague, InMark-Independent Marketing Corporation (Walnut Creek, CA)

Thomas Brinkoetter, Tektronix, Inc. (Beaverton, OR)

Algis Juodikis, Juodikis & Associates (Newport Beach, CA)

Paul Khanna, Avantek, Inc. (Santa Clara, CA)

Ganesh R. Basawapatna, Encore Communications Corp. (Englewood, CO)

Alan ("Pete") Conrad, Microwaves & RF (Hasbrouck Heights, NJ)

Raymond Camisa, David Sarnoff Research Center (Princeton, NJ)

# Technical Proceedings of the Second WIRELESS Symposium and Exhibition

#### ANALOG AND MIXED-SIGNAL ICs FOR WIRELESS COMMUNICATIONS....1

| A 3-V RF front-end GaAs MMIC for DCS-1800 cellular communications. Patrick Rousseau, Nathalie Caglio, Etienne Delhaye, Denis Masliah, Didier Meignant, and Eric Puechberty, LEP/Philips Microwave Limeil (Limeil-Brevannes Cedex, France)                                                                                                              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Push-pull receiver input amplifier stages—The solution to intermod problems. Hans Sapotta, TEMIC, Telefunken Microelectronic GmbH (Heilbronn, Germany)                                                                                                                                                                                                 |

| A low-voltage IC front-end for cellular radio. Sheng Lee and Alvin Wong, Philips Semiconductors (Sunnyvale, CA)                                                                                                                                                                                                                                        |

| A monolithic quadrature demodulator and digitizer for PSK and QAM applications. Jim Marsh, Scott Williams, and Brent Jensen,<br>Tektronix, Inc., Microelectronics Div. (Beaverton, OR); Simon Atkinson and Jonathon Strange, Mosaic Microsystems Ltd. (Kent,<br>England); Dave May, Tom Bilotta, and Fred Harris, TV/COM International (San Diego, CA) |

| Fractional-N frequency synthesizers for next-generation cellular and wireless applications. Wing S. Djen and Daniel J. Linebarger;<br>Philips Semiconductors (Sunnyvale, CA)                                                                                                                                                                           |

| A 1-V CMOS FSK receiver for wireless applications. David Shiels and Evert Dijkstra, Centre Suisse d'Electronique et de<br>Microtechnique S.A. (Neuchatel, Switzerland)                                                                                                                                                                                 |

#### **MICROPHONE-TO-ANTENNA SOLUTIONS....21**

| The application (Norwood, MA      | as of advanced CMOS/CCD technology in spread-spectrum receivers. Scott C. Munroe, Analog Devices, Inc.                       |  |

|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------|--|

| Signal-processi<br>Products (Gree | ng requirements for direct IF sampling receivers. David Duff, Analog Devices, Inc., Broadband Communications<br>.nsboro, NC) |  |

| Baseband supe                     | rintegration roadmap for digital cellular handsets. Charles K. Fadel, Analog Devices, Inc. (Wilmington, MA)54                |  |

| Advanced RF I<br>MA)              | Cs for VHF/UHF systems. Robert Clarke, Doug Grant, and Charles Fadel, Analog Devices, Inc. (Wilmington,                      |  |

| Direct digital sy                 | nthesis/direct digital modulation. Terry Brown and David Duff, Analog Devices, Inc. (Greensboro, NC)                         |  |

#### **INTEGRATED-CIRCUIT SOLUTIONS...69**

| Designing integrated RF circuits for wireless communications products. Peter Bronner and Philip L. Carrier, AT&T Microelectronics (Reading, PA)                                                                                                                   |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Performance analysis of DS-CDMA with slotted ALOHA random-access for packet PCNs. Zhao Liu and Magda El Zarki, Depart-<br>ment of Electrical Engineering, University of Pennsylvania (University Park, PA)                                                        |  |

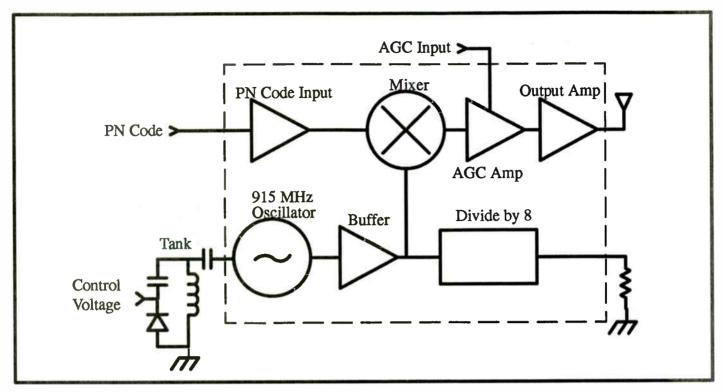

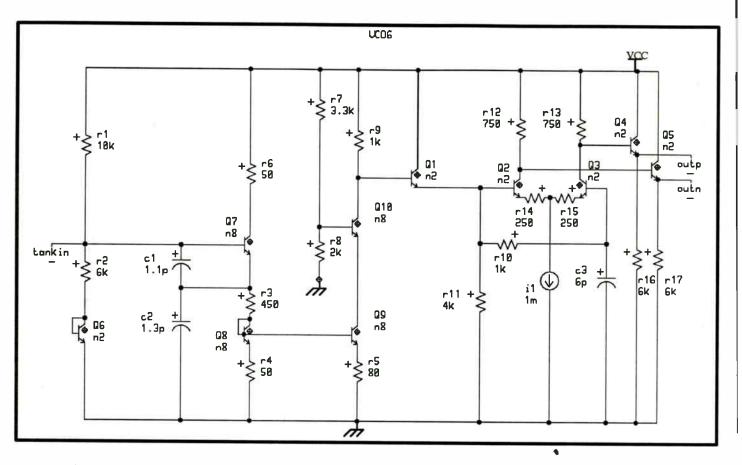

| A monolithic, 915-MHz, direct-sequence spread-spectrum transmitter. Stephen Press, Jeff Barry, and Jim Marsh, Tektronix, Inc.,<br>Microelectronics Div. (Beaverton, OR)                                                                                           |  |

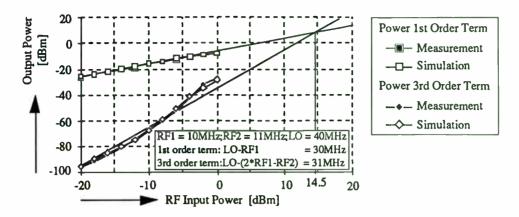

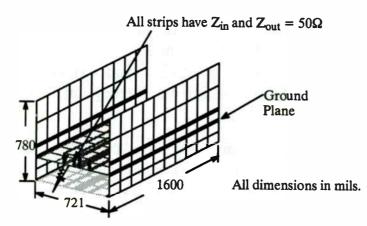

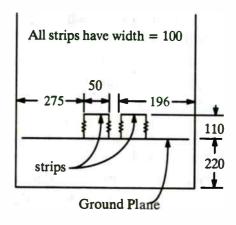

| An E/D model S-band MMIC frequency converter. M.C. Tsai, Y. Tajima, K. Alavi, B. Cole, B. Binder, S.L.G. Chu, and M. Goldfarb,<br>Raytheon Co., Research Div. (Lexington, MA); K. Gallagher and T. McGuire, Raytheon Co., Advanced Device Center (Andover,<br>MA) |  |

| RF IC components for cordless phones. Victor E. Steel, William J. Pratt, and Peter S. Bachert, RF Micro-Devices, Inc. (Greensboro, NC)                                                                                                                            |  |

| A 100-mW UHF spread-spectrum transmitter IC. Leonard D. Reynolds, Jr., William J. Pratt, and Powell T. Seymour, RF Micro-De-<br>vices, Inc. (Greensboro, NC)                                                                                                      |  |

# **TESTING FOR IMPROVED WIRELESS DESIGN....99**

| Improving wireless design and system integration with real-world testing. Ben Zarlingo, Hewlett-Packard Co., Lake Stevens Div.<br>(Everett, WA)                                                     | 1 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| Measuring carrier frequency of wireless communications systems in the presence of π/4-DQPSK modulation. David Chu and Dick<br>Schneider, Hewlett-Packard Co., Santa Clara Div. (Santa Clara, CA)106 |   |

| SMD component evaluation for RF circuit design. Mark Kato, Hewlett-Packard Co., Kobe Instrument Div. (Kobe, Japan)                                                                                  |   |

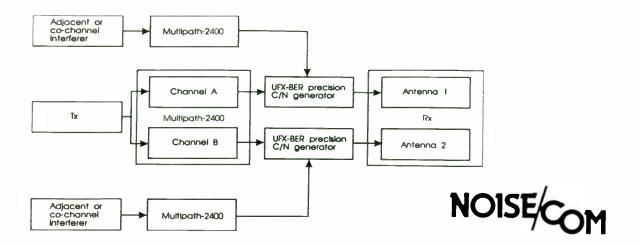

| Multipath fading simulation. Bent Hessen-Schmidt, NOISE/COM, Inc. (Paramus, NJ)                                                                                                                     |   |

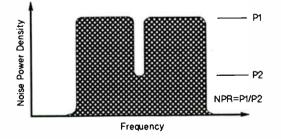

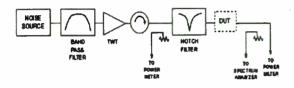

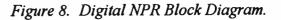

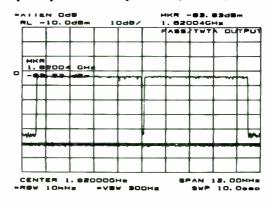

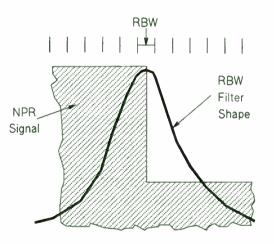

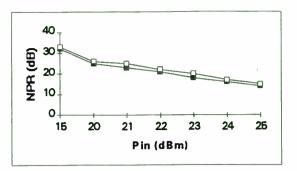

| Evaluating iridium amplifiers with a new noise-power-ratio technique. Rob McMorrow, Raytheon Co. (Wayland, MA); Steven E. Yates,<br>Hewlett-Packard Co., RF/Microwave Systems (Burlington, MA)      | ) |

| Trends, formats, and testing of digital cellular. Craig A. Hendricks, Anritsu Wiltron Sales Co. (Morgan Hill, CA)                                                                                   | ! |

### **CELLULAR DESIGN....148**

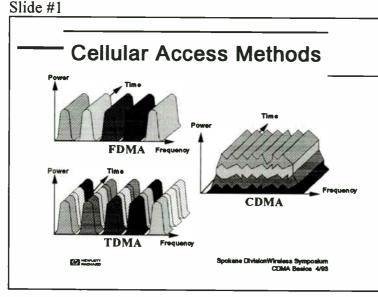

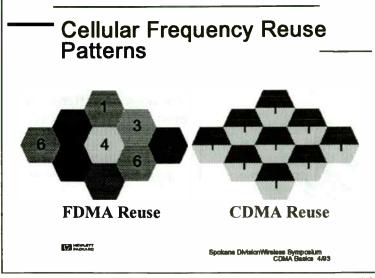

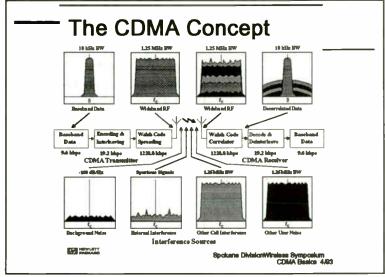

| Concepts of CDMA (dual session). Ken Thompson, Hewlett-Packard Co., Spokane Div. (Spokane, WA)149                                                                                                                                                                                                                                                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Sequence generation and detection for variable-rate CDMA networks. Bart F. Rice, Lockheed Missiles & Space Co., Inc. (Sunnyvale, CA)                                                                                                                                                                                                                   |

| Codes for multiple-access communications. Dennis A. Jiraud, Defense Systems, Inc. (McLean, VA)                                                                                                                                                                                                                                                         |

| Acoustic-echo cancellation for digital cellular applications. Shawn McCaslin, Crystal Semiconductor (Austin, TX)                                                                                                                                                                                                                                       |

| DECT and DUCT: Digital cellular telephone with wireless LAN capability. David Long and Gordon Lindsay, Sierra Semiconductor (San Jose, CA)                                                                                                                                                                                                             |

| UV-curable, conformal EMI-shielding coatings for cellular and cordless phones and walkie-talkies. V.K. Varadan, V.V. Varadan, and J. Terosky, Center for the Engineering of Electronic and Acoustic Materials, Pennsylvania State University (University Park, PA); James F. Kelly, US Army Communications and Electronics Command (Fort Monmouth, NJ) |

| New technology for low-cost RF connectors. John T. Doyle, Amphenol Corp. (Danbury, CT)                                                                                                                                                                                                                                                                 |

## WIRELESS MEASUREMENT STRATEGIES....188

| Testing GSM mobile phones. David Picken, Rohde & Schwarz (Munich, Germany)                                                                                   | .189             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| Multi-tone IMD measurement accuracy is assured with phase-aligned test carriers. Darryl R. Schick, RDL, Inc. (Conshohocken, PA)                              | .205             |

| Wireless Markets: Implications for RF test and measurement. Bert Berson and Joyce Peterson, Berson & Associates (Palo Alto, CA)                              | 218              |

| Noise-figure and gain measurement on high-speed bipolar junction transistors. Wayne Jung, Tektronix, Inc., Microelectronics Div.<br>(Beaverton, OR)          | 227              |

| Flexible instrumentation for wireless spread-spectrum signal-transmission testing. Herman C. Okean, LNR Communications, Inc.<br>(Hauppauge, NY)              | 234              |

| Measurement of group delay of frequency converters for satellite receivers. Martin Grace, Ed Daw, Don Culver, and Eric June, Wiltre<br>Co. (Morgan Hill, CA) | on<br><b>235</b> |

# **COMPUTER-AIDED ENGINEERING, I....236**

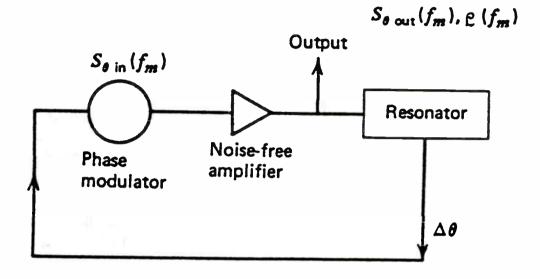

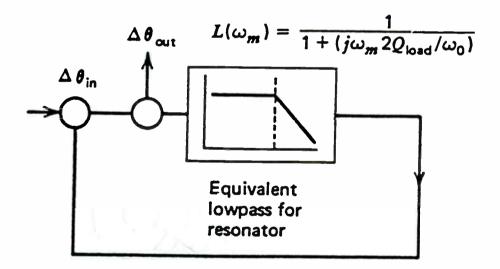

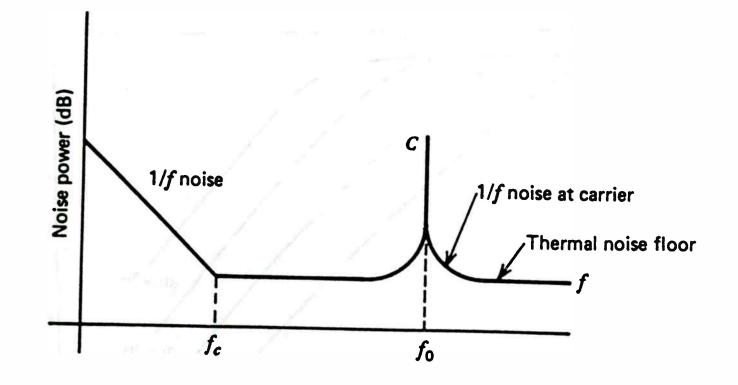

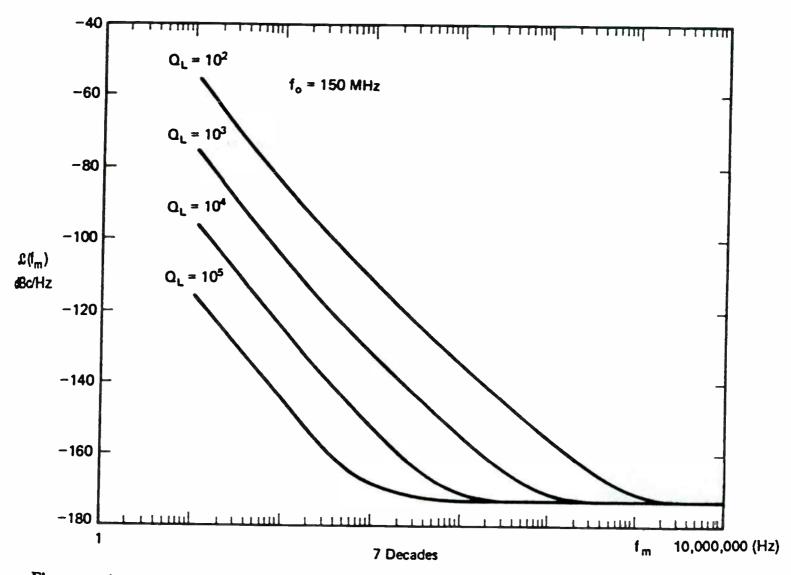

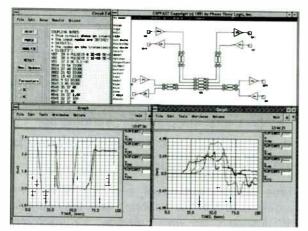

| The accurate simulation of oscillator and PLL phase noise in RF sources. Ulrich L. Rohde and Chao-Ren Chang, Compact Software, Inc. (Paterson, NJ)                                                                                                      |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

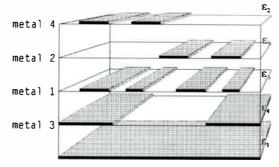

| The application of Super-SPICE in the design of multilayer boards. Krishna Kottapalli and Jason Gerber, Compact Software, Inc.<br>(Paterson, NJ)                                                                                                        |  |

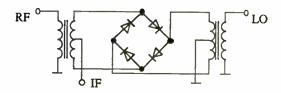

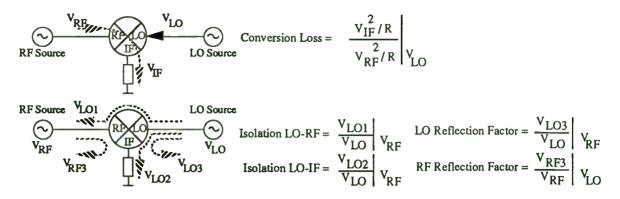

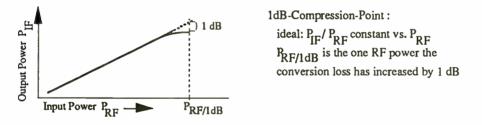

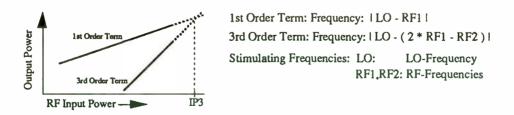

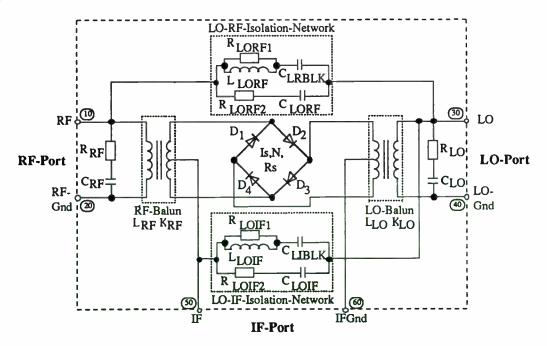

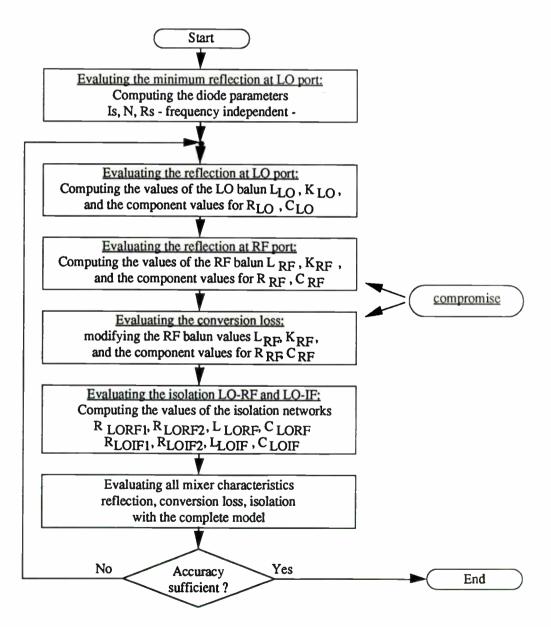

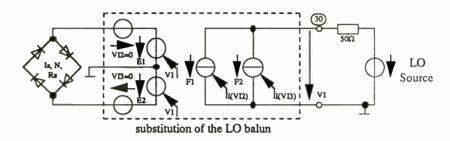

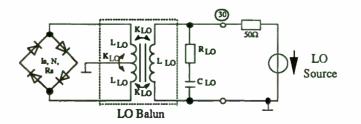

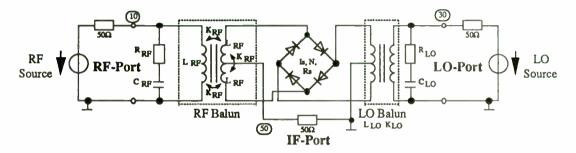

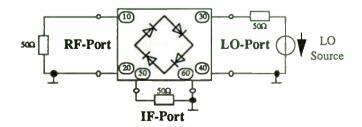

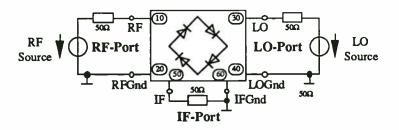

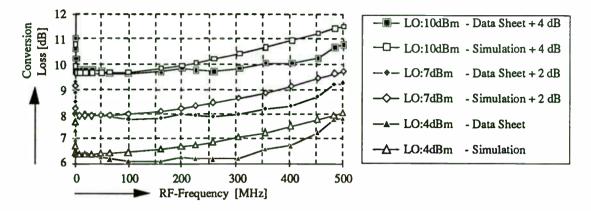

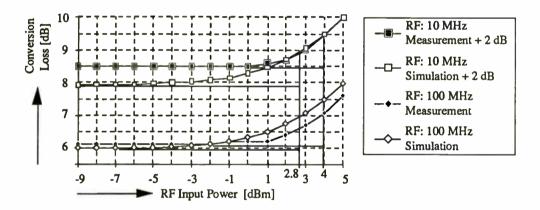

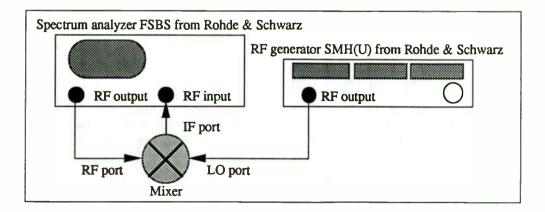

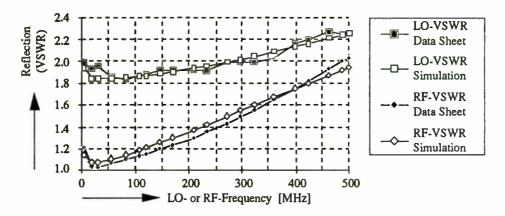

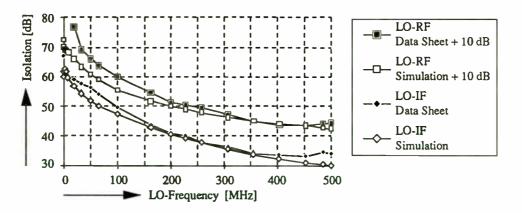

| A SPICE model for passive diode ring mixers. Siegfried Geiselbrecht and Albert Heuberger, Fraunhafer Institut fur Integrierte<br>Schaltungen (Erlangen, Germany)                                                                                        |  |

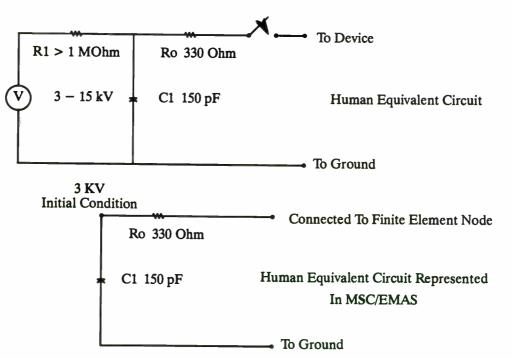

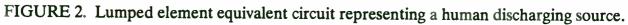

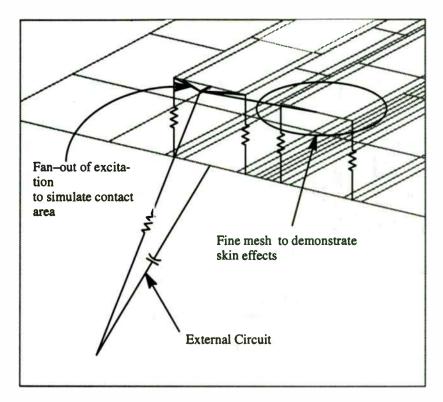

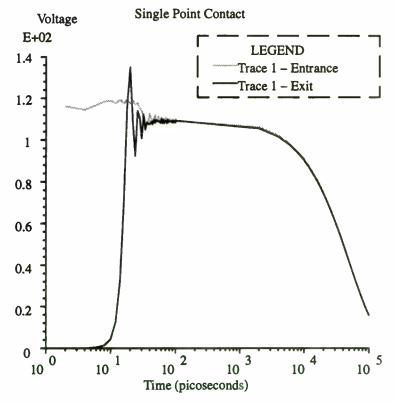

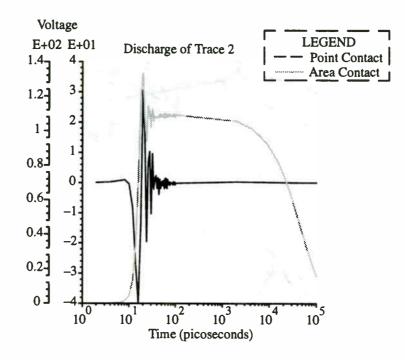

| Simulating short-duration static-discharge events in a printed-circuit board using the finite-element time-domain technique. Brian S.<br>Brown, The MacNeal-Schwendler Corp. (Milwaukee, WI)                                                            |  |

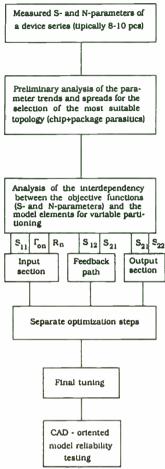

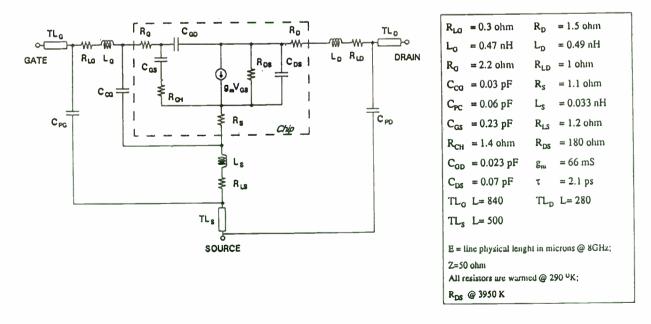

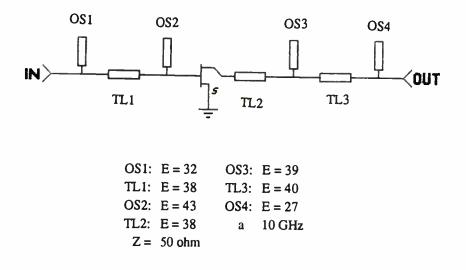

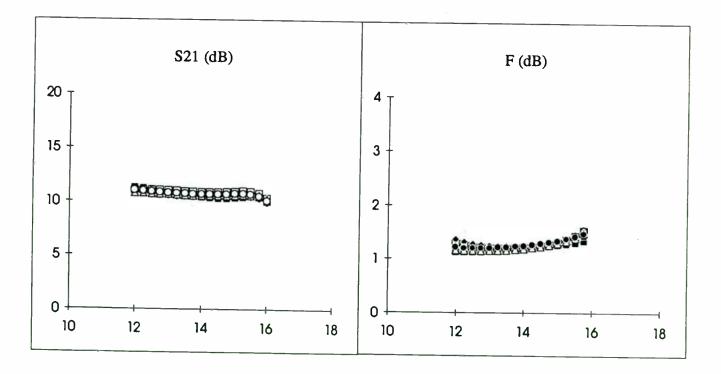

| CAD of LNAs for DBS applications from statistical modeling of pseudomorphic HEMTs. Alina Caddemi, Giusy Gambinoi, and<br>Mario Sannino, Dipartimento di Ingegneria Elettrica, Laboratorio di Elettronica per le Microonde-Viale delle Scienze (Palermo, |  |

#

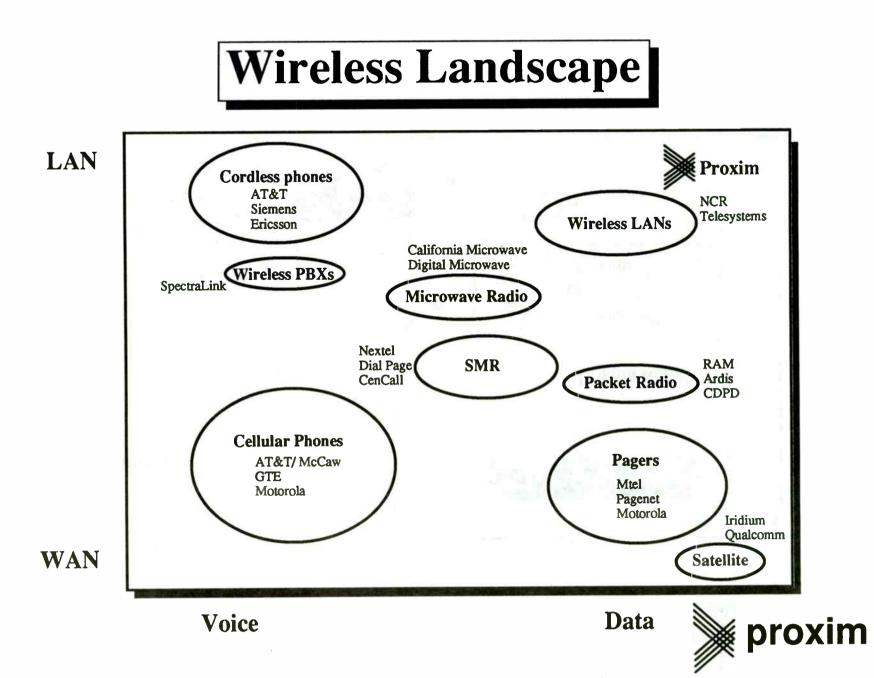

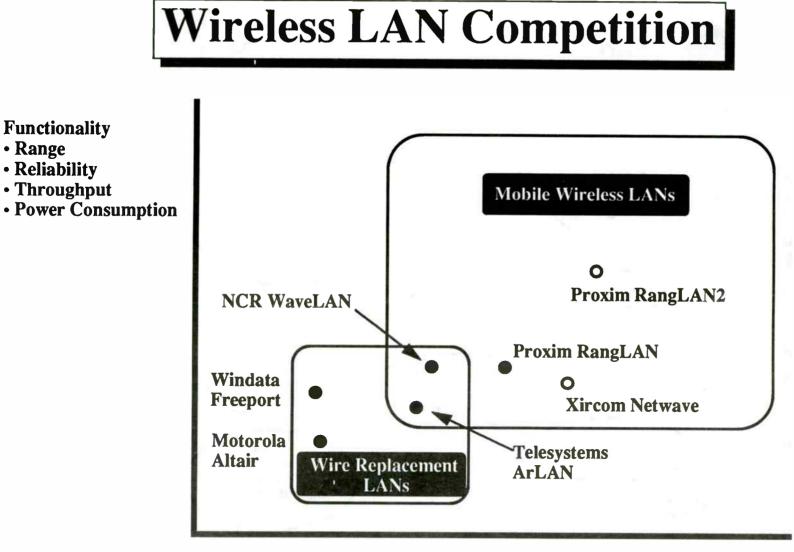

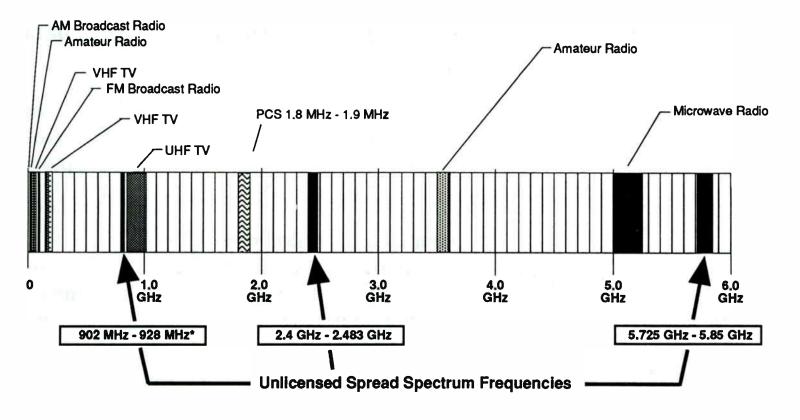

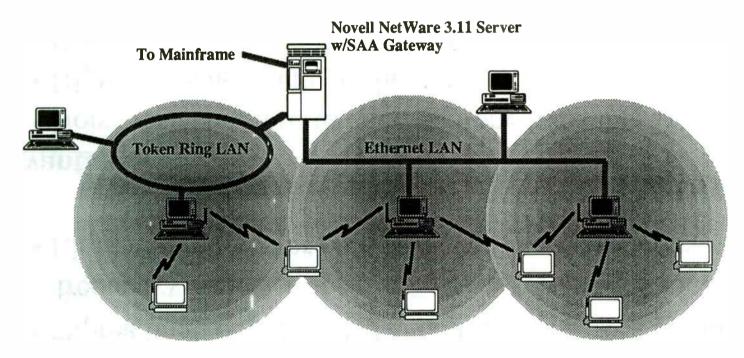

## WIRELESS DATA COMMUNICATIONS.....337

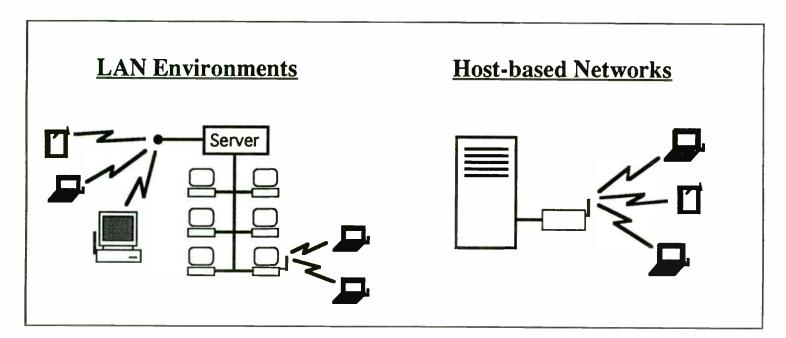

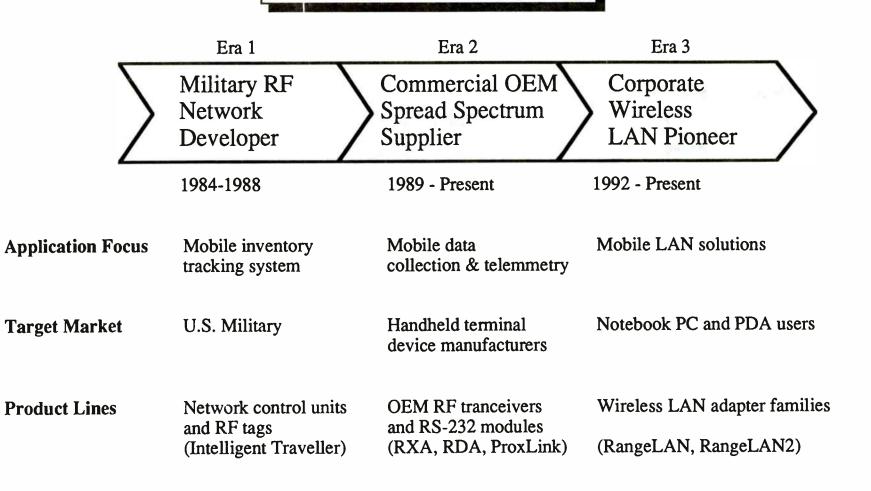

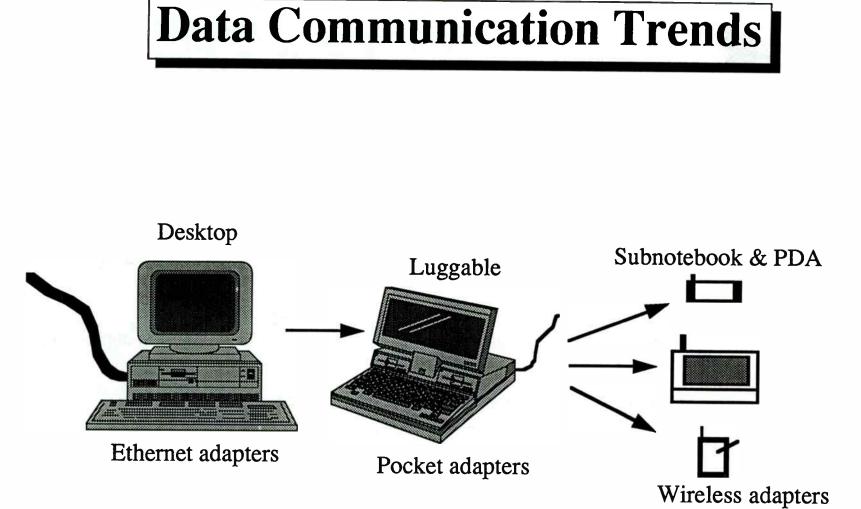

| Wireless local-area networking. Mack Sullivan, Proxim, Inc. (Mountain View, CA)                                                                                                                                                                                              |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Wireless LANs in industrial environments. Algis Juodikis, Juodikis & Associates (Newport Beach, CA)                                                                                                                                                                          |

| Flexible UHF data-transmission system with broad tuning range. Thilo Lenhard, Albert Heuberger, Rainer Perthold, and Ludwig<br>Wallrapp, Fraunhafer Institut fur Integrierte Schaltungen (Erlangen, Germany); Max Heckl, Hetronix Steuersysteme GmbH<br>(Langquaid, Germany) |

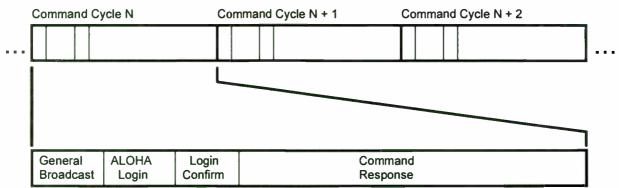

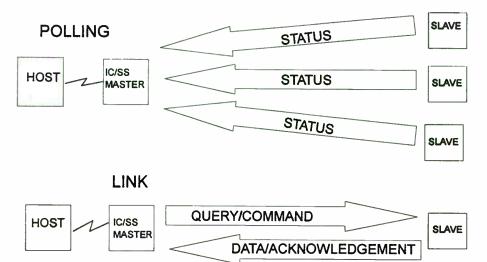

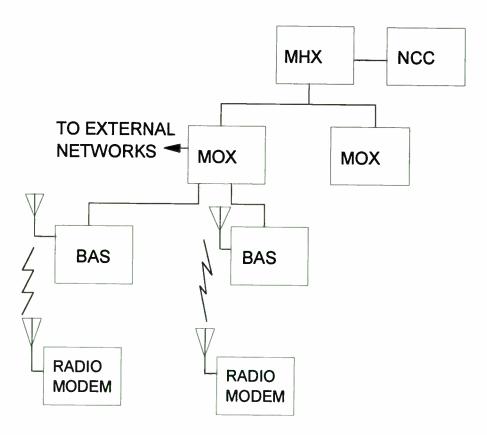

| Command-response data-link layer for wireless mobile communications. Stephen Hockaday, S. Ron Oliver, Jeffrey Gerfen, William Hartin, Steve Caminiti, and Brian Young, College of Engineering, California Polytechnic State University (San Luis Obispo, CA)                 |

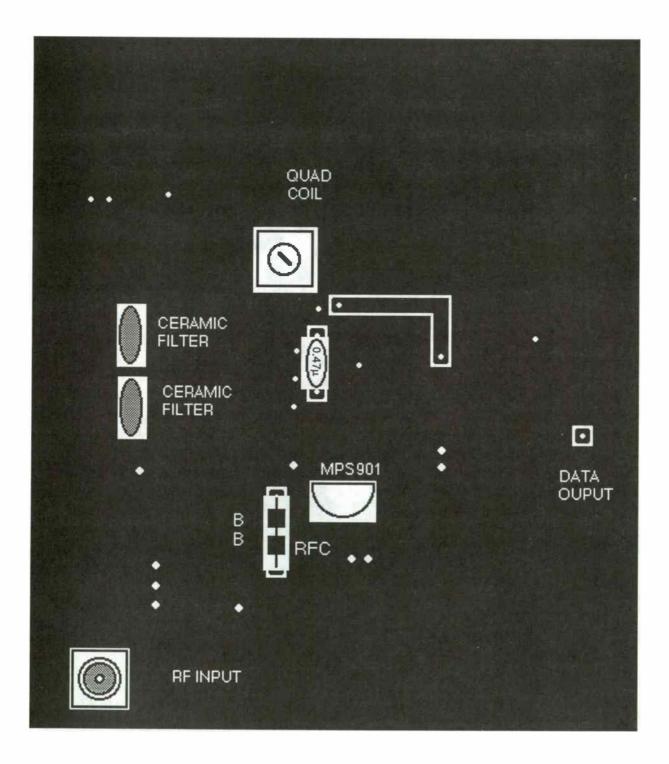

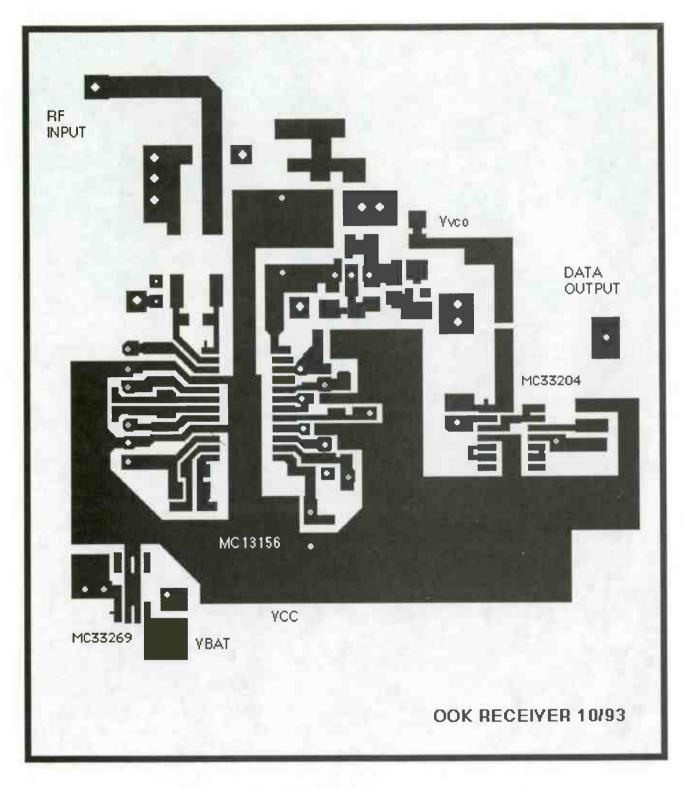

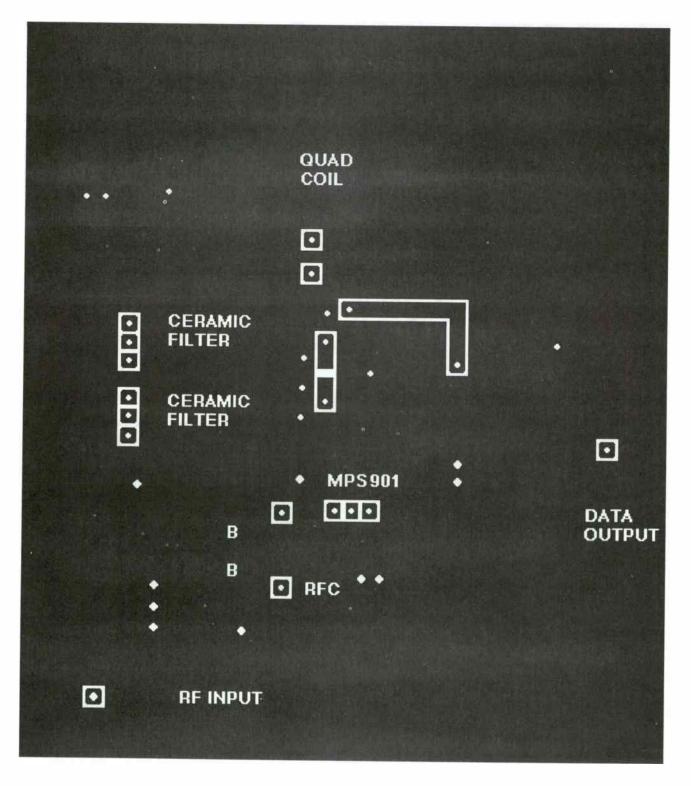

| An OOK-modulation data receiver for periodic Part 15 operation using a low-cost silicon monolithic integrated circuit. Sam Marshall and Harry Swanson, Motorola, Inc., Semiconductor Products Sector (Tempe, AZ)                                                             |

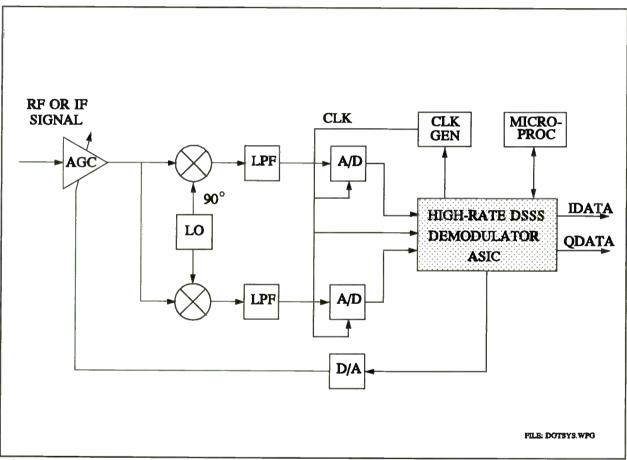

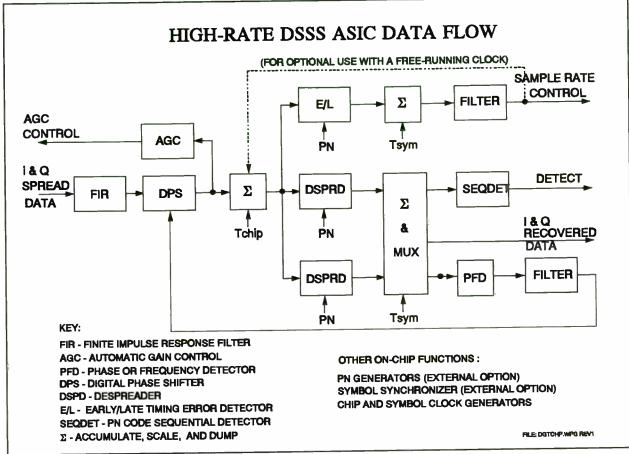

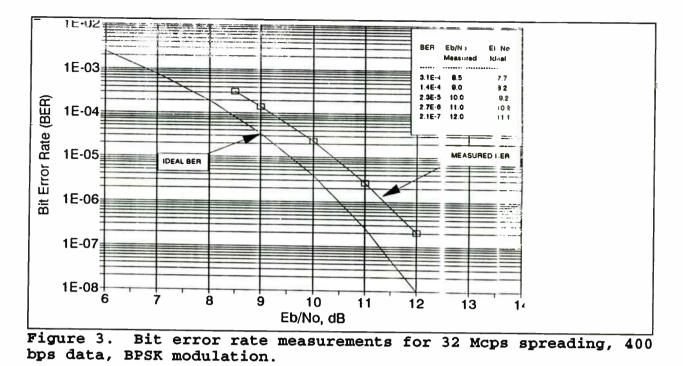

| A high-rate direct-sequence spread-spectrum demodulator ASIC. Sam Kingston, Steve Barham, Glen Rattingourd, Harold                                                                                                                                                           |

## **RFID/PERSONAL COMMUNICATIONS....405**

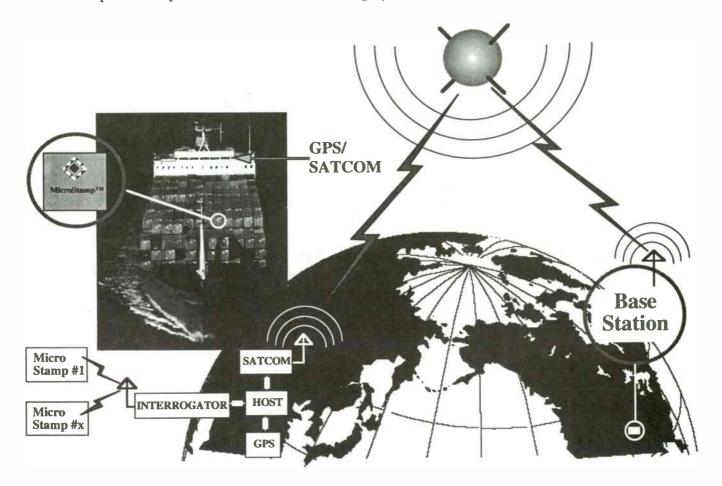

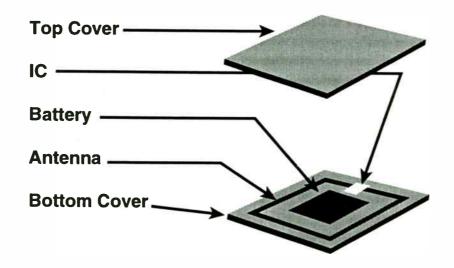

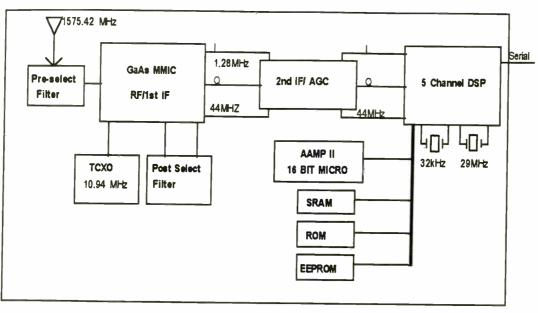

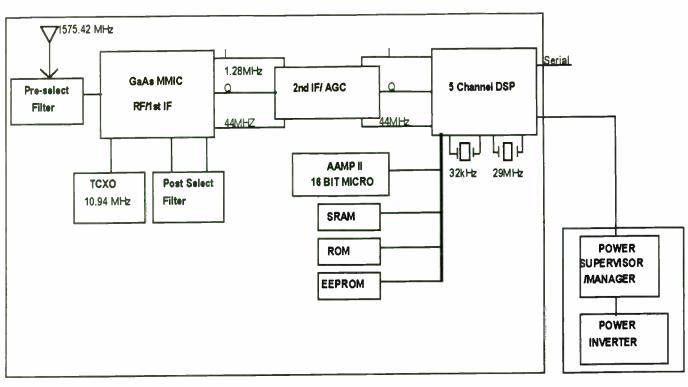

| Digital RFID enhances GPS. John R. Tuttle, Micron Communications, Inc. (Boise, ID)                                                                                                                                                                                                                                                 | 406        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

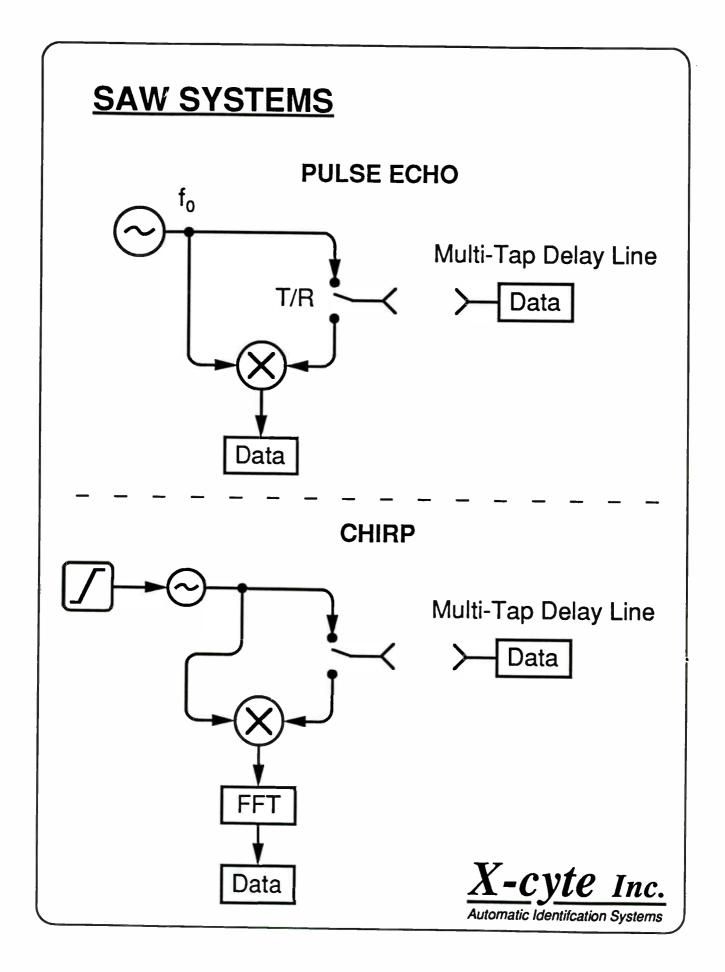

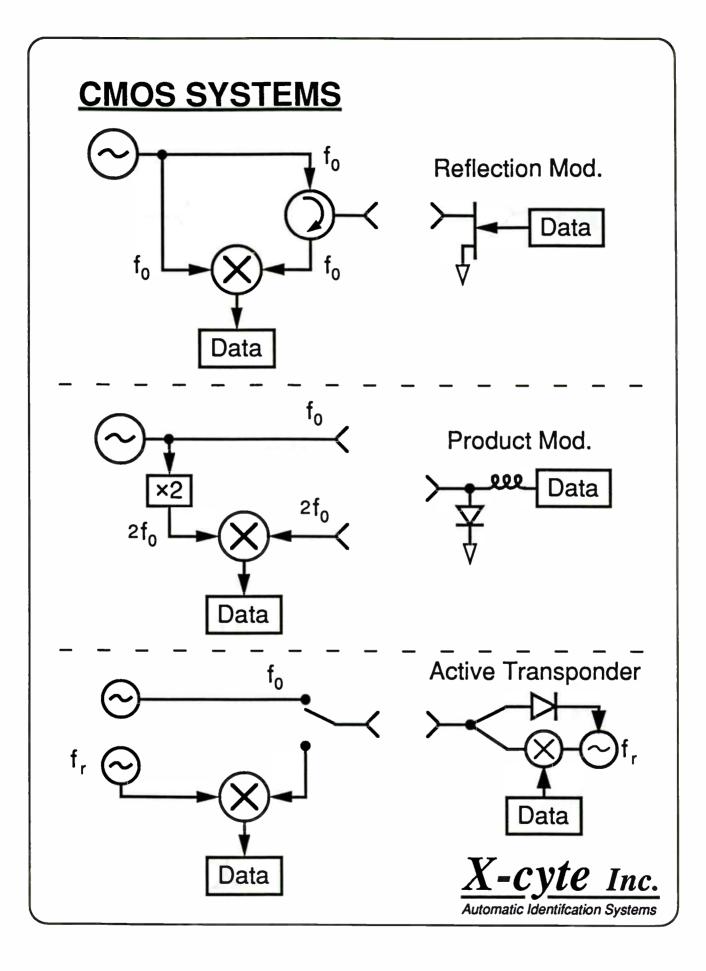

| RFID systems: SAW versus CMOS. Paul A. Nysen, X-cyte, Inc. (San Jose, CA)                                                                                                                                                                                                                                                          | 412        |

| Low-voltage RF power amplifiers for hand-held communication equipment. Rudolph van der Last, Philips Semiconductors (Eindhoven, The Netherlands)                                                                                                                                                                                   | 123        |

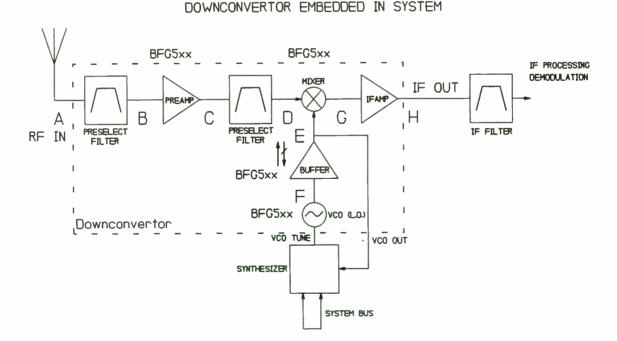

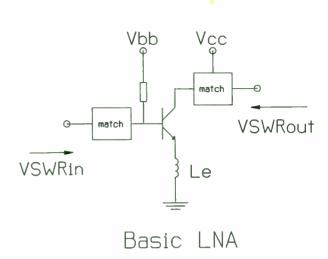

| A low-voltage receiver downconverter with discrete RF transistors. Bart Balm; Philips Semiconductors, Discrete Semiconductor Group (Slatersville, RI)                                                                                                                                                                              | 135        |

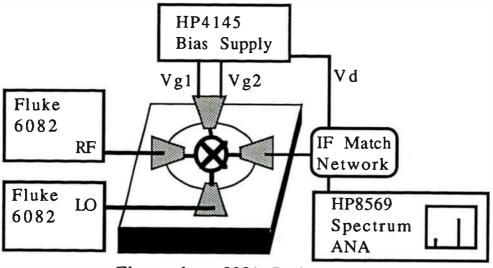

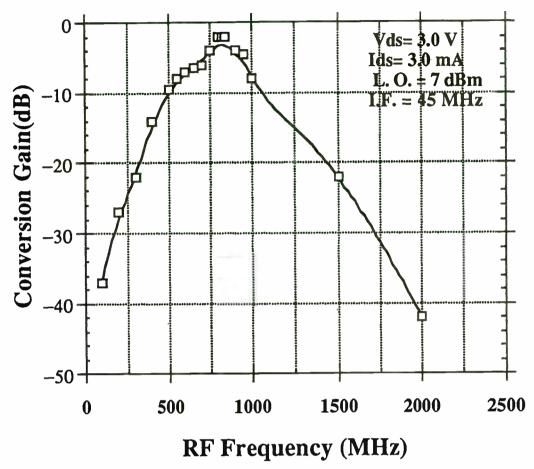

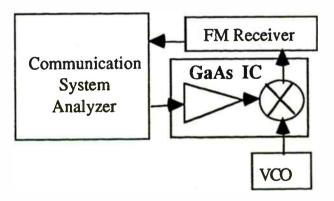

| Low-power GaAs MMIC downconverter for portable communications applications. Vijay Nair, Motorola, Inc., Phoenix Corporate<br>Research Laboratories (Tempe, AZ); Harry Swanson, Motorola, Inc., Logic and Analog Technology Group (Tempe, AZ); D.<br>Scheitlin, Motorola, Inc., Phoenix Corporate Research Laboratories (Tempe, AZ) |            |

| A new RF/microwave proximity tag system. Jonathan Schepps, David Sarnoff Research Center (Princeton, NJ)4                                                                                                                                                                                                                          | <b>162</b> |

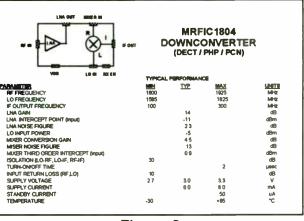

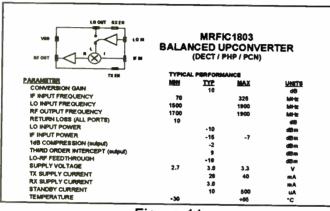

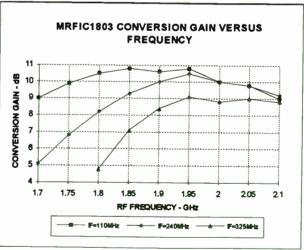

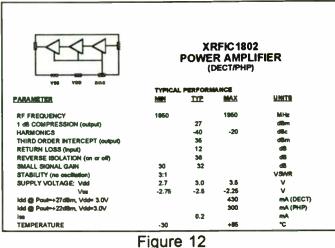

| A 1.9-GHz chip set for personal communicators. Mark Williams and Tom Schlitz, Motorola, Inc., Communications Semiconductor<br>Products Div. (Tempe, AZ)                                                                                                                                                                            | 68         |

| A Caltrans-compliant AVI system. Bill Frazee, Texas Instruments (Dallas, TX)4                                                                                                                                                                                                                                                      | 78         |

# WLAN AND DIGITAL WIRELESS APPLICATIONS.....479

| Microwave component requirements for personal communications and wireless LAN applications. Ganesh R. Basawapatna, Encore<br>Communications Corp. (Englewood, CO)                                                                                                                                                   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| The AC power line as a wireless medium. Michael Propp, Adaptive Networks, Inc. (Cambridge, MA)                                                                                                                                                                                                                      |

| Increasing spectral efficiency in personal communications systems. Andrea Goldsmith and Pravin Varaiya, University of California at<br>Berkeley (Berkeley, CA)                                                                                                                                                      |

| Spread-spectrum systems: Evaluating performance criteria for your application. Dean Gaston, Utilicom, Inc. (Goleta, CA)                                                                                                                                                                                             |

| TLE-95 and TLC bridge the microwave and digital worlds. Jack Daniels, Taconic Plastics Ltd. (Petersburg, NY)                                                                                                                                                                                                        |

| A new modulation/radio technique for wireless applications. Yanpeng Guo, Digital Communications Research Laboratory, Depart-<br>ment of Electrical Engineering, University of California at Davis (Davis, CA); Kamilo Feher, Department of Electrical Engineering,<br>University of California at Davis (Davis, CA) |

# COMPUTER-AIDED ENGINEERING, II....532

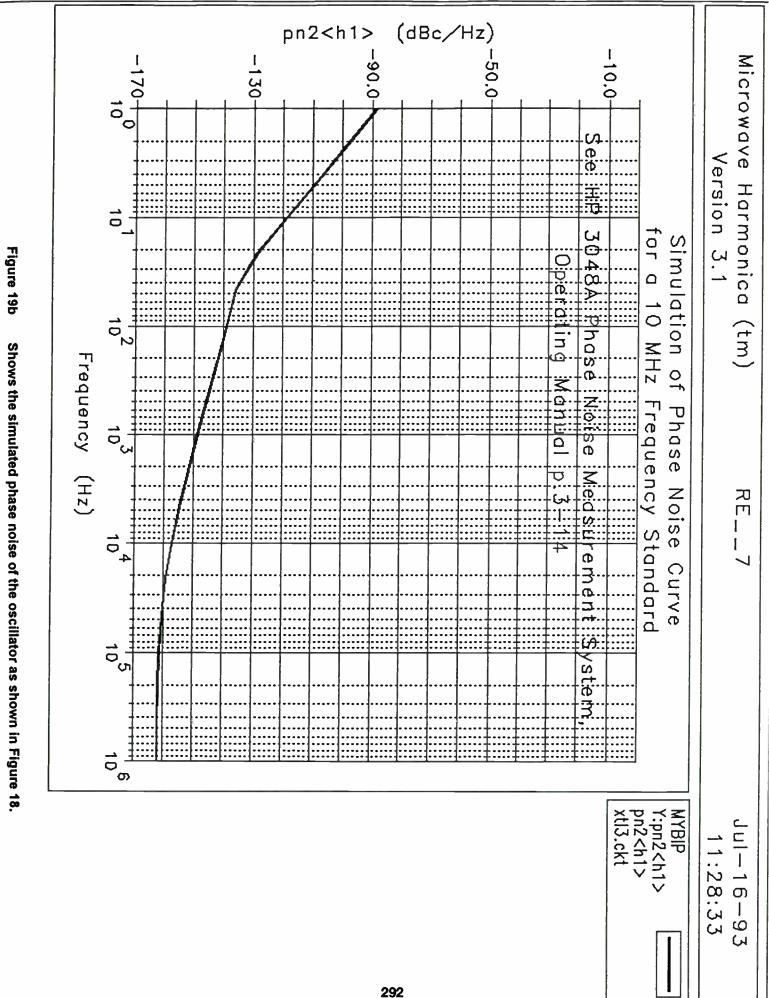

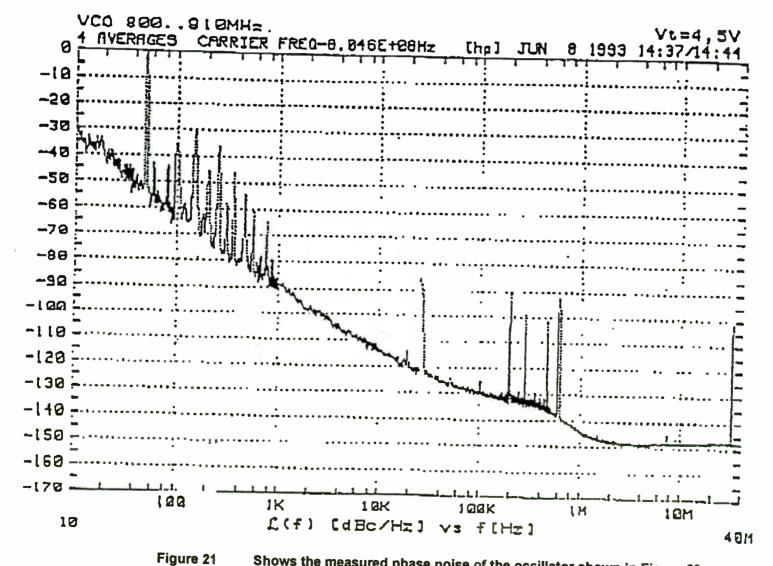

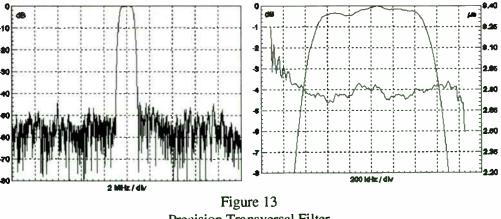

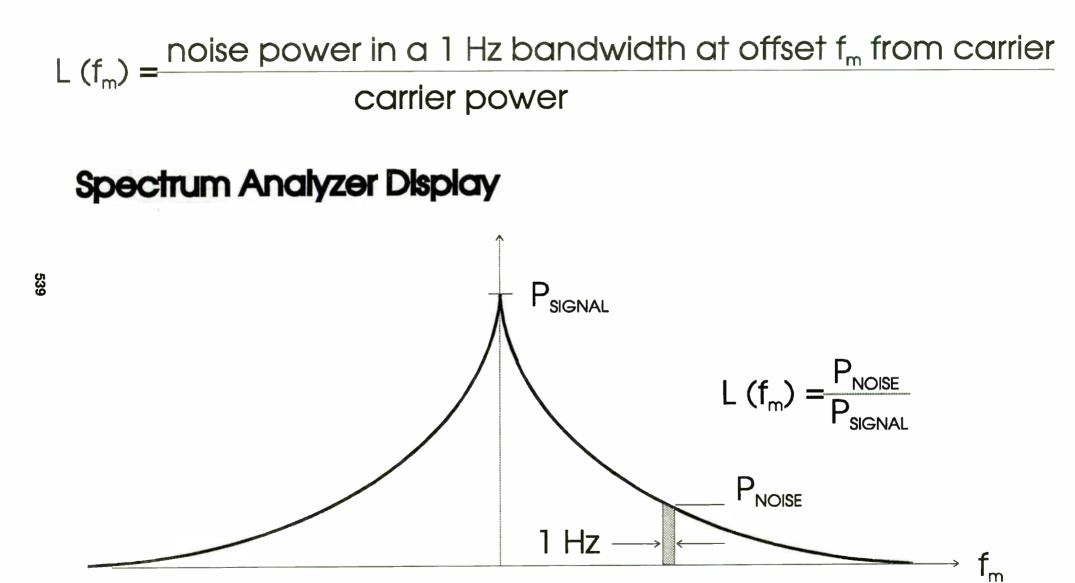

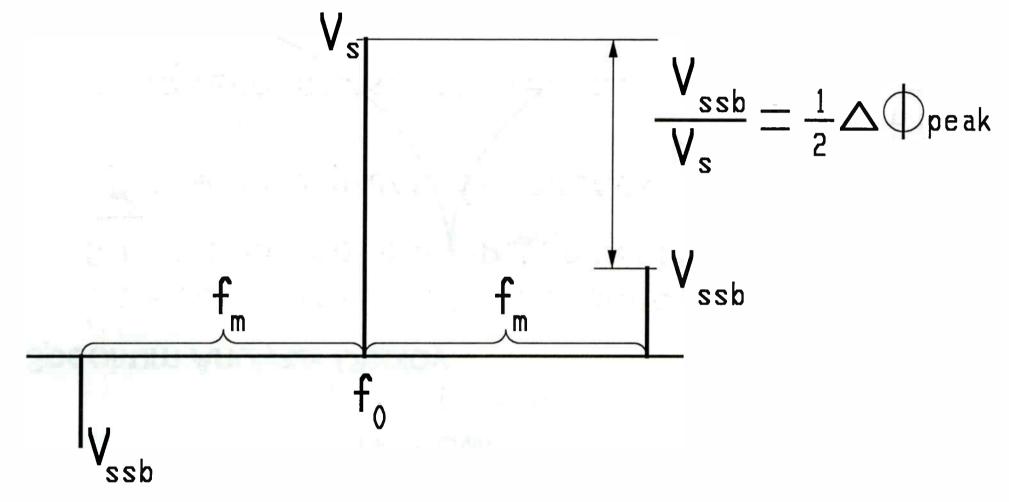

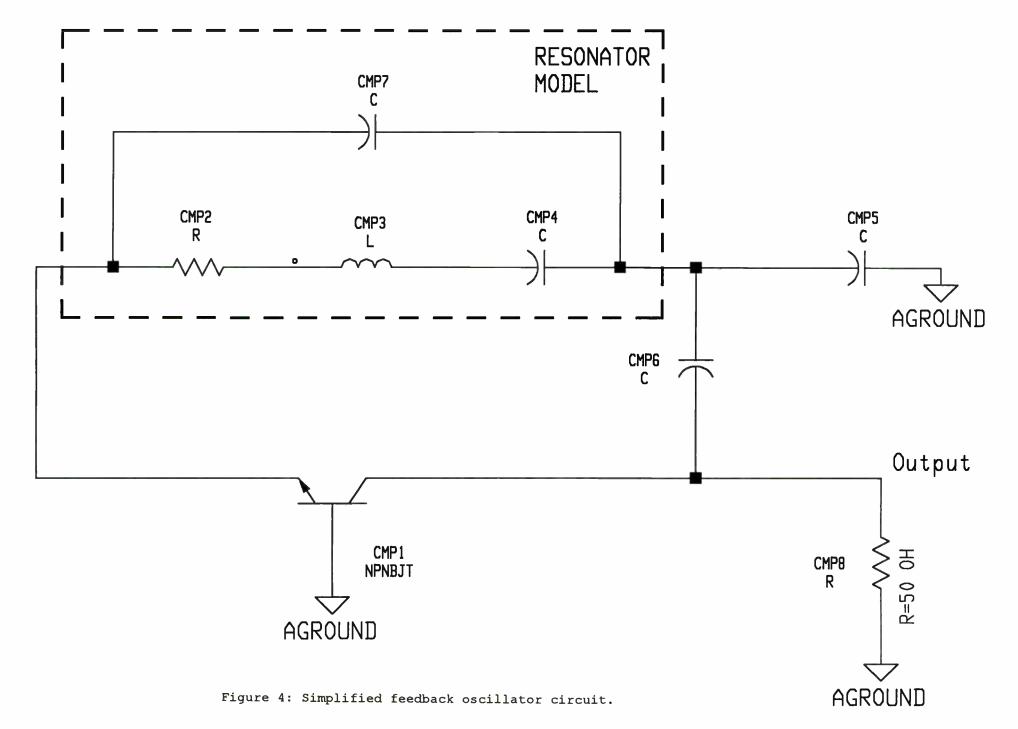

| Simulating oscillator phase noise. Andy Howard, Hewlett-Packard Co., Santa Rosa Systems Div. (Santa Rosa, CA)                                                                                                        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Where did RF ground go? Jaime Tenedorio, Samsung Microwave Semiconductor (Milpitas, CA)                                                                                                                              |

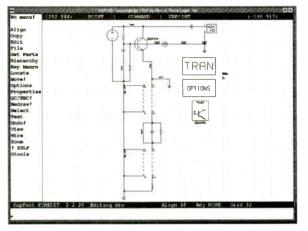

| Use of computer-aided engineering in spread-spectrum design. Gary Mitchell, NOVA RF Systems, Inc. (Vienna, VA)                                                                                                       |

| EDA applications in CDMA system design. R. Kyle Martin and Jeremy Bunting, HP-EEsof, Inc. (Westlake Village, CA)                                                                                                     |

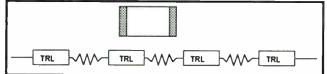

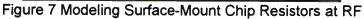

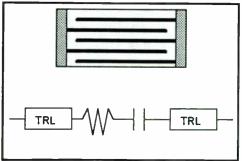

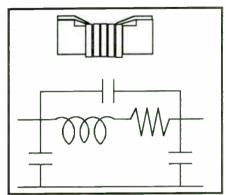

| A transmission-line model for single-layer capacitors. Mark Ingalls, Dielectric Laboratories, Inc. (Cazenovia, NY); Paul Romanowski,<br>Martin Marietta (Utica, NY); Gordon Kent, Syracuse University (Syracuse, NY) |

| RF printed-circuit layouts: A practical tutorial for wireless applications. Allan Coon, Sr., RF Monolithics, Inc. (Dallas, TX)                                                                                       |

# AUTOMOTIVE ELECTRONICS/SATELLITE COMMUNICATIONS....595

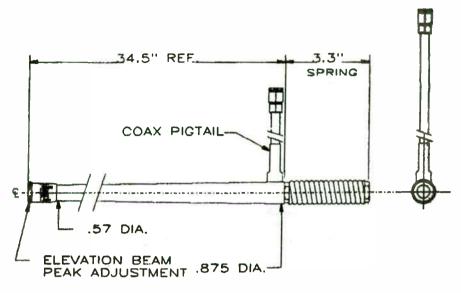

| Two vehicular antennas for the mobile satellite service. Charles D. McCarrick, Seavey Engineering Associates, Inc. (Cohasset, MA)                                                                               | 6  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Seventy-seven-GHz automotive radars: The markets, technologies, and production costs. Lamberto Raffaelli, Alpha Industries, Inc.<br>(Metheun, MA)600                                                            |    |

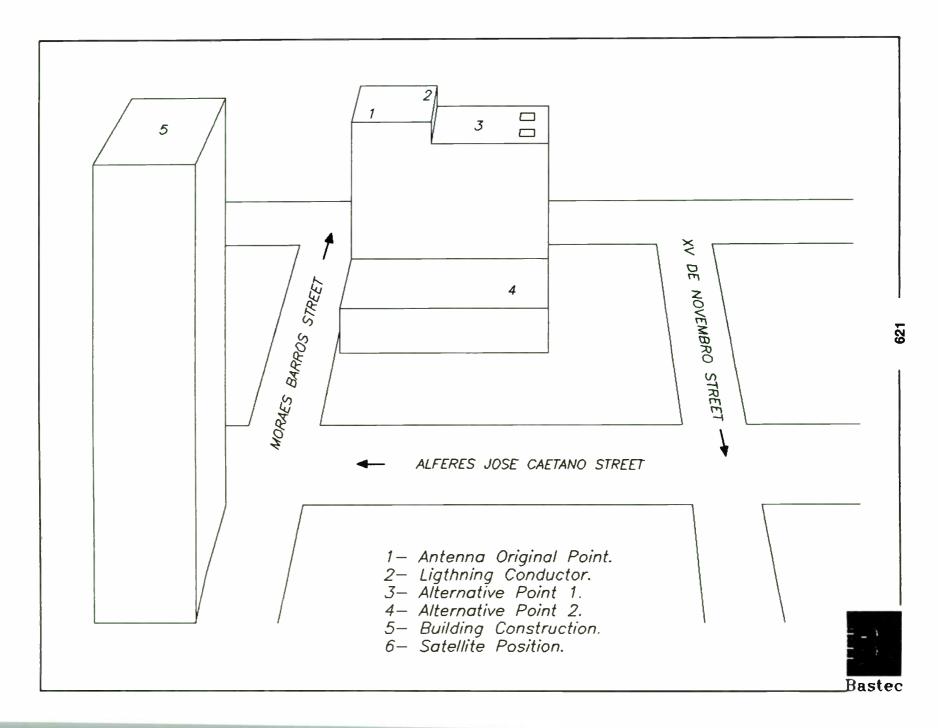

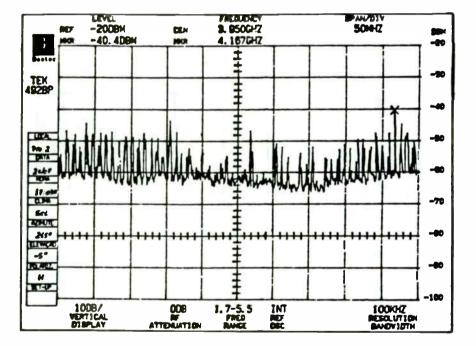

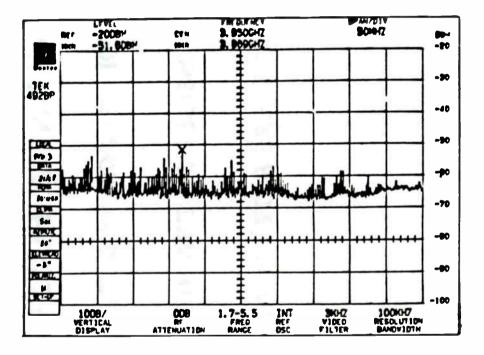

| Study of automotive electronic interference in the Brazilian satellite system. Cladimir Jose Benvenutti, Mauricio Anastacio Costa,<br>and Edmar Munhoz Pensutti, BASTEC (Curitiba, Parana, Brazil)607           | 7  |

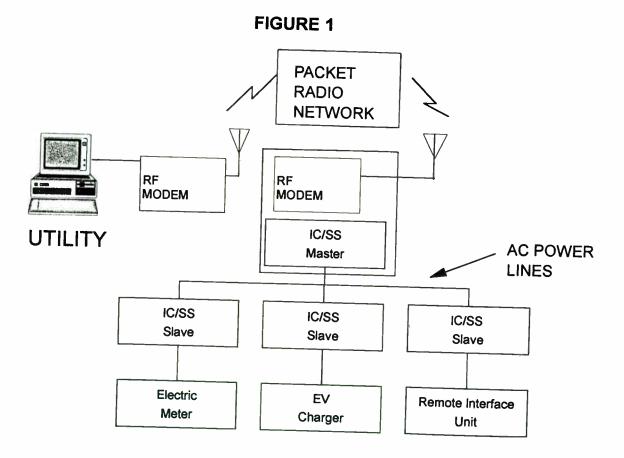

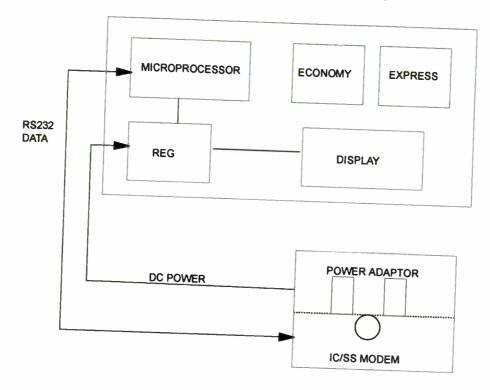

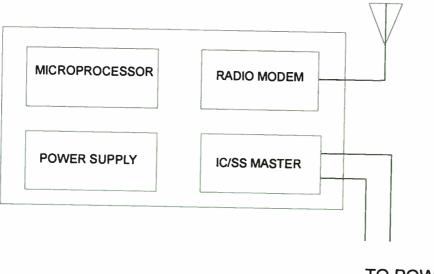

| Electric-vehicle-charger demand-side-management communications system. Mike Murphy, CYPLEX (Nashua, NH)                                                                                                         | 8  |

| The Globalstar Mobile Satellite System for worldwide personal communications. Robert A. Wiedeman, Loral-Qualcomm Satellite<br>Services, Inc. (Palo Alto, CA); Andrew J. Viterbi, QUALCOMM, Inc. (San Diego, CA) | 0  |

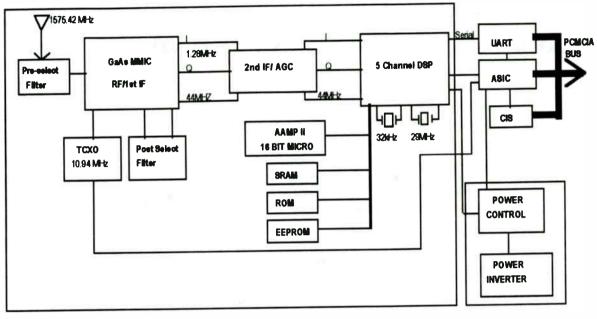

| NavCard: GPS technology in a PCMCIA format. Terry Dawson, Stuart Thomson, and Ed Vignone, Rockwell International, Tele-<br>communications Group (Newport Beach, CA)                                             | 1  |

| Electronically-steerable millimeter-wave automobile collision-warning antennas with tunable ceramic phase shifters. V.K. Varadan and V.V. Varadan, Pennsylvania State University (University Park, PA)          | 18 |

# **Analog and Mixed-Signal ICs for Wireless Communications**

Session Chairperson: Mark McDonald, Wireless Communications, National Semiconductor (Santa Clara, CA) A 3-V RF front-end GaAs MMIC for DCS-1800 cellular communications. Patrick Rousseau, Nathalie Caglio, Etienne Delhaye, Denis Masliah, Didier Meignant, and Eric Puechberty, LEP/Philips Micro-Push-pull receiver input amplifier stages—The solution to intermod problems. Hans Sapotta, TEMIC, Telefunken Microelectronic GmbH (Heilbronn, Germany)......10 A low-voltage IC front-end for cellular radio. Sheng Lee and Alvin A monolithic quadrature demodulator and digitizer for PSK and QAM applications. Jim Marsh, Scott Williams, and Brent Jensen, Tektronix, Inc., Microelectronics Div. (Beaverton, OR); Simon Atkinson and Jonathon Strange, Mosaic Microsystems Ltd. (Kent, England); Dave May, Tom Bilotta, and Fred Harris, TV/COM Inter-Fractional-N frequency synthesizers for next-generation cellular and wireless applications. Wing S. Djen and Daniel J. Linebarger, Philips

A 1-V CMOS FSK receiver for wireless applications. David Shiels and Evert Dijkstra, Centre Suisse d'Electronique et de Microtechnique S.A. (Neuchatel, Switzerland)......20

# A 3 V RF FRONT-END GaAs MMIC FOR DCS 1800 CELLULAR COMMUNICATIONS

# Patrick ROUSSEAU, Nathalie CAGLIO, Etienne DELHAYE, Denis MASLIAH, Didier MEIGNANT, Eric PUECHBERTY

LEP / Philips Microwave Limeil 22, avenue Descartes, 94453 Limeil-Brévannes Cedex, France tel. 33.1.45.10.67.89 - Fax 33.1.45.10.69.53

#### Abstract

An integrated class II RF front-end including a 500 mW power amplifier has been designed and fabricated for the Digital Cellular Communication System operating at 1800 MHz (DCS 1800) using the standard Philips Microwave Limeil (PML) enhancement and depletion modes ER07AD process. The IC operates at 3 V supply voltage and includes RF functions of both the Rx (Receive) and Tx (Transmit) chains. This paper describes the design and experimental performance of the circuit, which constitutes, to the authors' best knowledge, the first monolithic 3 V RF front-end for DCS 1800 cellular communications.

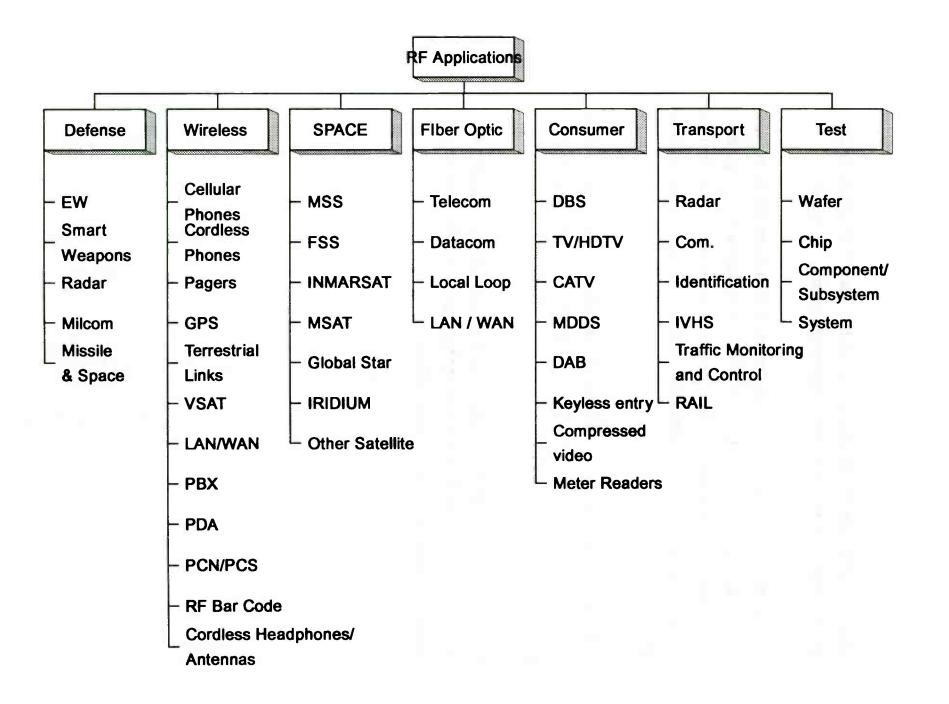

#### Introduction

RF Integrated Circuits for cellular communications will constitute a considerable market for the semiconductor industry in the 1995-2000 period, where GaAs technology will play an important role. Indeed, it is now widely considered that GaAs MESFET technology is particularly well suited for the implementation of the Tx power stages, where high efficiency amplification is required, and several Power Amplifiers (PA) have already been reported at L-band. This holds particularly true since the volume and weight reduction of the mobile terminals leads the battery supply voltages to decrease steadily to 3 V. Arguments for a monolithic implementation of a complete Rx-Tx frontend are manifold :

- ➤ a power stage uses transistors with high periphery even at medium output power (0.5 to 2 W) and therefore occupies a relatively large area of semiconductor, typically 2 to 3 mm<sup>2</sup> for a 0.5 W three-stage power amplifier at L-band [1]. The integration of low power RF functions (Low Noise Amplifier, Local Oscillator and even Rx and/or Tx mixers) can therefore be implemented at a marginal cost in terms of semiconductor area, thus resulting in a cheap one-package solution for an integrated RF front-end

- ▶ In almost all cellular communication standards, Rx and Tx channels use 2 separate frequency bands and are alternatively switched. They never operate simultaneously, which excludes cross-coupling interference problems.

- GaAs enhancement mode MESFET technology leads to excellent power consumption performance allowing the use of low cost plastic packaging required for these consumer products.

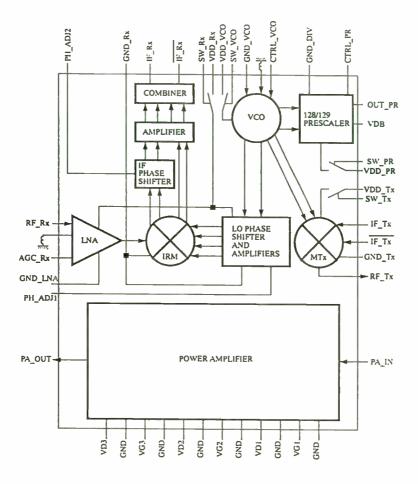

#### **General architecture**

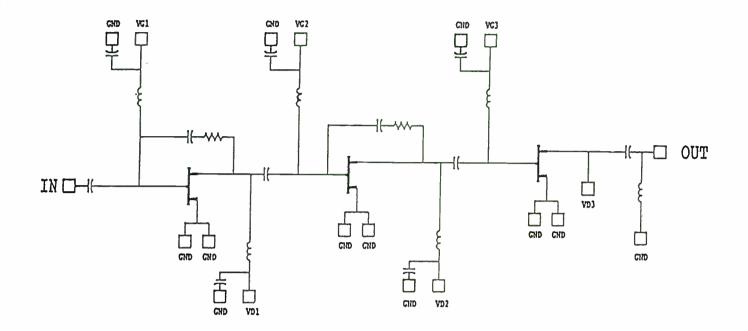

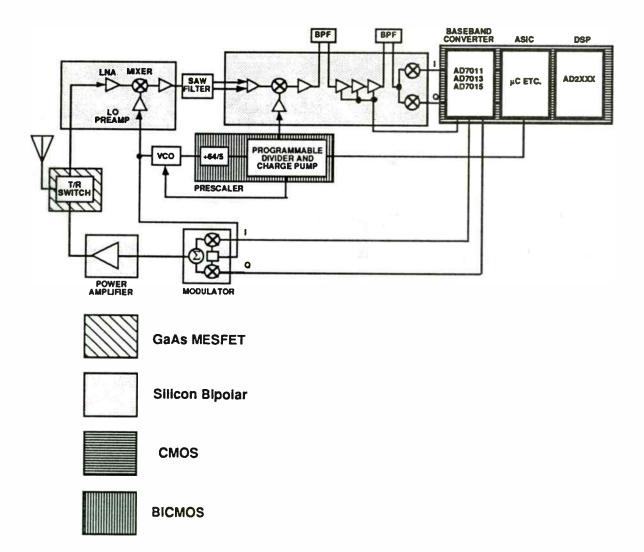

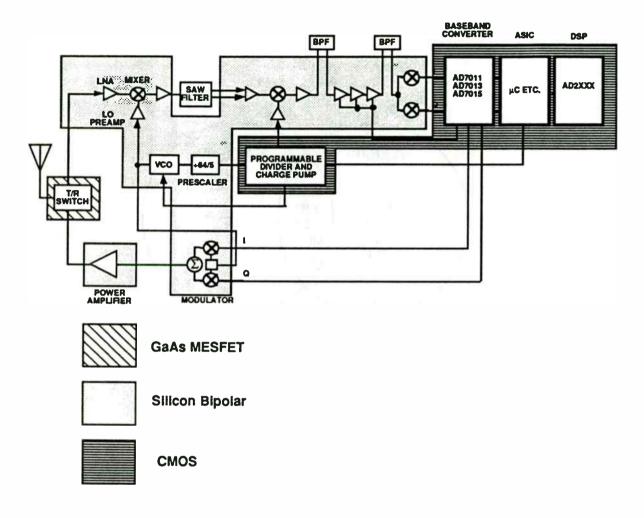

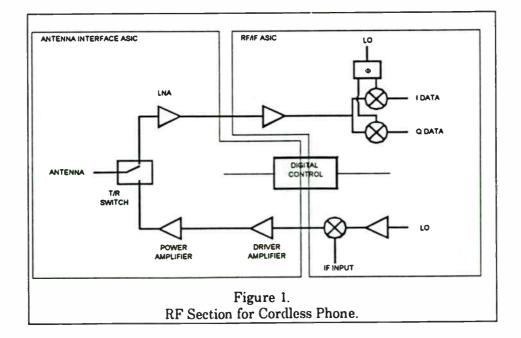

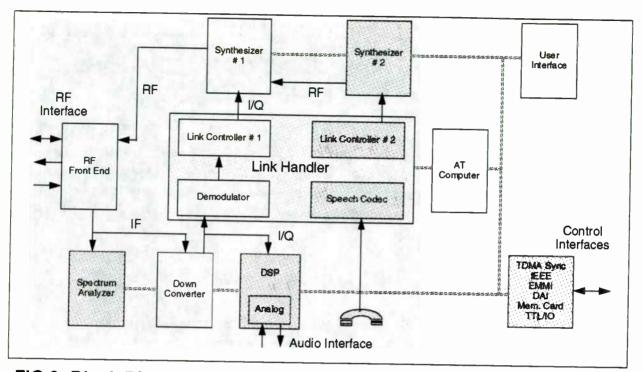

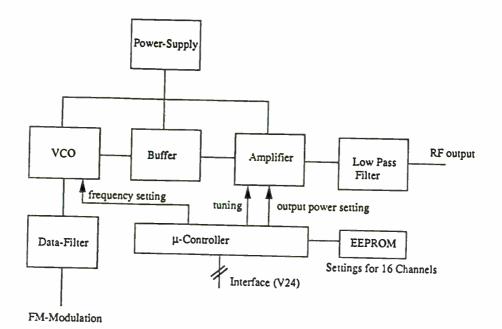

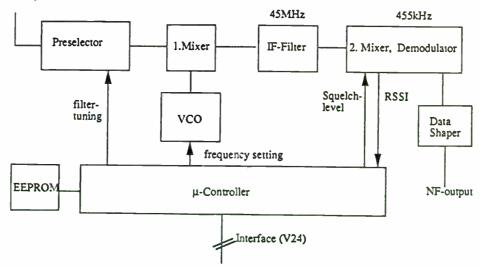

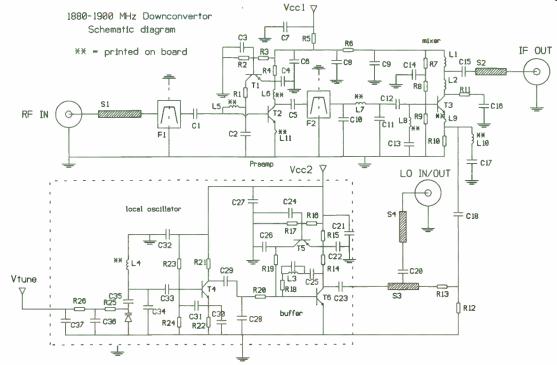

The block diagram of the designed RF front-end is shown in Figure 1. In addition to the Power Amplifier, the Tx stage includes an up converter (MTx) mixing the Local Oscillator frequency LO and the Intermediate Frequency IF\_Tx, which is set to 400 MHz. The LO frequency is generated by a Voltage Controlled Oscillator (VCO); it is tuned by an external resonator into a frequency plan ranging from 2110 MHz to 2185 MHz. An external filter is inserted between the MTX output RF\_Tx and the PA input PA\_IN in order to remove the signals generated in the image bandwith from 2510 MHz to 2585 MHz.

The Rx stage consists of a Low Noise Amplifier (LNA) and an Image Reject Mixer (IRM). The RF input RF\_Rx has a bandwidth from 1805 MHz to 1880 MHz, while the IF output IF\_RX is set to 300 MHz, thus resulting in a LO frequency in the range of 2105-2180 MHz. Therefore, as the same VCO is used for both Tx and Rx modes, LO frequencies between 2105 MHz and 2185 MHz have to be available.

Moreover, a 128/129 dual-modulus prescaler is implemented on chip in order to generate from the LO frequency an output signal of around 17 MIIz, which is compatible with standard synthesizers.

The supply voltages of the Rx and Tx chains are alternatively switched off by depleted FETs controlled by an external signal.

#### **Circuit** fabrication

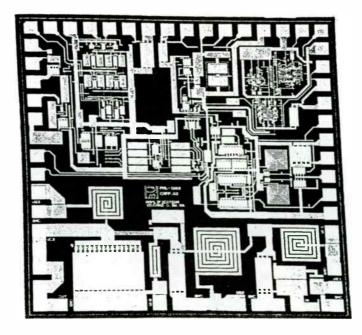

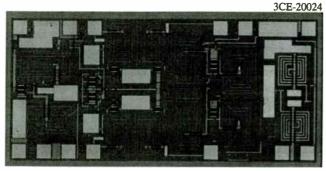

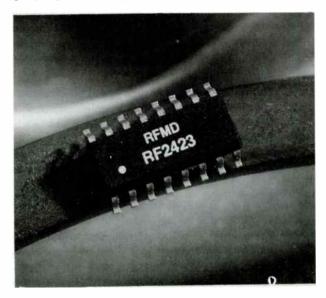

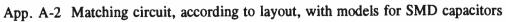

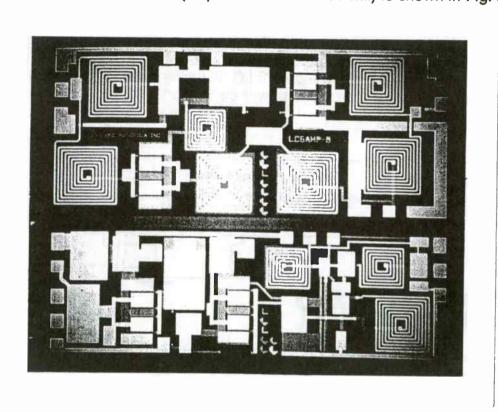

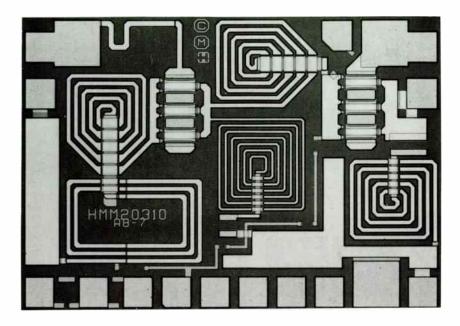

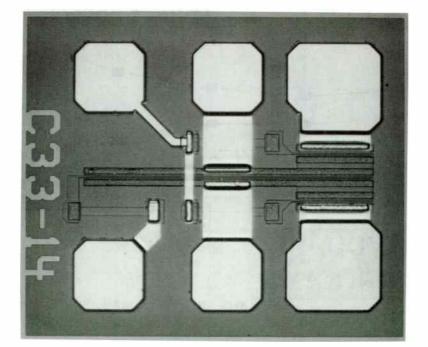

The DCS 1800 RF front-end has been fabricated using PML's 0.7  $\mu$ m MESFET ER07AD process. This process uses 3" LEC wafers, gate recessing, Si<sup>+</sup> implantation, boron isolation, standard photolithography, dry etching and enhanced lift-off techniques. It is especially suited for low power L-band to C-band mixed analog/digital applications. Enhancement mode transistors (E-FET) and depletion mode transistors (D-FET) are available in this process, which both have a typical F<sub>T</sub> of 17 GHz. The E-FET threshold voltage is V<sub>t</sub> = 0.175 V and the drain current is 50 mA/mm at Vgs = 0.7 V. The D-FET, which is mostly dedicated to power applications, has a threshold voltage of -2.0 V and an associated drain current of 200 mA/mm at Vgs = 0 V. A photograph of the IC is shown in Figure 2, the chip size is 2.5 mm x 2.5 mm.

#### **Power Amplifier**

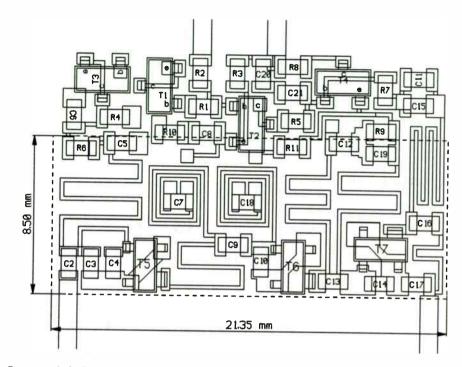

The PA design is designed to reach an output power of over 27 dBm and a Power-Added Efficiency (PAE) higher than 30 % in the DCS band (1710 MIIz-1785 MIIz) under a 3.3 V supply voltage. The input power at PA\_IN is set to 0 dBm.

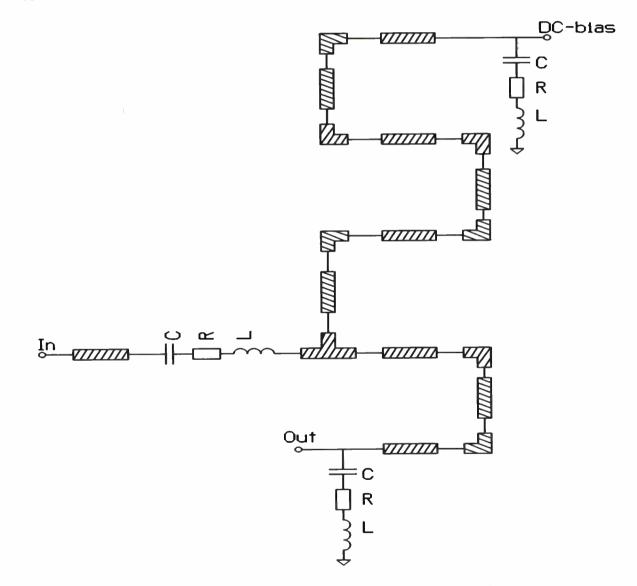

The design of the three-stage PA is based on the high power-added efficiency of the D-FET in saturated class-AB and makes use of harmonic enhancement for the interstage matching circuits (Figure 3). The sizes of the D-FETs are fixed to insure power output capability as well as saturation. Feedback circuits are positioned between the drain and the gate of the depleted transistor in order to insure low frequency stability. The last output matching network is chosen to be implemented externally because of the 9 mm gate width output transistor in order to lower losses. Furthermore, the power gain of the PA can be adjusted by applying gate voltages between -2 V and -1 V on the nodes VG1, VG2 and VG3 for a total gate current less than 0.5 mA.

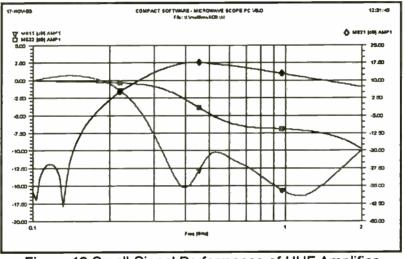

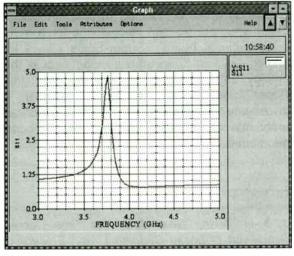

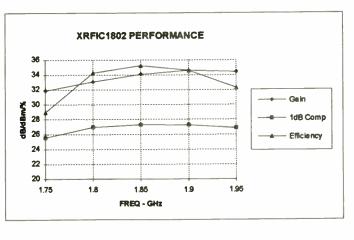

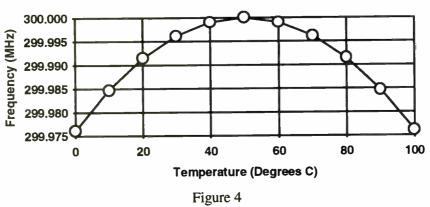

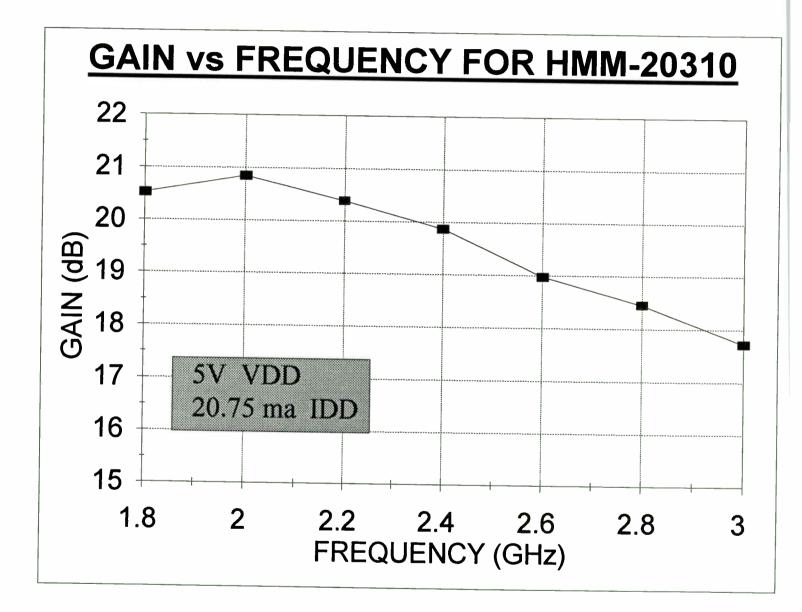

The PA performance has been measured at 1.8 GHz under 3.3 V and the results are presented in Figure 4. For 0 dBm input power, the measured output power is around 27 dBm and the PAE is higher than 34 %.

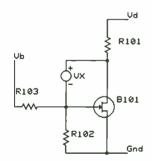

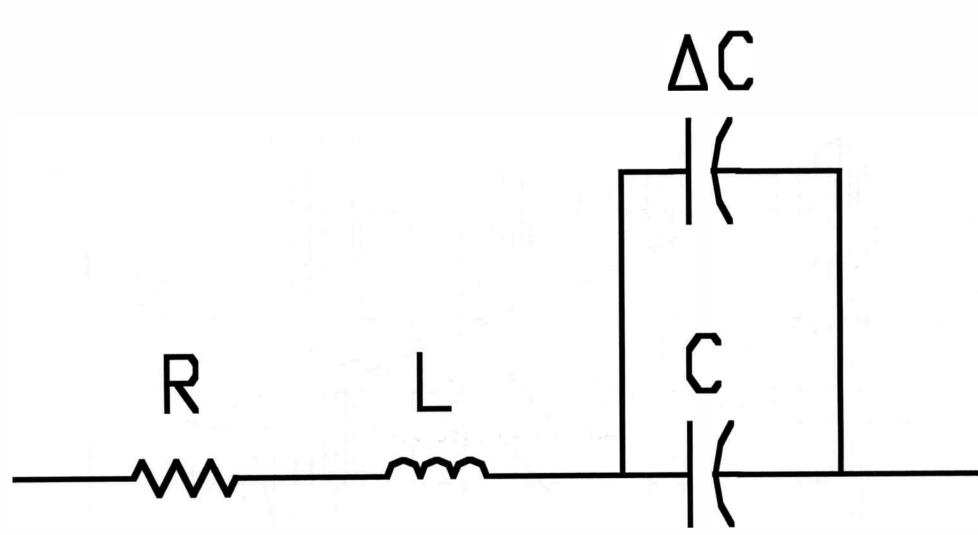

#### <u>Tx stage</u>

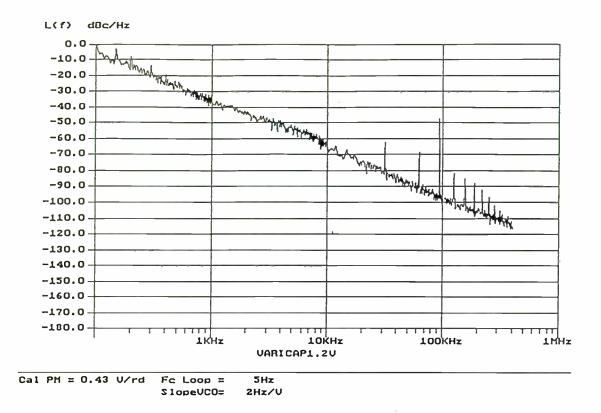

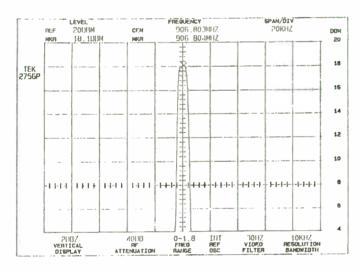

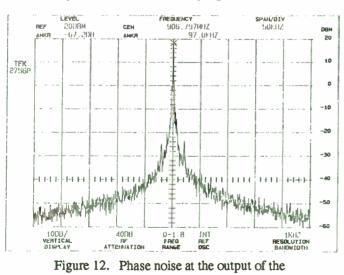

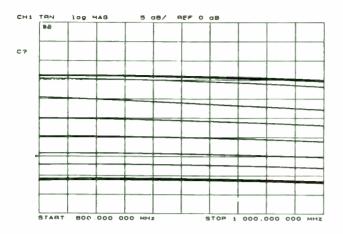

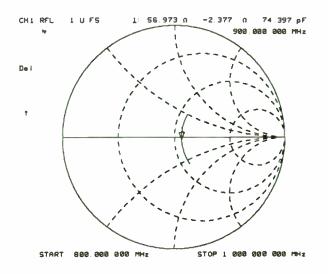

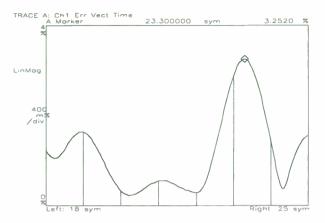

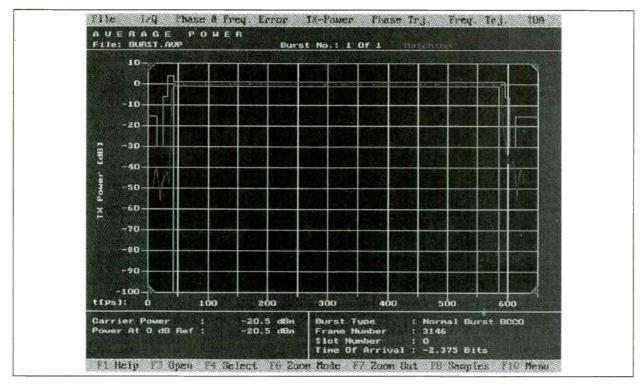

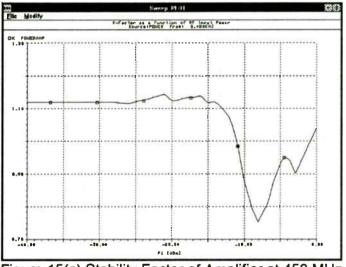

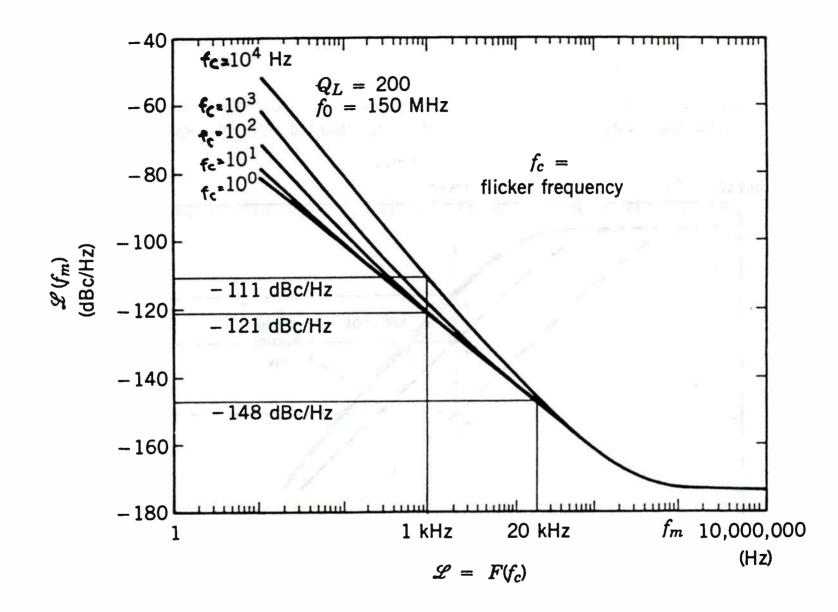

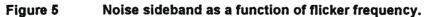

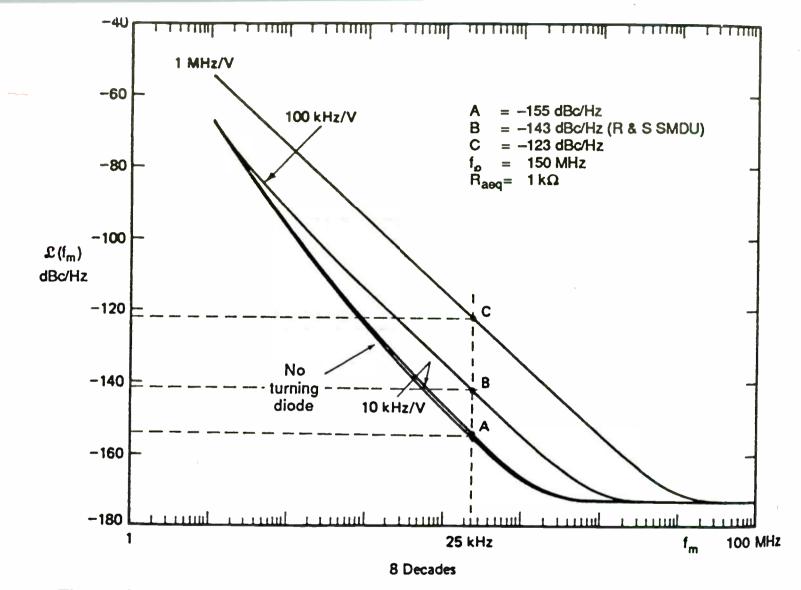

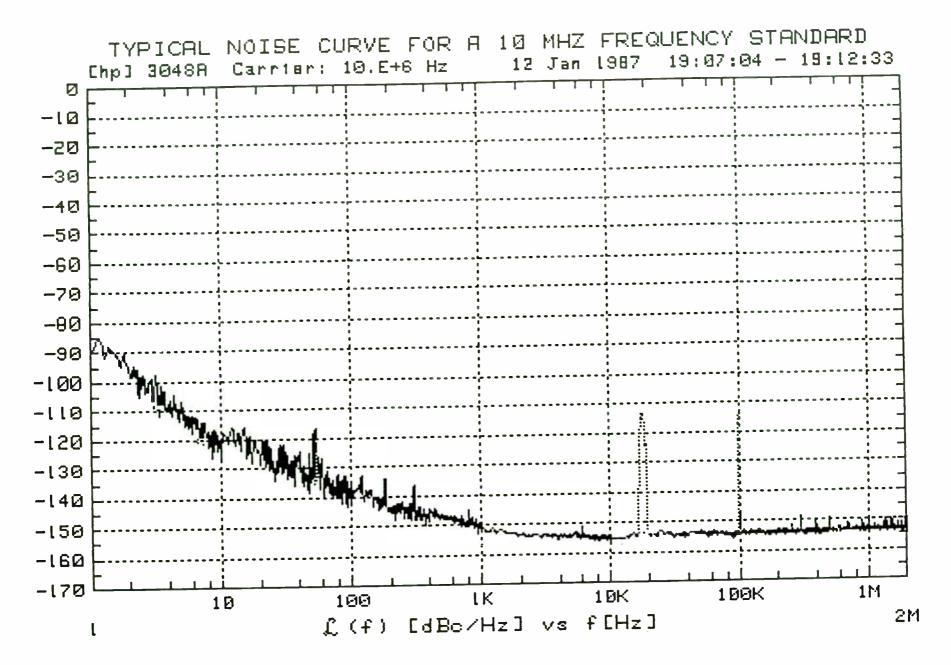

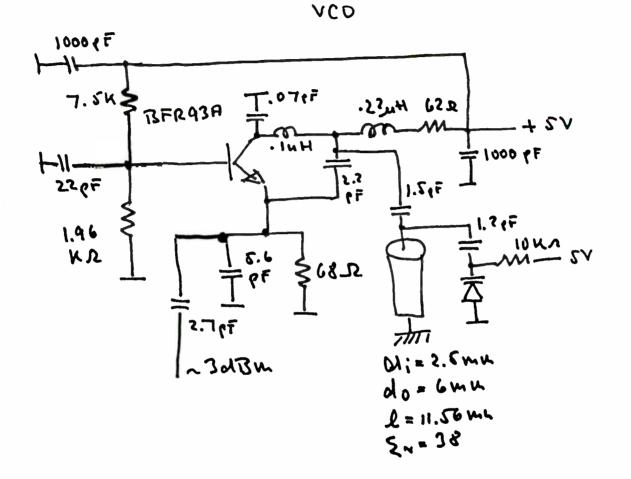

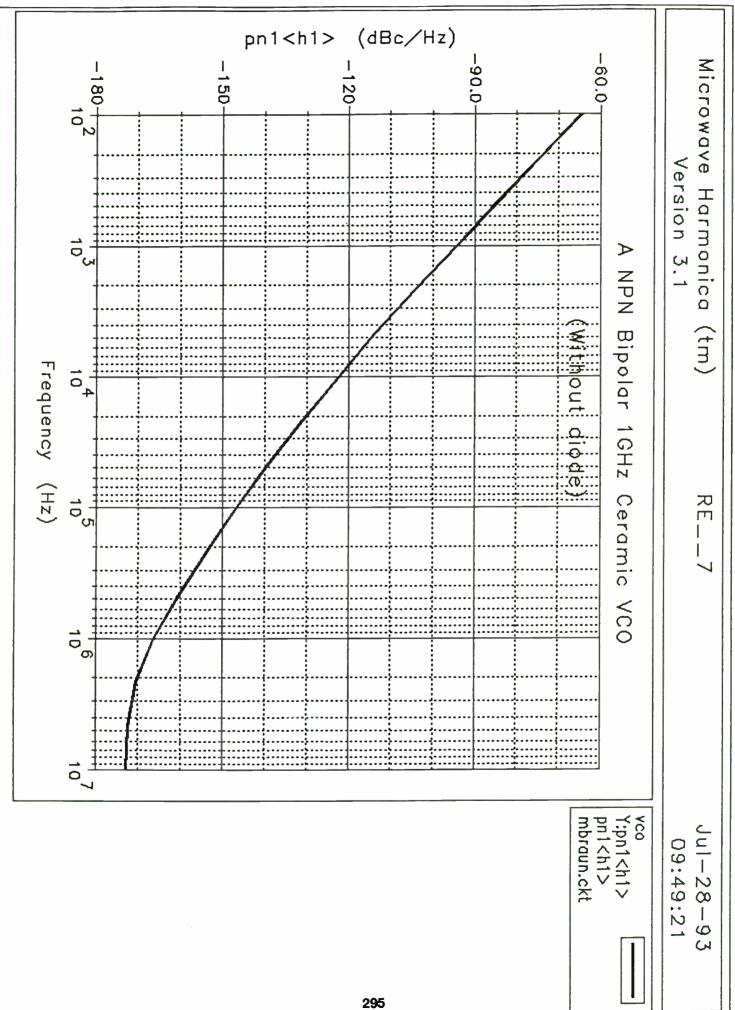

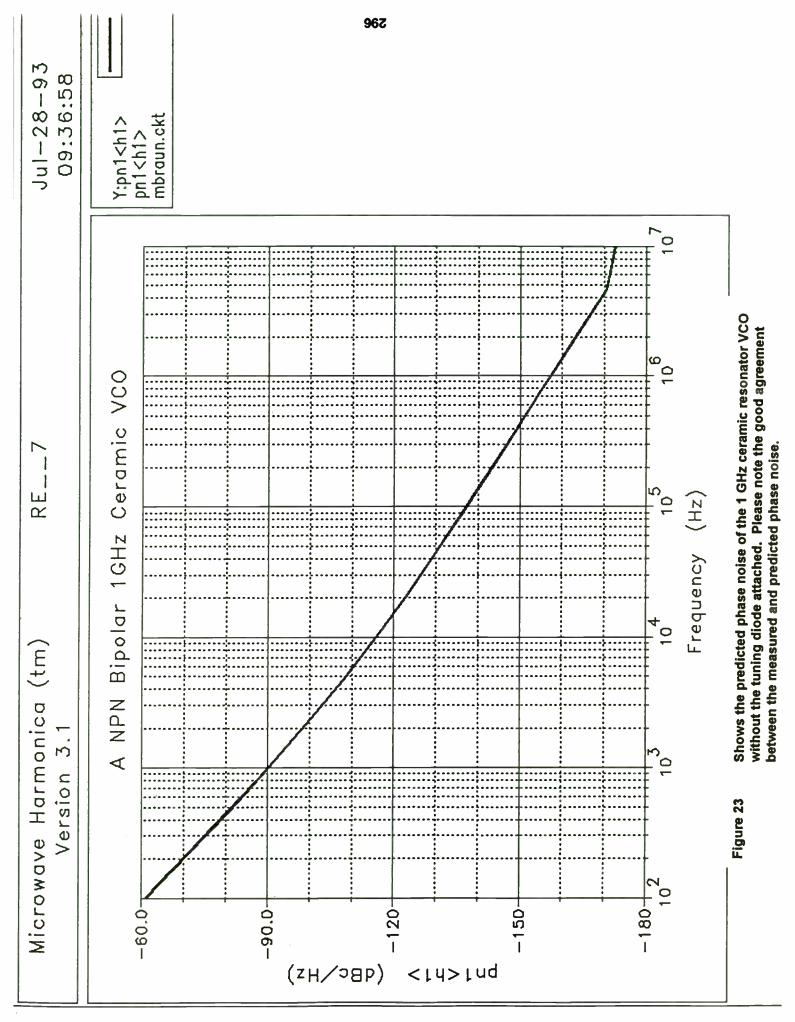

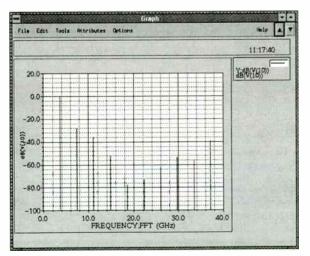

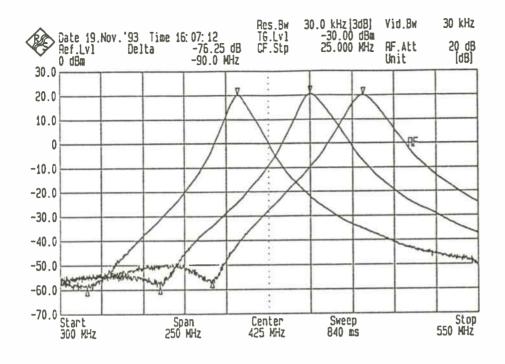

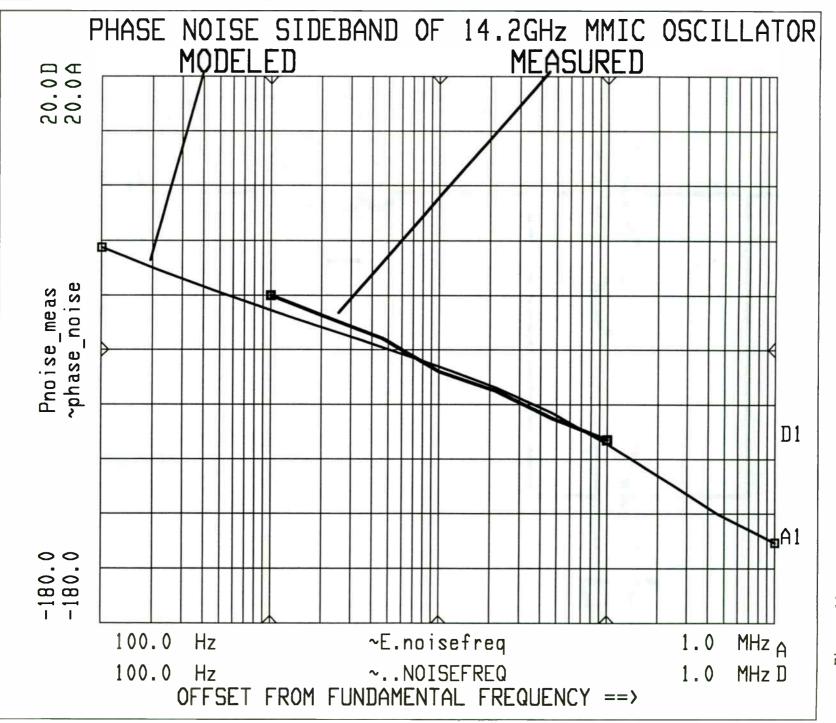

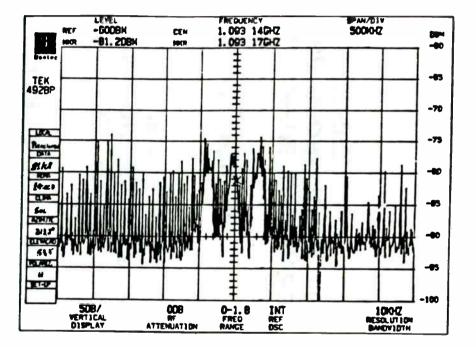

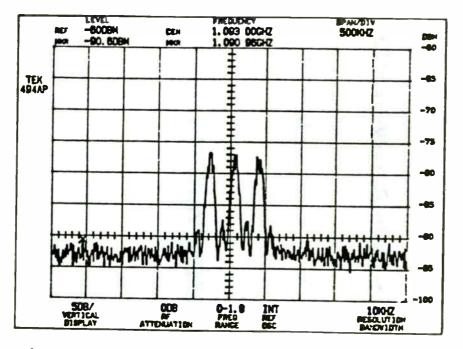

A Colpitts type VCO, which is well suited for low supply voltages, is used. The positive feedback is achieved via a capacitive bridge between gate and source of the E-FET. Two varactor diodes are integrated on the IC and the LO frequency is determined by the external resonator and the control voltage CTRL\_VCO. Measurements on a similar VCO shows a phase noise of -100 dBc at 100 kHz frequency offset (Figure 5). The signal delivered by the VCO is fed into the up converter MTx via 2 differential amplifier stages.

The MTx stage is a double-balanced Gilbert cell with a differential IF stage designed with D-FETs because of the large amplitude (0 dBm) of the input signals IF\_Tx. The RF output signals are taken on the drains of the mixing transistors and are then combined into a low input impedance push-pull stage. The loads of the Gilbert cell are LC parallel networks tuned at the required RF\_Tx frequency band OL-IF\_Tx (1710 MIIz-1785 MIIz). Thus, the amplitude of the signals in the image band OL+IF\_Tx (2510 MIIz-2585 MHz) is reduced before being filtered externally.

The simulated DC power consumption of the complete Tx stage is around 210 mW.

#### <u>Rx stage</u>

The LNA consists of 2 cascaded E-FETs biased via a resistive bridge which achieves the best trade-off between gain and noise figure. A feedback loop is added for the stabilization of the operating points. The input matching of this cell is achieved via an external inductance. The LNA integrates an Automatic Gain Control, thus providing a conversion gain from -6 dB to 17 dB from the whole Rx chain by applying an input voltage between 0 and 3 V at the pin AGC\_RF.

The IRM removes by phase cancellation the undesired signal and noise generated at the RF frequency  $OL + IF_Rx$ . It consists of 2 double-balanced Gilbert mixers with a RF differential stage with one grounded input. The first Gilbert cell mixes the LNA output with the VCO complementary outputs, the second one with the LO complementary signals phase shifted by 90°. After mixing, the four phases of the IF signals are available. Two of them with a phase difference of 90° are combined with the two others via a differential stage so that the adjacent RF image band is rejected.

The IRM requires therefore the quadrature phase shifting of the LO signals. Each phase shifter is a RC network and integrates a phase adjustment pin for optimum phase balance. Amplifier stages are added to the phase shifters so that the phase shifted signals have the same amplitude as the non phase shifted ones.

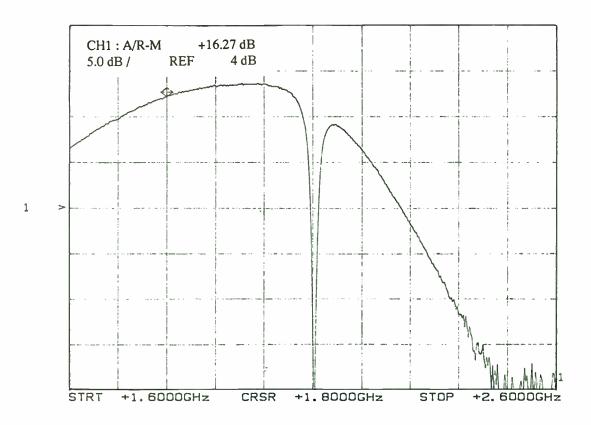

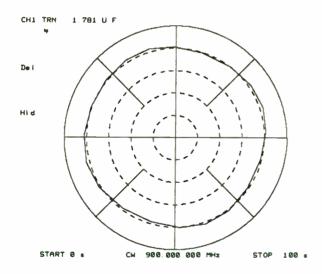

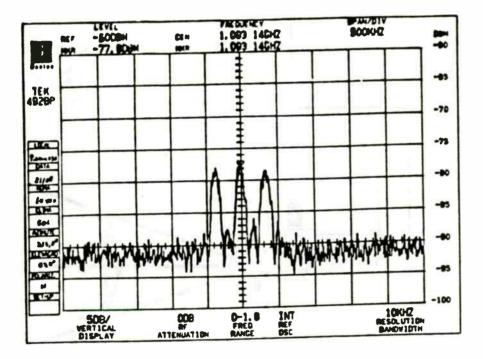

The measured performance of the Rx chain indicates a DSB noise figure less than 7 dB, a typical 1 dB compression point of -30 dBm with respect to the input at 1.8 GHz and an input third order intercept point higher than -22 dBm. Figure 6 shows that an image rejection higher than 25 dB is obtained for a conversion gain of 16.3 dB at 1.8 GHz. The measured power consumption of the Rx stage is less than 135 mW under 3 V supply voltage.

#### 128/129 dual-modulus prescaler

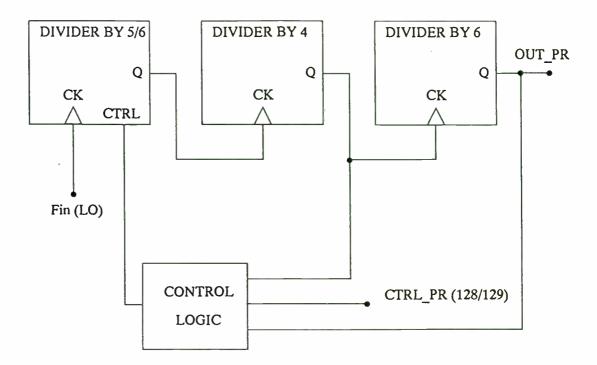

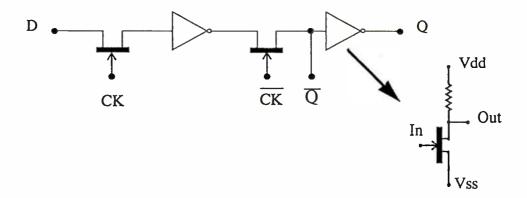

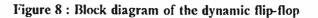

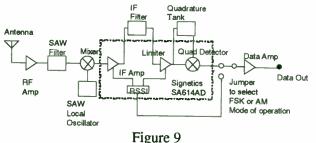

The proper division range 128/129 is obtained by 3 cascaded dividers and a pulse swallowing technique, as indicated in the Figure 7. A control logic driven by the input pin CTRL\_PR ensures correct toggling of the divider by 5/6. The design goal is to reduce significantly the power consumption of the prescaler. The use of dynamic logic is therefore required [2]. A dynamic flipflop is easily implemented using 2 transmitting gates and 2 Direct Coupled FET Logic (DCFL) inverters as shown in Figure 8. The divider by 5/6 (operating at the highest frequency) and the divider by 4 use dynamic flip-flops. The dynamic logic is limited by a minimum operating frequency of around 500 M11z given by the discharge time of the flip-flop noninverting stage. This limitation is alleviated by adding a memory cell in parallel to the dynamic flip-flop leading to semidynamic flip-flop (Figure 9). The divider by 6 has been designed with such flip-flops.

Moreover, as the DCFL gates requires only a 1.5 V supply voltage, a middle node VDB = 1.5 V is generated on chip via a resistive bridge. The divider by 5/6 is implemented between VDB and 3 V, and the 2 other dividers between the Ground and VDB in order to reduce the prescaler power consumption.

The division of frequencies from 1.9 GHz to 2.3 GHz under 3.0 V with a power consumption of around 15 mW is obtained.

#### Conclusion

A fully monolithic 3 V class II DCS 1800 RF front-end integrating a 500 mW power amplifier, a Rx low noise amplifier and image rejection mixer, a Tx up converter mixer as well as a voltage controlled oscillator and a PLL dual modulus prescaler is demonstrated. Performance compatible with its integration in a DCS 1800 terminal is obtained, thus demonstrating the validity of the monolithic approach. A low cost, SMD packaged, simplified version will be introduced on the market by the end of 1994.

Extensive experimental data will be presented at the conference.

#### Acknowledgements

This project has been designed for Matra Communication and supported by the DRI (Direction des Relations Industrielles, France Telecom). The authors would like to thank François-René Humbert, Pierre-Jean Séverin and André Jolivet at Matra Communication for their fruitful

cooperation. They are grateful to Marc Grillaud and Marcel Pertus for their effort in the layout, assembly and testing of the circuit.

#### References

.

[1]A.Herrera et al., "High efficiency, highly compact L-band power amplifier for DECT application", Proc. 23rd EuMC Conference, Madrid, pp. 155-157, 6-9 September 1993.

[2]M.Rocchi et al., "GaAs Digital Dynamic IC's for Applications up to 10GHz", IEEE Journal of Solid-State Circuits, vol. SC-18, no. 7, pp. 355-356, March 1986.

.

Figure 1 : Block diagram of the 3 V DCS 1800 RF front-end IC

Figure 2 : Photograph of the 3 V DCS 1800 RF front-end IC

Figure 3 : Block diagram of three stage power amplifier

Figure 4 : Output power, PAE and drain current curves versus input power

Figure 5: Phase noise of the Voltage Controlled Oscillator

Figure 6 : Conversion gain vs RF frequency for a fixed LO of 2100 MHz

World Radio History

Figure 7: Block diagram of the 128/129 dual-modulus prescaler

Figure 9 : Block diagram of the semidynamic flip-flop 9

Push-Pull Receiver Input Amplifier Stages -- The Solution to Intermod Problems

Hans Sapotta, TEMIC (Telefunken Microelectronic GmbH, P. O. Box 3535, D7100 Heilbronn, Germany; 49/7131/67-2244

Today's battery operated handhelds require an optimal sensitivity, an excellent large signal behaviour and an extremely low dc power consumption. But as normally the large signal behaviour is directly combined to dc current, there exists a system boundary that could not be passed up to now.

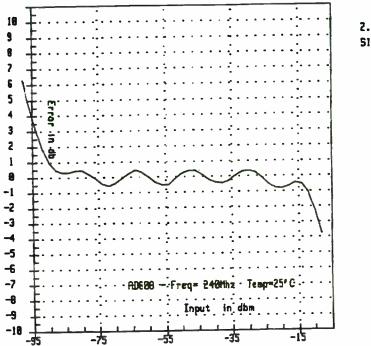

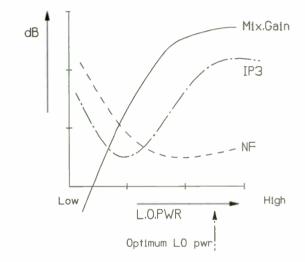

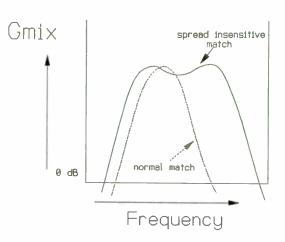

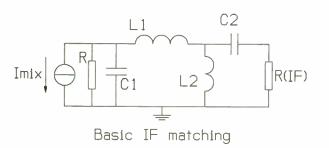

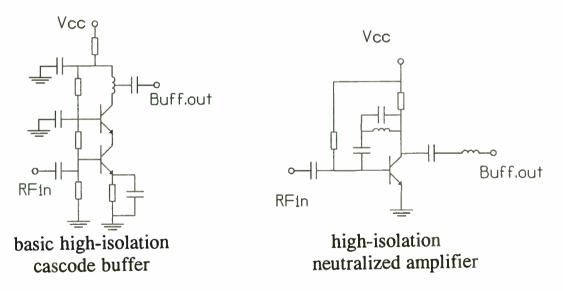

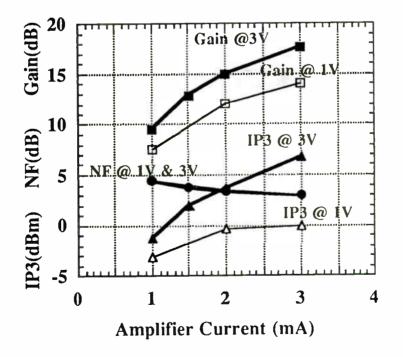

The new circuit offered here allows an increase in IP3 of 17dB at 8mA dc current with almost no decrease in gain, noise behaviour or reverse isolation. IM2 behaviour is improved as well as higher order intermodulation (see table below).

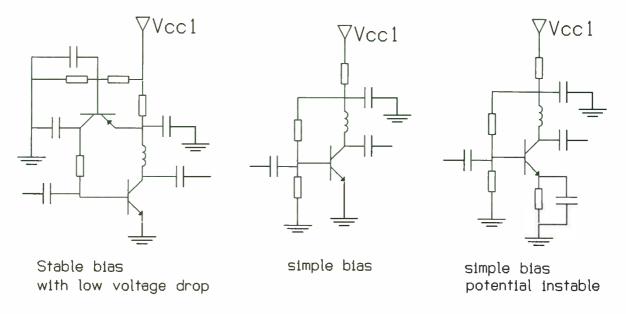

These results are achieved with a push pull complementary grounded base arrangement. A NPN bipolar transistor and a pnp bipolar transistor operate as parallel amplifiers for high frequency signals. If the supply current through both devices is equal, the intermod distortions compensate each other to a certain extent and therefore a nearly ideal linear amplifier is built. The same current through both devices is achieved by simply switching both transistors in series. One can connect either the emitters or the collectors of both transistors. Both circuits are equivalent in their electrical behaviour, so that practical aspects like operating point stabilization or signal handling may decide what is preferred. For a correct function, the parallel ac operation must be maintained down to the lowest difference frequency of two possible input signals.

The transistors need not be matched, just taking similary types is sufficient. The resulting noise figure is about the mean value of the noise figure of the npn- and pnp-device.

Taking over these results to FET-devices suffers from the fact that matching becomes necessary, as FET devices do not follow the Shockley's equation.

It is planned to extend these results from amplifier devices to mixer devices. First results are quite promising.

| device      | Mosfet          | BJT           | Push Pull BJT |

|-------------|-----------------|---------------|---------------|

| circuit     | grounded source | grounded base | grounded base |

| source imp. | 500 Ω           | 50 <b>Ω</b>   | 50 Ω          |

| F/db        | 0.8             | 1.0           | 1.2           |

| Gain/dB     | 20              | 10            | 10            |

| IP2/dBm     | 26              | 46            | 51            |

| IP3/dBm     | 0               | 10            | 27(=0.5W)     |

| IP5/dBm     | -9.5            | 9             | 18            |

Table 1: Comparing different devices as receiver input stages at 100MHz and 8mA biasing current (measurement values)

10

A low-voltage IC front-end for cellular radio

Sheng Lee and Alvin Wong Philips Semiconductors, 811 E. Arques Avenue, P. O. Box 3409, Sunnyvale, CA 94088-3409

Today's portable cellular users are demanding smaller, lighter phones with loner talk time. In response, cellular phone manufacturers are forced to use highly integrated and low-voltage ICs in their designs. The Philips SA601 front-end IC fulfills these needs by incorporating a high-performance LNA and mixer in a single 3-V device. The SA601 can be combined with the Philips SA606 (lowvoltage FM/IF) and SA5752/SA5753 (low-voltage audio processor chipset) to form a complete 3-V receiver section which meets AMPS specifications.

This presentation will discuss the importance of a high-performance integrated front-end to meet the strict requirements for cellular radio. Additionally, SA601 performance graphs will be shown along with performance graphs for the entire cellular receiver.

11

# A Monolithic Quadrature Demodulator and Digitizer for PSK and QAM Applications

Jim Marsh, Scott Williams, Brent Jensen Tektronix Microelectronics, P.O. Box 500, Beaverton, OR

Simon Atkinson, Jonathon Strange Mosaic Microsystems LTD 3 The Old Yard, Rectory Lane, Brasted, Westerham, Kent, England

# Dave May, Tom Bilotta, Fred Harris TV/COM International, 16516 Via Esprillo, San Diego, CA

# Abstract

The signal conditioning and processing required in modern QPSK and QAM modems is performed by imbedded low cost, high performance digital signal processors. Sample rates exceeding 60 MHz (I/Q), representing input bandwidths up to 45 MHz, can now be supported in consumer grade products. The pre-processing task required of a DSP based modem is the transformation (or transduction) of the modulated input signal from an input IF carrier to a pair of quadrature baseband analog to digital (A/D) converted data streams. While conceptually simple to implement, this conversion represents a formidable challenge at the 60 MHz sample rate. This transformation, requiring a quadrature spectral translation, anti-aliasing filtering, sampling, quantization, and binary coding has been implemented by a versatile, highly integrated, mixed mode integrated circuit which we introduce and discuss here.

# Introduction

Digital signal processing (DSP) techniques are being applied to the implementation of various stages of radio receivers (and in particular, modems) for a number of reasons. These include improved cost–performance considerations, reduced costs of manufacturing, alignment and testing, reduced inventory requirements in support of a product line, low cost for product enhancements, and ease of incorporating growth features.

Modems can be implemented incorporating various degrees of imbedded DSP. The interface between the analog and digital portions of the modem is the analog to digital converter (ADC). The location of this interface is related to the required performance parameters of the converter. The most important parameters are signal bandwidth and signal to noise ratio which define, respectively, the necessary sample rate and effective number of bits required for the conversion. Additional considerations are stability of the sampling clock, aperture uncertainty, quadrature channel matching, and the cutoff frequency of the quantizer networks. Subject to satisfying these considerations it is desirable to locate the analog to digital interface as early in the processing chain as possible.

Conventional quadrature receiver architectures designed to leverage the advantages of DSP have relied on separate functional blocks for the IF gain, quadrature demodulation, baseband filtering, I and Q sampling, clock generation, and local oscillator subsystems, resulting in considerable complexity and cost. This traditional implementation is particularly unsuited to a volume production environment due to the difficulty of achieving repeatable amplitude and phase matching of I and Q channels without post–assembly adjustments.

We discuss here a highly integrated component that provides IF to baseband quadrature demodulation, anti-aliasing filtering, and A/D conversion on a single monolithic die. The high level of integration, combined with superior specifications, provides a reliable cost effective solution for the most demanding of vector modulated digital receiver applications.

# Architecture

# **Functional Description**

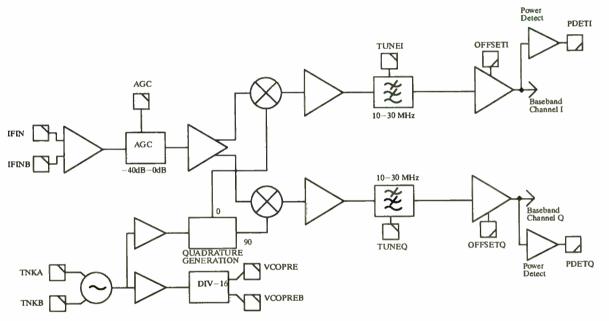

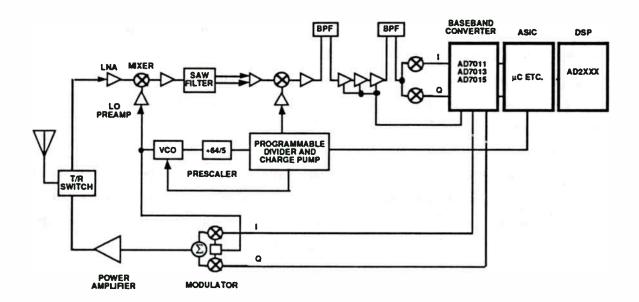

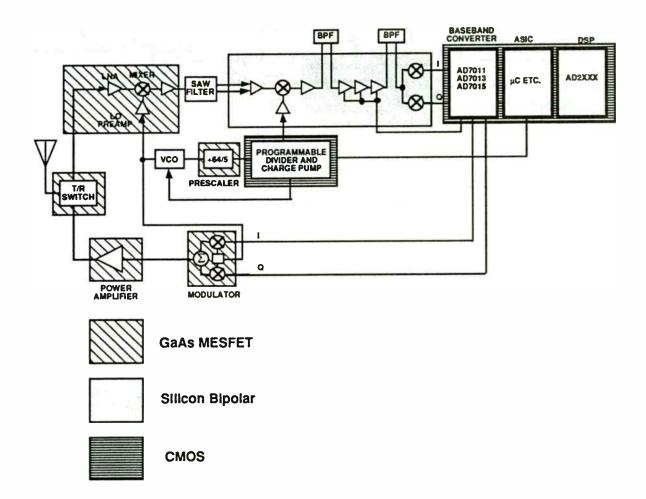

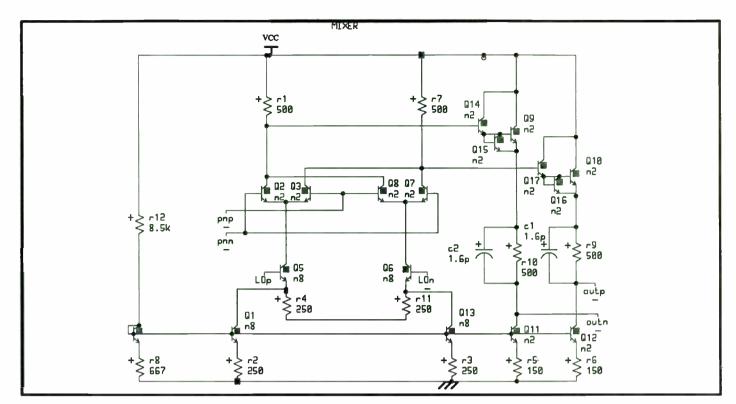

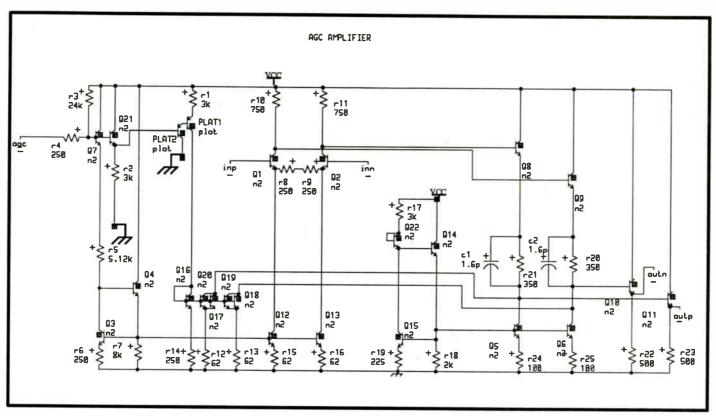

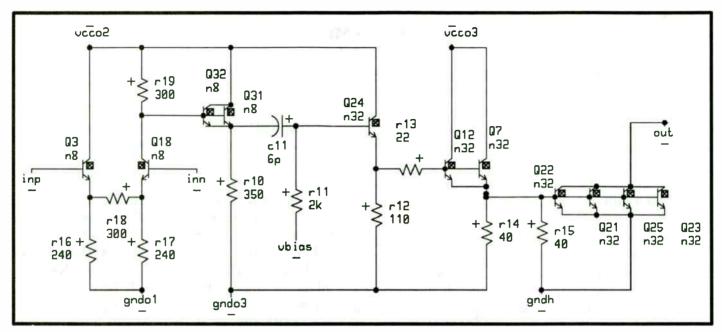

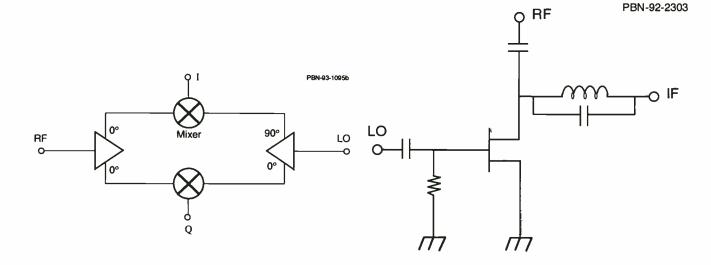

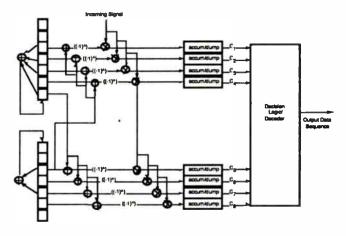

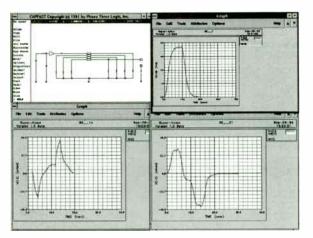

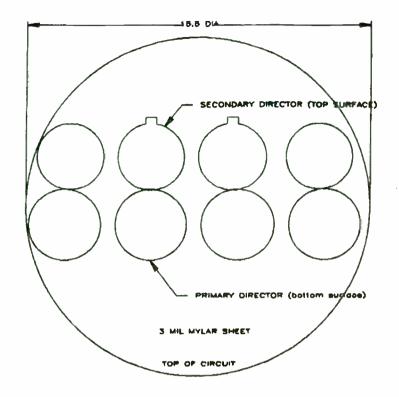

The component can be functionally divided into two block diagrams, illustrated in figures 1 and 2. The analog signal conditioning, consisting of IF processing, quadrature demodulation, baseband lowpass filtering, and buffering functions are shown in figure 1. The ADCs and supporting circuitry are illustrated in Figure 2.

# IF Quadrature Demodulator

We now present details of the quadrature demodulator block of the component which is shown in figure 1. This block integrates the IF processing functions which includes a controlled input impedance amplifier, a variable gain amplifier, and matched mixers to produce the I and Q baseband signals. The block also includes an integrated VCO, a divide-by-16 frequency prescaler, and an active phase shift network which forms the quadrature LO signals. The final portion of this block contains a pair of integrated active low pass filters and baseband amplifiers to supply the drive levels required by the ensuing ADCs.

The IF input amplifier is a wide bandwidth 50 ohm input impedance amplifier with sufficient insertion gain and linearity to provide an IIP3 of +5 dBm for an expected input power of -10 dBm. Differential inputs are provided, but single-ended drive is accepted with proper termination of the unused input. A variable gain cell follows the input amp. This cell uses a modified double balanced mixer topology to provide an attenuation range in excess of 40 dB. An amplifier follows the variable gain cell to provide additional gain and drive to the mixers. Linearity is enhanced by a current feedback topology and by buffering the degeneration resistors. A classic double balanced mixer cell is the core of a baseband power detection function, provided for each of the two channels. A differential to single ended converter drives the on board gyrator filters.

The negative resistance amplifier of a resonant tuned oscillator is provided on chip. A differential topology is utilized to provide maximum interference rejection. The oscillator is buffered, and drives a quadrature generation network as well as a divide-by-16 prescaler.

A variation of a phase lock loop topology is utilized in the quadrature generation circuitry to provide the stringent phase error specifications called for in this design. This architecture uses a variable delay element, a

phase detector, and an integrator in a feedback loop to lock the I and Q LO signals at 90 degrees phase difference.

A fully integrated 5th order Butterworth low pass filter is realized using a gyrator topology. The cutoff frequency is adjustable from 10 MHz to 30 MHz. The filters for each channel are independently adjustable.

The baseband amplifier, one each for the two channels, provides 29 dB of gain to drive the A to D converter. The amplifier exhibits a 3 dB bandwidth in excess of 120 MHz, providing a maximally flat response from DC to 20 MHz. Each amplifier has an offset adjustment to compensate for any offsets introduced by the filters.

# A/D Converter

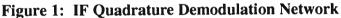

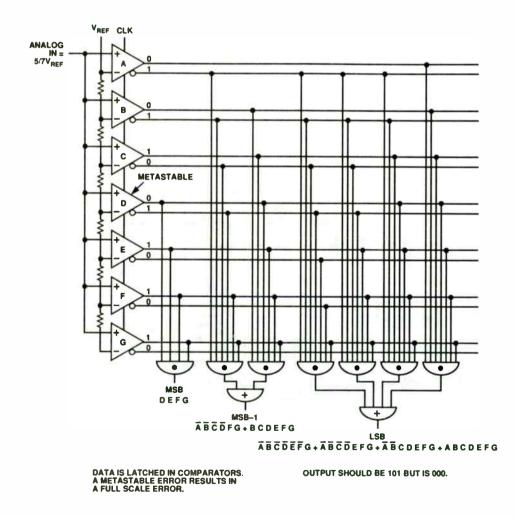

The dual ADCs and supporting circuitry are shown in figure 2. This block integrates two matching 6 bit flash ADCs, the clock generation network, and all the bias and reference generation circuitry.

Each ADC provides 6 bits of resolution, and is implemented using a full flash topology. All signal paths in the converter are balanced to minimize common mode interference and eliminate ladder droop. The converter uses a Thermometer to Grey to Binary decoding sequence to minimize the errors due to out of sequence codes when digitizing a high speed signal. The decoding sequence is coupled with appropriate delay elements to drive metastable related errors to a statistically acceptable level. The data is latched, and is available to the user in either a 2s complement or offset binary format.

The resistive ladder, which provides the threshold voltages for the ADC comparators, is driven by an on chip reference amplifier. A ladder and reference amplifier is provided for each channel. The reference amplifiers' drive levels, derived from a bandgap voltage, define the full scale input voltage of the ADCs. The common mode levels of each reference amplifier are designed to mimic the common mode voltage of the corresponding baseband amplifier. Feedback is incorporated to insure proper common mode match between reference and signal.

The clock generation network accepts a sinusoidal input from the user, buffers and translates the signal, and drives the programmable sample rate prescaler as well as a reference clock prescaler. The programmable sample rate divider determines the actual sample rate for the ADC and the data clock out, as well as the latched output data.

Most reference and bias levels are generated from master bandgap reference cell. This cell provides supply independent biasing, and both temperature independent and PTAT bias are available. Slave reference cells provide the reference and bias signals for the various functions.

The design includes an independent single supply operational amplifier for use as determined by the user. The op amp runs on a single +10 volt supply and provides greater than 85 dB of open loop gain, 10 MHz gain bandwidth product, and less then 1 uVpp integrated noise voltage. This op amp is useful in AGC loops or for conditioning the filter cutoff frequency adjustment.

# The Interface

The interface between the RF front end and the ADC consists of differential baseband signals and all reference signals necessary for the circuitry. The baseband amplifier must only drive a high impedance load, as the signal remains on chip. The power requirement of the baseband amplifier is thus considerably less than that required to drive a signal off chip into a controlled impedance environment. The monolithic solution also provides simplified bias requirements, as all gain dependant functions will track over variations in process. This eliminates the need for the user to compensate for changes in gain from part to part, and from channel to channel.

## **Banner Specifications**

The design boasts many characteristics that have never before been achieved in monolithic form. The level of integration will simplify the job of the receiver designer by eliminating several of the traditional interfaces required by discrete designs. The high level of integration will decrease the total parts count of a design, increasing the reliability of a receiver system.

Each channel ADC provides 6 bits of resolution at a sample rate of 60 MSPS. The dynamic resolution of the converter degrades by only 0.5 effective bits for input frequencies near nyquist. The dynamic accuracy of the converter is possible due to proprietary design of the comparators and the process technology specifications. Metastable errors that might contribute to Bit Error Rate (BER) have been statistically eliminated by appropriate placement of signal regeneration. In addition, the Thermometer to Grey to Binary conversion insures that any problems in the conversion will result in at most a 1 LSB error at the output.

The quadrature generation network utilizes the PLL topology mentioned above to achieve unprecedented phase and amplitude accuracy in a monolithic quadrature demodulator.

The variable gain amplifier discussed above exhibits a range of attenuation from -3dB to an excess of -43dB, thus delivering an input dynamic range in excess of 40dB.

The filters are realized utilizing a gyrator topology and implement a fifth order Butterworth response. The cutoff frequency of the filters can be adjusted between 10MHz and 30MHz via an analog input. The variable

15

cutoff characteristic is useful in multi-sample rate situations, where the baseband signal has a predetermined bandwidth. The integrated filters provide superior channel to channel matching, in addition to simplifying the overall system design.

# **Isolation Issues**

A design with this level of complexity will provide many opportunities for unwanted coupling between various functions of the chip. The majority of these isolation issues involve the digital outputs and the associated harmonic energy coupling into the circuitry in question, either through the substrate or via the package parasitic capacitance and mutual inductance. Several design techniques were utilized to minimize the effect of coupled signals, including the use of differential topologies for all analog and digital signals. Differential I/O was used wherever possible to increase isolation through the package and on the board. The digital outputs have been designed with controlled rise and fall times into well defined loads to limit the harmonic energy. The integrated filters, where the signal path is single–ended, utilize grounded capacitors to take advantage of a parasitic PN junction, thus increasing the substrate isolation. The prescaler divide ratio was chosen such as to guarantee the prescaler frequency does not fall in the baseband. Finally, separate supplies are brought out of the package to insure sufficient cell to cell supply rejection.

# Results

# **Chip Statistics**

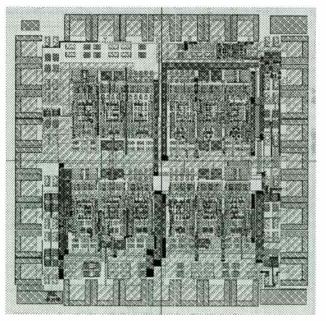

The die measures  $156 \times 129 \text{ mils}^2$ , and a die photograph is shown in figure 3. The design integrates 500 cell instances and utilizes 10,000 transistors and 10,000 passive elements. The component dissipates 1.3 watts at room temperature, and is packaged in a 100 pin MQFP.

Figure 3: Quadrature Digitizer Chip Photograph

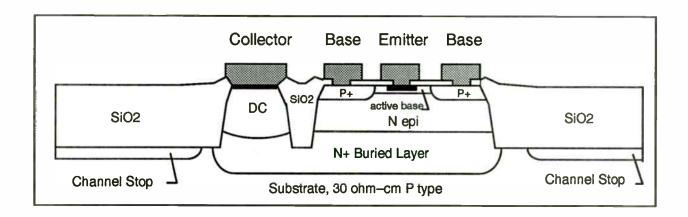

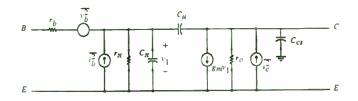

The design is fabricated on a trench isolated, double poly-silicon, bipolar technology. The NPN transistors exhibit a nominal  $f_T$  of 14 GHz, and may be scaled to a minimum area of 8 x 12  $\mu$ m<sup>2</sup>. At this minimum size the junction capacitors have the following values: Cjc = 15.5fF, Cje = 9.3fF, and Cjs = 11.3fF. The technology also offers lateral PNPs, schottky diodes, 200 ohm/sq poly-silicon resistors, 50 ohm/sq thin film trimmable Nichrome resistors, and MOS capacitors.

Four layers of interconnect are available, including three layers of gold and 1 ohm/sq poly-silicon. The poly-silicon and bottom two layers of gold metal may be patterned at a 4  $\mu$ m pitch. The third gold layer may be drawn at a 16  $\mu$ m pitch. This top gold layer is very useful for power bussing, as it is twice the thickness of the other two layers of metallization.

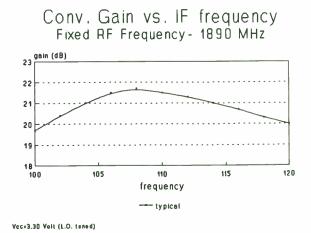

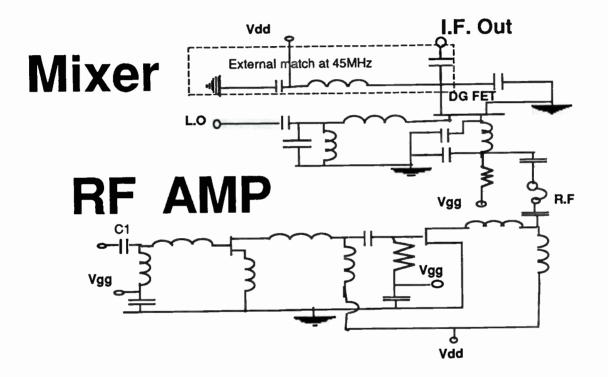

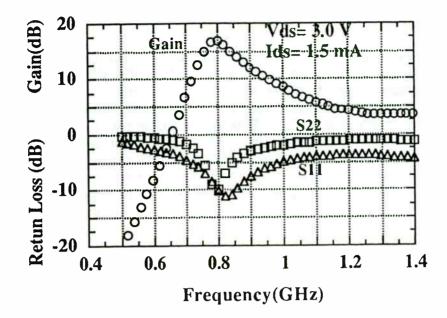

## Measurements

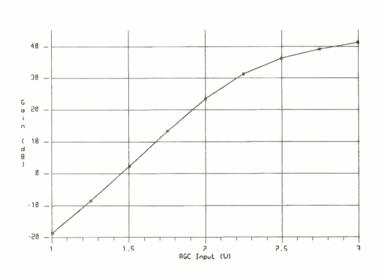

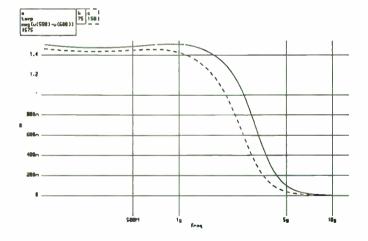

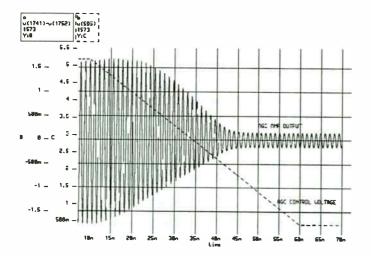

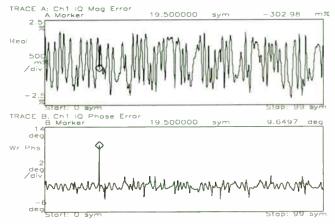

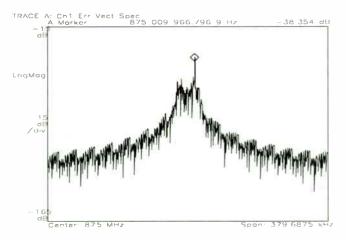

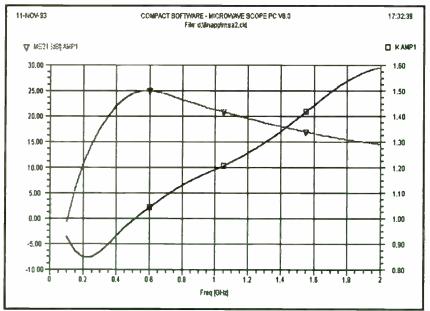

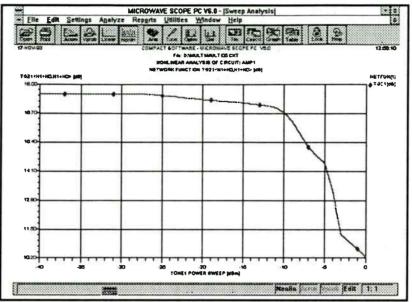

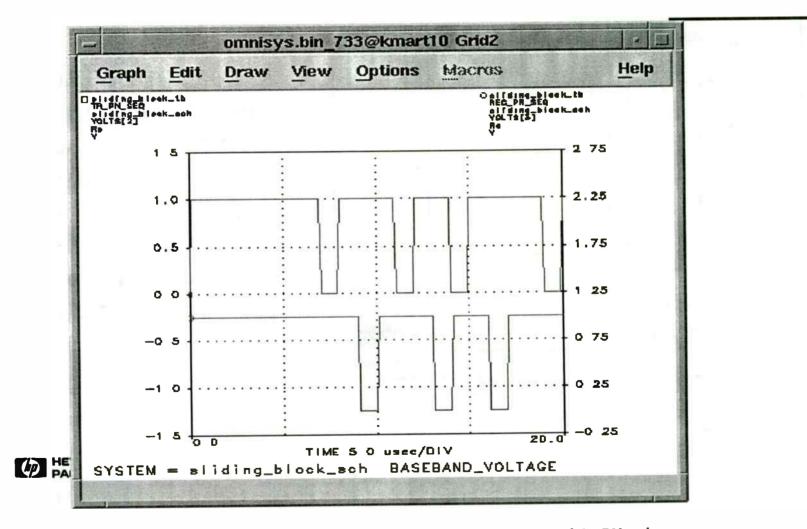

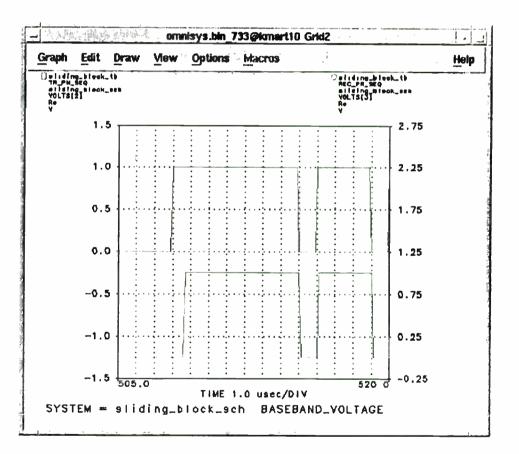

Evaluation was performed on the die to determine part functionality. All major blocks of the chip were functional. The range of IF Gain vs. AGC input, shown in figure 4, enables the component to deliver greater than 40 dB of dynamic range.

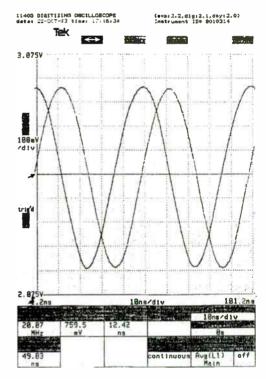

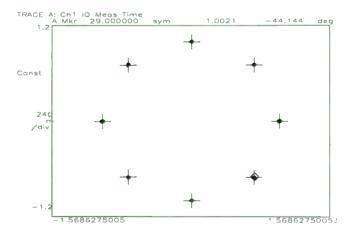

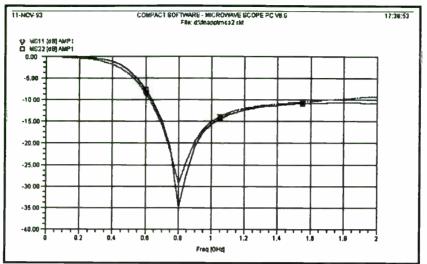

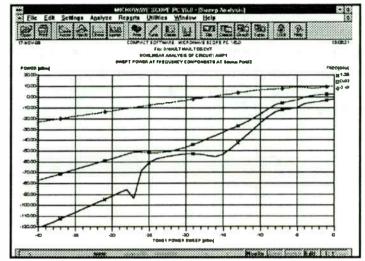

The result of the quadrature demodulation process is shown in figure 5, which shows both I and Q baseband signals that are the result of a 684MHz VCO frequency and a 664 MHz IF frequency. The test environment necessitated the averaging of the baseband signals, but this will only serve to ease the measurement of any systematic quadrature phase or amplitude error. The measurements in figure 5 result in a phase error of less than 0.3 degrees and an amplitude error less than 0.1 dB.

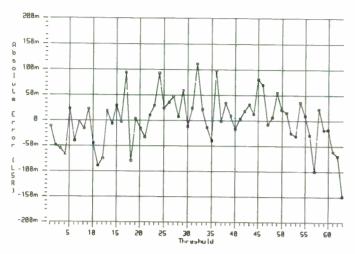

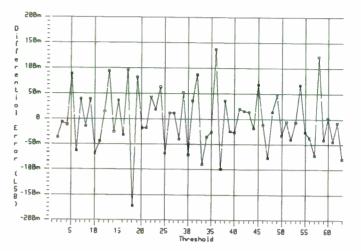

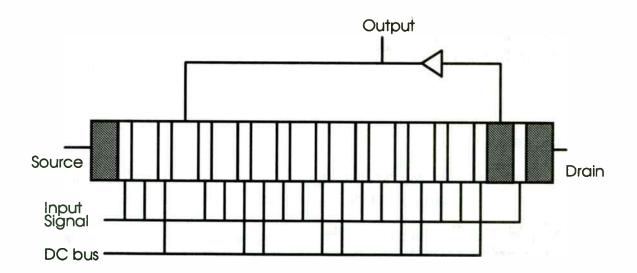

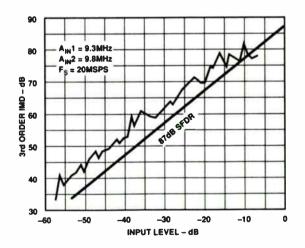

The ADC linearity is presented in figures 6 and 7. The maximum integral linearity error and differential linearity error are both less than 0.2 LSB. The measured gain match is less than 0.05 dB.

# Figure 4: IF Gain Vs. AGC Control Voltage Conclusions

Figure 5: I and Q Baseband Signals

# The emergence of DSP techniques that drive digital communication and data compression technology is enabling consumer and industrial applications not economically feasible just a few years ago. These markets will put cost pressure on traditional receiver implementations, thus encouraging integration of functionality. New technologies will require greater performance requirements on these functions, again requiring increased integration of traditional discrete designs. A component is described that performs the IF to baseband quadrature demodulation, anti-aliasing filtering, and digitization in a format compatible with evolving digital

World Radio History

demodulation and video compression standards. This design delivers exceptional dynamic range, linearity, dynamic accuracy, and is targeted for emerging QPSK and QAM applications.

# Figure 6: ADC Integral Linearity vs. Threshold Acknowledgements

Special thanks goes out to Keith Rast and Chris Saint for mask design, Dan Knierim, Walt Ainsworth, Dick Hung and Randy Lloyd for circuit design and consultation, Dave Entrikin for test and characterization, Tony Wechselberger, John Brewer and Don Becker for systems level consultation, and Chuck Miller, Mason Wood, Allen Hughes and Richard Lodge for consultation and support.

# References

Harris, F.J., and Wechselberger, T., "Multirate All–Digital Modems for Compression," 1993 NCTA Technical Papers, 42nd Annual NCTA Convention, June 1993: reprinted in Communications Technology, Trade Journal of Society of Cable Television Engineers, Sept. 1993, pp. 20, 22, & 34.

Harris, F.J., "On the Design of Pre-Equalized Square-Root, Raised Cosine Matched Filters for DSP Based Digital Receivers", 27th Asilomar Conference on Signals, Systems, and Computers, 31 Oct.-3 Nov. 1993

Harris, F.J., "Design Considerations and Design Tricks for Digital Receivers", 9th Kobe International Symposium on Electronics and Information Sciences, Kobe, Japan, June 18–19 1991

G. A. DeVeirman and R. G. Yamasaki, "Monolithic 10 – 30 MHz Tunable Bipolar Bessel Lowpass Filter," IEEE Proc. ISCAS, pp. 1444–1447, 1991

J. Marsh, et. al., "A 10 Bit 75 Mega-Sample Per Second A/D Converter," IEEE Proc. CICC, paper 26.6, 1991

T. Yamaguchi, et. al., "Process and Device Performance of a High–Speed Double Poly–Si Bipolar Technology Using Borosenic–Poly Process with Coupling–Base Implant," IEEE Trans. Electron Devices, vol. 35, no. 8, p. 1247, Aug. 1988

# Fractional-N Frequency Synthesizers for Next Generation Cellular and Wireless Applications

Wing S. Djen and Daniel J. Linebarger

Philips Semiconductors 811 E. Argues Avenue M/S 61, P. O. Box 3409 Sunnyvale, CA 94088-3409 U.S.A.

#### <u>Abstract</u>

The phase detector comparison frequency of the described 1 GHz fractional-N PLL frequency synthesizer can be either 5 or 8 time higher than the channel bandwidth. This implies that the close-in phase noise of the carriers can be up to 14dB (20log5) and 18dB (20log8) lower than the ones generated by the traditional synthesizers. At the same time, since the reference spurs are at least 5 times further away than the next channel, wider loop filters are allowed to use, which yields a faster switching time. By simple software programming, the device can switch between two loop filter configurations, where loop responses can be designed differently in switching or steady state. Combined with low-noise and fast lock-time performance, this fractional-N synthesizer is a true winner for the next generation cellular and wireless handsets.

A 1-V CMOS FSK receiver for wireless applications

David Shiels and Evert Dijkstra, Centre Suisse d'Electronique et de Microtechnique S. A. (Neuchatel, Switzerland)

This paper will report on an extremely low voltage (1 V) CMOS process for battery-operated wireless circuits and systems. Results will be shown for a low-current FSK receiver chip that is suitable for a variety of applications.

# Microphone-to-Antenna Solutions

# Session Chairperson: Robert Clarke,

Analog Devices, Inc. (Wilmington, MA)

| The applications of advanced CMOS/CCD technology in spread-<br>spectrum receivers. <b>Scott C. Munroe</b> , Analog Devices, Inc.<br>(Norwood, MA)                    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Signal-processing requirements for direct IF sampling receivers.<br><b>David Duff,</b> Analog Devices, Inc., Broadband Communications<br>Products (Greensboro, NC)44 |

| Baseband superintegration roadmap for digital cellular handsets.<br>Charles K. Fadel, Analog Devices, Inc. (Wilmington, MA)54                                        |

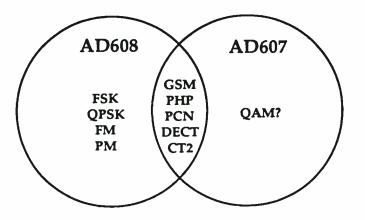

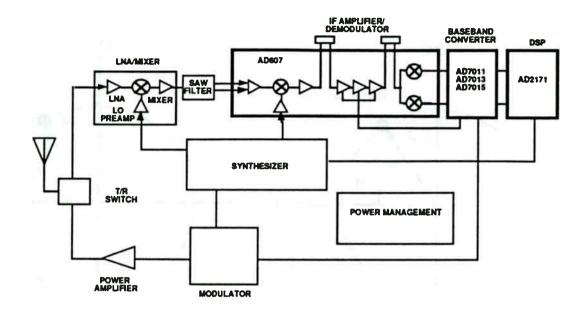

| Advanced RF ICs for VHF/UHF systems. <b>Robert Clarke, Doug</b><br><b>Grant, and Charles Fadel,</b> Analog Devices, Inc. (Wilmington,<br>MA)                         |

| Direct digital synthesis/direct digital modulation. Terry Brown and David Duff, Analog Devices, Inc. (Greensboro, NC)                                                |

21

# The Applications of Advanced CMOS/CCD Technology in Spread-Spectrum Receivers

Scott C. Munroe Analog Devices, Inc. 617/937-1245

# Introduction

Recent advances in charge-coupled device (CCD) signal-processing technology, together with its merging with mainstream silicon CMOS technology, make it an attractive candidate for many functions in wireless receivers. Integrating a high-speed, low-voltage CCD with a mixed-signal CMOS process allows discrete-time analog signal processing sample rates and bandwidths to far exceed those possible with switched-capacitor filter (SCF) technology. Indeed, sample rates are increasing rapidly as the technology is scaled. We believe that as scaling progresses below 1  $\mu$ m sample rates and bandwidths will equal or exceed those practical with surface acoustic wave (SAW) and acoustic charge transport (ACT) technologies. Even at these high speeds the CCD will retain its advantage of low power and precise, programmable clock control of delay.

This availability of high-speed, low-power discrete-time analog technology allows many receiver functions to be implemented more efficiently than with either pure analog or pure digital signal processing (preceded by an A/D converter). Furthermore, with the merging of advanced CCD technology with CMOS (ultimately BiCMOS) technology many receiver functions can be implemented on the same chip, each in the most appropriate technology. In this manner the highest performance/cost ratio can be achieved at the system level.

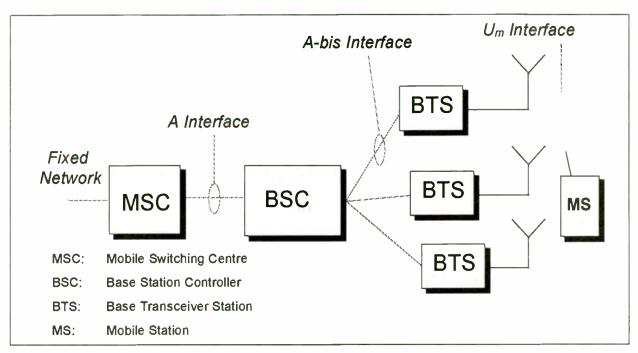

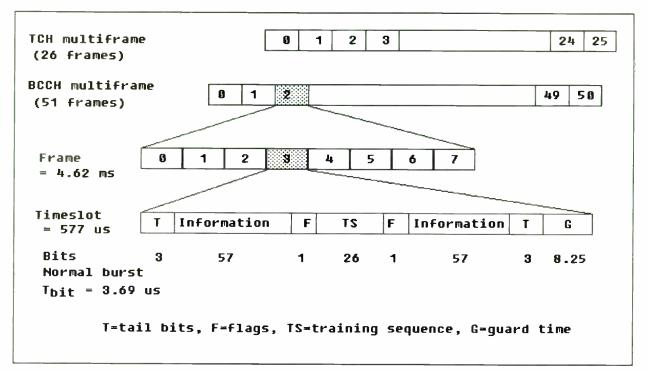

# **Requirements of Spread-Spectrum Communications Receivers**

Spread-spectrum communications technology has long been used by the military and NASA because of the well-known advantages in the areas of security, fade resistance due to reduced multipath sensitivity, immunity to interference, and ability to accommodate more users in a given bandwidth. However, the high cost of spread-spectrum technology has inhibited its use in the commercial sector until recently. This situation is rapidly changing as a result of advances in IC technology. With the recent approval of Qualcomm's code-division multiple-access (CDMA) format as the interim standard for cellular telecommunications in North America this trend to spread-spectrum communications should accelerate. In addition, the Global Positioning Satellite system (GPS) employs spread-spectrum technology. The civilian applications of this extremely precise navigation system are growing rapidly as the cost of GPS receivers decreases. For example, personal navigators coupled with digital mapping technology promise to revolutionize automobile driving once the cost of the technology reaches consumer levels.

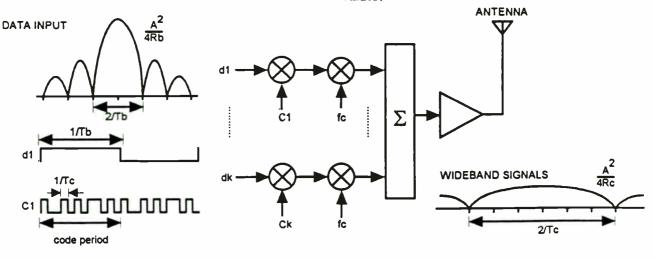

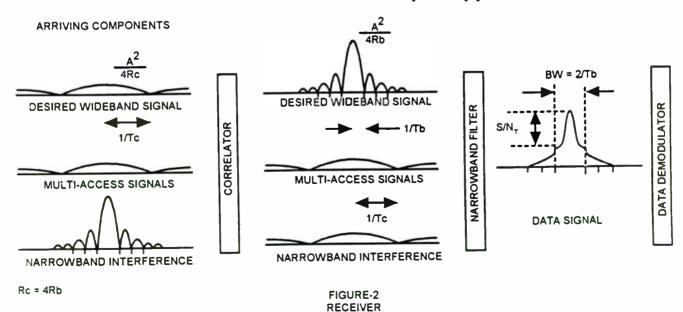

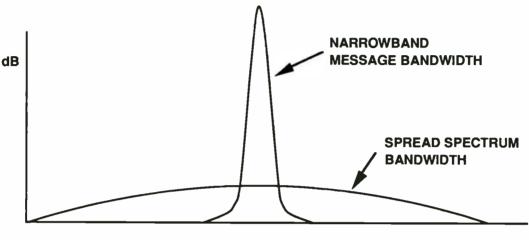

In spread-spectrum systems the signal bandwidth is spread over a much wider bandwidth either by frequency hopping (FH) of the carrier or pseudonoise (PN) modulation of the signal. Communication systems have been built that use both of these spreading techniques simultaneously. Common to both types of systems is the use of error correction techniques to mitigate the effect of an occasional missed or corrupted transmission.

In the FH case the instantaneous carrier bandwidth is identical to the signal bandwidth. Accommodation of multiple users is achieved by assigning different carrier hopping patterns to the different users. For the PN case, the signal bits are modulated by a much higher frequency code (in communications jargon the bits in the PN code are called "chips," and the PN bit rate is referred to as the "chipping" rate). Hence, the instantaneous bandwidth is much wider than the signal bandwidth. A desirable result of this wider instantaneous bandwidth is that the instantaneous spectral power density is lower than in the FH case. Consequently, a transmitter causes less interference, and without error-correction coding more users can simultaneously occupy the same bandwidth. Furthermore, the direct-sequence transmitter will drop below the thermal noise floor of the receivers at a shorter range, thereby allowing greater spatial reuse options. Accommodation of multiple users is effected by assigning different PN codes to individual users. In both FH and PN cases security is added by randomizing and frequently changing the hopping patterns or PN codes, respectively.

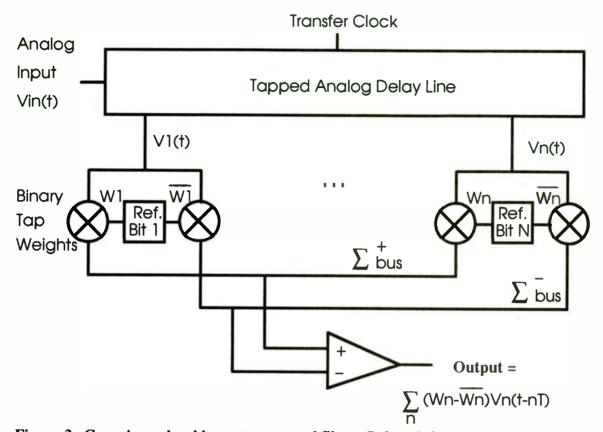

In both types of spread-spectrum systems the receiver must collapse the spread signal and recover the original information. To perform this function in the FH scenario a hopping local oscillator (LO) is required for "dehopping" the carrier. For a fast hopper a very fast-settling frequency synthesizer is required to generate the hopping LO. For the PN case a programmable matched filter is needed to strip off the PN modulation from the signal. However, this matched filter must sample at the PN chip rate (or higher), which can be many times the bit rate of the original signal. Furthermore, when the PN code is changed rapidly the matched filter must be able to update its reference code quickly, with minimum dead time in the signal path.

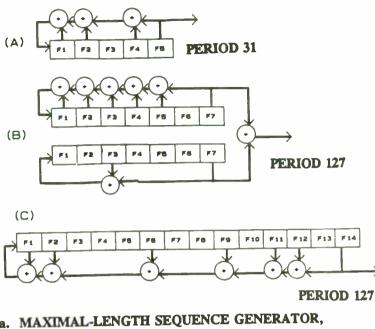

In scenarios where signal acquisition time is unimportant simple serial correlators suffice for the PN case. Here, the synchronized receiver adds up appropriately-weighted samples of the modulated signal and determines whether the original signal chip was a 1 or 0. Because the acquisition time tends be very long for serial correlators [proportional to (number of chips)<sup>2</sup>x(chip duration)] this approach is appropriate only for systems whose messages are long compared to the acquisition time.

In an increasing number of cases, however, rapid and frequent acquisition is required. Mobile communications and navigation systems often experience dropouts due to fading caused by buildings, bridges, tunnels, etc. Furthermore, modern digital communications systems are increasingly using packet-switching techniques to transmit data. Virtually all data transfer is packetized in new systems today. For example, the telephone system is converting to asynchronous transfer mode (ATM) technology, a form of packet switching. Such packets tend to be short (~100s of bits), and adding a synchronization sequence to each packet incurs a stiff overhead penalty that decreases effective throughput. Consequently, parallel matched filters are often required to significantly reduce acquisition times. Such filters are able to look at a pipelined sequence of samples simultaneously and rapidly determine the point in time when the received sequence matches the stored reference. To perform this matched-filtering operation requires a massive amount of high-speed signal processing, with simultaneous delays, and multiply-adds of a large number of signal samples required. Up until recently, it has been difficult to implement programmable high-speed matched filters of the required length with acceptable throughput, power dissipation, and component count.

The sample rate required in the matched filter can be surprisingly high. Take the case of a voice signal represented by a 16-kb/s stream. If each bit in that stream is modulated by a PN code of length 256 then the resulting stream has a bit rate of 4.1 MHz. This information must be sampled at a minimum of 4.1 Ms/s (and often at twice that rate).

The situation for Ethernet is even more dramatic: if the 10-Mb/s data stream is modulated by a 12-bit PN sequence the resulting stream must be sampled at a minimum of 120 Ms/s. The FCC mandates that a spreading factor of at least 10 be used in wireless spread-spectrum communication systems, and the limit on transmitted power in the allocated slots is 1 W. The C-band (5.400-5.525 GHz) bandwidth allocation is 125 MHz, the S-band (2.400-2.4835 GHz) allocation is 83.5 MHz, and the L-band (902-928 MHz) allocation is 26 MHz. For highest data rates the maximum bandwidth allocation should be used, and to do so will require very high-speed matched filters.

At the other end of the transmitted power budget are spread-spectrum systems intended for low-power inter- and intra-building and personal communication systems. Here, the extremely low limit on transmitted power ( $\sim$ 1 mW), coupled with the multipath environment common in buildings, severely degrades the signal-to-noise (S/N) ratio. The instantaneous power limit is too low for FH systems to be used effectively. To mitigate the effects of low power and multipath, PN systems with long codes are desirable because the noise and interference typically are uncorrelated to the PN code used to modulate the signal. Therefore, the S/N power ratio improves by the number of PN chips per bit. For example, a PN code of length 256 increases the S/N by 24 dB.

Because increasing the spreading bandwidth improves all of the desirable features of a spread-spectrum communications system there is inexorable pressure to build faster, wider-bandwidth systems. This trend, however, conflicts with the requirements of wireless systems: low power and low cost. Hence the need to implement each function as efficiently as possible.

Finally, modern digital communications systems tend to have "bursty" data. Packet radio is a good example of such a system. If the duty cycle of the data is low enough it would be desirable to absorb and store the burst but process the signal during dead time at a bandwidth or data rate lower than that of the incoming signal. At a 50% duty cycle there is no advantage (readout rate must equal input rate). However, as the duty cycle decreases below 50% the readout rate can be significantly reduced. At a duty cycle of 1/3 the readout rate can be half the input rate. At a 10% duty cycle the readout rate can be 1/9<sup>th</sup> of the input rate. The advantage to this scheme, known as FISO (fast-in, slow-out) is that many of the downstream signal processing components can be slower, lower power, lower cost, and potentially lower noise. To realize the full benefits of FISO, however, requires that the high-speed input sampling and storage circuitry be very area

and power efficient. This generally is not the case when flash A/Ds and high-speed digital memory are used for this function.

A summary of the requirements of wireless spread-spectrum communications receivers is given below.

# Summary of spread-spectrum receiver requirements

- Fast, programmable, parallel matched filters -For wideband PN systems requiring rapid acquisition

- Fast-settling frequency synthesizers for building fast-hopping local oscillators -For fast-hopping FH systems

- Long, programmable matched filters for narrowband signals -For low-bandwidth, low-power systems requiring long PN codes

- High-speed, low-power FISO circuitry to absorb data bursts

Allows processing of signals at lower speed, power, noise, and cost in low-dutycycle systems

- Low-power, low-cost components for consumer wireless applications

As will be discussed below, advanced CMOS/CCD technology can be of great benefit in meeting many of these requirements.

# Characteristics of Advanced CMOS/CCD Technology

Signals can be represented in the voltage, current, or charge domains. Historically, the use of the voltage domain has dominated, with the current domain sometimes employed in applications where its advantage in speed outweighs its typically higher power dissipation (e.g., RF, ECL). As geometries and power supply voltages are reduced, however, these two domains become more difficult to use. In the case of voltage-domain circuits, headroom, noise margins, and speed are negatively impacted by shrinking geometries and supplies, and higher parasitic capacitance. In the current domain, performance is degraded by reduced headroom and more resistive devices and interconnects. Because a current inevitably flows between supplies the number of signal-processing operations (each requiring at least a diode drop) that can be performed before this current must be "reflected" off a supply is severely diminished as headroom drops. Indeed, even the reflection requires a minimum of a diode drop, and is itself a source of signal degradation and power dissipation.

More recently, charge-domain signal-processing techniques have begun to make inroads. Charge is *the* fundamental electrical quantity (voltage and current are manifestations of charge), and the processing of signals in the charge domain appears to have significant advantages in many applications. As IC technologies are scaled below about 2  $\mu$ m they become much more capacitive. Charge-domain signal processing takes advantage of this inevitable trend: higher capacitance per unit area allows higher charge densities. In switched-capacitor filter (SCF) technology, for example, the easy availability of capacitors and good switches have made it possible to replace "current through a resistor" with "charge on a capacitor" as a way to process signals. Such capability allows precision and programmability to be achieved with the control clock, rather than a fixed precision resistor. Furthermore, a savings in power is frequently realized. However, SCFs require voltage-domain feedback in order to move charge from one capacitor to another. This has resulted in frequency limitations that have restricted the use of SCFs to applications requiring sample rates below approximately 1 MHz (depending upon the required accuracy).

CCD signal processing does not require feedback to transfer charge. Its characteristics more closely resemble those of current-domain signal processing, but with the strong advantage of a self-restoring operating point after each transfer. Although many of the advantages of CCD-based signal processing have long been recognized, the high voltages, multiple clock phases, and high capacitance of early CCDs made it difficult to realize the advantages. However, these drawbacks are historical, not fundamental; many stem from the attempt to use CCD imager processes for signal-processing applications. The requirements for imaging and signal processing are so different that IC processes tailored for the former are unsuitable for signal processing.

CCD signal-processing technology has made major strides over the past decade. The advances have been so rapid that most public domain references are out of date. Noteworthy among these advances are the reduction of operating voltages to 5 V and the perfection of uniphase clocking [1]. The lower voltage and use of a single clock have been accomplished without a reduction in maximum CCD charge transfer rate. Indeed, 5-V CCDs fabricated in the late 1980s with older 4-um NMOS/CCD technology had reached test-equipment-limited speeds of 370 MHz [2]. Both device-level simulations and experience indicate that CCD charge transfer rates far exceed the ability of the on-chip peripheral circuitry to keep pace.

These recent advances have made CCD signal-processing technology compatible with 5-V CMOS technology. Simulations of more advanced CCD structures indicate that operation down to at least 3 V should be possible. It should be emphasized that CCD structures and processes designed for signal processing are much simpler than those for imaging applications, where optical and anti-blooming characteristics are critical. The simpler CCD structures are much more compatible with standard MOS technology. Furthermore, it appears that the compatibility with CMOS and BiCMOS technology improves as geometries are scaled down.

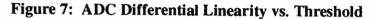

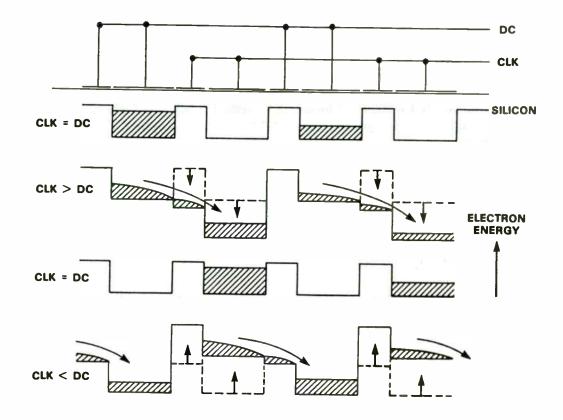

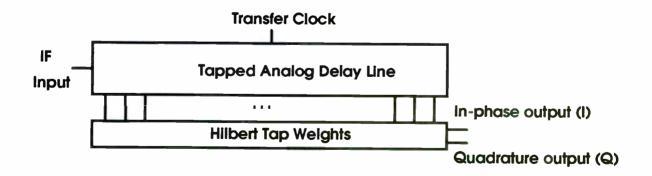

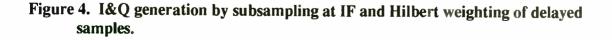

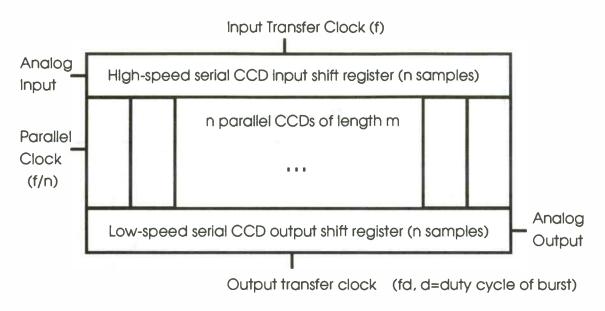

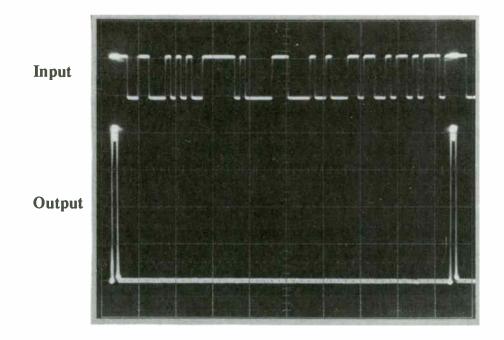

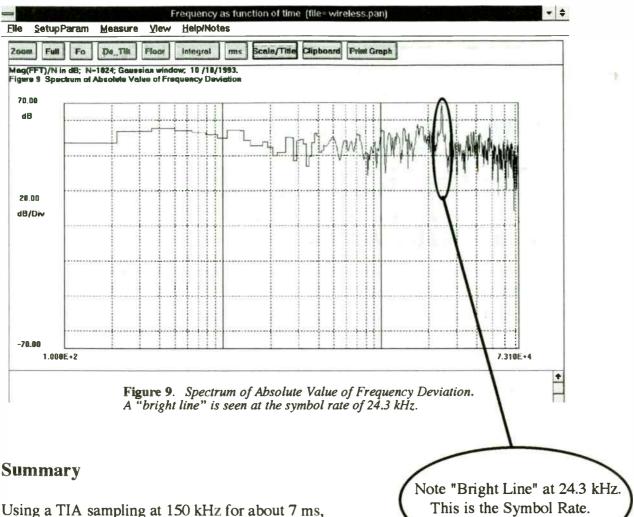

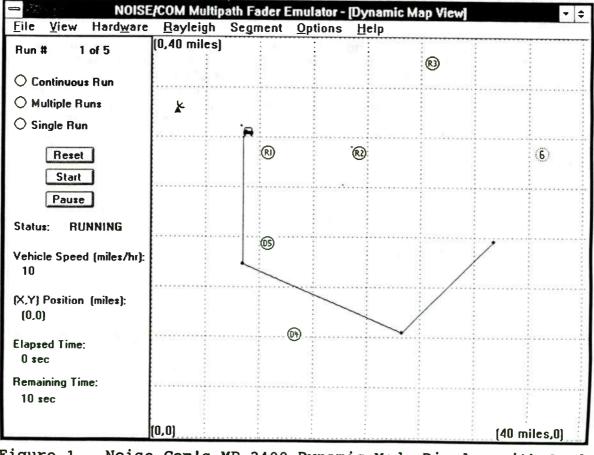

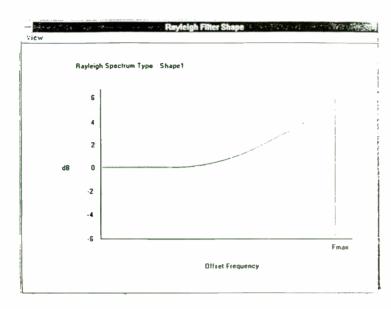

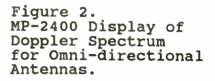

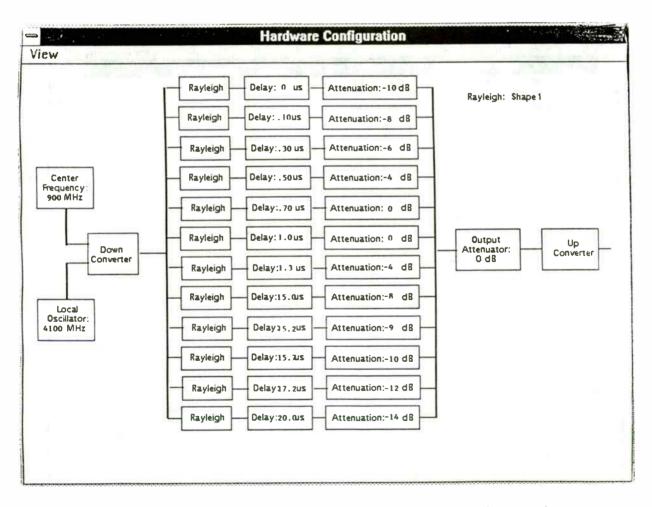

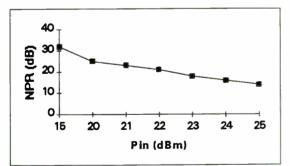

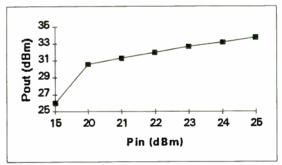

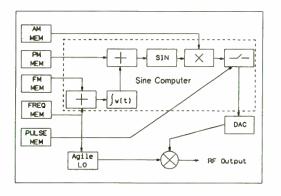

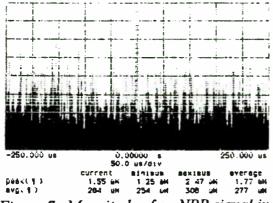

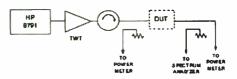

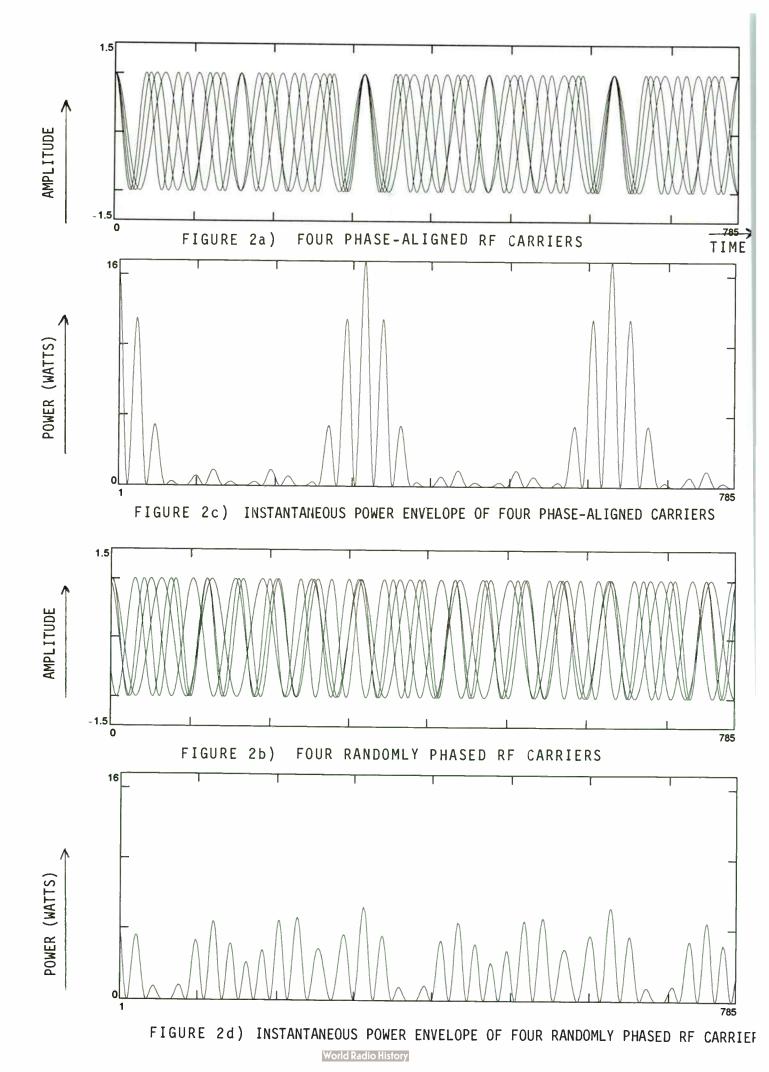

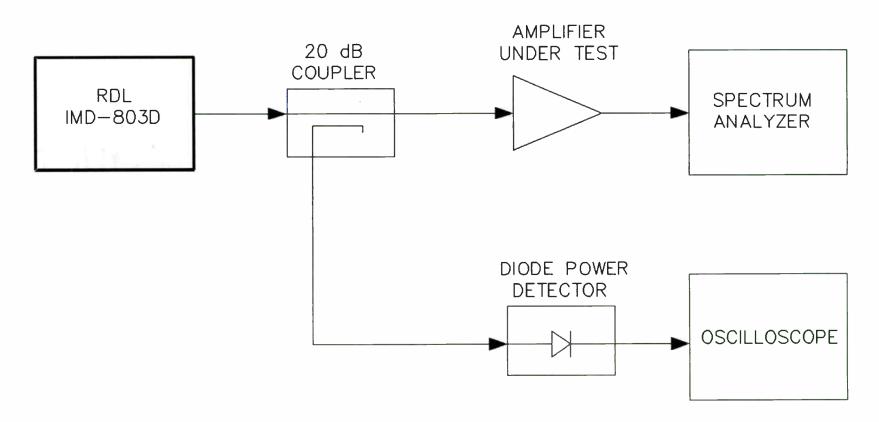

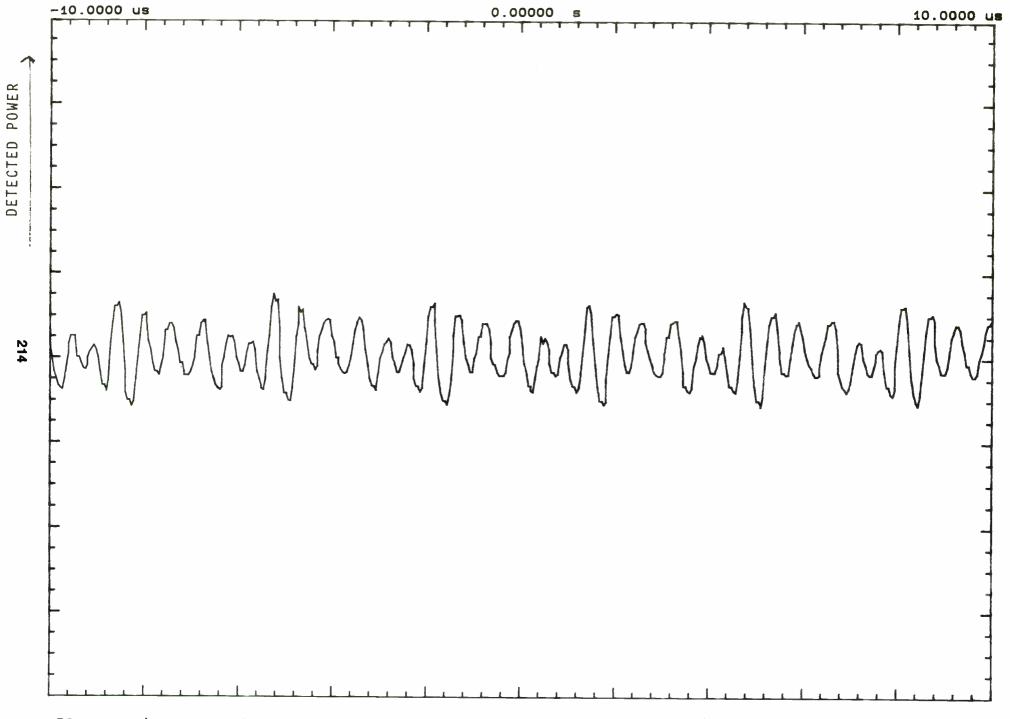

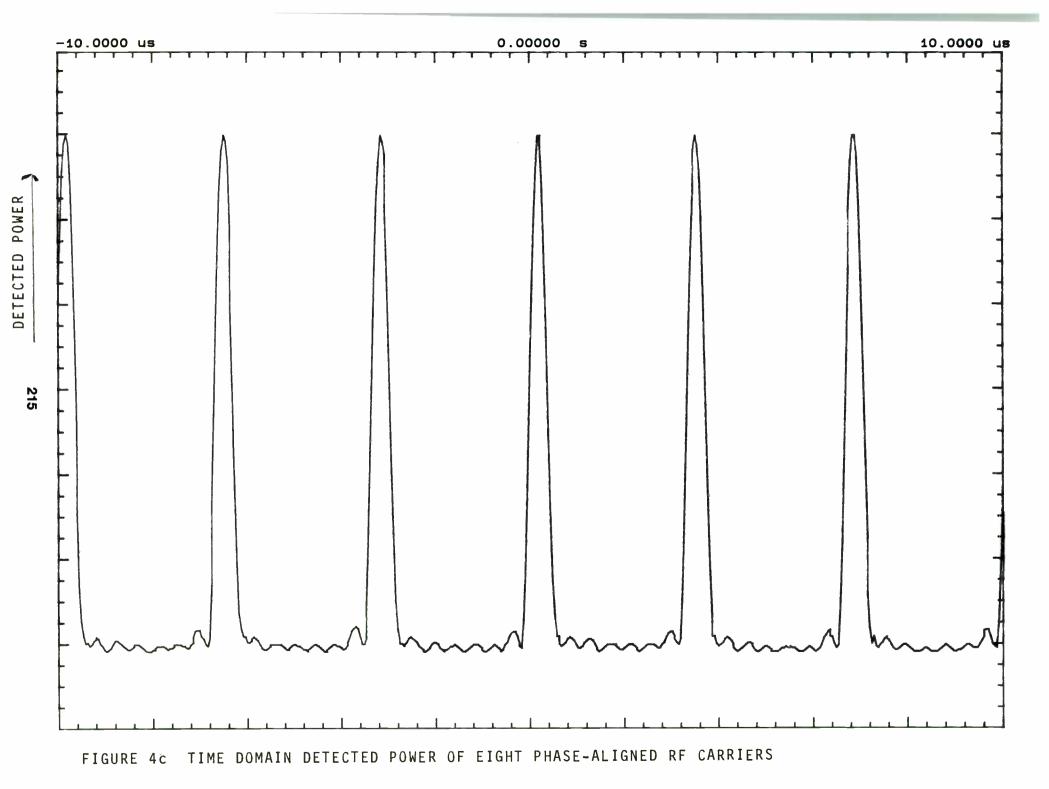

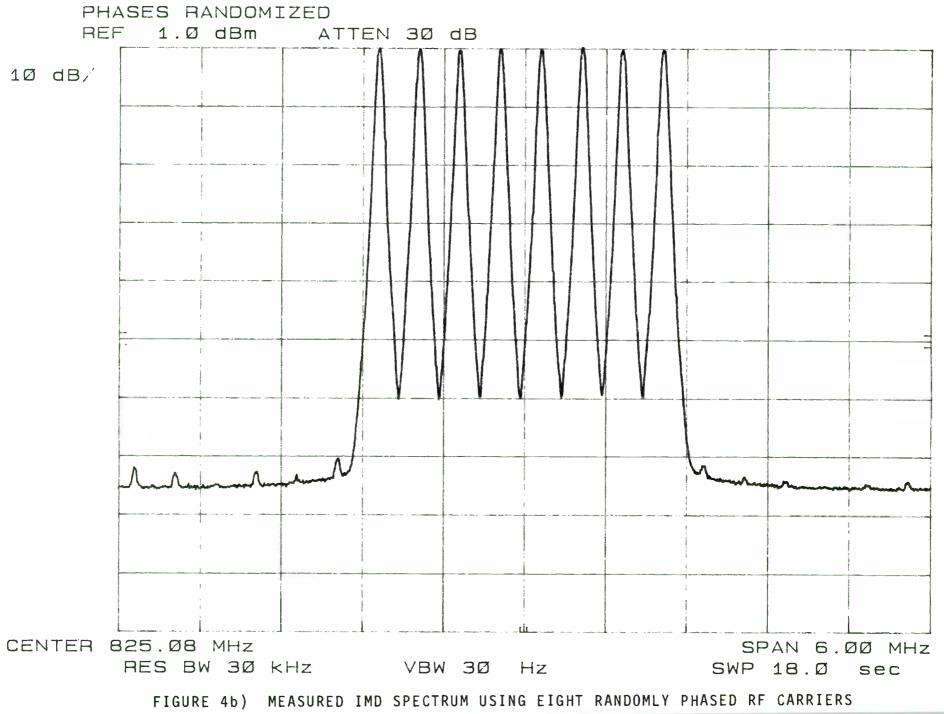

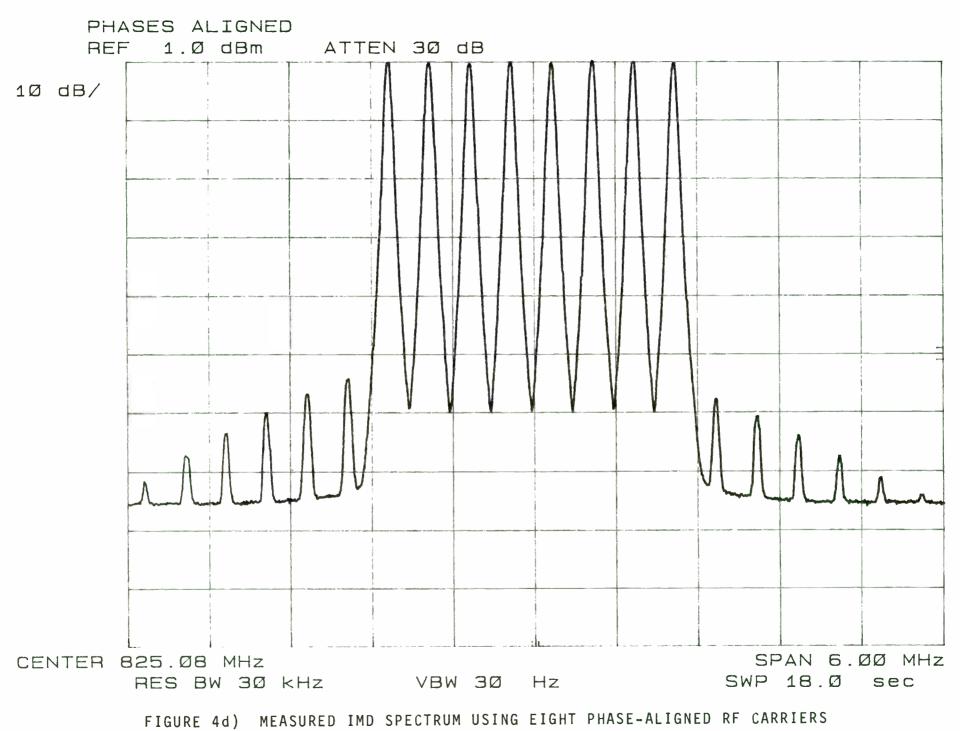

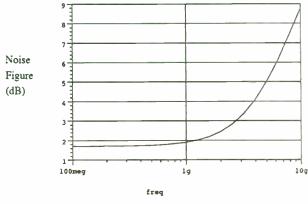

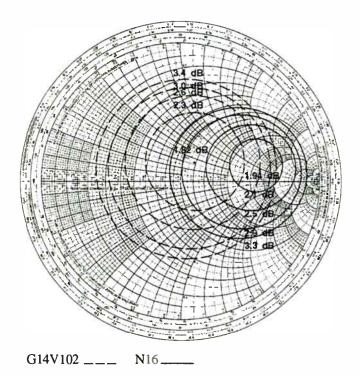

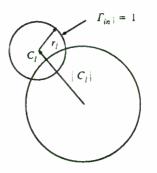

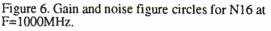

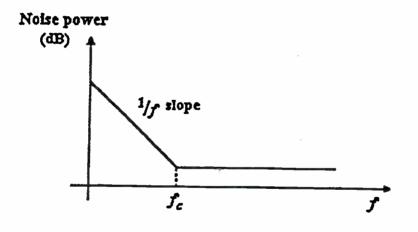

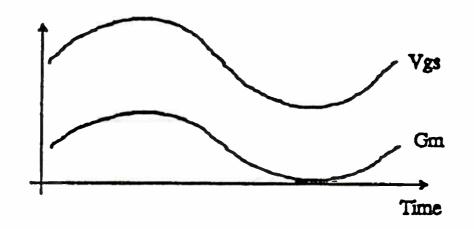

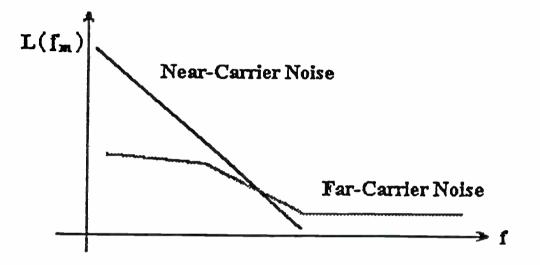

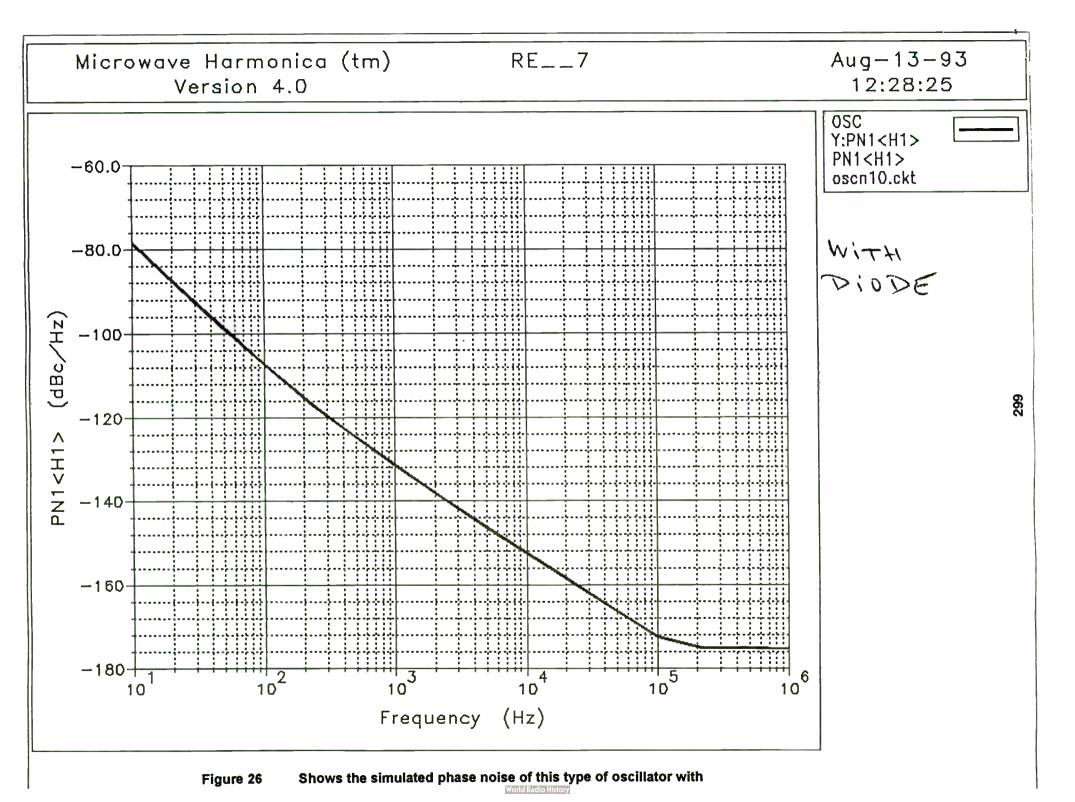

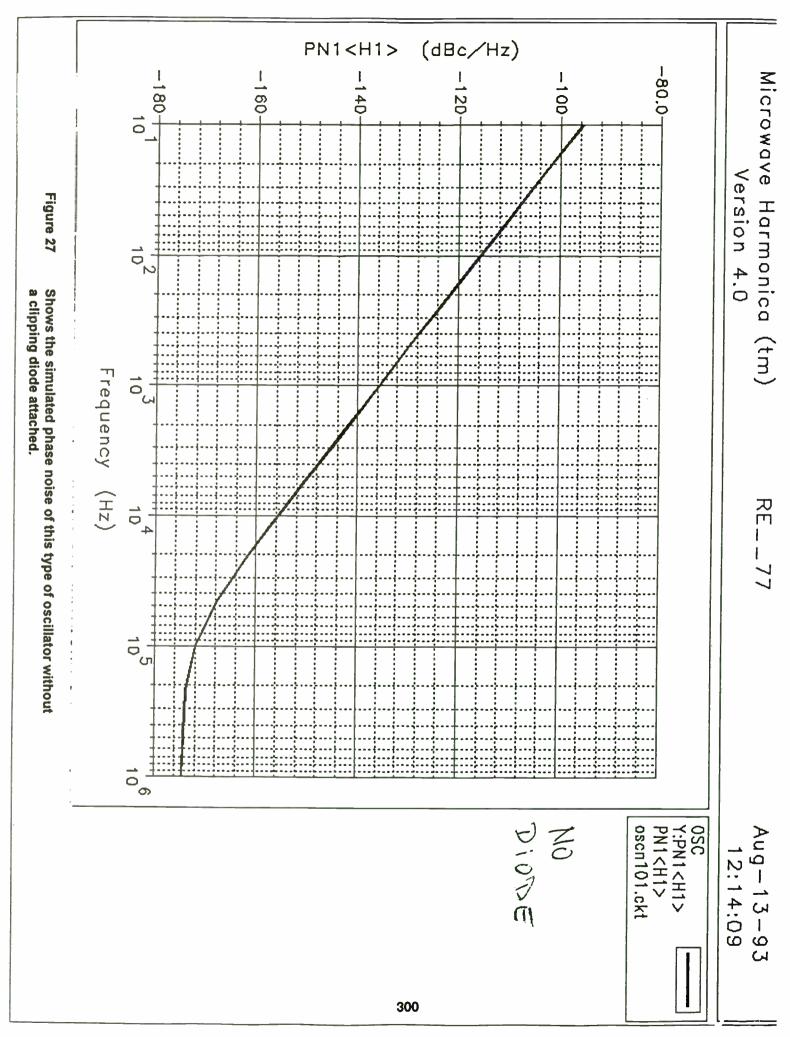

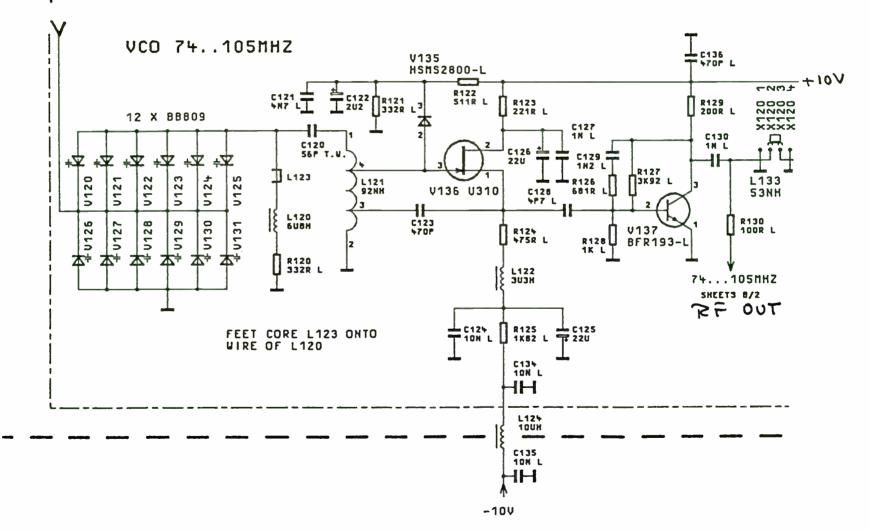

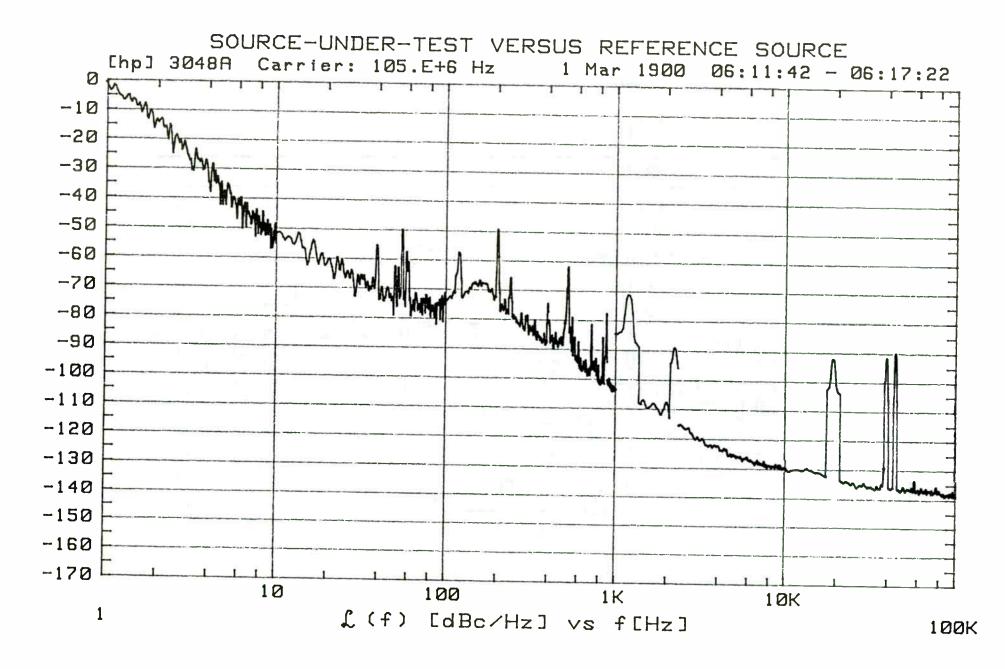

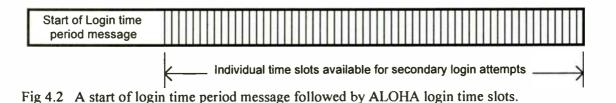

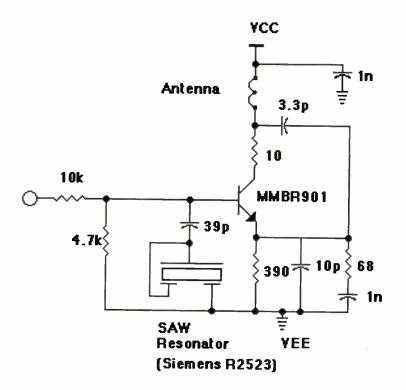

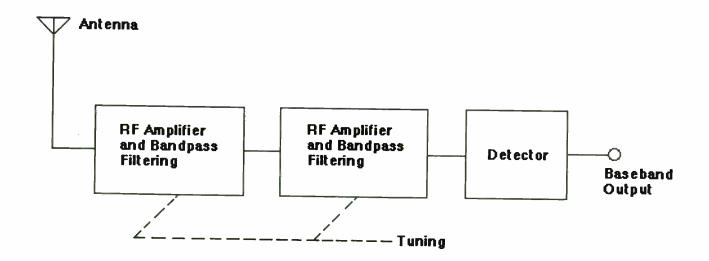

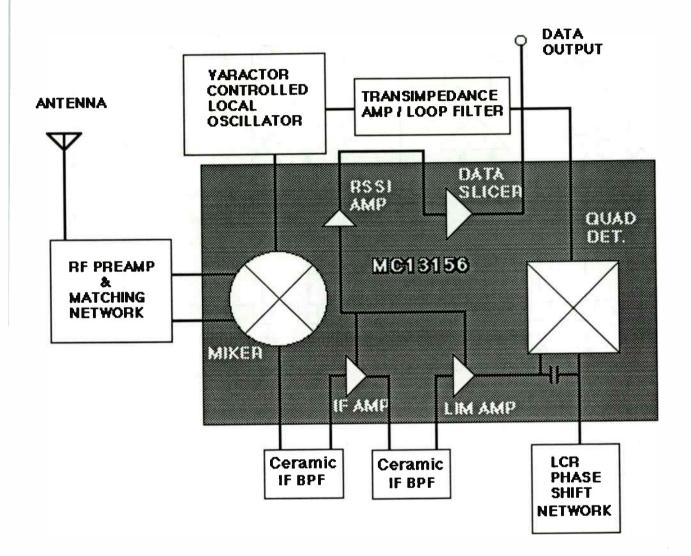

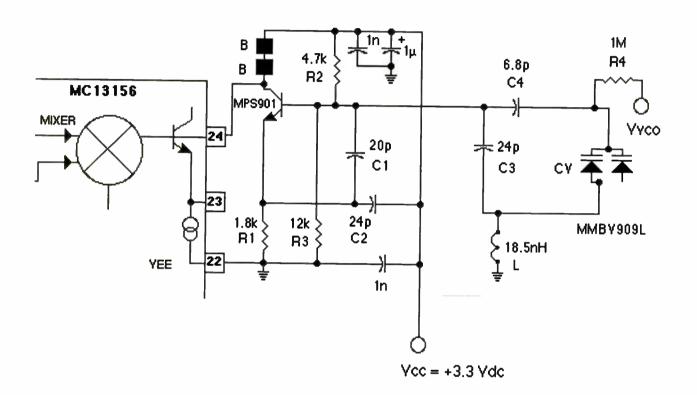

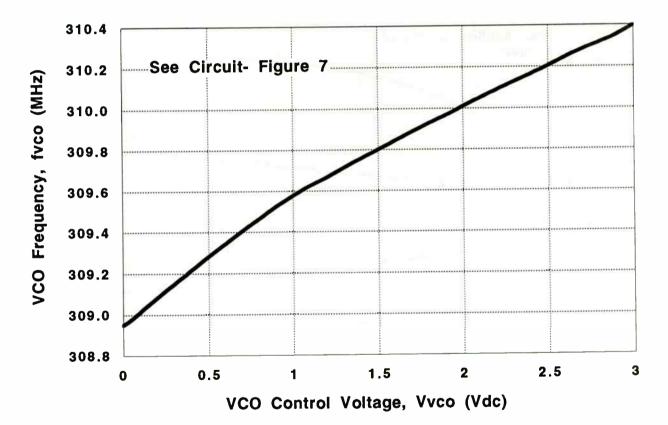

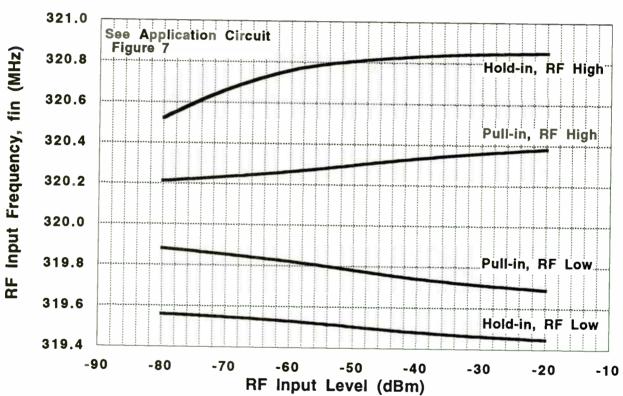

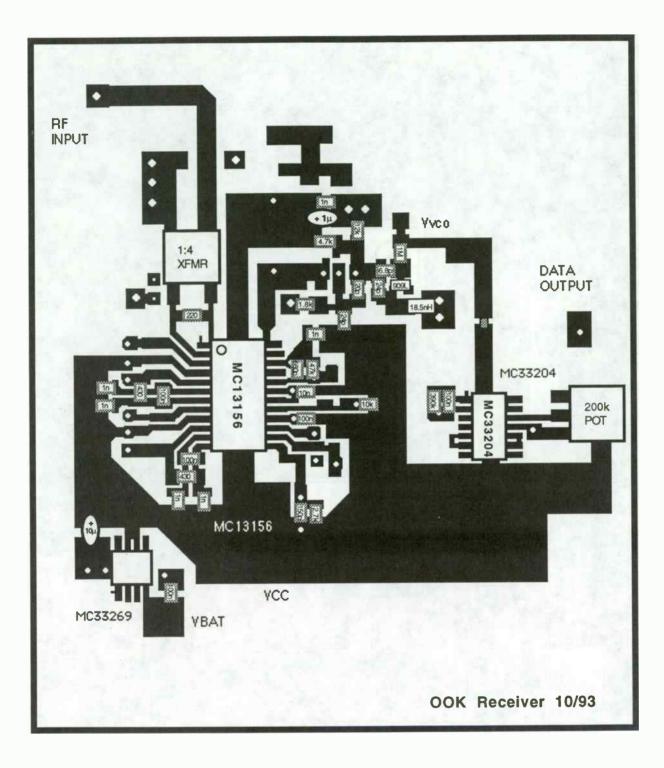

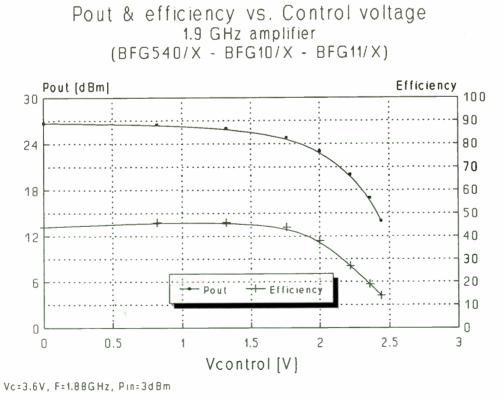

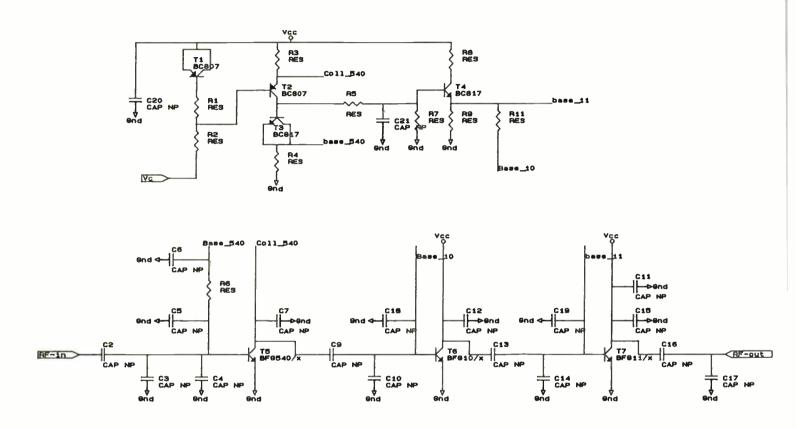

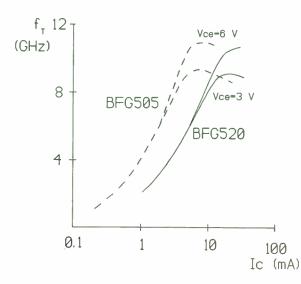

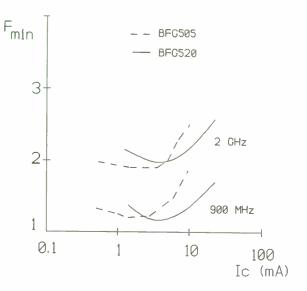

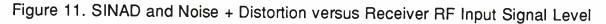

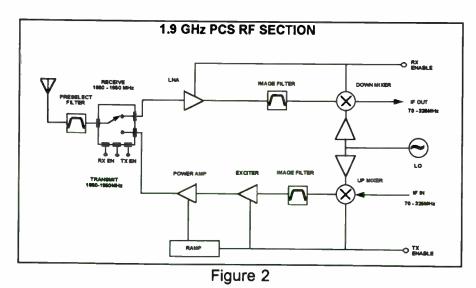

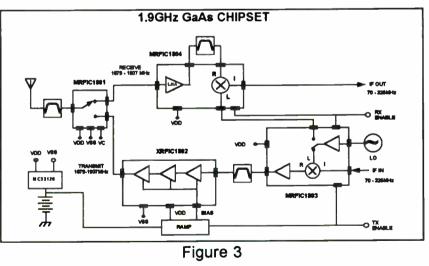

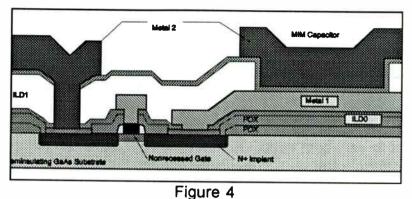

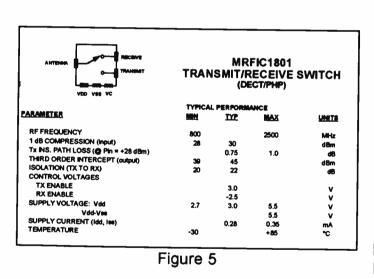

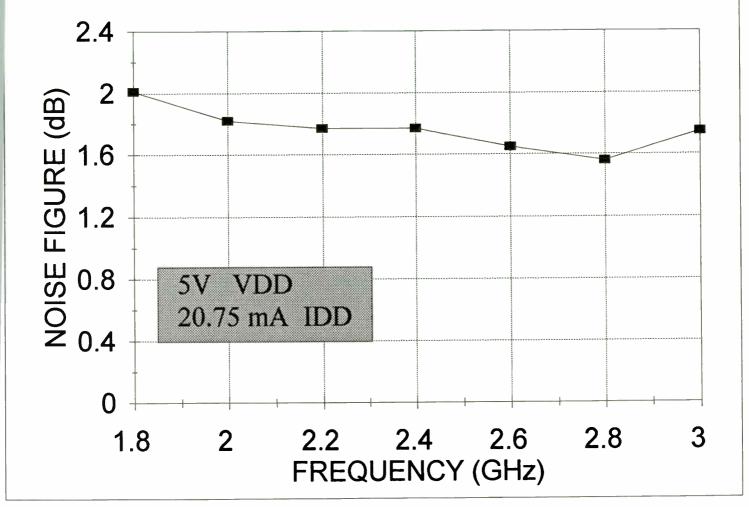

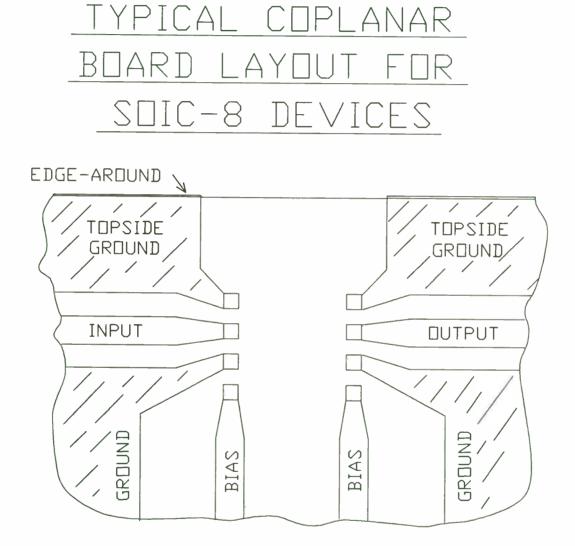

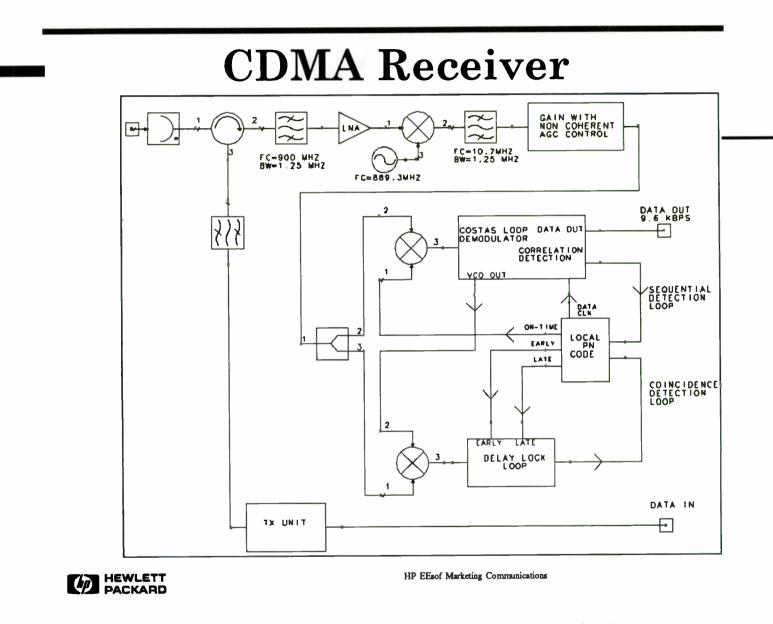

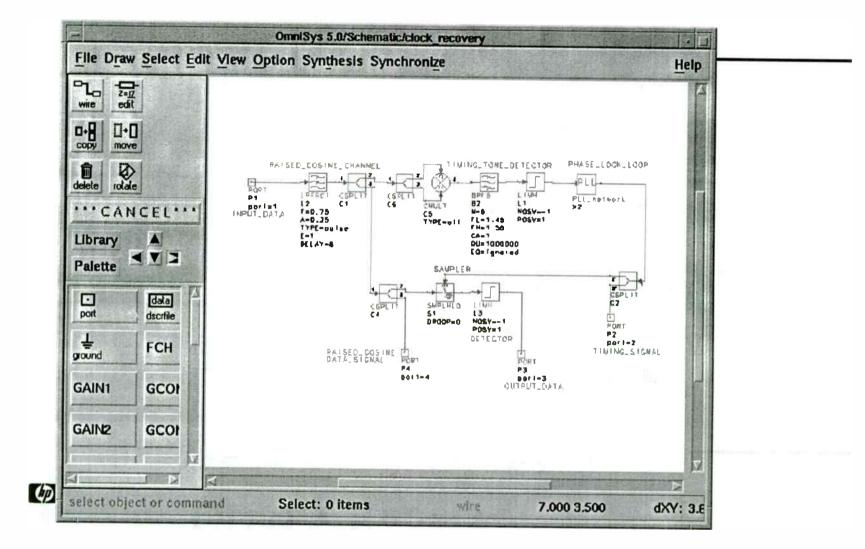

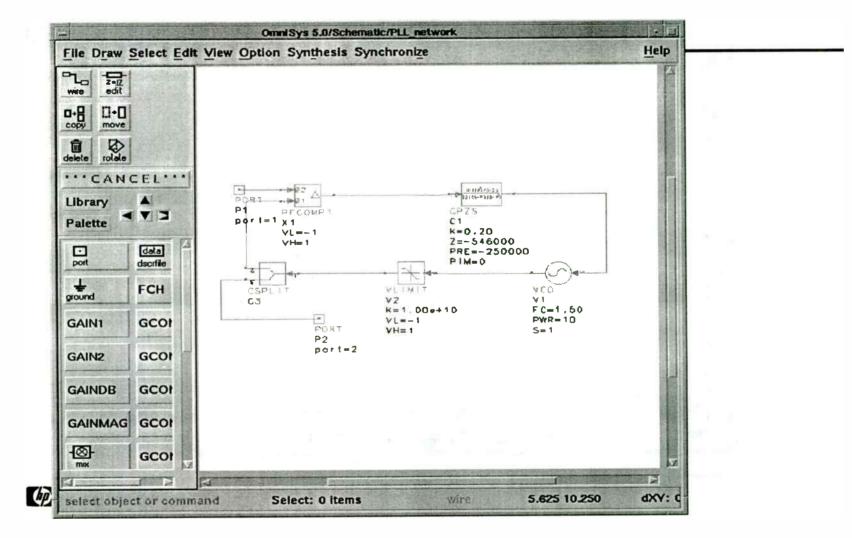

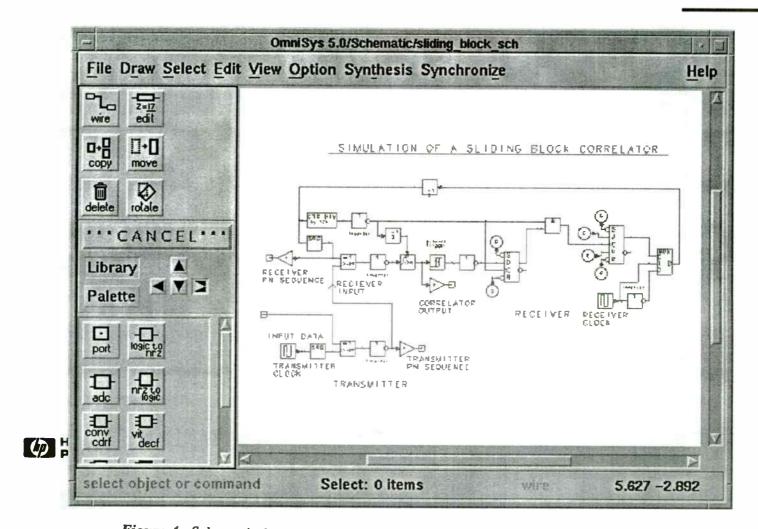

CCDs transfer packets of charge under clock control. The packets reside in potential wells created by MOS capacitors (see figure 1). Because of leakage currents the charge packets cannot be stored indefinitely; hence, CCDs are dynamic devices. In modern CCD technology this leakage current ("dark current") is very low, and storage times of 100s of  $\mu$ s at room temperature is possible. Storage times decrease with increasing temperature.