# **Conference Proceedings**

Tampa Convention Center Tampa, Florida

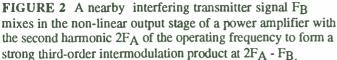

# Conference **Proceedings**

Copyright © 1993 Argus Business All rights reserved

Argus Business 6300 S. Syracuse Way Suite 650 Englewood, Colorado 80111 (303) 220-0600

World Radio History

# TABLE OF CONTENTS

. .

| Session A-1, B-1 — Digital Communications and DSP                   | Tradeoffs in Practical Design of Class E High-Efficiency RF<br>Power Amplifiers |

|---------------------------------------------------------------------|---------------------------------------------------------------------------------|

| An ISM Band Design for WLAN and PCS                                 | Nathan O. Sokal, Laszio Drimusz, Design Automation;                             |

| Robert I Zaurel                                                     | Istvan Novak, Technical University of Budapest                                  |

| GEC Plessey Semiconductors                                          |                                                                                 |

|                                                                     | High Power, Low Frequency Microstrip Switches                                   |

| Integrated Modem/RF Design Architectures for Reduced                | S. Irons, E. Higham                                                             |

| Power, Increased Capacity F-QPSK Wireless Systems                   | M/A-COMN/A                                                                      |

| Kamilo Feher                                                        |                                                                                 |

| University of California, DavisN/A                                  | Class-E Power Amplifier Delivers 24 W at 27 MHz at 89-92%                       |

|                                                                     | Efficiency, Using One Transistor Costing \$0.85                                 |

| A DSP Microprocessor Based Receiver for a Cosine Transition-        | Nathan O. Sokal, Ka-Lon Chu<br>Design Automation                                |

| shaped BPSK Signal<br>Bruce H. Williams, Roy E. Greeff              | Design Automation                                                               |

| Paramax Systems Corp                                                | A LIHE/I Band FET Madula for Pulsed Power Avianias                              |

|                                                                     | Applications                                                                    |

| Designing a High Performance Monolithic Digital BPSK                | Frank Sulak, Ken Sooknanan, Toru Nakamura,                                      |

| Modulator                                                           | Al Rosenzweig, Adrian I. Cogan                                                  |

| Frank Hayden, Robert J. Zavrel                                      | MicroWave Technology, Inc                                                       |

| GEC Plessey Semiconductors                                          |                                                                                 |

|                                                                     | Session C-1, D-1 — Wireless Personal                                            |

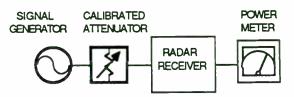

| Session A-2, B-2 — Test & Measurement                               | Communications                                                                  |

|                                                                     |                                                                                 |

| Methods for Estimating and Simulating the Third Order               | Frequency Synthesizer Strategies for Wireless                                   |

| Intercept Point                                                     | Bar-Giora Goldherg                                                              |

| Carl Stuebing, Mojy C. Chian                                        | Sciteq Electronics, Inc                                                         |

| Harris Semiconductor                                                |                                                                                 |

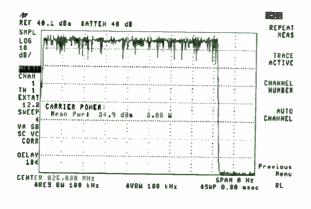

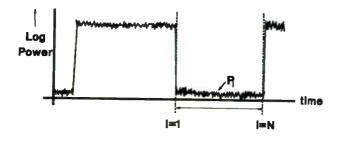

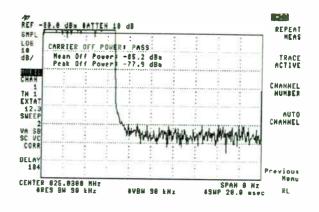

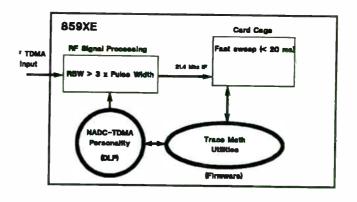

|                                                                     | TDMA Transmitters — Characterizing Power, Timing and                            |

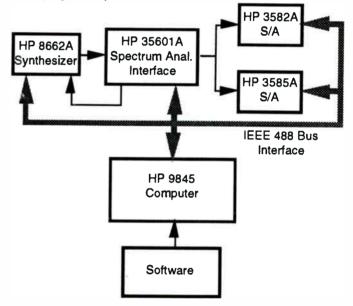

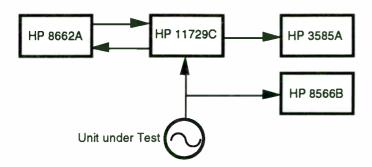

| Low Cost Phase Noise Measurement Technique                          | Modulation Accuracy                                                             |

| Jim H. Walworth<br>Tampa Microwave Lab, Inc                         | Helen Chen                                                                      |

| Tampa Microwave Lab, Inc                                            | Hewlett-Packard Co145                                                           |

| Externally-Induced Transmitter Intermodulation:                     | Destruction of a Low Down In Duilding Window                                    |

| Measurement and Control                                             | Performance Simulation of a Low-Power In-Building Wireless                      |

| Ernie Franke                                                        | Centrex System<br>Douglas Alston                                                |

| E-Systems ECI Division                                              | BellSouth TelecommunicationsN/A                                                 |

|                                                                     |                                                                                 |

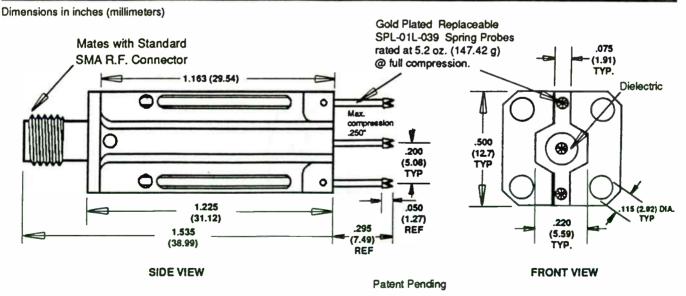

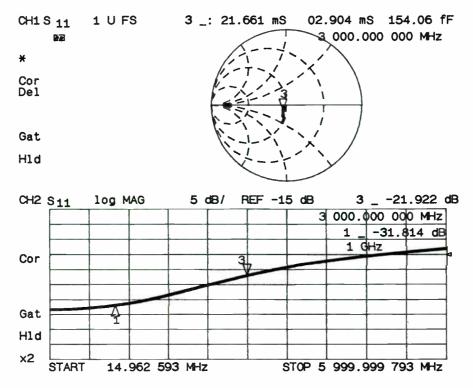

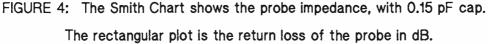

| A 3 GHz 50 Ohm Probe for PCB Measurements                           | Practical Applications of a Low Cost Low Noise GaAs PHEMT                       |

| Joel Dunsmore, Hewlett-Packard Co;                                  | MMIC for Commercial Markets                                                     |

| Robert Kornowski, Motorola;                                         | Al Word Henrik Morkner                                                          |

| Chuck Tygard, Everett-Charles Tech                                  | Hewlett-Packard Co163                                                           |

|                                                                     |                                                                                 |

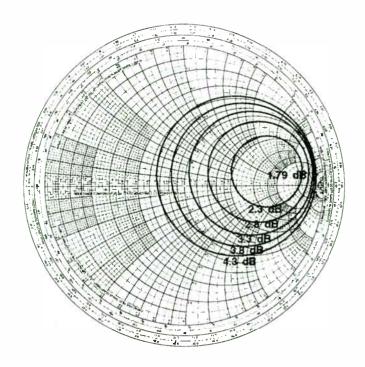

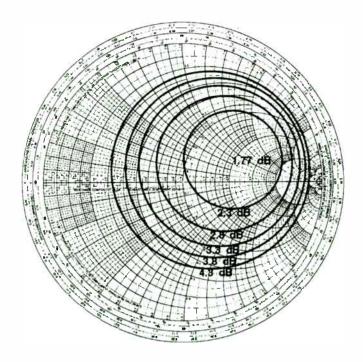

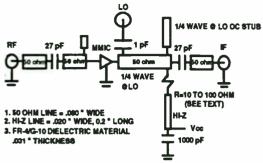

| Low Cost RF Tuner System for JDC Load Pull and SSPA Design          | Highly Integrated GaAs MMIC RF Front End for PCMCIA                             |

| Christos Tsironis, Dominique Dubouil                                | PCS Applications                                                                |

| Focus Microwaves Inc65                                              | J. Mondal, S. Geske, T. Kotsch, A. Laundrie, G. Dietz,                          |

| Notes Plana and Only Management on High Ohend Ditalay               | E. Bogus, J. Blubaugh, S. Moghe                                                 |

| Noise Figure and Gain Measurement on High Speed Bipolar             | Northrop Corp                                                                   |

| Junction Transistors                                                |                                                                                 |

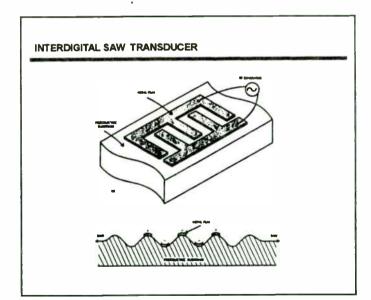

| Wayne Jung, Tektronix, Inc.;<br>Paul Van Halen, Portland State Univ | Low Power Transmitter Design Using SAW Devices                                  |

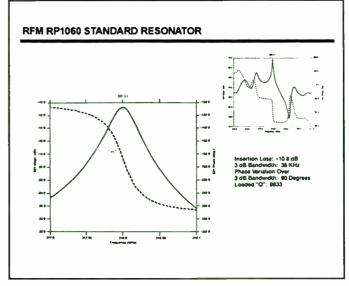

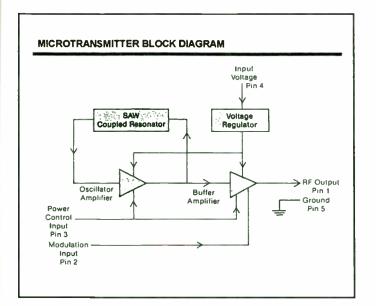

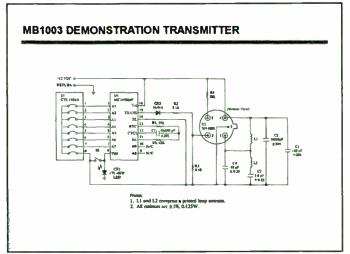

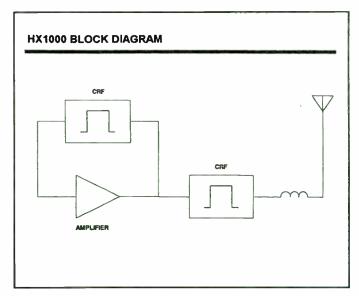

|                                                                     | Earl E. Clark<br>RF Monolithics, Inc175                                         |

| Session A-3, B-3 — Essential RF Circuits                            | Kr Wollolithics, Inc                                                            |

| Session A-3, B-3 — Essential KF circuits                            | Session C-2, D-2 — Specialized Design Techniques                                |

| The Current-Feedback Op Amp – A High-Speed Biulding Block           | Session C-2, D-2 - Specialized Design reclandues                                |

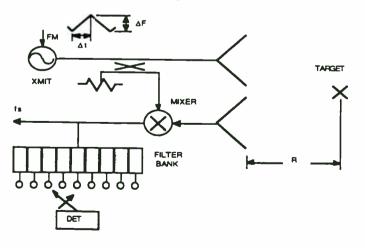

| Anthony D. Wang                                                     | FMCW Radar Architecture                                                         |

| Burr-Brown Corporation                                              | Ken Puglia                                                                      |

|                                                                     | M/A-COM                                                                         |

| The SLAM: A New Ultra-linear Power FET Module Concept               | • • • • • • • • • • • • • • • • • • • •                                         |

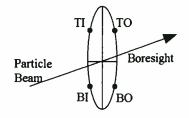

| for HF Applications                                                 | Filter Comparator Network for Beam Position Monitoring                          |

| Adrian I. Cogan, Lee B. Max, Al Rosenzweig                          | Michael Ferrand, Mark McWhorter                                                 |

| MicroWave Technology, Inc                                           | Lorch Electronics                                                               |

|                                                                     |                                                                                 |

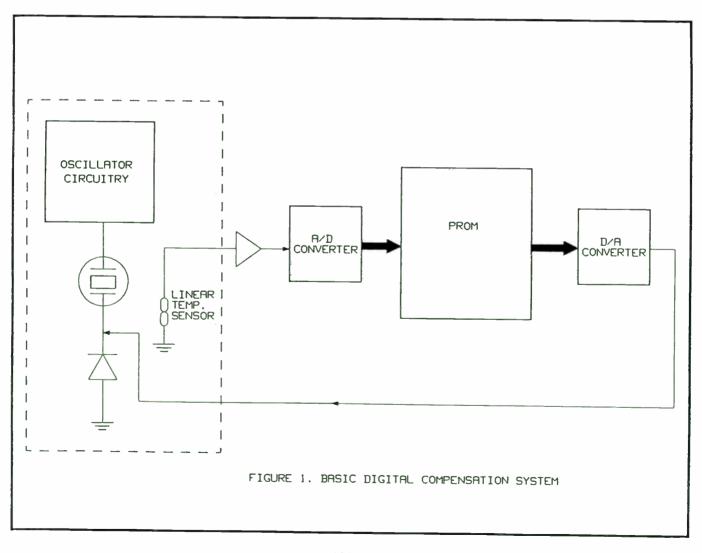

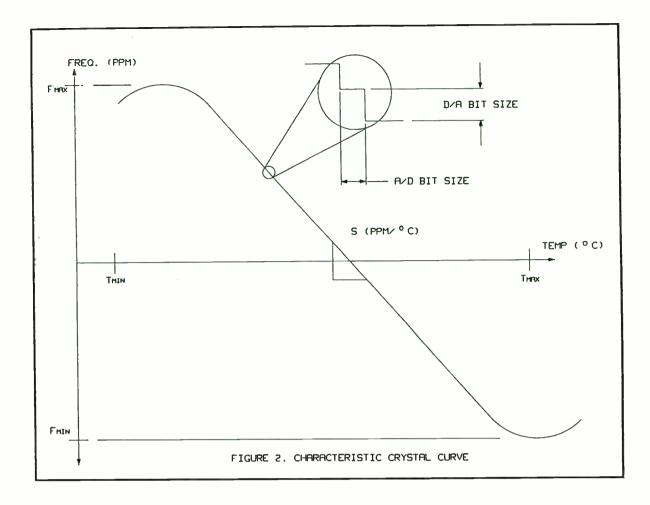

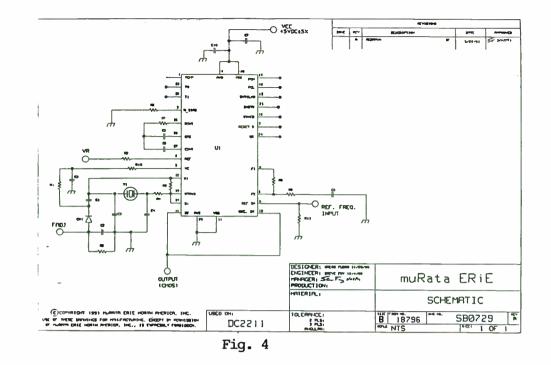

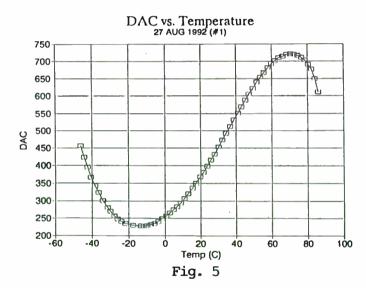

| Digital Temperature Compensation of Oscillators Using a<br>Mixed Mode ASIC<br>Steve Fry               | Coupling of Modes Technique                                                                         |

|-------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|

| Murata Électronics North America186                                                                   | University of Central Florida                                                                       |

| A Synthesizer Design Program With Detailed Noise Analysis<br>Terrence Hock                            | Session E-3 — Practical RF CAD                                                                      |

| National Center for Atmospheric Research                                                              | Basics of CAD at RF for Wireless Circuits and Subsystems<br>Ray Pengelly<br>Compact SoftwareN/A     |

| Donald E. Phillips<br>Rockwell International                                                          | Defining Circuit and Subsystem Specifications for Cordless                                          |

| Linear Frequency Modulation – Theory and Practice<br>Bar-Giora Goldberg, Henry Eisenson               | Telephone Applications<br>Ray Pengelly<br>Compact SoftwareN/A                                       |

| Sciteq Electronics, Inc                                                                               |                                                                                                     |

| Session C-3, D-3 — Analytical Methods                                                                 | Design Examples of Small-Signal Circuits Operating from 3.3<br>to 4.5-Volt Supplies<br>Ray Pengelly |

| RF Active Device Modeling for CAD, A Coming Necessity<br>Gary Roberts                                 | Compact SoftwareN/A                                                                                 |

| Hewlett-Packard Co                                                                                    | Design Examples of Large-Signal Circuits<br>Ray Pengelly                                            |

| Regression Based Algorithms for Inductor Modeling<br>Edmund (Joe) Tillo                               | Compact SoftwareN/A                                                                                 |

| Ford Motor Company217                                                                                 | Using CAD for Circuit Layout and Packaging Design<br>Ray Pengelly                                   |

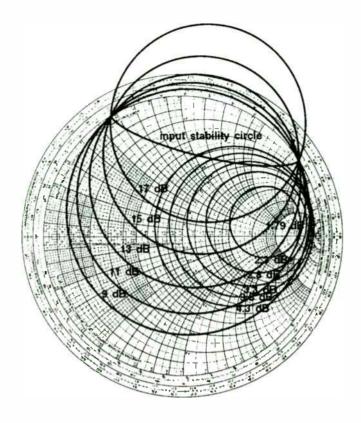

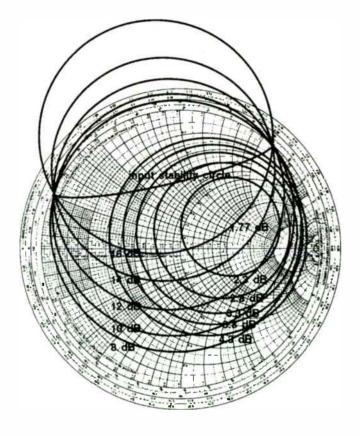

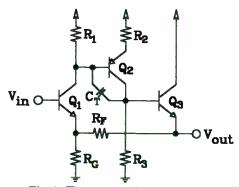

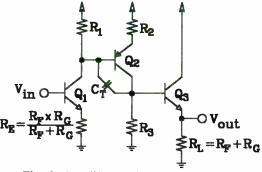

| Computer Aided Design Tools for Small Signal Matching<br>Networks                                     | Compact SoftwareN/A                                                                                 |

| Michael Rothery, Sam Ritchie, Madjid A. Belkerdid<br>University of Central Florida                    | EXPO PLUS SESSION 1 — Satellite and Space Systems                                                   |

| SAW Resonator Oscillator Design Using Linear RF Simulation<br>Alan R. Northam                         | EXPO PLUS SESSION 2 — Components for Space Applications                                             |

| RF Monolithics, Inc235                                                                                | Designing Microwave Circuits for Geosynchronous Space                                               |

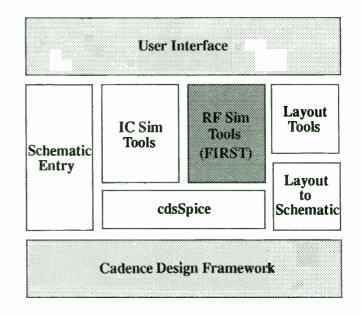

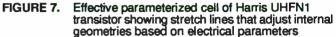

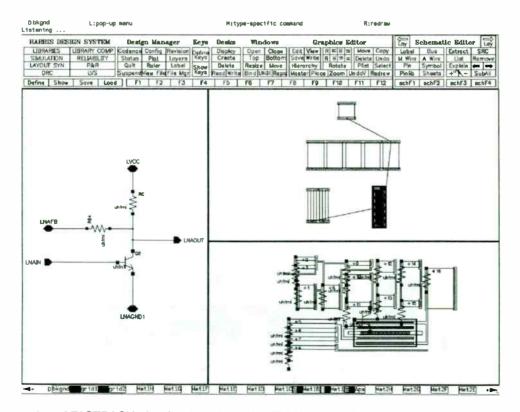

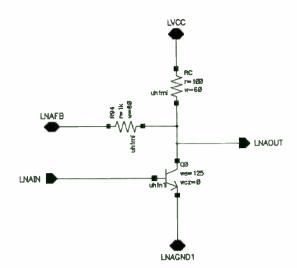

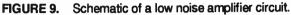

| Embedding RF Design Tools in an IC Design System<br>Mojy C. Chian, Steve S. Majors, Alan G. Whittaker | Applications<br>Ronald Ogan                                                                         |

| Harris Semiconductor                                                                                  | TRAK Microwave Corp                                                                                 |

| Circuits                                                                                              | Low Cost Plated Plastic Diplexers For Use In Commercial<br>Mobile Satellite Communications          |

| Daren McClearnon<br>Hewlett-Packard Co250                                                             | Chip Scott<br>Teledyne Microwave                                                                    |

| Session E-1 — Wireless Applications                                                                   | EXPO PLUS SESSION 3 — Satellite and Space Systems                                                   |

| A Monolithic 915 MHz Direct Sequence Spread Spectrum<br>Transmitter                                   | Satellite Channel Utilization in the Presence of Rain                                               |

| Stephen Press, Jeff Barry, Jim Marsh<br>Tektronix, Inc259                                             | Attenuation<br>Kaivan A. Karimi, Valentine Aalo                                                     |

|                                                                                                       | Florida Atlantic University                                                                         |

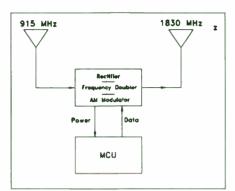

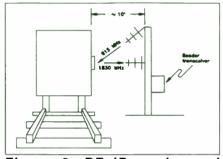

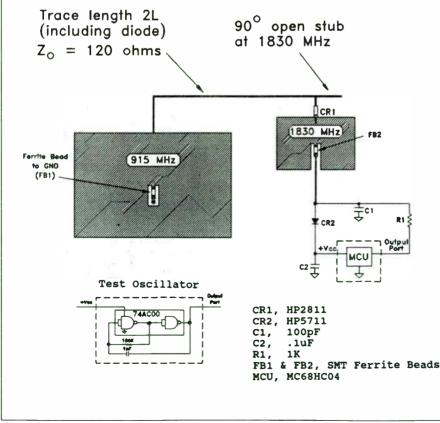

| A Low Power RFID Transponder<br>Raymond Page                                                          |                                                                                                     |

| Wenzel Associates, Inc                                                                                | Hardware Verification of Communication System Simulations<br>Henry F. Helmken                       |

| Session E-2 — RF Circuits and Systems                                                                 | Florida Atlantic University                                                                         |

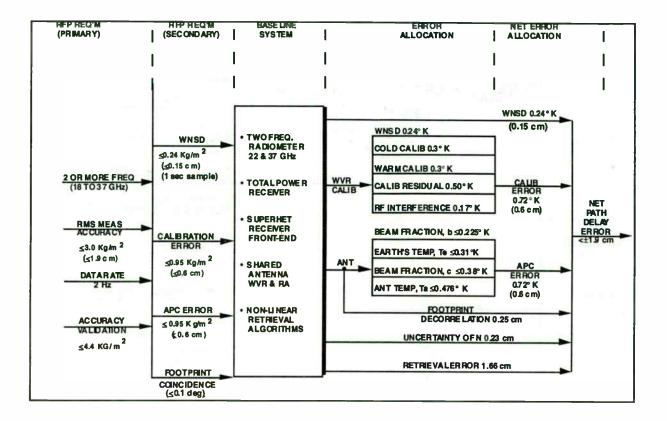

| Multi-Component Module for High Speed Passive Design                                                  | GFO Water Vapor Radiometer<br>Muhammad A. Malik                                                     |

| Mark Brooks<br>Thin Film Technology                                                                   | E-Systems, Inc                                                                                      |

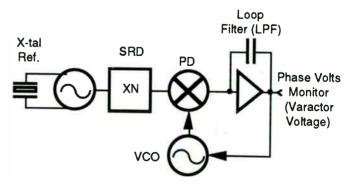

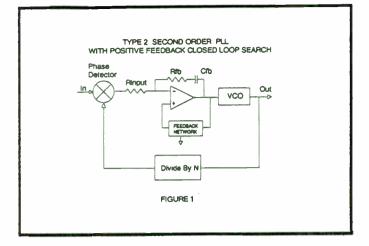

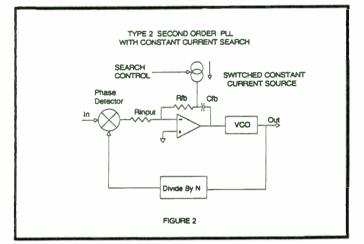

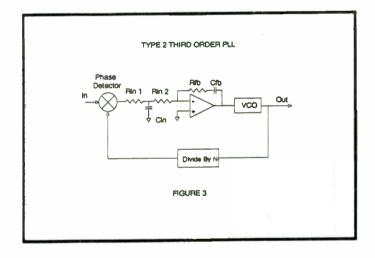

| Design of a Search Based PLL                                                                          |                                                                                                     |

| Michael F. Black<br>Texas Instruments                                                                 |                                                                                                     |

|                                                                                                       |                                                                                                     |

## An ISM Band Design for WLAN and PCS

Robert J. Zavrel

Worldwide Applications Manager, WLAN Products GEC Plessey Semiconductors 1500 Green Hills Road Scotts Valley CA 95066

#### 1. Introduction

To realize the promise of personal wireless communications on a massive scale, a complex set of business, political, and technical issues must be resolved. New frequency allocations seem to be a certainty within the next few years. However, by using the existing ISM bands reliable and economic systems can now be configured addressing very large volume markets. This paper presents the design methodology for such a system.

The three Industrial, Scientific, and Medical band allocations (ISM bands) in North America are quite attractive for a wide range of would-be wireless services. These bands not only pose the opportunity but also design challenges to realize effective systems. FCC regulations permit up to one watt of RF output power without requiring a license. In order to facilitate *some degree* of interference rejection in a license-free environment, spread spectrum techniques are mandated. The two types of spread spectrum techniques that are permitted are frequency hopping and direct sequence. Much has been written over the past few years about these two techniques and the reader can seek the references for background information. (Ref. 1 & 2).

#### 2. Architecture Considerations

In order to optimize an architecture one of three bands and one of two spread spectrum techniques must be chosen. A complex set of system trade-offs must be considered in this decision-making process. A review of the status of the three bands, together with design considerations can lead to a rational choice.

The 902 MHz band was recently labeled "the kitchen sink band" (Ref. 3). This is indeed an accurate description. Multiple users include radiolocation services, amateur radio, fixed and mobile services and AVM. In addition, the FCC has proposed wind profile radars and AVM for the entire band. Furthermore, the 902 MHz band is only available in North America limiting its desirability for most high volume manufacturers. This band, however, has the advantage that silicon devices can be used efficiently in both the receiver front ends and transmitter PAs. Use of this band for PCS and/or WLANs is tenuous at best.

The 2.4 GHz band is partially allocated to amateur radio. Microwave ovens also operate in this band. However, compared with the 902 MHz band, these users are comparatively benign. Another major advantage of the 2.4 GHz band is that allocations exist within the 2.4 to 2.5 GHz band in North America, Europe, and Japan. For these reasons the 2.4 GHz band was chosen for our design solution.

The 5.8 GHz band is also attractive, but the higher operating frequency offers greater design and manufacturing problems and higher power consumption. This band might be quite interesting for future generation products, if exclusive PCS/WLAN bands are not allocated in the near future.

Having chosen the 2.4 GHz ISM band the question of which spread spectrum technique remains. There are two basic spread spectrum techniques: direct sequence and frequency hopping. In contrast to direct sequence systems, frequency hopping systems offer better immunity to interference. In short, a direct sequence system relies totally upon processing gain (and the resulting jamming margin specifications) to reject in-band interference.

$G(p) = 10 \log Bs/Rd$

where G(p) is the processing gain, Bs is the spreading bandwidth, and Rd is the data rate and

Mj = G(p) - (L + (S/N))

where Mj is the jamming margin, L is system losses, and S/N is the signal-to-noise ratio necessary to maintain a given bit error rate (BER) or error probability (Pe).

These equations are fundamental to direct sequence systems. Indeed, even low data rate direct sequence systems mandate the use of sophisticated power level control of all transmitters operating in band. The unpredictability of the ISM band environment typically renders direct sequence systems unreliable for use in these bands. There may be some special circumstances where direct sequence can be the technique of choice, but the interference trade-off is omnipresent. Perhaps the most important mitigating circumstance is for data rates exceeding about 2 Mb/sec. It is difficult to achieve over 2 Mb/sec. with frequency hoppers while maintaining the initial advantages of the hopping system. However, as data rates increase in the direct sequence system, the vulnerability also increases. Furthermore, for each doubling of data rate, the system noise figure increases by 3 dB resulting in a net reduction in range. These might be an acceptable trade-offs, particularly if communications is intended for very short ranges, perhaps under 3 meters. However, for most practical applications, the data rate in ISM applications is limited to about 2 Mb/sec.

Frequency hopping systems rely upon the more traditional techniques of radio receiver design: dynamic range, sensitivity and selectivity. These basic specifications, in turn, reflect such specifications as noise figure, local oscillator spectral purity, filter skirts, and intermodulation. In contrast, in-band selectivity in direct sequence systems relies completely upon processing gain.

For example, in a typical ISM direct sequence system, 5 dB of jamming margin is typical (for 800 kb/sec data rates, 10E-5 BER, operating in the US 2.4 GHz ISM band). In contrast, frequency hopping systems easily provide 60 dB of ultimate rejection by using cascaded SAW filters. Under some circumstances the LO phase noise can become more constraining than the IF filter skirts. In frequency hopping systems, a narrow-band interferer might "wipe out" several hopping channels. With proper coding, however, individual "packets" can be recovered despite the loss of a considerable number of hopping channels (Reference 4). In the direct sequence case, if the interferer exceeds the jamming margin of the system, the bit error rate (BER) begins to increase. Further reduction in interference will upset the link and communications will be lost completely rather than a percentage of packets. Some direct sequence systems combine frequency channelization to provide filter selectivity in addition to processing gain. However, it is our conclusion that once frequency division schemes must be employed, the designer might as well limit bandwidth to the baseband and realize the full advantages narrow-band systems offer. In other words, use frequency hopping.

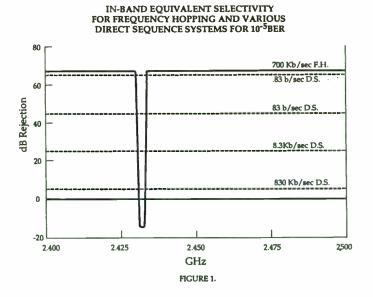

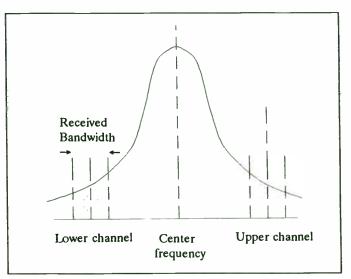

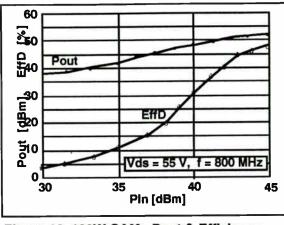

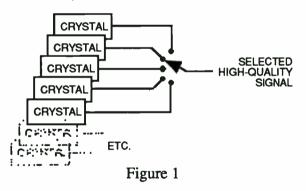

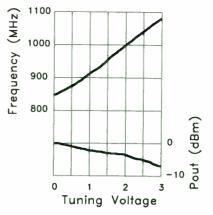

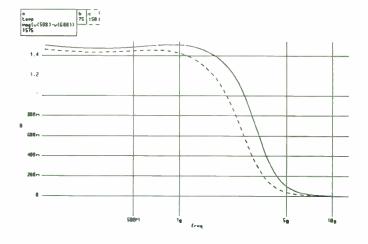

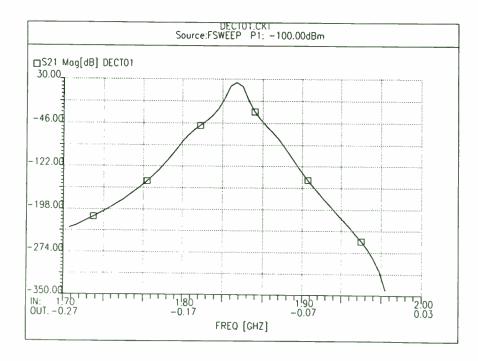

Direct sequence systems can be very attractive only in a pristine wide band where all in-band transmitters are rigidly controlled. Direct sequence systems must control all transmitters' power output in real time, or one or more transmitters are likely to interfere with each other. Thus, direct sequence systems must assume that all users of the spectrum within range will conform to that system's control mechanisms. If any signal source appears in-band that exceeds the jamming margin of a receiver, the bit error rate or the link itself will be compromised. Of course, this premise is not possible to attain within the ISM bands. Indeed, even with exclusive use of a band complex control mechanisms are required to control the real-time power outputs of the transmitters. Furthermore, these control mechanisms compromise the power consumption and price of the system. The ISM bands are anything but pristine. Indeed the ISM bands are hostile communications environments requiring excellent interference-avoidance techniques. The ISM band environment is not unlike circumstances presented to electronic warefare (EW) designers. It is interesting to note that tactical military communications systems typically use frequency hopping techniques to mitigate enemy jammers. Figure 1 shows in-band equivalent selectivity for the 83 MHz-wide 2.4 GHz band for various data rates of direct sequence systems

contrasted against a frequency hopping system. The jamming margin numbers are based on 10 dB necessary C/N ratio for 10 E-5 BER and 5 dB system loss.

#### 3. System Requirements

Having settled upon 2.4 GHz frequency hopping as the architecture of choice, a detailed design analysis can now proceed. In order to "open" the very high volume data and voice communications markets certain criteria must be met in the design solution:

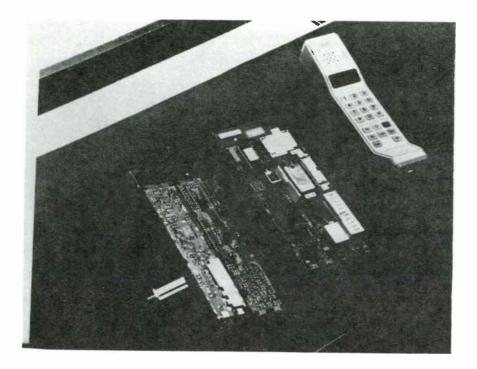

Power consumption: about 350 mW in receive mode Cost: under \$100.00 for high volume (>500K/year) Size: PCMCIA form factor (about 2x3 inch circuit board)

Performance:

A. Data Rate: up to 1 Mbit/second

B. Dynamic range: >60 dB (defined by filter skirts, noise figure, and compression point)

C. Dual antenna diversity

D. Receiver noise figure: <10 dB

E. double conversion superhet design for outstanding adjacent channel rejection

F. Tx-to-RX and RX-to-TX time <4 uS

G. Hopping settling time: <100uS

H. RF Power Output: selectable 10 or 100 mW.

The extremely fast transmit-receive transition time and hopping speed permits the use of state-of-the-art control algorithms and excellent acquisition times. Double conversion minimizes image response, permits the use of two SAW filters for outstanding selectivity, and permits limiting and detection at the optimum frequency. Most of the end-use system requirements such as range, BER, data rate, and reliability reduce to the set of RF specifications listed above. These specifications, in turn, must conform to the power, cost and form factor requirements. These combined specifications reflect a fairly high performance microwave transceiver built on a credit card from full custom devices, selling for under \$100.00. This challenge has been met with the GEC Plessey DE6003. A microwave transceiver on a credit card sized circuit board with the above set of specifications speaks for itself as a state-of-the art design.

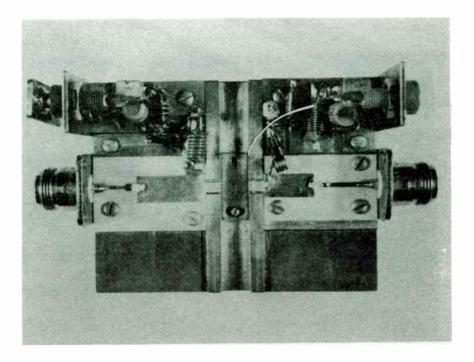

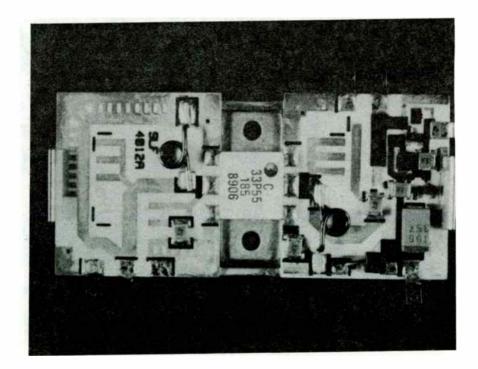

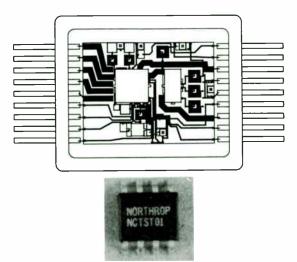

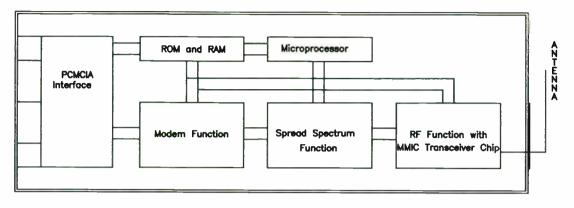

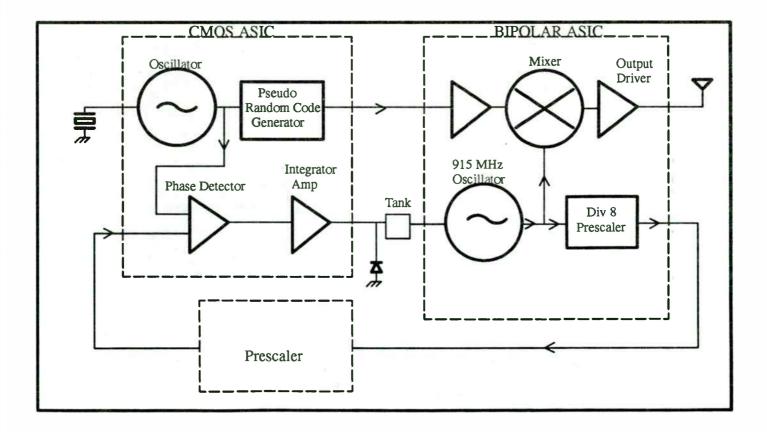

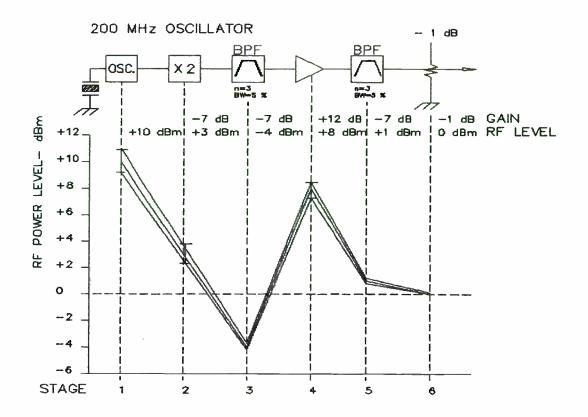

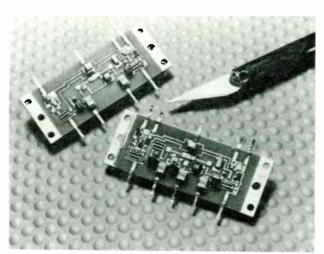

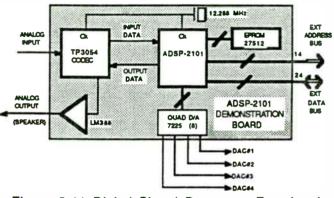

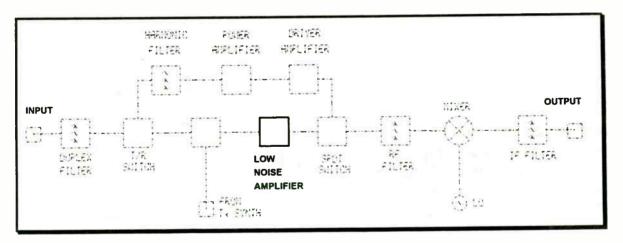

#### 4. RF Transceiver Description

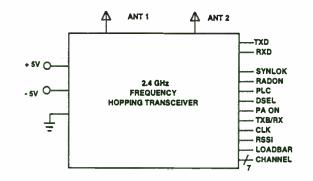

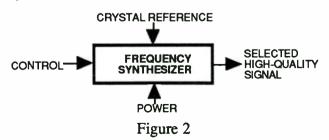

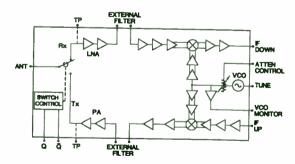

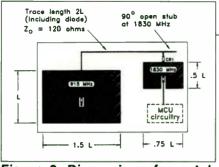

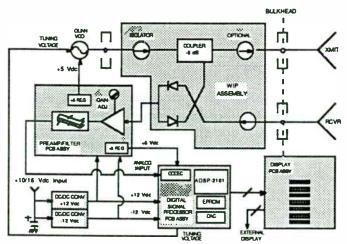

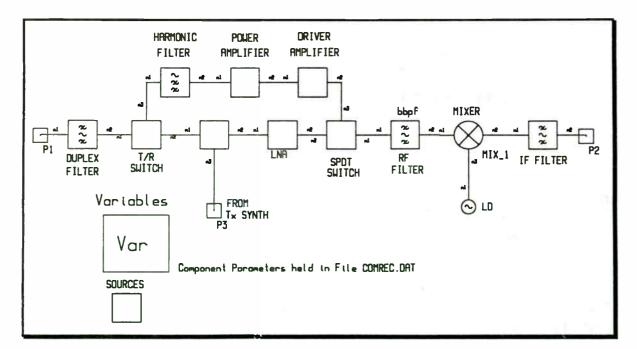

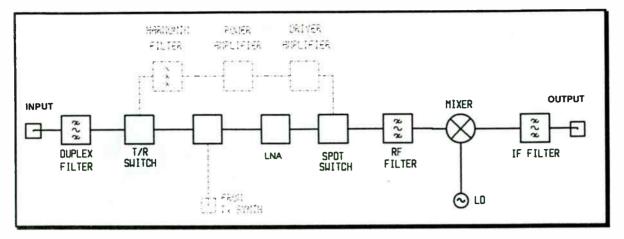

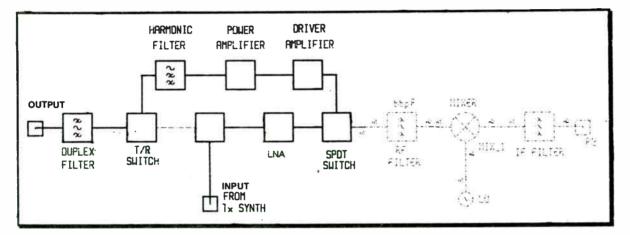

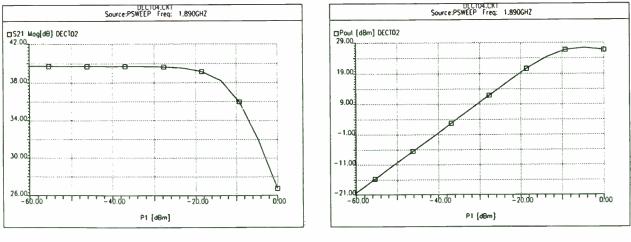

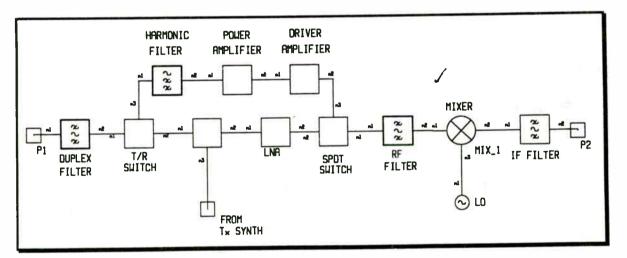

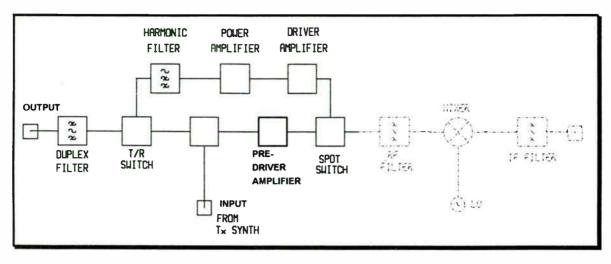

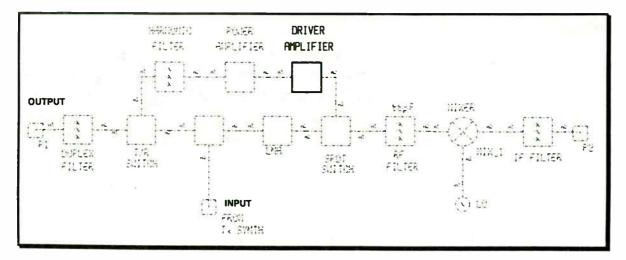

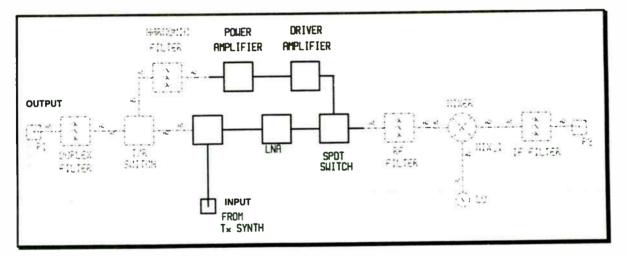

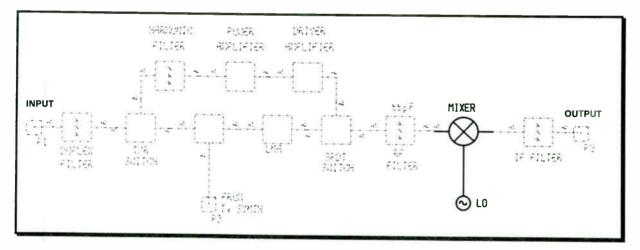

The DE6003 represents the most advanced licensefree radio data transceiver available for low power, low cost, miniature packaged and high performance applications. These transceiver modules are designed for portable battery-operated data or voice communications equipment. For example, lap-top and hand-held computers, cordless telephones, point-ofsale, inventory, security, and medical equipment can utilize these modules to great advantage. Figure 2 shows an interface block diagram of the DE6003 with power supply, antenna, and digital control bus.

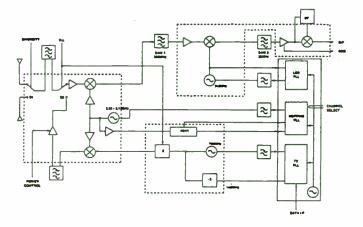

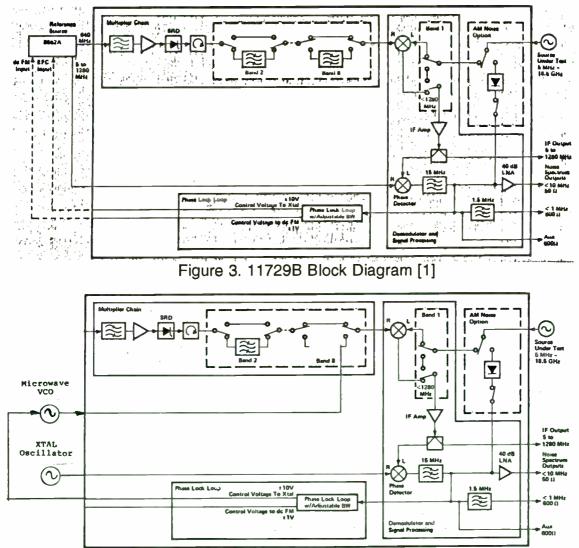

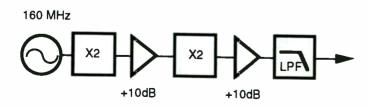

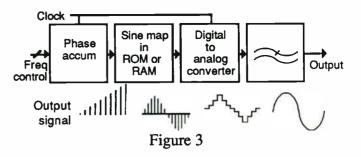

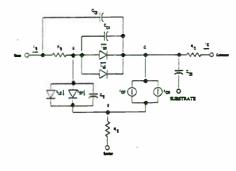

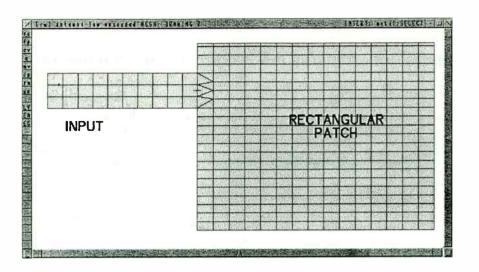

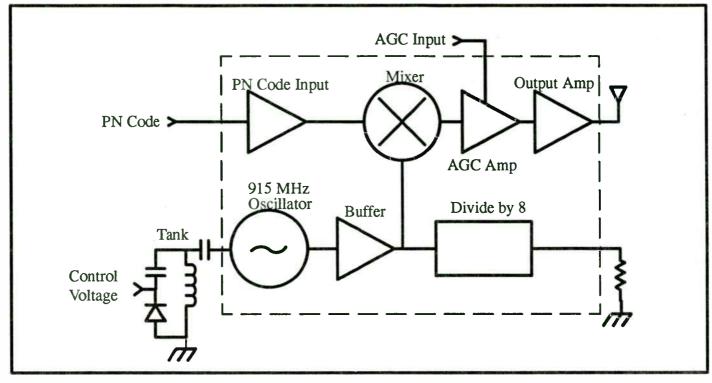

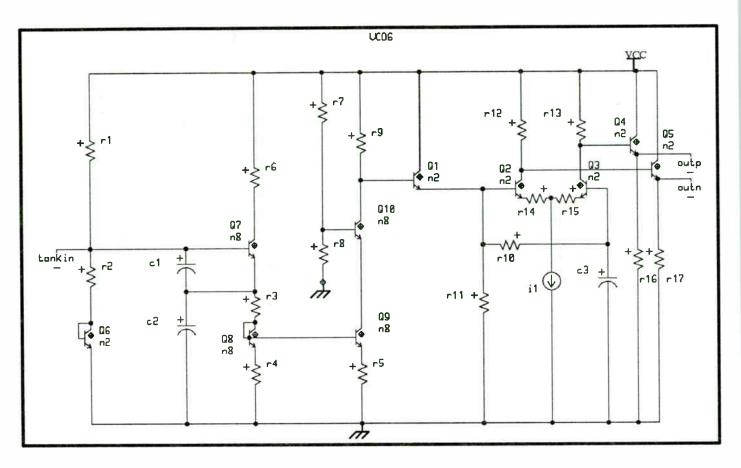

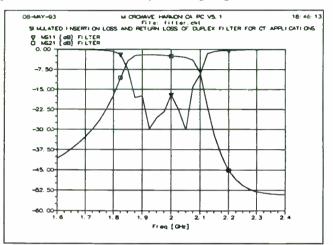

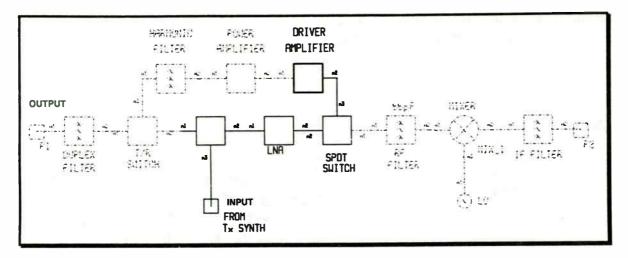

Figure 3 shows an RF functional diagram with divisions of the integrated circuits delineated. Three PLL synthesizers run continuously to provide the very high hopping and TX/RX speeds. A patented divide-by-two switch is used in the transmit loop to prevent interference into the receiver IF. Dual conversion facilitates excellent selectivity and image rejection.

The DE6003 covers 2.400 to 2.500 GHz and utilizes a binary Gaussian frequency shift keying modulation scheme (GFSK). GFSK has several distinct

advantages over alternative baseband schemes. The IF systems do not require linearity and the complications involving AGC design. Limiters are easy to design and manufacture and signal strength indication (RSSI) is also relatively easy to realize. In the hostile ISM environment with interference and multipath distortion, GFSK also provides a effective and simple solution. SImplicity, manufacturability, low cost, and low power consumption are all inherent characteristics of GFSK systems. The main disadvantage of GFSK is a comparatively low bit/Hz/sec specification (typically 0.7 bits/Hz/sec.). Also, M-ary FSK, particularly 4FSK can be used to increase data rates well above 1b/Hz/sec. and is being investigated for second generation products. However, most of the current high volume market applications require well under 1Mb/sec. rates, reflecting the DE6003 specifications.

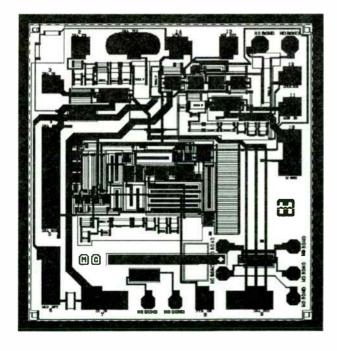

Early in the design stage of the transceiver it was realized that the effort would necessitate full custom integrated circuits. During innumerable design reviews power consumption (milliwatt by milliwatt) and cost were traded-off the various performance requirements (data rate, dynamic range, speed and others). GEC Plessey's design effort was greatly enhanced in that the IC, filter, and system designers all report through the same program manager. Consequently, optimum designs were possible from the various processes used while maintaing tight scheduling. Aggressive pricing was realized because all the critical components for the transceiver are fabricated within the same company. The radio takes full advantage of the three most important semiconductor manufacturing processes: GaAs, high speed bipolar, and CMOS.

World-class design people and facilities exist within GEC Plessey's multiple facilities. (GEC Lincoln started

in the microwave business during World War II manufacturing point contact diodes for early radar sets.) Since then, the company has built a very impressive array of RF integrated circuits encompassing markets from consumer to space qualification. Traditional strengths have included synthesizers and low power RF integrated circuits, both critical to successful specification conformance.

The WLAN development program was broken into three stages:

1. Proof of concept (completed March, 1992)

2. System development "Alpha" units (completed September, 1992, DE6002)

3. Production prototype samples (available February 1994, DE6003)

"Beta" units of the DE6003 are currently being evaluated and design-ins are taking place in many companies.

The next generation of specifications will require MCM (multi-chip module) technology. The notion of a monolithic WLAN radio with the above specifications is currently not possible. Optimum performance must be realized by using optimum processes and designs for each function. There are no silicon processes currently available that meet all these requirements. Furthermore, Bi-MOS processes have limited advantages in meeting overall system objectives.

#### 5. Digital Control Interface

Table 1 shows the details of the digital control interface. All interface functions to the DE6003 use standard CMOS levels. All the interface connections are digital except where otherwise noted. The digital control interface allows direct control of the radio's

functions. The digital hardware that interfaces to the radio can be tailored to any specific application and any set of regulations. Consequently the DE6003 affords the system designer great flexibility for data, voice, and even video transmission systems. All the remaining circuitry to complete a data communications transceiver can be implemented in a CMOS ASIC.

#### <u>TABLE 1</u>

TXD: Serial data input to the transmitter RXD: Serial data output from the receiver SYNLOK: Indicates when all PLL synthesizers are locked RADON: On/off switch for the radio PLC: Power level control selects either 10 or 100 mW transmitter RF output DSEL: Diversity select one of the two antennas PAON: On/off switch for the PA transmitter stage TXB/RX: Selects either transmit or receive modes CLK: 10 MHz clock output (200 mV PTP) RSSI: Received signal strength indicator (analog voltage proportional to dB received signal level). LOADBAR: Loads frequency channel select CHANNEL SELECT: Parallel seven bit word defines frequency used by the radio from 2.4 to 2.5 GHz.

#### 6. Antenna and EMI Considerations

Placing the antenna on the circuit board is not acceptable because the radio would require shielding to prevent unwanted radiation from the radio circuitry. Also, the optimum placement of the antenna is typically not the optimum place for the radio proper. Maximizing receiver and transmitter performance only to compromise the effort by poor antenna placement is an iladvised proposition. Most antenna problems can be minimized if external antennas are permitted. At 2.4 GHz external antennas can assume small profiles, with helictical configurations fitting into one or two inch plastic hemispheres.

Incorporation of these microwave radio transceivers into portable computer-based hardware will require some new approaches to hardware design. Electromagnetic considerations, up to now, have been limited to electromagnetic interference (EMI) issues in computer hardware design. Extensive shielding is required to keep unintentional RF noise produced by high speed computer clocks from escaping the computer and interfering with radios, televisions, and other equipment. With radios and antennas "inside" the electromagnetic considerations become far more complex. Indeed, shielding will remain critical, but at the operating frequencies (2.4 GHz) the "unit" must provide the opposite function: transmit and receive antenna. Indeed, electromagnetic issues necessitate new ways of thinking about computer product engineering. Handheld and laptop microprocessor based equipment must now be considered complex electromagnetic devices.

#### 7. Protocols, control, and standards

It is one problem to build an optimum radio for the above given constraints. It is another problem to control the radio, control the communications link, provide for clock recovery, synchronization, and interface to the data bus and networks. This is the work of the protocol circuit. GEC Plessey is developing several protocols and is providing interfaces to many of the important data communications standards: ISA, ETHERNET, PCMCIA, and others. Much of this work is covered by NDAs (non-disclosure agreements) in place with major customers. Consequently details cannot as yet be published. Suffice it to say that the protocol and interface considerations are not trivial and that a complete solution (antenna to data communications standard socket) will be available in early 1994. However, the key to opening the ISM and other radio bands is to build adequate radios.

The entire question of protocols begs the introduction and adoption of standards for WLANs. These standards will have to embrace not only ISM band radios but also IR and other radio band systems as well. The *IEEE 802.11* group and the new *IEEE Communications Society Technical Committee on PCS* are working on such standards. In addition, ETSI is working on European standards and *WINForum* (an industry group) is dealing with securing new bands and writing an etiquette for these bands' use. Clearly, convergence on standards will occur within the next year, either through these and other standards groups or by de-facto standards.

#### 8. Conclusions

Efficient, reliable, and cost effective wireless digital communications systems are now possible to address the high volume portable markets. The opening of this market has been accomplished by providing good microwave transciever specifications derived from exhaustive market analysis and design processes. Reliable use of the difficult ISM environment has been accomplished with designs that can be translated to new WLAN/PCS frequencies quickly when these bands become available. Effective use of these radios requires interface CMOS circuits curently under development. Standards must also be set and accepted. Electromagnetic issues for antennas and shielding must also be rectified. A comprehensive program to address WLAN and PCS radio applications is in place at GEC Plessey Semiconductors. Standard

products that solve all problems between the data communications interface and the antenna will soon be available on the open market.

#### 9. References

1. *Spread Spectrum Systems*, Robert C. Dixon, John Wiley & Sons, 1984

Spread Spectrum Communications, Volumes 1, 2, &

Marvin K. Simon, Jim K. Omura, Robert A. Scholtz, Barry K. Levitt, Computer Science Press, 1985

3. The Kitchen-Sink Band: 902 MHz, "It Seems to Us...", <u>QST</u>, David Sumner, American Radio Relay League, June, 1993

4. Wireless Access Methods and Physical Layer Specifications, Ed Geiger, IEEE 802.11 Document number IEEE P802.11-93/104, July, 1993

FIGURE 2 Functional Block Diagram of DE6003

FIGURE 3 Detailed Block Diagram of DE6003

# A DSP Microprocessor Based Receiver for a Cosine Transition-shaped BPSK Signal

Roy E. Greeff and Bruce H. Williams Unisys Government Systems Group 640 N. 2200 W. MS-F1E03 Salt Lake City, UT 84116

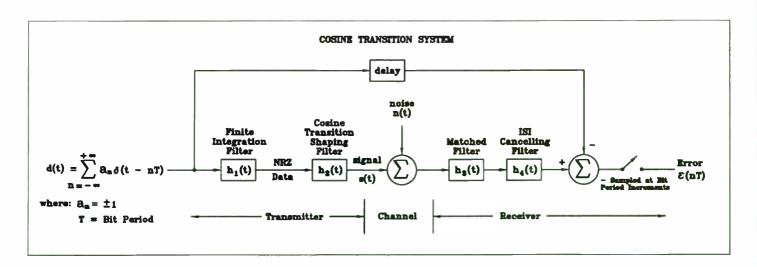

In a previous paper (RF EXPO East 92) we discussed a cosine transition-shaping BPSK modulator implemented by direct digital synthesizers. This waveform has advantages over conventionally filtered BPSK in that filter distortion effects can be tightly controlled and reproduced consistently This paper continues with the development of a system utilizing the shaped BPSK signal. This paper discusses a DSP microprocessor receiver for the cosine transition-shaped BPSK signal.

#### **Modulation Waveform**

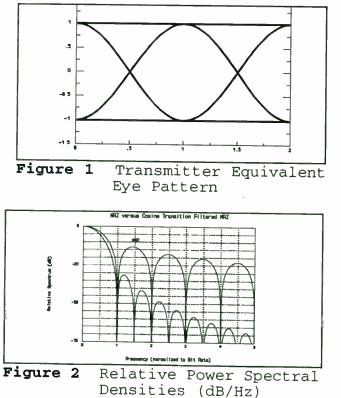

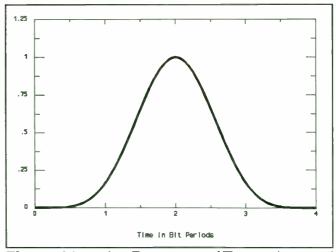

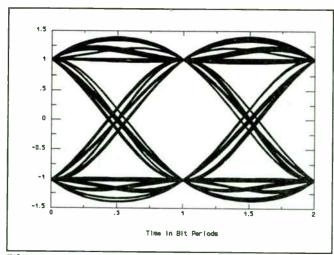

By shaping NRZ data transition shapes one can effectively filter the spectrum. Figure 1 shows an "eye-pattern" for the shaped NRZ signal.

Figure 2 demonstrates the effect of cosine transition shaping on the spectrum. Energy in the sidelobes is significantly reduced.

The receiver necessary to optimally demodulate this signal differs from conventional BPSK demodulators in that the matched filters are combined with intersymbol interference (ISI) canceling filters.

#### Main Receiver Functions

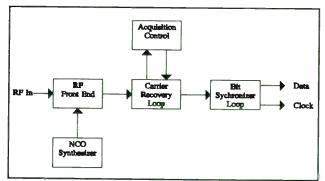

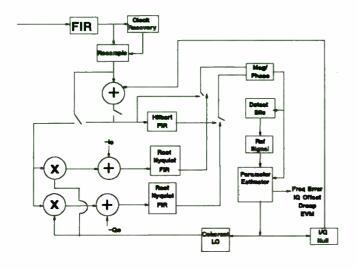

Figure 3 shows a block diagram of the main receiver functions necessary for PSK demodulation.

Figure 3 Main Receiver Functions

The RF front end consists of filters, the AGC, downconverter, and the A/D converters. The rest of the functions are implemented using DSP products. These functions in the past have been implemented using analog circuits. With the advent of higher speed DSP products (such as the Texas Instruments TMS320C40) these functions can now be implemented digitally for low data rates. The receiver built at UNISYS implements the Data Recovery Loop, acquisition control, and the bit

8

Figure 4 RF Front End

synchronizer with software loaded on a TI C40 floating point processor. Considerable flexibility is obtained by programming these functions into the C40. This flexibility is most apparent in the different algorithms that can be programmed (with no hardware changes) into the C40 for different modulation types (PSK, FSK, etc.).

### **RF Front End**

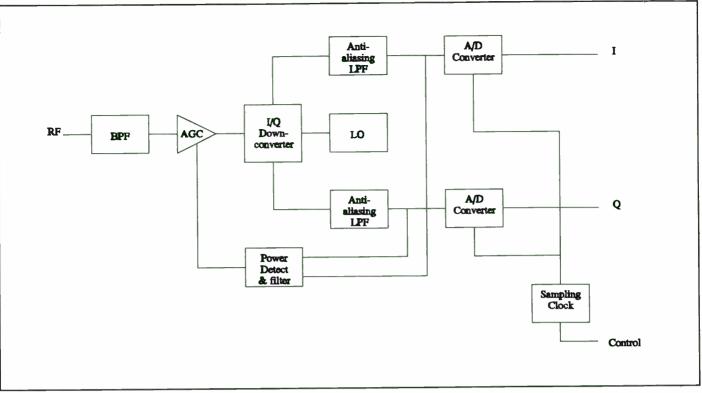

Figure 4 shows a block diagram of the RF font end of the receiver.

The first filter is used to limit the noise bandwidth of the receiver. It's bandwidth is chosen to be only wide enough for the tuning flexibility required for multiple channels. The AGC amplifiers follow the filter. The detection of power for the AGC is at the output of the anti-aliasing filters. The power detection could occur after the baseband matched filters but if this is done to much power may be input into the I/Q downconverter. Additional AGCing is done at baseband in the demodulator algorithm. After the AGC amplifiers, the signal is downconverted as close to baseband as the frequency uncertainty of the received

signal. An NCO is used as the synthesizer for the downconversion. The resultant I and Q signal is then filtered with the anti-aliasing filters. These signals are converted to digital signals using A/D converters operating at four times the maximum data rate. The sampling rate oscillator is controlled by the demodulator algorithm. The signals are fed to the C40 processors where the samples are used to perform the appropriate demodulation. The RF circuitry can be used with many different data rates and modulation types with no changes to the hardware.

### Software Carrier Recovery Loop

Using DSP techniques to perform the demodulation vs analog techniques has various advantages. A demodulator design using analog circuits may degrade over temperature, vibration or other environmental factors. The software loaded into a digital processor is immune to environmental factors. A software demodulator can be changed easily to accommodate new data rates or even new modulation types. The one advantage that analog circuits have over the same digital

Figure 5 Demodulator Algorithm

implementation is speed. Analog circuits have the capability of operating at much higher data rates. As faster and faster digital components are developed, more and more analog systems will be replaced with digitized systems.

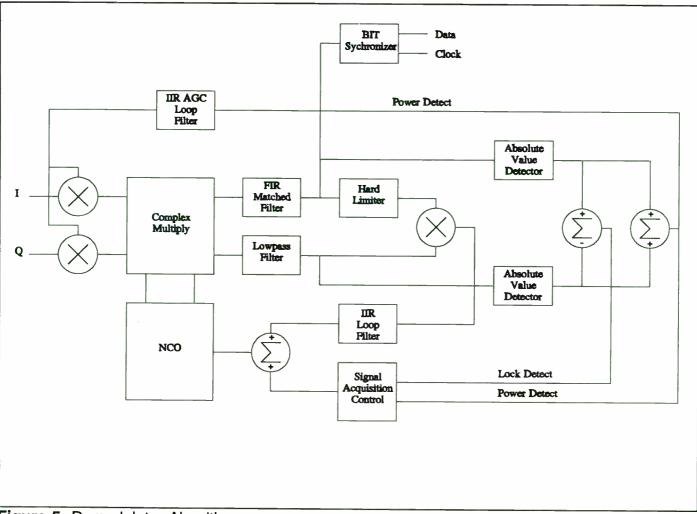

Figure 5 shows a block diagram of the demodulation algorithm. The algorithm is made up of three separate functions: 1) BPSK Carrier recovery loop (CRL) 2) Signal Acquisition Control for the CRL 3) clock regeneration using a bit synchronizer.

The BPSK CRL can be viewed as software implementation of a costas loop. The requirements that need to be met when a loop is designed in the analog world are the same as for loops designed in the digital world.

The digitized complex signal received from the

RF front end is demodulated using the following software functions. Refer to figure 3.

<u>Complex Multiplier</u> - The input complex signal received from the RF front end is first multiplied with the complex signal received from the software NCO which is phased locked to the incoming signal. The resultant signals are the I channel (data channel for BPSK) and the Q channel (the tracking channel for BPSK).

<u>FIR Matched filters</u> - The I channel is filtered using the FIR matched filter discussed earlier. This FIR filter spans 8 data bits or is 32 samples long for signals that are sampled 4 times per bit. The Q channel is filtered using an integrator that has the same delay as the matched filter. Filtering of the Q or tracking channel is actually not required (data aided loop) but is done to make a less noisy lock detect. An integrating filter is used instead of the FIR filter because the integrating filter uses less clock cycles than the FIR to implement.

<u>Hard Limiter</u> - The hard limiter outputs a '1' or '-1' depending on if the sample is positive or negative.

<u>Multiplier</u> - The multiplier simply takes two sample and does a floating point multiply.

<u>IIR Loop Filter</u> - Much work has already been done to analyze 2nd order type 2 loops in the analog world. This work can be used by designing the loop filter using an IIR filter. The weights for the IIR filter can be obtained by taking the transfer function of the filter and using the Bi-linear Z transform.

<u>NCO</u> - The software NCO (Numerically Controlled Oscillator) is basically the same as the hardware NCOs that are now available. The C40 processor keeps a record of phase using an integer 32 bits long. On each sample a delta phase is added to this integer. The first 8 bits of the integer are then used in a look up table that has the sine and cosine functions stored. Frequency is changed by changing the delta phase added to the integer.

The above software functions are all performed between adjacent samples. If the C40 operates at 40 MHz, the data rate is 50 kBs, and four samples are taken for each bit, all the above functions need to be done in 200 clock cycles or 100 instruction cycles (2 clock cycles = 1 instruction cycle). If higher speeds are desired multiple C40s operating in parallel could be used. Parallel processors can be added until the pipe line delays approach the delay of the loop filter.

### **Signal Acquisition Control**

For low data rate systems acquisition of the signal can be a problem. Low data rate systems have small loop bandwidths in comparison with the system's frequency uncertainty. As a result some scheme to acquire the signal must be implemented. One method is to sweep the CRL over the entire frequency uncertainty band and allow the CRL loop to lock when it finds the signal. This method can lead to false locks. A better method is to search for the maximum signal power over the band and pretune the CRL to that spot and then allow the CRL to lock. The maximum power can be found by tuning the LO over the sweep band and using an absolute value detector after the matched filter. Maximum power can also be found by using an FFT. A combination of the two techniques for findina maximum power is being implemented in UNISYs's demodulator.

Another important part of acquisition is knowing whether or not the CRL is locked or not. The lock detect indication used for the BPSK demodulator is FILTER(ABS(I)-ABS(Q)). This gives a good lock indication down to Eb/No of 0 dB.

#### **BIT Synchronizer**

The bit synchronizer is implemented using a conventional early late type phase detector. An IIR filter is used for the loop filter and the error signal generated is sent to the Sampling Clock located near the A/D converters. This loop determines where the samples are taken during the bit period which allows for best performance.

#### **Receiver Filter Design**

The transmitter filter is a combination of finiteintegration filter and the filter that creates cosine transitions. The finite integration filter impulse response is:

$$h_1(t) = \begin{cases} 1, \ 0 \le t < T \\ 0, \ otherwise. \end{cases}$$

The transition shaping filter impulse response is:

$$h_2(t) = \begin{cases} \frac{\pi}{2T} \sin\left(\pi \frac{t}{T}\right), \ 0 \le t \le T\\ 0, \ otherwise. \end{cases}$$

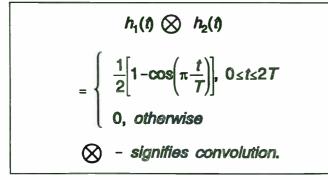

The composite transmitter filter is the convolution of  $h_1(t)$  with  $h_2(t)$ . The effective transmitter filter impulse response is:

The matched filter is, by definition, a time

reversed and delayed version of the composite transmitter filter. Because the effective transmitter filter's impulse response is a real and even function, the matched filter is the same as the effective transmitter filter.

By convolving the matched filter with the

$$h_3(i) = [h_1(-i) \bigotimes h_2(-i)]^*$$

$$= h_1(i) \bigotimes h_2(i)$$

\*- signifies complex conjugate

transmitter filter, one can determine if any intersymbol interference (ISI) has been introduced.

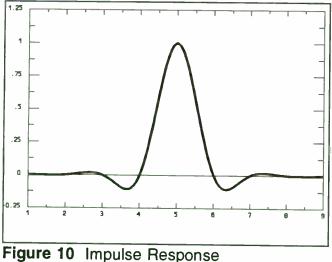

Figure 6 Impulse Response of Transmitter and Matched Filter

The calculated weights show that the matched filter will indeed introduce ISI. The weights

$$h_{1}(t) \bigotimes h_{2}(t) \bigotimes h_{3}(t) =$$

$$\left\{\begin{array}{l} \frac{t}{4} + \frac{t}{8} \cos\left(\pi \frac{t}{T}\right) - \frac{3T}{8\pi} \sin\left(\pi \frac{t}{T}\right), \\ for \ 0 \le t \le 2T, \\ T - \frac{t}{4} - \frac{t}{8} \cos\left(\pi \frac{t}{T}\right) + \frac{T}{2} \cos\left(\pi \frac{t}{T}\right) \\ + \frac{T}{8\pi} \sin\left(\pi \frac{t}{T}\right) + \frac{T}{4\pi} \sin\left[\pi \frac{(t-2T)}{T}\right], \\ for \quad 2T < t \le 4T, \\ 0, \ otherwise. \end{array}\right\}$$

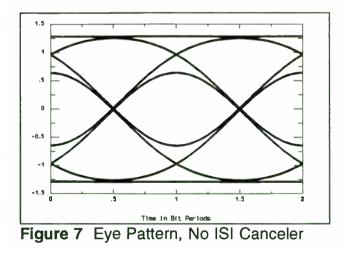

correspond to the impulse response of the transmitter and matched filters at plus and minus one bit period on either side of the impulse delay of 2 bit periods (see figure 6). At time T and 3T the amplitude of the impulse response is T/8; at time 2T the amplitude is 3T/4. Figure 7 shows the resulting eye pattern with ISI.

Obviously, the ISI would have a severe impact on bit error rate. Therefore, an ISI canceling transversal filter is necessary and would need to have the following impulse response:

$$h_{4}(t) = \frac{4}{3T} \begin{bmatrix} -\frac{T}{8}\delta(t) + \frac{3T}{4}\delta(t-T) \\ -\frac{T}{8}\delta(t-2T) \end{bmatrix}$$

$$= -\frac{1}{6}\delta(t) + \delta(t-T) - \frac{1}{6}\delta(t-2T)$$

Since  $h_4(t)$  is comprised of delta functions, convolutions involving  $h_4(t)$  are easily calculated:

$$h_{4}(t) \bigotimes f(t) = -\frac{1}{6} \int_{-\infty}^{\infty} \delta(\tau) f(t-\tau) d\tau + \int_{-\infty}^{\infty} \delta(\tau-T) f(t-\tau) d\tau - \frac{1}{6} \int_{-\infty}^{\infty} \delta(\tau-2T) f(t-\tau) d\tau = -\frac{1}{6} f(t) + f(t-T) - \frac{1}{6} f(t-2T)$$

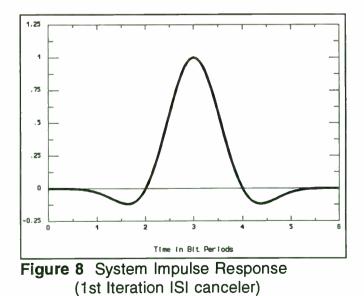

The resulting system impulse response when the ISI canceling filter,  $h_4(t)$ , is combined with the matched filter,  $h_3(t)$ , is shown in Figure 8.

There still appears to be ISI. This is verified

World Radio History

by looking at the resulting eye-pattern, figure 9.

Figure 9 Eye Pattern (1st Iteration ISI Canceler)

Figure 11 Eye Pattern (Modified ISI Canceler)

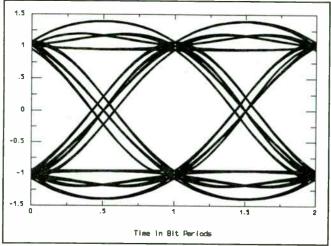

A modified ISI canceling filter is determined by subtracting by the correlation at 2 bit period offsets (see figure 8). The modified system impulse response is shown in figure 10:

(Modified ISI Canceler)

The correlation at bit period increments from the peak is now zero! The eye-pattern should have no ISI as shown in figure 11!

And, indeed, no ISI. The only question now to be answered is what kind degradation from ideal is the bit error rate when this system is used. Since the actual filters were implemented with digital FIR algorithms, the number of taps required and tap spacing needs to be determined. First the receiver impulse response is determined.

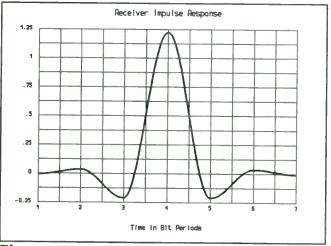

Figure 12 Receiver Impulse Response

It is advantageous to use the minimum number of taps as possible in the FIR filter. The greater the number of taps, the longer the processing time required, and the lower the data rate allowable. We analyzed a variety of spacing possibilities and ended with a sampling rate of 4 times our highest data rate. This was convenient because it allowed us to implement an early/late gate bit synchronizer with 1/2 symbol spacing. Also, by comparing the equivalent noise variance of an ideal finite integration filter (matched filter for nonbandlimited NRZ data) with our receiver filter, we analytically determined the implementation loss to be 0.25 dB from ideal! It later was verified through simulation.

## **Designing a High Performance Monolithic PSK Modulator**

#### Frank Hayden and Robert J. Zavrel GEC Plessey Semiconductors 1500 Green Hills Road Scotts Valley, CA 95066

The objective of this program was to build a low power, monolithic, high performance PSK modulator. There are a wide variety of applications for such a device. The primary objectives was to fabricate a direct sequence "spreader" that could operate up to 1 GHz and provide excellent carrier suppression and combine the spreading PRN code with the data for both CDMA cellular and Part 15 applications. A second objective was to provide a high performance PSK modulator for more traditional applications, including TDMA and point-to-point microwave systems. A third objective was to facilitate derivative products that can provide QPSK, OQPSK and MSK baseband signals.

The "SL801" has been fabricated and tested. Proceeding into a true product development depends upon market acceptance of the device. Therefore, this paper represents a report on a development project and should not be considered a "product" introduction.

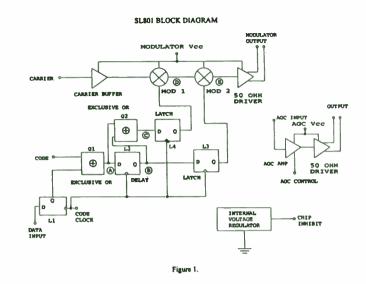

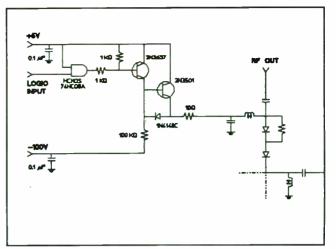

#### 1. Digital Section

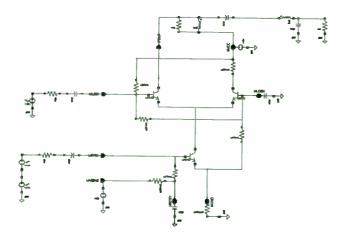

The SL801 is a Bi-Phase shift keyed (BPSK) modulator. The device accepts data in a digital format along with a spreading code that is used to modulate an RF carrier for transmission in spread spectrum systems. A primary performance goal was to maximize carrier suppression. The chosen circuit topology reflects this primary design objective in that two modulators are cascaded thus the carrier supression characteristics are greatly enhanced.

Referring to the block diagram of figure 1, asynchronous data is fed into a type D flip flop at the data input. This serves to synchronize the data to the code clock. Note that the code clock is clocking all the flip flops and latches. After clock synchronization of the data, code inversion modulation is performed by modulo-2 addition of the code and the synchronized data. This takes place in exclusive OR gate G1. This serves to embed the code and data and also adds a greater level of security to the transmitted information. All the user must remember to do in the receiver is to modulo-2 add the received baseband information with the same spreading code in the receiver. This approach ensures that good auto correlation and low cross correlation are preserved.

Referring to the block diagram, Figure 1 , at point A we have

(1)  $A = C \oplus D$

Where:

A is the output of exclusive OR gate G1. C is the Spreading Code. D is the synchronized data.

At point A the output of G1 is fed into another D type flip flop that serves to delay the code and data by one full code clock cycle. The output of the flip flop at point B may be expressed as;

(2)  $B = (C \oplus D)\tau$

Where:

B is the output of the delay flip flop L2. au is the clock delay through L2.

At this point in the circuit, point B is exclusive OR'ed with point A giving output C which can be expressed as;

(3)  $C = (C \oplus D) \oplus (C \oplus D)\tau$ Where:

C is the output of exclusive OR gate G2.

In order to assure proper cancellation of the undesirable terms and thus maximizing carrier suppression, the modulation inputs to the two multipliers must be correctly phased. Latches L3 and L4 assure that the modulation input signals are fed simultaneously to MOD2 and MOD1 respectively.

#### 2. Modulator Section

The carrier input to MOD 1 and MOD 2 require a differential drive. The unbalanced input is converted to the required differential input by the carrier buffer, a unity-gain amplifier-balun with a maximum allowable input signal level of -5 dBm. The balanced modulators (MOD 1 and MOD 2) are Gilbert Cell multipliers configured such that the operation of the circuit provides balanced bi-phase modulation. Each modulator has 0 dB gain to minimize the effect of offsets that could corrupt the balance of the modulator and hence compromise carrier suppression. The modulators are cascaded so that the carrier suppression of each modulator will add to effectively double the carrier suppression (dB).

The instantaneous phase of the RF carrier is determined by the instantaneous polarity of the modulating signal. Consequently, two phase states, 0 or  $\pi$  radians (BPSK) are permitted. In this respect the

balanced BPSK modulator serves as an analog exclusive OR gate. The output of the balanced modulator can be expressed as follows;

(4)

$$V_{out} = \omega_c \oplus V_{data}$$

Where:  $V_{out}$  is the output voltage of the modulator.  $\omega_c$  is the RF carrier signal to be modulated.  $V_{data}$  is the modulating data signal.

To facilitate maximum carrier supression, unity gain in the modulator path is used. Unity gain eliminates amplification of the offset voltages. Offset in the modulators leads directly to a decrease in the carrier suppression in the modulator.

The carrier buffer is simply a differential amplifier that takes a single ended input and gives a differential output. The inputs are biased at approximately 3 volts and the input impedance is approximately 10 k ohms and 2 pF. If a 50 ohm source is to be used to drive the SL801, simply terminate the input with 50 ohms and capacitivly couple the signal to the input. The other differential input is AC grounded through 50 ohms in series with 10 pF. The 10 pF capacitor is connected to a pin on the package that allows the low frequency response of the input to be extended by adding a capacitor from this pin to ground. Emitter degeneration is used in the amplifier to extend the linear signal handling ability of the amplifier up to a maximum of -5 dBm.

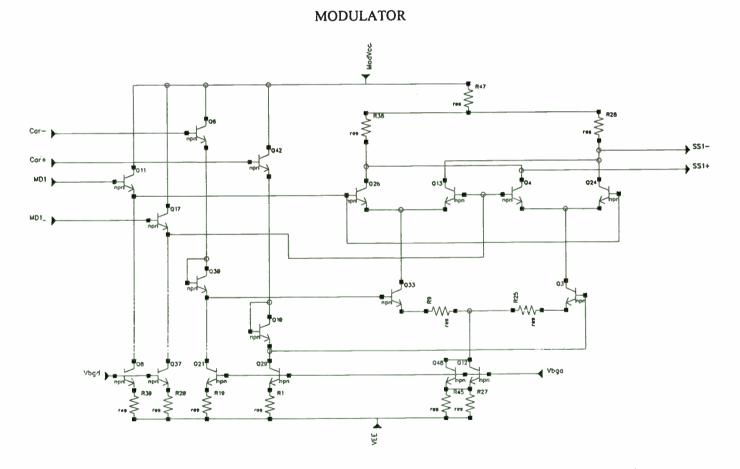

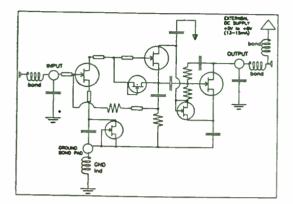

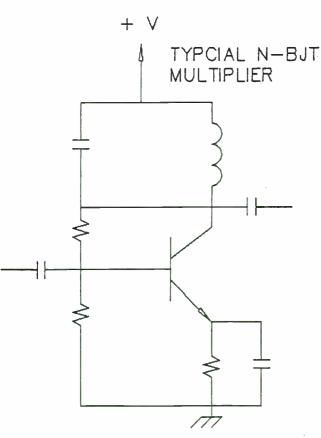

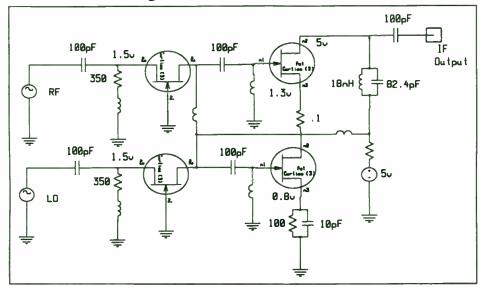

The Gilbert cell modulator schematic is shown in Figure 2. The schematic shows the basic Gilbert cell and the level shifters at the modulating inputs and the carrier inputs. this level shifting ensures that the transistors in the cell do not saturate, which could degrade carrier suppression.

The lower two transistor pairs Q33 and Q3 are the RF input and the four upper transistors Q26, Q13 and Q4, Q24 are the modulating or phase reversing transistors. Emitter degeneration is used in the lower pair of transistors to extend the linear signal handling capability of the RF input. The upper four transistors in the cell have no degeneration as this would degrade the gain of the modulator.

As the upper pairs of transistors are switched the RF carrier is steered to the modulator output depending on which set of transistors in the top of the cell are biased on. For instance if Q 26 and 24 are on, then RF is passed to the output through the cascoded pair made up of Q33 and Q26 and Q3 and Q24. As Q13 and Q4 are turned on by the modulating wave form the cascode arrangement switches over to Q33 and Q13 and also Q3 and Q4. So as the modulating wave form changes state the phase of the carrier is changed 180 degrees. The gain of the modulator circuit can be approximated by the following equation;

(5)

$$G_v = \frac{RI}{(R_e + r_e)}$$

Where;

$G_{\rm r}$  is the voltage gain of the circuit.

*RI* is the collector load resistance. (R38 or R28 in the schematic)

r, is the intrinsic emitter resistance of the transistor

where

$$r_e = \frac{IC}{V_t}$$

.

Since the modulator path has 0 dB of gain , both of the modulators are identical. Now returning to the block diagram in Figure 1, the output of the first modulator can be expressed as follows with appropriately substituting (3) into (4);

(6)

$$D = \omega_c \oplus [(C \oplus D) \oplus (C \oplus D)\tau]$$

where  $\omega_c$  is the RF carrier signal, and

(7)

$$E = \omega_c \oplus [(C \oplus D) \oplus (C \oplus D)\tau] \oplus [(C \oplus D)\tau]$$

Now using the following Boolean identity;

$$(8) \quad A \oplus B \oplus B = A$$

(9)

$$E = (D, \oplus (C \oplus D))$$

which is the desired result for the output of MOD 2.

So by using the delay component, two modulators may be cascaded together to achieve approximately twice the carrier suppression that can be achieved with one modulator. It should also be noted that the output from the first modulator is indeed a spread spectrum signal. However, there is no way that the receiver can demodulate the information that is in this signal unless the appropriate delay is generated in the receiver.

It is also worth noting that the choice of the delay component is quite critical to the success of the cascaded arrangement of modulators. It is important that the two modulating signals be as closely decorrellated as possible. Therefore, the minimum clock delay for correct operation is one, and the larger the delay, the more decorrellated the two signals become, but at the expense of added circuitry. It was felt that the minimum delay period would yield a satisfactory result.

#### 3. Driver Section

After modulating the RF carrier, the output of the modulators is driven into a differential output 50 ohm driver. The output of this differential driver can be configured in several ways. Since the output is an .

open collector circuit, a 50 ohm resistor connected to each output and up to the supply rail will properly set the gain of the driver and allow the circuit to drive up to -5 dBm into any 50 ohm load. The output signal can also be driven into a balun and an additional 6 dB of drive obtained, less any balun losses.

The 50 ohm driver circuits are open collector differential amplifiers. A bias resistor of 50 ohms must be connected to the open collector outputs up to the 5 volt supply line. These loads can then be AC coupled to the next circuit in a single ended fashion, coupling one of the outputs to the next stage and also AC coupling the unwanted output to a 50 ohm load. This terminates the collectors with the correct differential impedance. Either output can supply -5 dBm, or if a RF balun is used correctly, the output power would increase to +1 dBm.

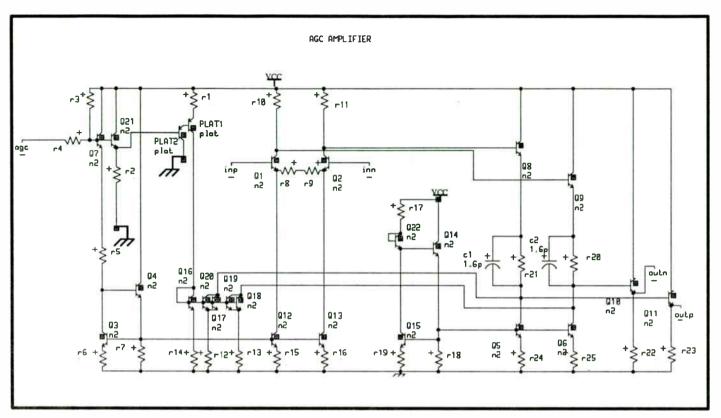

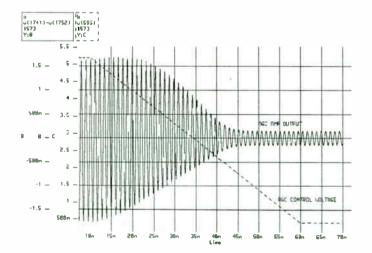

#### 4. AGC Amplifier

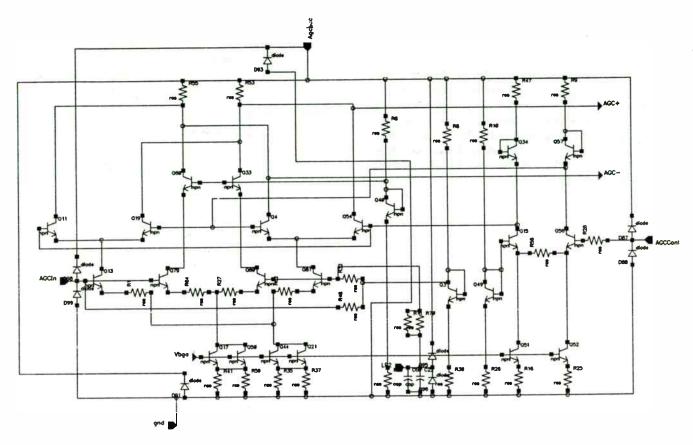

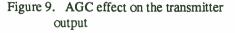

The modulated signal is filtered externally before entering the input to the AGC amplifier. Alternatively, further processing and/or phasing with other Sl801s can yield QPSK signals. The AGC amplifier has 5 dB of gain and 30 dB of AGC control range.

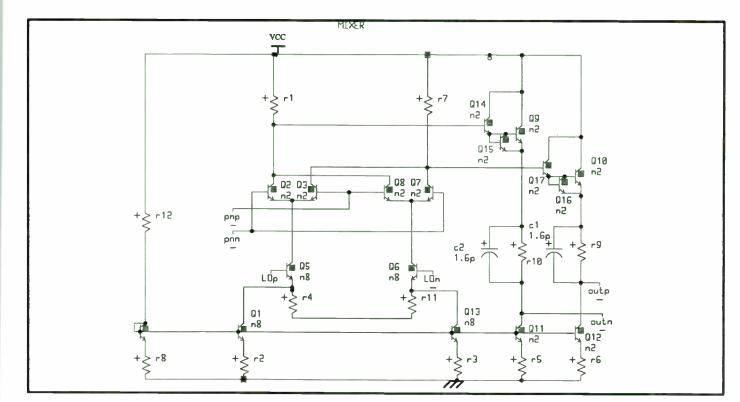

The AGC amplifier is also a Gilbert cell type circuit. Referring to the schematic of the amplifier in figure 3, the main portion of the amplifier is made up of transistors Q13,Q81,Q11,Q19,Q4 and Q54. In parallel with this Gilbert cell is another amplifier made up of transistors Q79,Q80,Q60 and Q33. This amplifier in parallel with the Gilbert cell serves to keep the DC point at the load resistors R55 and R53 constant as the gain control is varied by diverting current away from the collectors of Q11,Q19,Q4 and Q5.

The gain of the AGC amplifier is controlled via the differential amplifier comprised of transistors Q15 Q56. as the voltage at the AGC control input is increased above the DC bias point at the base of Q15, Q56 turns on and the current through the diode load Q57 supplies the bases of Q19 and Q4. The diode current compensates for the nonlinear control characteristic and provides a linear control characteristic over the voltage range of 2.5 to 3.5 volts.

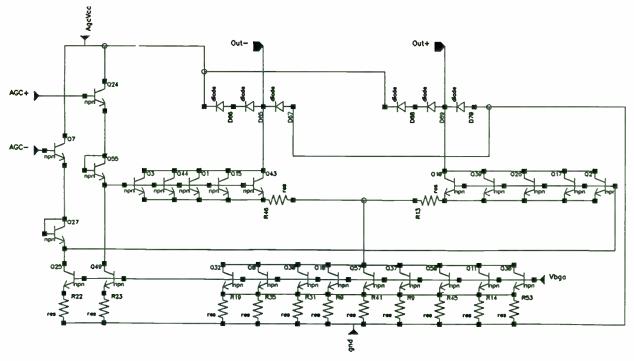

#### 5. Output Amplifier

The output of the AGC amplifier is fed into a differential amplifier capable of driving 0 dBm into a 50 ohm load. This differential amplifier has 0 dB gain and is similar to the 50 ohm driver at the output of the modulator section. The outputs of the amplifier are pulled up to the supply via 50 ohm resistors and capacitvely coupled to the load. If a differential drive is not desired the unused output should be capacitivly coupled to a 50 ohm load.

This 50 ohm driver is similar to the 50 ohm driver that is at the output of the modulators, only capable of supplying 0 dBm to the load in a single ended application or again if an RF balun is used it is capable of delivering +3 dBm.

#### 6. Design Considerations

On the chip are separate voltage regulators and grounds for the digital and analog functions. The chip can be put in a standby mode by supplying a TTL compatible signal that is active high.

In the digital section of the device all TTL/CMOS input levels are level translated down to a peak swing of 150 mV on chip. This is done to avoid large signal swings at the modulating inputs of the Gilbert cell and also helps with cross talk on chip.

Separate bandgap regulators for the digital and analog functions on the chip are used to set the bias point for the current sources. This was done to reduce the cross talk among the various digital and analog circuits.

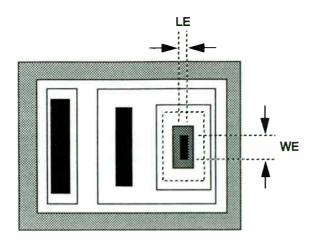

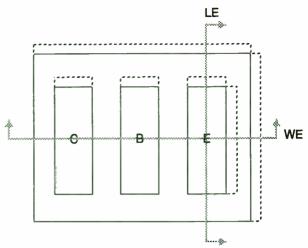

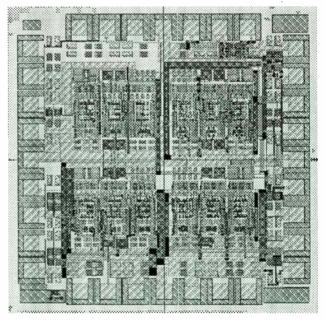

In the layout of the I.C., great care was taken to match all of the transistors and metal runs in both the digital and analog sections. In the modulator section of the device all metal traces were matched to within 1 milliohm to avoid DC offsets. The carrier buffer, two modulators and the first 50 ohm driver are also surrounded with trench isolated substrate contacts to further avoid cross talk from the digital section. Both the AGC amplifier and the AGC 50 ohm driver are also surrounded with trench isolated substrate contacts to ensure that the carrier does not leak into these circuits degrading the carrier suppression after the modulator section.

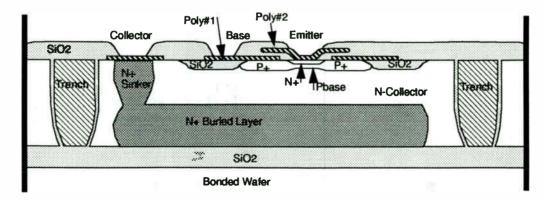

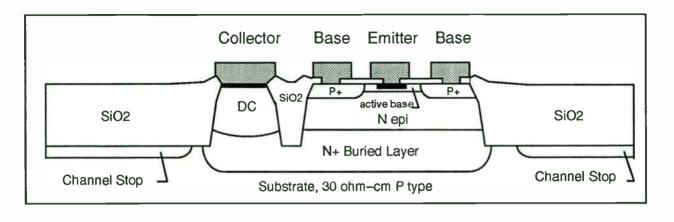

#### 7. The HE Process

Process HE is a bipolar process incorporating polysilicon base/emitter contacts, trench isolation and an advanced base/emitter structure. The process has been characterized as having a peak Ft of 14 Ghz. There are three layers of metalization available on the process.

The NPN devices are available in four different emitter lengths of 2, 5, 10 and 15 microns. There are also PNP devices available. Internitride capacitors can also be fabricated on the process with realizable values of up to 5 pF for a single capacitor. Inductors can be fabricated on the third metal layer with Q's measured at 10. There are also two different types of resistors, both of which are polysilicon. Low value resistors can be realized using 200 ohms per square polysilicon and high value resistors can be made by putting a barrier around the 200 ohms per square polysilicon increasing the sheet resistivity to 2000 ohms per square. Another feature of process HE is the ability to open selective substrate contacts around different portions of the circuitry and then surrounding these substrate contacts with walled trench isolation. This then serves to isolate portions of the circuit from other functions on the chip, thereby increasing the amount of isolation between different circuit functions.

#### 8. Conclusions and Further Work

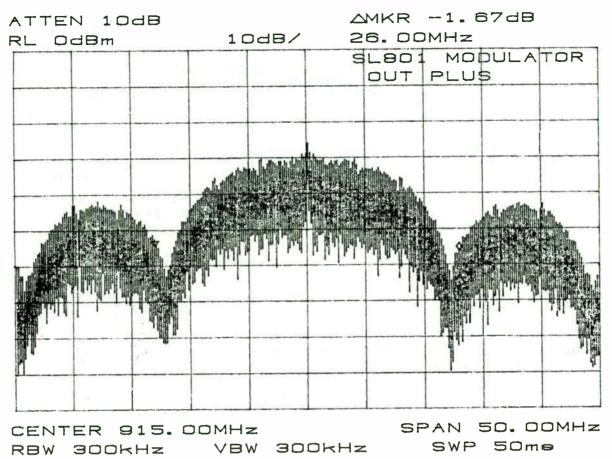

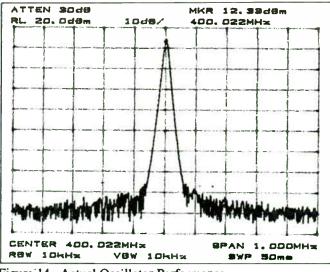

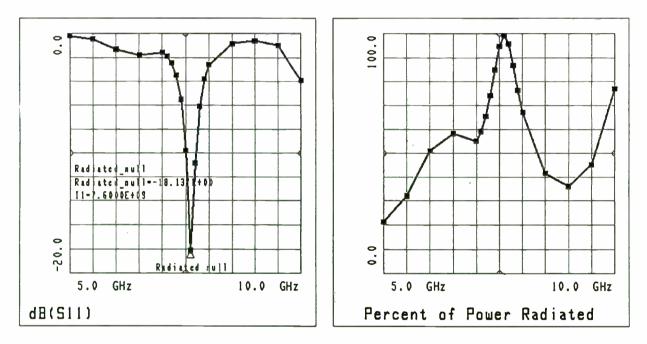

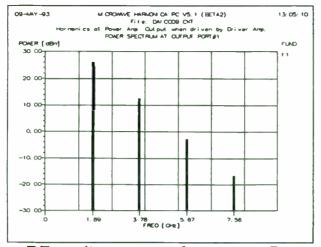

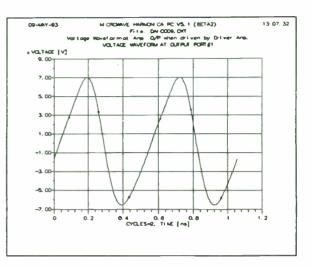

The objectives of designing a high performance, low power, and convenient PSK modulator have been met. Figure 5 shows a typical output spectrum of the device.

Two SL801 circuits can be combined to produce QPSK or OQPSK signals. Furthermore, MSK can be generated with two SL801s operating in quadrature. MSK is the most likely baseband of choice for frequency hopping spread spectrum systems operating under Part 15. These applications are certainly possible using the currect SL801 and/or derivative circuit configurations.

Figure 2.

50 Ohm DRIVER

Figure 4.

World Radio History

#### TYPICAL OUTPUT SPECTRUM

Figure 5.

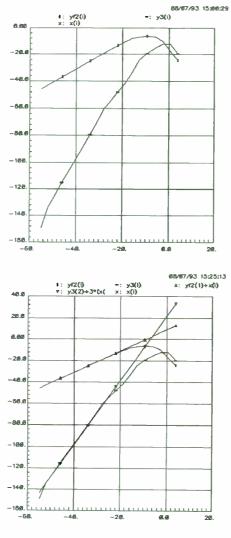

### Methods for Estimating and Simulating the Third Order Intercept Point

Carl Stuebing and Mojy C. Chian

Harris GCSD and Harris Semiconductor Melbourne, FL 32901

Abstract - The third order intercept point  $(P_{ip3})$  is a metric to quantify the nonlinearity of a circuit.  $P_{ip3}$  is used to describe the adjacent frequency isolation and gain distortion. This paper describes the concept of  $P_{ip3}$  and reviews methods to estimate and simulate it. The common simulation pitfalls are identified and practical solutions are discussed and illustrated.

#### I. Introduction

The nonlinearity of a radio amplifier determines it's distortion. As the input signal level increases, distortion of the output signal becomes prominent and undesired harmonic products are produced.

Consider two FM carriers at 50MHz and 100MHz applied to the input of a radio amplifier. Assume that there is little filtering of the input signal and that we are interested in amplifying the 100MHz signal. However, the 50MHz signal is so strong that it drives the amplifier into distortion. In this situation, the second (2X50MHz) harmonic of the 50MHz signal would interfere with the 100MHz signal at the output of the amplifier.

Obviously, radio receivers generally do have selective filters on their signal inputs. So interference of signals is, as a practical matter, more important for signals which are close together in frequency (i.e. in band).

Nonlinearity can also cause less obvious interference problems with signals that are close together in frequency. When two in band signals are applied to a nonlinear circuit element, they will mix. This process is called intermodulation and the resultant frequency components are referred to as intermodulation products. It can be shown that the frequencies of the intermodulation products are defined by  $k_1f_1 \pm k_2f_2$ , where  $k_1$  and  $k_2$  are integers. The component with a frequency equal to  $n_1f_1 \pm n_2f_2$  is defined as the *n*th order intermodulation product, where  $n = n_1 + n_2$  [1,2].

While the two fundamental signals will typically be magnified by the amplifier, components at the sum and difference frequencies are also produced at the output. These second order intermodulation products are not usually considered to be important, because they are typically far enough out of band from the fundamentals that they can be easily suppressed with filters.

More important are the third order intermodulation products. These occur at frequencies given by the two times one frequency minus the other, and vice versa. While these parasitic signals may be smaller in amplitude than the second order products, they are more difficult to filter out. Consider two FM signals at 100 and 101 MHz. The third order parasitic tones are produced at 202-100=102MHz and 200-101=99MHz. When the signal distortion is large, these products become significant since they are produced well within the band of the input frequencies.

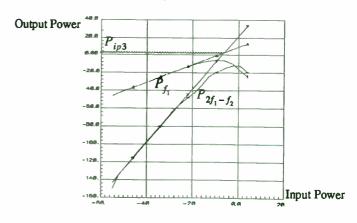

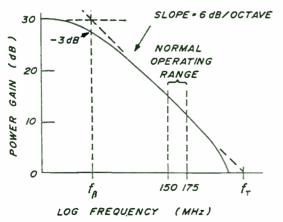

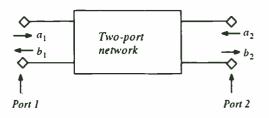

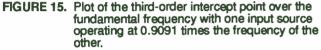

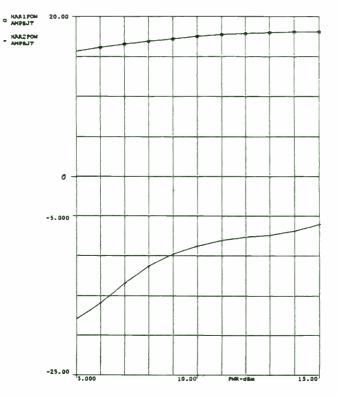

A popular metric to quantify distortion is the Third Order Intercept Point, or " $P_{ip3}$ ". For a two-port network excited with two sinusoidal signals with frequencies  $f_1$  and  $f_2$ , if the third-order intermodulation product output power ( $P_{2f_1-f_2}$ ) and the output power at  $f_1$  ( $P_{f_1}$ ) are plotted versus the input power at  $f_1$ , the third-order intercept point ( $P_{ip3}$ ) is defined as the point where  $P_{f_1}$  and  $P_{2f_1-f_2}$  intercept. The third-order intercept point is a theoretical level, however, it is a useful and popular quantity to estimate the third-order intermodulation products at different power levels (Figure 1).

The power gain of the fundamental frequencies is linear and remains constant until we have a large enough input signal that clipping or gain compression occurs. However, the voltage gain of the third order products is raised to a cubed power instead of linear (as in the case of the fundamental). This means that the power gain of the third order harmonics is three times higher than that of the linear fundamental. Of course, the power level of the third order product is normally less than that of the fundamental. As the input power level increases, the ratio of the fundamental power output to the third order product output power level decreases rapidly.

The output  $P_{ip3}$  ( $P_{ip3o}$ ) is defined as the point where the asymptotes of the fundamental linear power gain curve and the third order product power gain curve intersect. We can use simple trigonometry to relate this output power level to the fundamental and third order frequency gain curves. Knowing  $P_{ip3o}$ , the input power level, and the power gain, we can extrapolate the power level of the third order intermodulation products. If G is the power gain, then

$$P_{ip3o} = P_{ip3i} + G$$

When  $P_{ip3}$  is large, the power level of the third order products is suppressed, or distortion is reduced. Obviously, this is desirable. When  $P_{ip3}$  is small, the third order product power is relatively large, or distortion is increased.

While the "real world" does not consist of only two interfering radio channels, this is a convenient technique. Here we allow ourselves to define a metric for quantifying the distortion and thus the interference of radio signals.

#### II. Review of Some Traditional Estimation Techniques

Several "rules of thumb" exist within the RF industry for estimating  $P_{ip3}$ . Since accurate simulation of  $P_{ip3}$  can be very computer time intensive, one should attempt first to estimate this parameter.  $P_{ip3}$  is in some ways more dependent on system level considerations (such as the input termination method and available power supply voltage and current) than device design considerations (such as the geometry selected for the RF transistor). Generally, once the system determines  $P_{ip3}$  (which should be quickly albeit roughly estimated), computer simulation can be used to measure the somewhat subtle effects of transistor or integrated circuit level design on  $P_{ip3}$ .

#### Rule #1

The first (system level) rule of thumb is that  $P_{ip3}$  is about 6 to 10dB higher than the 1dB gain compression power level. The 1dB gain compression level refers to the signal level at which the gain at the frequency of interest has decreased due to clipping by 1dB or 12%.

There are no known elegant mathematical discussions to prove this rule. We simply have an empirical number which has been known to be a useful approximation. This is not an extremely accurate rule, but coupled with a one tone simulation is much faster than two or three tone simulations.

#### Rule #2

The second rule of thumb relates output power available to output intercept point. As an approximation, use the maximum (RMS) power available to the load as the 1dB compression point for output power.

This rule implies that the amplifier is piecewise linear. Thus, gain is approximated to always be equal to the (very) small signal level until the available output power level has been reached. Once the peak output power has been exceeded, the signal is suddenly clipped and incremental gain becomes zero at the maximum or minimum voltages of the output. The point at which this process starts is used to identify the approximate one dB compression point.

Real amplifiers typically demonstrate increasing compression with amplitude. Thus, 12% gain compression normally occurs below the maximum available output power level. Therefore, this rule of thumb is very rough and optimistic.

#### Extension #1

Some interesting results can be obtained from carrying the above assumption further. Assuming that voltage saturation of devices is not permitted, the available output power for a single collector load resistor in a common emitter amplifier is given by:

$$P_{out1dB} = \frac{I_{nom}^2 R_1}{2}$$

Where  $I_{nom}$  is the nominal DC bias current in the collector of the transistor. This is assumed to be the available zero-to-peak output current. Of course, this equation neglects the lost power output (i.e. gain) at higher frequencies due to capacitive loading.

Rule #2 can now allow us to take this available output power and use it for 1dB gain compression estimates. First, we rewrite the above equation in dBm:

$$P_{out1dB} = 10\log(500I_{nom}^2 R_l)$$

Now, we apply Rule #1 to estimate Output Intercept:

$$P_{ip3o} = 10\log(500I_{nom}^2R_l) + 6dB$$

#### Extension #2

A popular method for obtaining Input Intercept is to find the difference between  $P_{ip3o}$  and power gain. However, a shortcut can simplify the calculation of  $P_{ip3o}$ . Power gain depends on input impedance, output impedance, and current gain (i.e.  $\beta$ ). This information can also be used to determine the available output power and input power levels that are associated with the estimated 1dB compressed output power. No explicit gain estimate is really necessary. This method, generally, works best at frequencies much less than the  $f_T$  of the transistor.

Thus at the 1dB compression point, output signal power can be related to input signal power. The RMS input signal power is given by:

$$P_{in} = \frac{I_b^2 R_{in}}{2}$$

where  $I_b$  is the nominal base bias current associated with  $I_{nom}$ . We observe that the input current "just below compression" (given our simplified, piecewise linear model) is simply specified by  $I_{nom}$  divided by  $\beta$  (which is a function of frequency). The input resistance is given by  $r_n$  and  $R_b$ :

$$P_{in1dB} = \frac{I_{nom}^2(r_n + R_b)}{2\beta^2}$$

Since

$$r_n = \frac{\beta V_i}{I_{nom}}$$

, thus [3]:

$$P_{in1dB} = \frac{R_b I_{nom}^2}{2\beta^2} + I_{nom}^2 \left(\frac{\beta V_t}{2\beta^2 I_{nom}}\right)$$

therefore,

$$P_{in1dB} = \frac{R_b I_{nom}^2}{2\beta^2} + \frac{I_{nom} V}{2\beta}$$

Since we are considering frequencies much lower than the  $f_T$  of the device (where  $\beta$  is large and  $R_b$  should be much less than  $r_{\pi}$ ), the above equation can be approximated by:

$$P_{in1dB} = \frac{I_{nom}V_t}{2\beta}$$

To convert the 1dB output compression level to  $P_{ip3o}$ , apply rule #1, and add 6 to 10 dB.

$$P_{ip3i} = 10\log{(\frac{500I_{nom}V_{t}}{\beta})} + 6dB$$

What is particularly interesting about this result is that  $P_{i_p3i}$  (in Watts, not dBm) is proportional to  $V_i$ ,  $I_{nom}$  (nominal collector current) and  $1/\beta$ . Of all the above terms, the only process related one is  $\beta$ . The rest are dependent on absolute temperature and the available power supply current. So system constraints dominate this situation. Also notice that large  $\beta$  is "bad", because it reduces  $P_{i_p3i}$ . Of course, large  $\beta$  tends to help noise figure.

This rough method is much faster than lengthy computer simulations, and can give us a reasonably good feel for the system level trade offs affecting Pipi3.

# III. Simulation tools and techniques for Computing $P_{in3}$

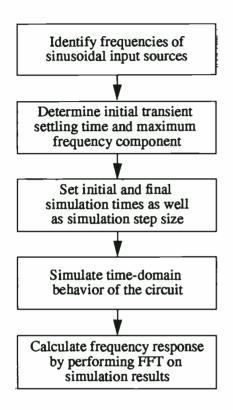

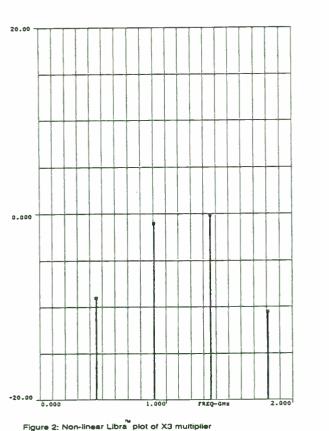

The traditional method for calculating  $P_{ip3}$  by simulation is to use a Harmonic Balance based simulator. Harmonic Balance is a frequency domain method applied to nonlinear circuits, where the computations are performed using the trigonometric-series coefficients. The approach is based on balancing of currents between the linear and nonlinear subcircuits in the frequency domain. Since nonlinear devices are generally expressed in the time domain (e.g. Gummel Poon model for a BJT) their response has to be determined using time domain techniques. First, the input signals to the nonlinear devices are converted to time domain signals (using IFFT). Second, the time domain signals (voltages) are applied to the nonlinear devices and the time domain response (currents) is determined. Third, the time domain currents are converted to the frequency domain (using FFT). Finally, the frequency domain currents of the nonlinear devices are used in a global circuit equation to satisfy KCL at each node. This process is repeated many times until a consistent solution is attained (convergence).

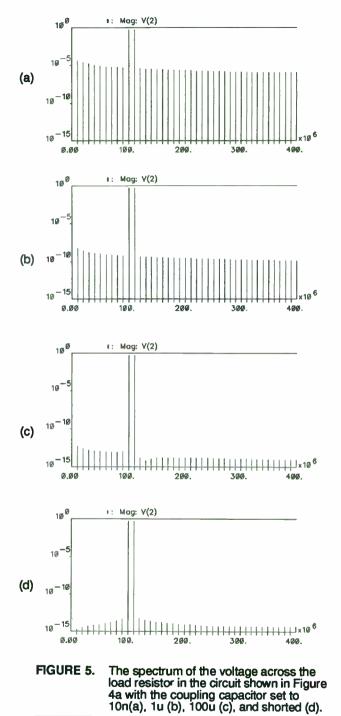

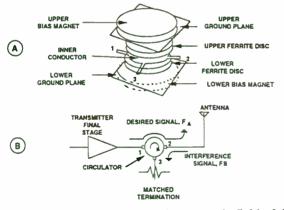

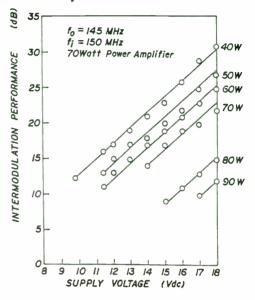

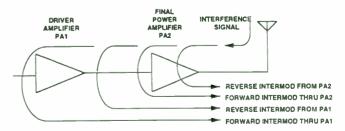

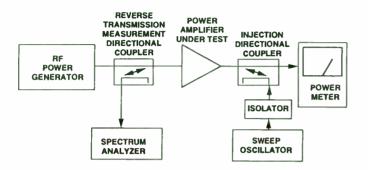

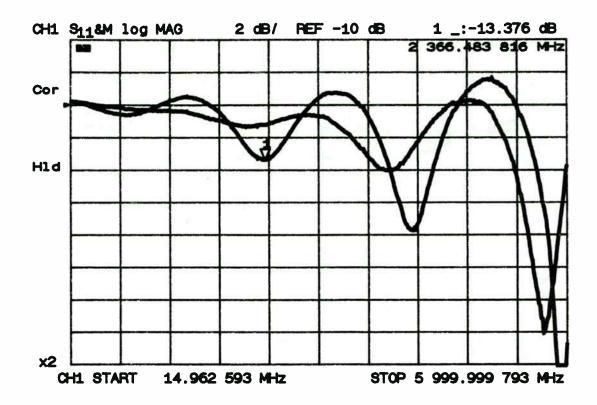

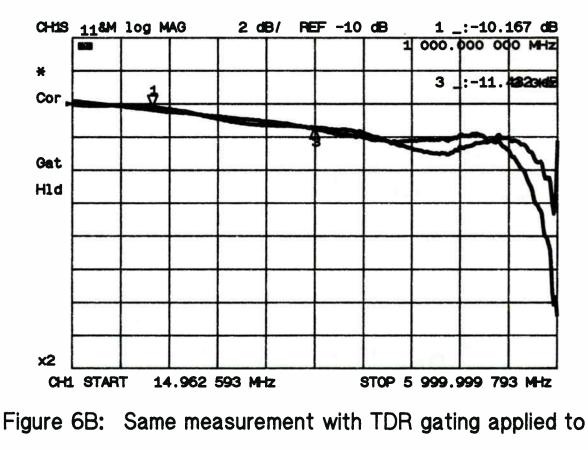

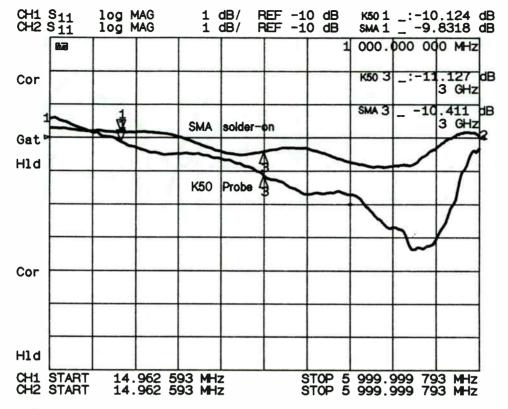

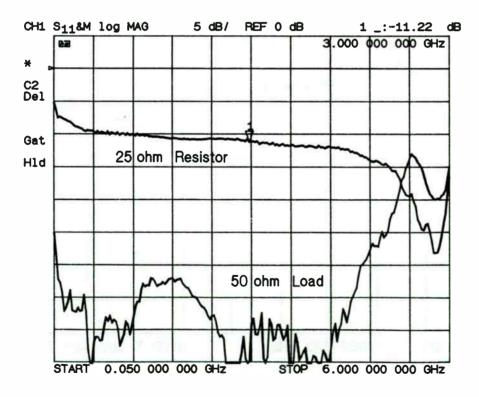

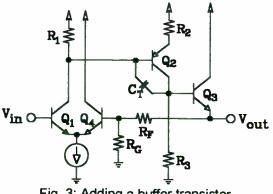

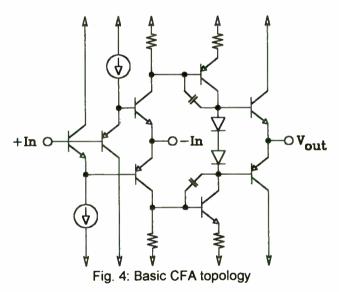

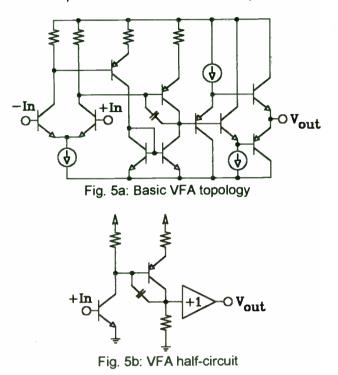

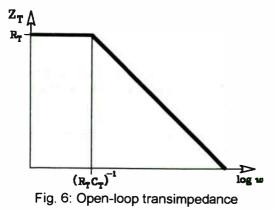

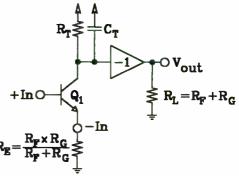

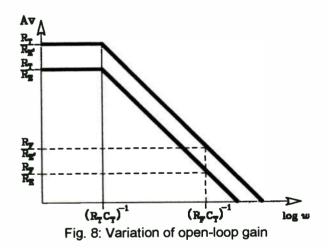

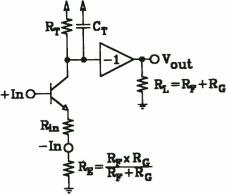

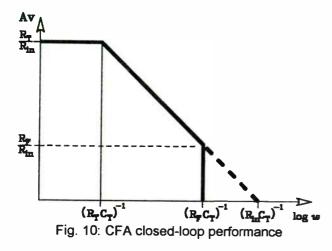

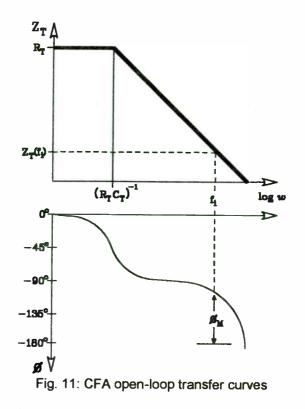

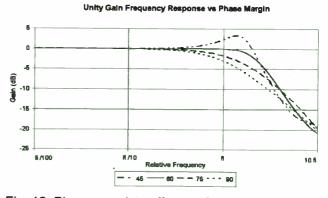

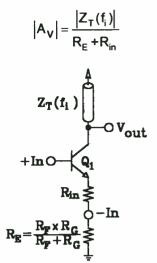

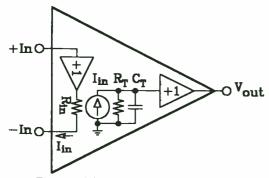

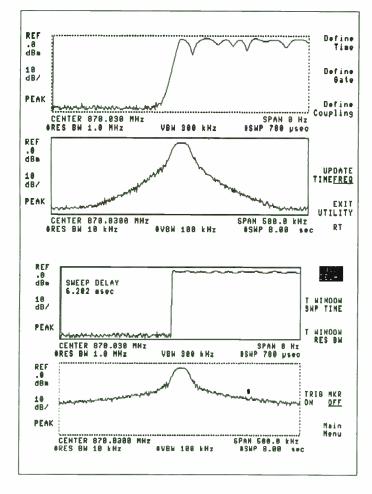

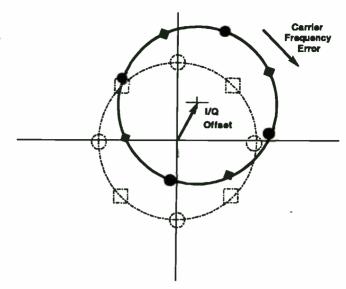

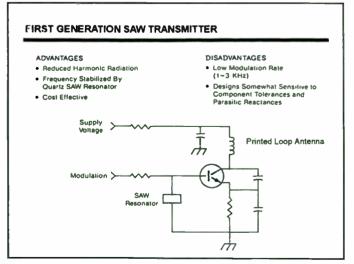

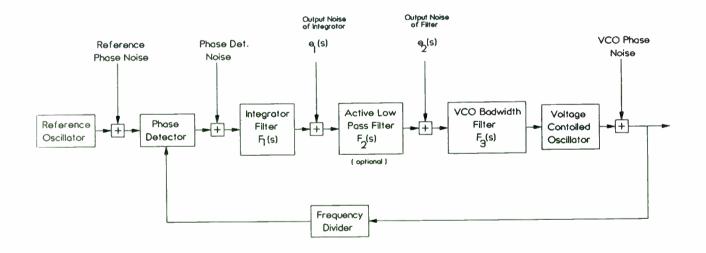

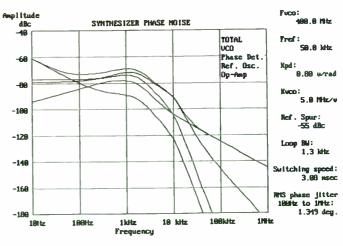

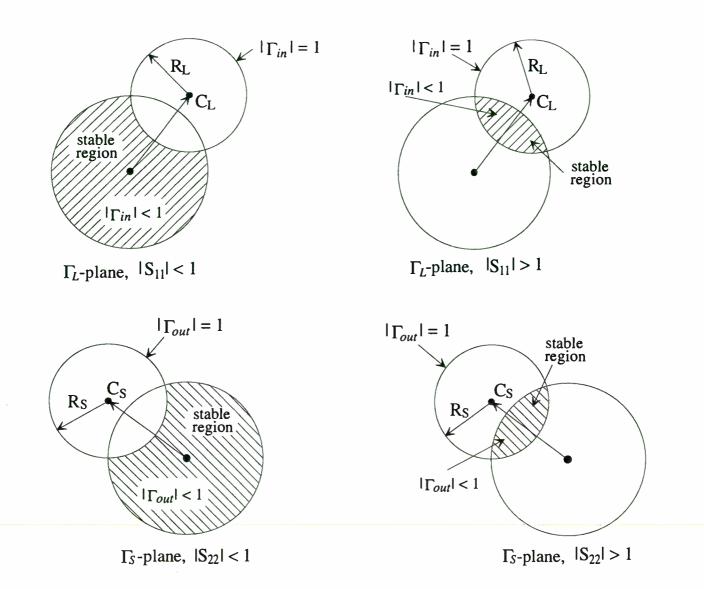

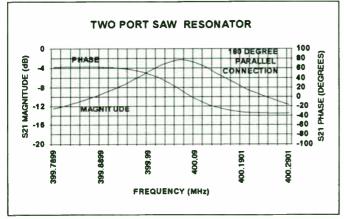

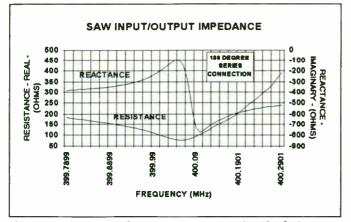

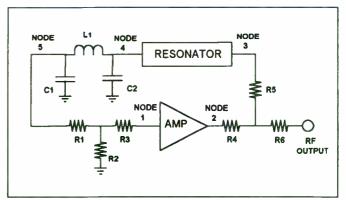

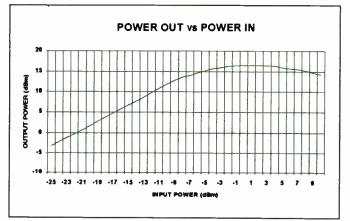

Harmonic Balance determines the steady state response of nonlinear circuits to sinusoidal excitations. Even though the frequency domain response can be converted to the time domain, it does not contain the transient response of the circuit. This feature is a mixed blessing. For circuits with a very long and unwanted transient response (e.g. switching power supplies), harmonic balance is an efficient technique to bypass the transients and obtain the steady state response. For such cases, time domain based analysis algorithms can waste a lot of CPU time analyzing an undesired region of the response. On the other hand, for circuits like LNAs and comparators, it is essential to observe the transient response of the circuit to determine its effect on the frequency domain response. This issue is discussed in more detail in Section IV.