# Radio Shaek

# Understanding Microprocessors

For the newcomer to microprocessors — what they are, what they do, how they work — and how they can be used to solve problems electronically. Written in everyday language. Ideal for self-paced, individualized learning.

Developed for Radio Shack by Texas Instruments Learning Center

•

- Ha Cd

# Understanding Microprocessors

Written By: Don L. Cannon, Ph.D

Assoc. Prof. of Electrical Engineering University of Texas at Arlington Staff Consultant, Texas Instruments Learning Center

Gerald Luecke, MSEE Mgr. Technical Products Development Texas Instruments Learning Center

A DIVISION OF TANDY CORPORATION FT. WORTH, TEXAS 76102 This book was developed by: The Staff of the Texas Instruments Learning Center P. O. Box 225012 MS-54 Dallas, Texas 75265

With Contributions By:

Tim Shirey

Appreciation is expressed to Jim Muller, Steve Howard and Doug Luecke for their valuable comments.

Artwork and Layout By: Schenck, Plunk & Deason

# IMPORTANT:

Texas Instruments makes no warranty, either express or implied, including but not limited to any implied warranties of merchantability and fitness for a particular purpose, regarding these materials and makes such materials available solely on an "as-is" basis.

In no event shall Texas Instruments be liable to anyone for special, collateral, incidental, or consequential damages in connection with or arising out of the purchase or use of these materials and the sole and exclusive liability to Texas Instruments, regardless of the form of action, shall not exceed the purchase price of this book.

Copyright © 1979

Texas Instruments Incorporated, All rights Reserved

Unless otherwise noted, this publication, or parts thereof, may not be reproduced in any form by photographic, electrostatic, mechanical, or any other method, for any use, including information storage and retrieval.

For conditions of use and permission to use materials contained herein for publication in other than the English language, apply to Texas Instruments Incorporated.

For permissions and other rights under this copyright, please write Texas Instruments Learning Center, P.O. Box 225012 MS-54, Dallas, Texas 75265.

# **Table of Contents**

|         | Pretace                                               | , 17        |

|---------|-------------------------------------------------------|-------------|

| Chapter | P                                                     | age         |

| 1       | The World Of Digital Electronics                      | 1-1         |

|         | Quiz                                                  |             |

| 2       | Basic Concepts In Microcomputer Systems               | 2-1         |

|         | Quiz                                                  | -28         |

| 3       | How Digital Integrated Circuits Provide The Functions | 3-1         |

|         | Quiz                                                  | -40         |

| 4       | Fundamentals Of Microcomputer System Operation        | 4-1         |

|         | Exercise and Solution                                 | <b>-5</b> 8 |

| 5       | A System Application With SAM                         | 5-1         |

|         | Quiz                                                  |             |

| 6       | Programming Concepts                                  | 6-1         |

|         | Exercise and Solution                                 | 5,26        |

| 7       | An 8-Bit Microprocessor Application                   | 7-1         |

|         | Exercise and Solution                                 | -28         |

| 8       | A 16-Bit Microprocessor Application                   | 8-1         |

|         | Exercise and Solution                                 |             |

|         | Glossary                                              |             |

|         | Index                                                 | I-1         |

# **Preface**

This book is written for the person that has a curiosity about how microprocessors and microcomputers work: Microprocessors that are being used in appliance and automotive controls, microcomputers that are used in toys and games, microprocessor systems that seem to be able to do so much in such a small space.

With this book some knowledge of how digital electronics work and how they are used is beneficial. However, it is not necessary. Basic concepts and fundamentals are a prime ingredient of the book content to provide the overall understanding desired. An understanding that should serve the reader well whether working directly with or on the fringe of microprocessors, or just wishing to be fully aware of the digital evolution

sweeping over us.

Microprocessors and microcomputers are causing a change in the design of digital electronic equipment. Where prior systems might have consisted of a set of hardware designed especially for a particular job, now common hardware will be used for many different types of jobs. The only thing that changes is the program of operations that causes the hardware to perform its task. Understanding how this can be done – from idea to completed hardware – is a prime purpose of this book.

This book, like the other Understanding Series, builds the understanding of the subject step by step. For this reason, the book should be read a chapter at a time starting at the beginning. Don't skip around to get details on individual subjects but study the chapters until the basic concepts are understood, then move on to a higher level of understanding in the next chapter. The book also encourages the reader, through examples

and exercises, to actually try to use a microprocessor system.

Quizzes and exercises are provided for checks on the understanding

received from each chapter.

A glossary and index help to further expand the understanding of

the subject.

The world of digital electronics is very exciting. We hope this book helps you to understand and enjoy it.

DC

G.L.

# The World of Digital Electronics

We are all surrounded by examples of electronic devices that make our lives simpler and more enjoyable. In the past, these devices were limited to radios, televisions, stereos, tape recorders — so-called analog systems that did not use digital electronics. More recently, electronic calculators have brought the world of digital electronics to our very fingertips. Now there are a variety of games, "smart" appliances, and even computers for the home that are being made available to us through the use of a special type of digital electronic device called a microprocessor.

# **ABOUT THE BOOK**

This is a book about microprocessors, or more specifically, about microcomputer systems which use a microprocessor as the central unit for processing and control. It is a book for the person who is not familiar with digital electronics, integrated circuits, analog systems, computers, microprocessors, microcomputers, software, programs, programming, source code, object code, machine code, assembly language, assembler, highlevel language, compiler, cross-support, etc. It is written to provide understanding of the basic concepts and fundamentals surrounding these terms. It is designed to help provide insight into what makes up a microprocessor, how the microprocessor fits into the microcomputer system, what other system units are required for the microcomputer system, and how one gets a microcomputer system to do something.

This all sounds very difficult and complicated. It's not. But to make the task easier let's make sure we all have the same initial understanding by discussing a few of the basic terms.

# SOME BASIC DEFINITIONS

# Computer

A computer is a system made up of units which are pieces of hardware (electronic circuits, printed-circuit boards, switches, lights, etc.) that perform operations on given inputs to obtain required outputs. These operations are performed by a particular set of steps arranged (programmed) to occur in a particular order.

Computers can be made by using mechanical devices such as gears and levers. Babbage's original analytical steam engine was made this way. Or electromechanical devices such as motors and solenoids can be used for systems such as an aircraft autopilot computer. A system such as the handheld calculator can be made by using only electronic devices. This book is about such electronic devices and how they are used to make computers.

# **Analog vs Digital Systems**

Computers can be analog systems or they can be digital systems.

When a system such as a computer is an analog system the quantities to be computed, transmitted or controlled are represented with physical means that vary in a smooth continuous fashion. The representation is not broken into discrete parts or separated into set levels and the signal is usually carried on one or two wires.

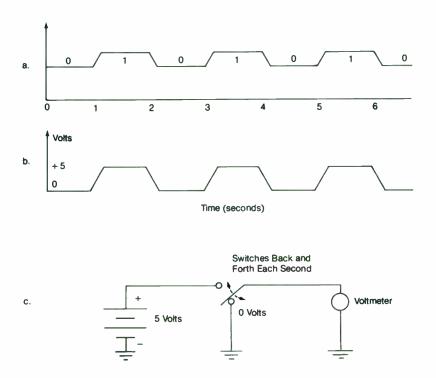

In contrast, digital systems represent a system quantity by breaking it into discrete parts, and usually several wires bundled in a group are needed to carry the signals.

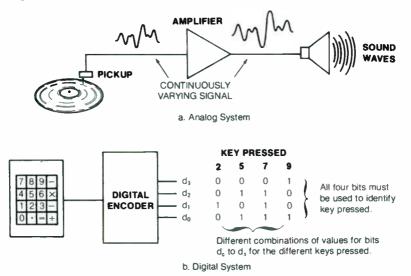

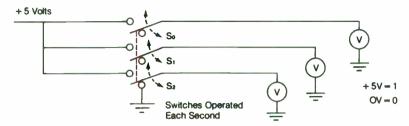

Let's look at Figure 1-1. A system that plays records or cassette tapes is an example of an analog system. Continuous varying signals of audio tones from the record or tape pass through the pickup head into the amplifier and out the speaker. The sound impulses on the record or tape are converted to continuous electrical signals that are amplified and reconverted to sound by the speaker. The electrical signals have provided an "analog" or analogy of the sound signals. The circuits used to handle analog information electronically are usually called linear circuits.

Digital systems on the other hand handle the information in digital form. The system quantities or system information is made up of a combination of separate parts called bits. The bits can have only set values, usually two -0 and 1. The particular combination of the bit values provides a code to represent a particular value of the information. In the case of Figure 1-1, there is a different code for each number.

Figure 1-1. Analog and Digital Systems

SILICON INTEGRATED CIRCUIT CHIP

# **Digital Systems and Digital Electronics**

Digital systems are systems that handle information in digital form and digital electronics are the electronic circuits that make up digital systems to handle the information in digital form.

# **Digital Functions**

A digital function is an operation (like adding two numbers, or selecting a code when a switch is thrown, or storing a combination of bits that represent a number) that is performed with digital circuits using digital information.

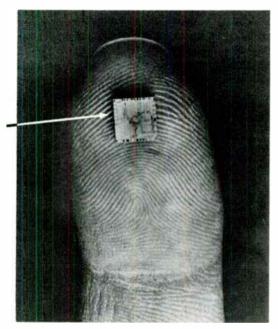

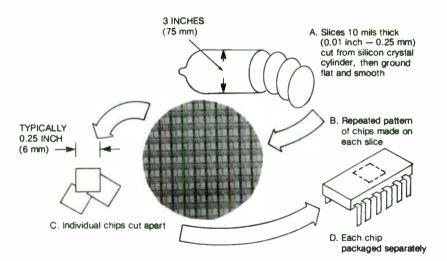

# **Digital Integrated Circuits**

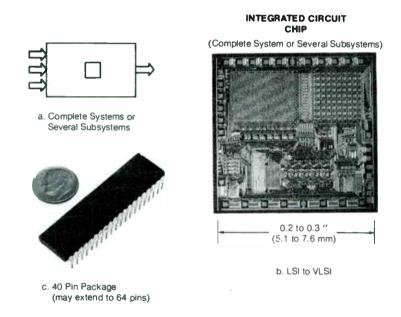

Figure 1-2 shows an "IC". That's the shortened name for an integrated circuit. It is a means of constructing and manufacturing digital circuits whereby all the circuits can be made very small on one piece of silicon semiconductor material so that the chip, about  $\frac{1}{4}$ " (6.35 mm) square, fits on a fingertip. Thus, digital integrated circuits are being called "fingertip electronics". All the digital functions required to perform complete system tasks can be put into such a small space that they fit on the tip of a finger.

Figure 1-2. Fingertip Electronics

UNDERSTANDING MICROPROCESSORS

# **Microcomputer**

A microcomputer is a complete digital computer, available in a variety of sizes from one or two printed circuit boards down to all circuitry on a single monolithic (one piece) chip. When all of the functions of a digital computer are available in one integrated circuit, it is called a single-chip microcomputer. It is called a microcomputer because of its small size (micro meaning small). It is usually in the smallest range of size and slowest range of speed when compared with all digital computer systems. On the other hand, it is a complete system and, as more and more digital functions are included as "fingertip electronics" on a single chip, the functions the microcomputer can do in a given size will increase rapidly.

A microcomputer has a microprocessor as its central functional unit. In computer jargon such a circuit is called a CPU (spoken as if you were spelling it – C - P - U) meaning Central Processing Unit.

# **Microprocessor**

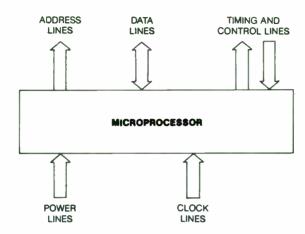

The microprocessor is a digital integrated circuit (or a set of IC's) that contains the digital functions necessary to be a CPU. It "processes" information and controls and keeps the system working in harmony as it responds to the step by step program that the CPU follows.

Throughout this book a microprocessor unit is considered to be within a microcomputer and when material is discussed on microcomputers it contributes to the understanding of microprocessors.

# **Computer-Like Circuits**

In many cases digital functions are being accomplished by digital integrated circuits that are not complete computers but use many of the same circuits used in computers. These may be designed especially for a given task (custom designed) or they may be combinations of standard functions. Such circuits are referred to as "computer-like" circuits.

# **ABOUT THIS CHAPTER**

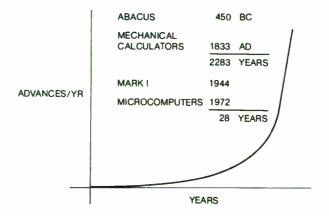

There is no question that digital electronics has made significant strides over the last few years. Take for example Figure 1-3 which shows the major technology advances that have occurred to impact computer technology since the abacus of 450 B.C. Examining the data shows that the real advances in digital systems have occurred since the early 1940's. The last 4 are directly related to advances in digital electronics and the integrated circuit. In fact, as demonstrated in Figure 1-4, it took almost 2300 years to advance from the abacus to Babbage's mechanical calculator, and it has taken only 28 years to advance from the Mark I relay computer to a single-chip microcomputer.

| 450 BC | CHINESE    | ABACUS                                 |

|--------|------------|----------------------------------------|

| 1642   | PASCAL     | MECHANICAL + MACHINE (GEARS & WHEELS)  |

| 1671   | LEIBNIZ    | MECHANICAL +, -, x, + MACHINE (BINARY) |

| 1833   | BABBAGE    | ANALYTICAL ENGINE (STEAM)              |

| 1944   | MARK I     | ELECTROMECHANICAL COMPUTER (RELAYS)    |

| 1946   | VON NEUMAN | STORED PROGRAM CONCEPT                 |

| 1948   | BELL LABS  | TRANSISTOR                             |

| 1950   | UNIVAC I   | VACUUM TUBE COMPUTER                   |

| 1959   | TI         | INTEGRATED CIRCUIT                     |

| 1971   | TI         | ONE-CHIP CALCULATOR                    |

| 1972   | TI         | 4-BIT MICROCOMPUTER ON A CHIP          |

| 1976   | TI         | 16-BIT MICROPROCESSOR                  |

| 1977   | TI         | 16-BIT MICROCOMPUTER ON A CHIP         |

|        |            |                                        |

Figure 1-3. Advances in Computer Technology

Figure 1-4. Computer Advances vs Time

Of the four computer eras shown in *Figure 1-5*, the last three are tied directly to advances in solid-state technology, more digital functions on a chip, and lower costs to provide more functions per dollar in a continually reduced space.

| 1ST GENERATION | 1950'S | VACUUM TUBES        |

|----------------|--------|---------------------|

| 2ND GENERATION | 1960'S | SOLID STATE         |

| 3RD GENERATION | 1970'S | INTEGRATED CIRCUITS |

| 4TH GENERATION | 1975   | COMPUTER-ON-A-CHIP  |

Figure 1-5. Typical Computer Eras

This is what's so exciting about microprocessors and microcomputers and computer-like digital circuits in general — they provide such high-powered digital functional capability in such a small space at such a low cost. This has caused an explosion in their use and a change in the approach to digital system design. To understand how and why this has happened is the subject of this chapter. Let's start with the use of digital electronics.

# WHO USES DIGITAL ELECTRONICS

Just about everyone uses digital electronics. We may not realize it, but digital electronic systems using microprocessors and microcomputers are appearing in more and more of the equipment that surrounds us each day — in our homes, the place where we work, the places where we shop, the places where we have fun. In our homes, in particular, the evolution is underway. Digital electronic circuits are controlling home appliances. Hand calculators are being changed into hand computers. More extensive fingertip digital electronics are finding their way into the home in the form of complete home systems.

# Digital Electronics in the Home

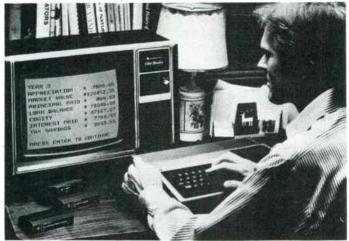

To see how digital electronics in the form of computer-like controls or microprocessors have become part of our everyday lives, let's look in on a modern family just getting settled after moving into their new home. We enter the scene with the man of the house working at his desk. He appears to be typing, but as we move in closer, we see that there is a keyboard and a small TV screen. We realize now that he is working with his home computer (Figure 1-6). He is looking at some family expenses and getting ready to study some possible investments.

Figure 1-6. Built-in Home Computer

# THE WORLD OF DIGITAL ELECTRONICS

1

# A Conversation — About a Home Computer

His son enters and interrupts him with a question: "Hi Dad, what are you doing?" "Working on some bills," replies the father. The son continues, "I was hoping I could play the space game; will you be through soon?" "Fairly soon, then we'll both play," said the father. The son watched the father making his entries and asked, "Dad, I was wondering the other day, are we the only family that owns a home computer?" His father answers, "No, there are many hobbyists who have them. We are probably one of the few families who have a computer that is built-in to help control many things around the house. But that's because we have just built a new house and we invested in a fairly complete home computer system."

"It must have cost a lot," the son commented. "Well, not really. About as much as we paid for Mom's used car," the father replies. "It's an investment that will last us a long time and it makes our lives easier and more enjoyable. We can do a lot of things with it. It helps us keep track of our expenses, supplies, and things we have to do. I can be a better investor, by making more money from investments. It helps us compare quickly things we want to buy so we can be better consumers and spend our money more wisely. It controls our heating and cooling system so that we get the most comfort for the least cost. It keeps our pool heated for the lowest cost."

"It even helps Mom in the kitchen. With the push of a few buttons, she can control her cooking time and temperature to save energy and, of course, time her cooking when she's away. It can keep track of her budget and what she needs to buy and when. It helps her save recipes and to adjust them for different meal sizes."

"It also keeps track of when we should fertilize the yard, when and how long to water the lawn, when we should change our furnace filters, and other simple schedules that we tend to forget without timely reminders."

"I've seen TV ads by companies that make computers and calculators and they talk about these small electronic circuits. I think they call them microelectronics or something like that — maybe integrated circuits," the son responded. "Are there any in our computer?" he asked.

"Oh, yes," said the father, "that's what makes it all possible. If the manufacturer didn't have integrated circuits, they would never be able to do everything in such a small space and at such a low cost. I know there's a central unit in here called a microprocessor. It does the main things, but I understand there are several other units that are just as complicated as the microprocessor that take care of getting the inputs in from this keyboard and from the tape recorder. Remember how we must play in the tape for the space game before we start. That's the program. It tells the computer what to do as we play the game."

# **About Appliances with Computer-like Controls**

"My teacher says it's very unusual for people today to have computers in their homes, but that many people will have them in the future," said the son.

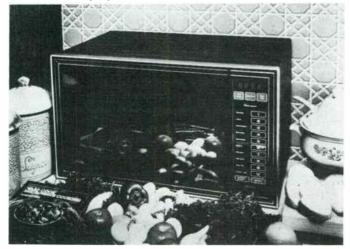

The father remarks, "That's particularly true since more and more people will be buying homes with built-in computers. What many people don't realize is that they already have computers of some form in their homes but don't recognize them as such. Take the microwave oven we have in the kitchen as an example (Figure 1-7). Contained inside it is a microprocessor circuit that controls its operation and provides Mom with many choices for cooking our food. She can tell the oven to defrost frozen food, tell it exactly when she wants it to start cooking, when it is to keep the food warm, and so on. She can program any sequence of these operations that she needs for any meal she wants to cook and the oven does the rest. Then, once the meal is prepared, the oven signals her with a buzzer."

Figure 1-7. Microwave Oven (Courtesy Litton Microwave)

"That's what's so nice about the new microprocessor control. The step-by-step sequence of things that it does can be set-up easily and changed easily; with the older controls you couldn't do that. They weren't programmable."

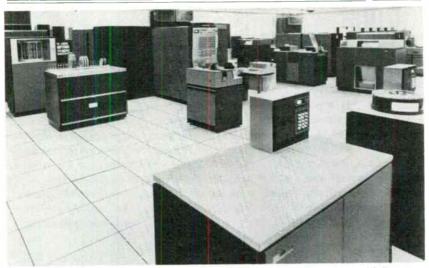

"The controls in that oven seem quite small," said the son, "I thought computers or controls like that were very large." "Well, they used to be much larger years ago," said the father. "In fact, when computers were first built (Figure 1-8), they required more room than the space in our entire house. But today, digital electronics, and especially digital integrated circuits, have changed that. They provide lots of functions in a very small space and for a very reasonable cost."

Figure 1-8. Early Large-Scale Digital Computer (Courtesy IBM Corp)

# **About Handheld Computers**

"Hand me that calculator there on mother's desk," he said. The son reached over and picked up the 4-function hand-held calculator they had purchased at the department store (Figure 1-9). "Now here is really a reduction in size," the father continued. "If you were to open this calculator you would find that essentially all the electronics except the keyboard and the display are in one package." "How much did we pay for it?" asked the son. "\$9.95," answered the father. "You mean that everything that's needed for all those calculations is made at the same time and put in one package?" asked the son. "That's right" said the father, "and that's why the cost is low. It takes only a small amount of time to put it together and test it."

Figure 1-9. Handheld Calculator

"I know they call these calculators, but is it really a computer?" asked the son. "Yes, somewhat," replied the father, "but it's one designed especially for certain problems and therefore limited in what it can do. It only has a keyboard input and a display as an output. It has no large memory for storing data or programs. It can't be changed in what it does unless the circuits inside are changed."

The father picked up the handheld scientific programmable calculator (Figure 1-10) he uses at work. "Now, here is a computer," he said. "It is programmable — that means it can be changed easily to solve many different problems. It has a magnetic card memory so that a program can be saved and used again and it can be attached to a printer to print out what's on its display. It's still limited in inputs and outputs and memory for storage, but it can solve problems as well as some of the better computers of the 1950's which were so large that they would have filled our living room. The size reduction is over 15,000 times." "Gosh, that's some size reduction," replied the son. "It sure is," replied the father.

Figure 1-10 . Programmable Calculator

# **About A Computer-Controlled Camera**

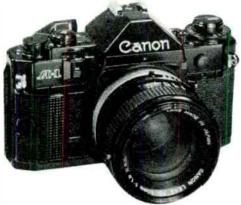

"Here, let me show you something else that really shows what digital electronics can do in a small size," said the father as he found a page in the photography magazine on the desk. "Take a look at the camera in this ad (Figure 1-11). It has a computerized control in it. It has a microcomputer with a microprocessor that was designed especially for this camera. It's really something. When you use the camera, you tell the microcomputer in the camera how you want the camera to act by simply setting switches on the camera to certain positions. The microcomputer then sets up the camera and automatically sets the exposure for you so that you get a perfectly

Figure 1-11. Automatic Exposure Camera (Courtesy of Canon Inc.)

exposed picture every time. All you have to do is point the camera, focus, and shoot." "Almost anyone could use one of those," the son observed. The father agreed, "and there's another advantage of using digital circuits. The camera settings can be displayed in number and letter form just as it is on your digital watch." "And look here," the father continued, "here's a picture (Figure 1-12) that gives you an idea of the small size of the computerized control circuitry. You see that most of the space in this small camera is used for film, viewfinder, lens, and mechanical controls. Only a very small space is required for the digital electronics that controls all the settings."

Figure 1-12. Interior View of Camera (Courtesy of Canon Inc.)

# **About Electronic Toys and Games**

"Dad, do the electronic toys contain computers?" asked the son. "Oh, yes, many of them do. That bowling game that Mary next door got some time ago for Christmas (Figure 1-13), that has a microcomputer in it. That ship game you received, (Figure 1-14), what do they call it?" "Code Name: Sector," the son replied. "That has a microcomputer in it and so does the one (Figure 1-15) that Steve gave Margo," continued the father, "And I found out something interesting about all of them from our engineer at work. All three of these games use the same single-chip microcomputer. Now, that really shows you the advantage of microprocessors and microcomputers. The same unit can be used to do many different things. Just by making it follow a different step-by-step procedure, the same microcomputer is used to control each of the three games."

Figure 1-13. Bowling Game (Courtesy of MARX)

Figure 1-14. Electronic Game (Courtesy of Parker Brothers CODE NAME: SECTOR® game equipment ©1977 Parker Bros, Beverly, MA.)

Figure 1-15. Computer Toy (Courtesy of Parker Brothers MERLIN<sup>TM</sup> game equipment © 1978 Parker Bros, Beverly, MA)

"I'm sure you can see the advantages to that. Instead of making three different microcomputers only one is made. The quantity of units for the single unit is now the sum of the units used in each of the three units. This reduces the cost." "Why is that?" asks the son. "It's just cheaper to make one unit in larger quantity than it is to make three units in smaller quantity," replied the father. "The game manufacturers use the same standard part but just change the step-by-step procedure to make their special game."

"That's what you said we do when we play games on our computer," noted the son. "Yes," agreed the father. "We play in a cassette and that programs the computer to: follow the position of the levers on our controls, to keep the score, to keep track of the action and set up the screen so we know what's happening."

"You see the same thing for many of the video games on the market. One central unit plays many different games by reprogramming it from cassette tapes. The number of different games is limited only by the number of cassettes that are available. This is why microcomputers and microprocessors are having such an impact, one unit can do so many things. They give you more for your money. Instead of having to buy a new game, you buy a new program. You get many different games for about the same price as older video games that were designed just to do a given set of games."

# **About the Future**

Thinking back on what they had talked about, the son said, "I didn't realize that electronics was doing so much. If this continues, we are going to be surrounded by electronics." "You're being surrounded already," was the father's reply. "We've just talked about what's going on in our home. Every place — in industry, in business, in the schools — electronics, and especially digital electronics, are doing things cheaper, more efficiently, quicker and are just making our life a lot easier. And it's going to continue. Microprocessors and microcomputers are bringing so much problem-solving capability into our hands at such a reasonable cost that more and more people are going to find ways to use them."

"Have you had anything on computers at school?" asked the father. "We are just starting to get into them in science class," replied the son. "You're going to be learning more about computers as you go on. You'll find they are not difficult to understand. They use common ways of doing things. Common names, terms, and functions are used over and over again. Once these common ways and terms are known, you will be able to understand how they are used over and over again in different ways to solve different problems or do different tasks. You'll be able to understand ———"

Quite a story, what's behind it? How did it come about? Why is digital electronics used? What made the so called digital electronic evolution happen? Let's start answering these questions by looking at why digital electronics are used.

# WHY DO WE USE DIGITAL ELECTRONICS?

In Figure 1-1 two systems were described. An analog system that has system quantities that vary continuously and a digital system where combinations of bits form codes to represent system quantities.

Analog systems are all around us. It is the conventional way that has been used for a long time to build systems. For some systems the analog solution is still the most economical and practical way, but because digital electronics can provide system solutions that solve the problem or do the task with less cost, more efficiently, more effectively, quicker, more accurately, digital systems are replacing analog systems.

# **System Solutions at Lower Cost**

Providing system solutions at lower cost has been a prime mover for digital electronic systems. The cornerstone for low cost has been solid-state semiconductor technology and, even more so, integrated circuit technology. Figure 1-2 showed an integrated circuit. Within such a chip of silicon material (a semiconductor material) enough digital circuits can be made to provide all the digital functions that are needed for a complete computer — a microcomputer. Because the circuits on the chips are made all at the same time, and because thousands of chips are processed together, the cost per function has been reduced up to 2,000 times below the cost when individual parts were wired together. All of this has occurred with improved system performance, smaller size and weight, lower power, wider temperature range operation, and much more reliable operation.

# A System Comparison

Perhaps this is best demonstrated by an example. Figure 1-16 is a comparison of an advanced scientific calculator and a computer of the mid 1950's. The calculator is an earlier model of the type shown in Figure 1-10. Within the calculator, which can be held in your hand, there is as much computing capability as the computer — and the computer occupies 270 cubic feet (7.56 m²). It's amazing but, in addition, the handheld calculator has better performance — adding 10 times faster, multiplying 5 times faster and transferring at approximately the same rate. Power is reduced by 100,000 times, volume by 16,000 times, weight by 8,500 times and all this with a cost reduction of almost 700 times. It seems impossible. Let's trace how this capability came about.

|                              | IBM 650<br>COMPUTER                                  | ADVANCED SCIENTIFIC CALCULATOR | IMPROVEMENT<br>RATIO                           |

|------------------------------|------------------------------------------------------|--------------------------------|------------------------------------------------|

| Components                   | 2,000 Tubes                                          | 166,500 Transistors            | 1:80                                           |

| Power, KVA                   | 17.7                                                 | 0.00018                        | 100,000:1                                      |

| Volume, cu. ft.              | 270                                                  | 0.017                          | 16,000:1                                       |

| Weight, fbs.                 | 5650                                                 | 0.67                           | 8,500:1                                        |

| Air Conditioning             | 5 to 10 Tons                                         | None                           | Uses None                                      |

| Operation                    | Stored Program,<br>Magnetic Drum<br>With 2,000 Words | Program Steps                  | Computing<br>Capability<br>Considered<br>Equal |

| Execution time, milliseconds |                                                      |                                |                                                |

| Add<br>Multiply              | 0.75<br>20.0                                         | 0.070<br>4.0                   | 10:1<br>5:1                                    |

| Transfer                     | 0.5                                                  | 0.4                            | Equal                                          |

| Price                        | \$200,000<br>(1955 Dollars)                          | \$299.95<br>(1977 Dollars)     | 700:1                                          |

Figure 1-16. Digital System Comparison

# The Digital Evolution

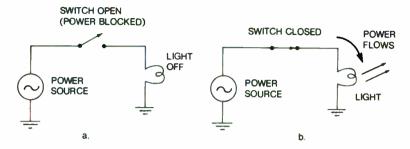

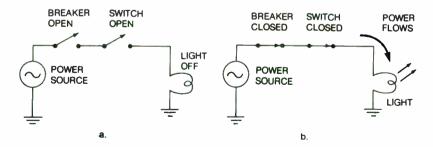

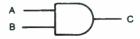

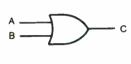

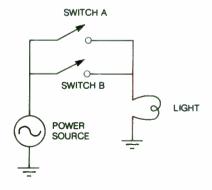

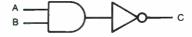

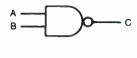

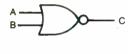

The digital codes of Figure 1-1 that carry the information in digital systems are moved through the system by digital circuits. The simplest of digital circuits is called a gate. Combinations of gates make more complex circuits. More complex circuits provide more complex digital functions. When more and more of these digital functions are combined, more complex subsystems and finally full systems result.

Such an evolution of digital electronics is shown in Figure 1-17, 1-18, 1-20, and 1-21.

Figure 1-17. Early 1950's - Discrete Devices Wired Together to Form Gates.

# Early 1950's

In the early 1950's (Figure 1-17), there were individual discrete solid-state devices such as diodes or transistors that had to be combined with separate resistors in order to form a gate. All had to be wired together by hand on terminal boards or printed circuit boards.

INTEGRATED CIRCUIT

# CHIP (All Gates) a. Gates c. 16-Pin Package c. 16-Silver (All Gates)

Figure 1-18. Early 1960's—Small Scale Integration (up to about 12 gates)

# Early 1960's

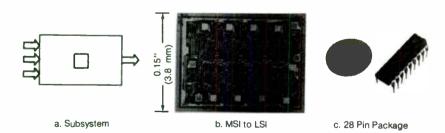

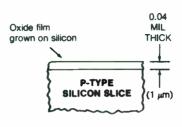

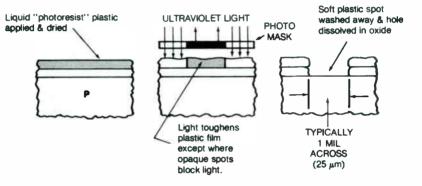

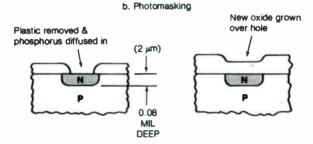

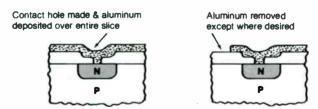

In the early 1960's (Figure 1-18), combining such components into one piece of solid-state material called an integrated circuit became a reality. This was called small-scale integration (SSI). Up to 12 gates were put into a piece of square material that was about twice as thick as a piece of paper and about as wide as a pencil lead. To interconnect the small circuits to the outside world, 1 mil diameter (0.0254-mm) wires are bonded from the silicon chip to a package lead frame (Figure 1-19). The complete assembly is molded into a plastic package.

Figure 1-19. Integrated Circuit Bonded to Lead Frame and Molded in Plastic Package

# Late 1960's

Through the late 1960's (Figure 1-20) the number of gates increased to over 1,000 on a single chip. First, using medium-scale integration (MSI), system building blocks were designed; then complete subsystems ushered in the age of large-scale integration (LSI).

# INTEGRATED CIRCUIT

(Building Blocks to Complete Subsystems)

Figure 1-20. Late 1960's - Medium Scale to Large Scale Integration (up to about 1,000 Gates)

# Through the 1970's

The LSI integration pace, launched by the handheld calculator with all its circuitry on one chip (except the keyboard and the display), continued through the 1970's (Figure 1-21). Advances were such that it was not uncommon to put 50,000 gates on the same chip as before  $-\frac{1}{4}$  inch (6.35 mm) on a side and 1/100th of an inch (0.254 mm) thick. All the circuitry for complete microcomputers on a single chip. This is very large-scale integration, VLSI.

Note that the number of package pins increased from 16 in early 1960 to 64 in the late 1970's to handle more bits for inputs and outputs, more bits for addresses and more control signals. The size of the integrated chip on the other hand hardly has increased in size. (It has increased a great deal by integrated circuit manufacturer's standards, but hardly by the user's standards).

Figure 1-21.

Thru the 1970's-LSI to Very Large Scale Integration (1,000 to 50,000 Gates)

## Results of the Evolution

In Table 1-1 and 1-2 the evolution is summarized. In Table 1-1, the change in the number of gates from early 1960 thru the 1970's means that 5,000 times more information can be handled digitally by VLSI integrated circuits than by SSI integrated circuits.

| TYPE     | TIME PERIOD NO. OF GATES |             | CHANGE FROM SSI (ratio) |

|----------|--------------------------|-------------|-------------------------|

| SSI      | Early 1960               | 10-12       |                         |

| MSI-LSI  | Late 1960                | 100-1000    | 100:1                   |

| LSI-VLSI | Thru 1970                | 1000-50,000 | 5000:1                  |

Table 1-1. Summary of Digital Evolution - Change in No. of Gates

| TYPE     | TIME PERIOD | NO. OF<br>GATES | AUG CH          | IP SIZE         | CHIP AREA (mils²) | CHANGE<br>FROM<br>SSI (ratio) |

|----------|-------------|-----------------|-----------------|-----------------|-------------------|-------------------------------|

| SSI      | Early 1960  | 10-12           | (mils)<br>50x50 | (mm)<br>1.3x1.3 | 2,500             |                               |

| MSI-LSI  | Late 1960   | 100-1000        | 150x150         | 3.8x3.8         | 22,500            | 9:1                           |

| LSI-VLSI | Thru 1970   | 1000-50,000     | 250x250         | 6.4x6.4         | 62,500            | 25:1                          |

Table 1-2. Summary of Digital Evolution - Change in Chip Size

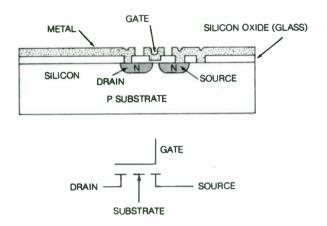

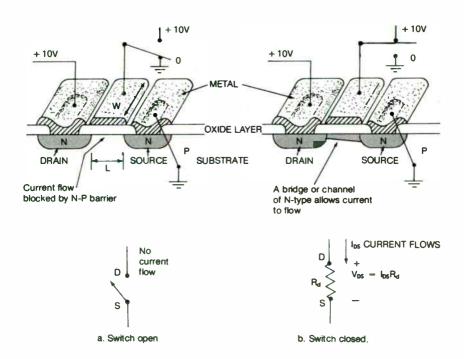

In contrast, the chip size has only changed by 25 times as shown in Table 1-2. This means that the area of solid-state material used per gate has been reduced by 200 times. To get an idea of how small a VLSI digital gate is look at a period on this page. Using MOS (Metal-Oxide-Semiconductor) integrated-circuit technology (this will be discussed in Chapter 3) over 20 logic gates can fit under the period at the end of a sentence.

Because the size of the integrated circuit chip has not increased that much, and because manufacturers have improved the ways the complex integrated circuits are made, the cost for processing each integrated circuit chip has increased very little. But, because there are so many gates per chip, the cost per gate has been reduced drastically!

For example, in the early 1960's, when SSI integrated circuits were first manufactured and there were 10 gates in a package, the cost of the package was \$10 and the cost per gate equaled \$1.

Contrast this with VLSI circuits with 50,000 gates which may sell at \$50 when first manufactured. The gate cost is 0.1¢, resulting in a cost reduction of 1000 times over the SSI circuit. As production volume increases such packages may well sell for \$10 and the cost reduction increases to 5,000 times.

# Impact on Equipment Cost

The total impact of the digital evolution is best demonstrated by the impact on end equipment costs. Figure 1-22 illustrates what has happened to the cost of a medium-scale computer. While in the early 1960's the hardware cost was \$30,000, in 1980 it will be approximately \$1,000, and it is projected to be \$100 in 1985. The result of increasing the number of digital functions available in a small space has been the reduction of the cost per function and the resultant lower end equipment cost — by as much as 300 times for the computer example.

| <b>EARLY 1960</b> |  |  |  |  |  |  |  | . \$30,000 |

|-------------------|--|--|--|--|--|--|--|------------|

| 1970              |  |  |  |  |  |  |  | .\$10,000  |

| 1977              |  |  |  |  |  |  |  | . \$5,000  |

| 1980              |  |  |  |  |  |  |  | . \$1,000  |

| 1985              |  |  |  |  |  |  |  | \$100      |

Figure 1-22. Cost of Medium-Scale Computer

In addition, the digital functions are available with the high reliability, low power consumption, increased speed of operation, high accuracy and light-weight features offered by digital integrated circuits. Such advantages are contributing to the explosion in the use of computer-like digital electronic systems and, in particular, microprocessors and microcomputer systems.

# WHY DO WE USE COMPUTERS?

Of the digital devices available to us, why do we use computers? What characteristics do these particular combinations of digital electronic subsystems have that make us want to use them? We can get an idea of what these characteristics are by looking at how computers have been used in the past. Refer to Figure 1-23.

#### 1. Computers are Fast and Accurate.

- A. Handle "Number Crunching" problems with ease.

- B. Handle tedious and routine tasks without error

- C. Handle "Real Time" problems fast and accurately.

## 2. What Computers Can Do is Continually Increasing

- A. Doing more in a small size with less weight and less power.

- B. Integrated circuit microprocessors and microcomputers.

## 3. Computers are Easily Changed (Programmable)

- A. Applications are changed by changing programs and not hardware.

- B. Expansion is possible by adding to the hardware, not discarding it.

Figure 1-23. Why do we use Computers?

## THE WORLD OF DIGITAL ELECTRONICS

# **Computers are Fast and Accurate**

# **Number Crunchers**

Computers first were used to handle very difficult and lengthy computations required for solutions to scientific problems. Because of their speed of operation, computers can handle "number crunching" problems in minutes that might take weeks or months to compute by hand. In addition, because digital electronic circuits handle information as bits, problem solutions and all computations can be computed with greater accuracy.

# **Tedious Jobs**

As computer hardware became more common, the tedious kinds of jobs of keeping track of records became a job for the computer. The same routine of debiting and crediting for checking accounts, credit card accounts, inventory, invoices, and receivables was accurately, consistently, and concisely accomplished by computers. The computer easily handles these routines and tedious tasks for us because it will happily repeat the same procedure over and over again without error.

# Fast Real Time

Business and project planning became the thing to do. Business plans were projected for years ahead, and these plans could be changed to try various approaches to determine the impact on profit or cash flow or return on assets. All of this became possible because of the incredible speed of modern computers and the increased computer capability in a given size.

Speed of computation is not critical to such business problems. It just means that the problem solution is obtained quicker.

"Real-time" problem solutions may have requirements where the computation speed is critical. For example, a system that checks that all conditions are GO for a space shot must do so in the last ten seconds. Digital computers do this job routinely with the necessary speed and accuracy.

# What Computers Can Do Is Continually Increasing

Refer again to Figure 1-23. With the increase in the applications came the demand to continue to reduce the size, weight, and power consumption of the computer. The digital integrated circuit fit right in. Systems that could perform the same computations were reduced in size by hundreds and thousands of times (See Figure 1-16).

Now microprocessors and microcomputers are available whereby computer systems can be assembled with just a few packages, or often with a single-chip microcomputer. This is enabling computer systems to be applied to almost any task – large or small.

# Computers are Easily Changed (Programmable)

Common to all of the applications and advantages of the computer is its programmable nature. This is a main reason why they are so versatile and can be applied to such a wide variety of jobs. Refer again to Figure 1-23.

The computer performs exactly the operations we instruct it to. We write down the things we want the computer to do in the order we want them done. This list of instructions is called the program for the computer. By changing the program, we change the behavior and thus the application of the machine. The main difference between a scientific computer and a business inventory computer is in the programs they are given. The scientific computer is given a procedure for calculating some arithmetic function to a desired accuracy. If we want to change the function or the accuracy, we just change the procedure, not the computer. The business computer is given a procedure to keep track of the business inventory as shipments are received and products sold. If we want to change the function or the accuracy, we just change the procedure, not the computer. If we want to expand the computer to handle payroll and timekeeping, the equipment is not changed to handle the job, just new programs are added.

Microprocessor and microcomputer systems bring this same flexibility to their applications, no matter how small the task. With an appropriate program and using basically the same hardware, a microcomputer system can be a toy, an oven controller, a camera control, part of a manufacturing line, etc. All that need be done is to make sure the system is given the right procedure to follow so that it will do the exact task that is required.

## ARE COMPUTERS REALLY EASY TO UNDERSTAND?

Since computers have been used to perform very complex tasks, most of us feel that they really must be complicated. In reality, computers offer us a simple, organized way to build almost any electronic system. They behave in ways that are similar to our own behavior. They are made up of circuits or functions that are easily understood and readily available. With microprocessors, we really only have to buy a few types of different circuits and connect them together to make a computer. This is because the computer consists of only a few different types of functional units.

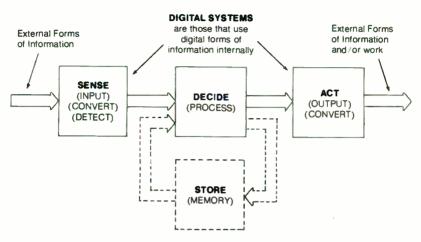

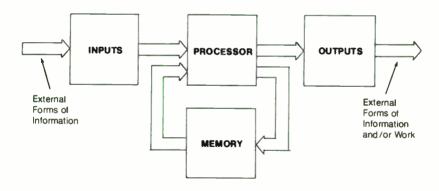

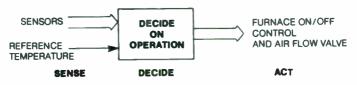

As shown in Figure 1-24, all systems (including the human system) can be broken into the functions of sense, remember (store), decide, and act. Once we can provide all these features, we can build anything we want. The computer system provides all four of these functions, as shown in Figure 1-25, in low cost units that are easy to connect together.

Figure 1-24. Universal Digital System Organization

(G. McWhorter, Understanding Digital Electronics, Texas Instruments Incorporated,

Dallas, Texas, 1978)

Figure 1-25. Computer System Organization

# **Sense Function**

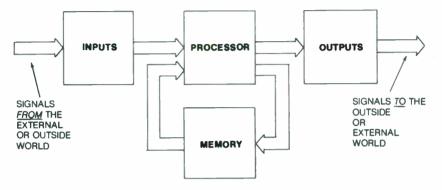

In Figure 1-24, the sense function is what the name implies. It senses information and transmits it to the machine for decoding (interpretation) and response. This input information can be data about surrounding conditions such as temperature, pressure, light, and so on, or it can be communications and commands that set the machine in a given mode and tell it where to start. By having such sense elements, the system can receive information from humans or from other similar equipment. In the computer system of Figure 1-25, the functional units that perform the sense function are simply called inputs.

## Remember Function

The remember (store) function (Figure 1-24) is important to all advanced machines. The machine must remember what it is to do, information for use in what it does, and results of what it has done. It also must remember a number of rules that must be used in making decisions, performing arithmetic and controlling the system. The computer system name for this function is memory, for obvious reasons. In the computer (Figure 1-25), the memory serves the same function as the memory portion of the human brain. It remembers the step-by-step sequence of operations (the program) the computer is to perform. It also remembers the instructions and information (data) that are used. Computer memory devices are available as single integrated circuits that can be connected easily to the other functional units of the computer system.

# **Decide Function**

The decide function (Figure 1-24) is much like the reasoning function of our brain. All the computations, logical operations, and operational decisions are made here. These decisions take into account the inputs (commands and information about the surroundings) and the information in memory. In the computer (Figure 1-25), the decide function is provided by the processor. It performs the basic arithmetic and logical decisions required by the computer. It also controls the operation of the computer by turning on and off the other functional units in the system at the proper times. The processor in a microcomputer system is a microprocessor. It may be in a separate package or be contained in the single-chip microcomputer that fits on the tip of a finger.

# **Act Function**

The act function (Figure 1-24) is again what the name implies. Once a decision has been made by the processor, the system carries out the decision with the act units of the system. These may be devices that display information so it can be communicated to humans. Or the act unit may turn on a motor, or turn off a light, or light the gas in a furnace; or it may be to position a drill bit, or some other similar control operation. The act units allow the system to control something external to the system or to exchange information (communicate) with humans or other machines. In the case of the computer (Figure 1-25), the devices that implement the act function are called the outputs of the system.

The functions of sense or input, act or output, remember (memory), and decide are functions that we can all understand easily. The computer provides all of these functions. The way in which the step-by-step sequence (the program) uses these functions defines the task that a particular system performs. A system can be made a video game by placing the game procedure or program from a magnetic tape cartridge into the system, providing a television screen output, and using game position controls as inputs. We can make a heating unit controller from the same basic set of hardware by providing temperature sensor inputs, furnace fuel and blower controls as outputs, and a program that will monitor temperatures and turn on the furnace at the proper times. The list of such examples is almost endless. We simply have to recall the conversation between the father and son to see how varied the possibilities are.

# WHY ARE MICROPROCESSORS SO IMPORTANT?

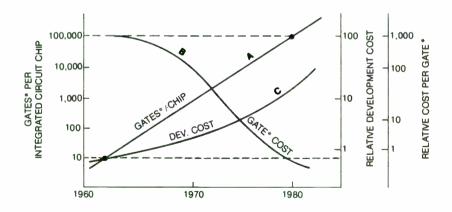

Look at Figure 1-26. Even though we have shown the advances that digital integrated circuits have made in providing more and more digital functions within a single package (curve A), and the reduction in cost per functional unit (curve B), the importance of microprocessors may still not be apparent.

\*Possibly Best Represented by a More All Encompassing Term Like Active Element Group—AEG.

Figure 1-26. Summary of Semiconductor Technology Evolution

Curve C will help to understand the final missing link. In the early 1960's the cost of developing an SSI integrated circuit was on the order of \$20,000. A 50,000-gate VLSI integrated circuit of the late 1970's may have cost nearly one-half million dollars to develop. Unless the complex integrated circuit with all its functions can be sold in large quantities so that the cost per package can be low, the development costs will not be recovered and the next design will not be financed. When the quantities manufactured are low, the package cost would have to be so high to recover the development costs, that no one would use them. Their end equipment cost would be too high.

There are complex chip designs that are designed for specific applications (custom designs), and the calculator integrated circuit is one of these, where the quantities to be manufactured are large enough to support the high cost of development. However, many systems are used only in small quantity and another solution is necessary. Here is where the microprocessor is so important.

# **A Standard Unit**

To meet the needs of large quantity production a "standard" integrated circuit was designed – the microprocessor – so it could be made at low cost. One that many different people could use; one that could be applied to many different applications by programming it differently. Thus, the emphasis changed in the design of a system. Instead of designing a particular set of hardware for each application that is dedicated to a particular system solution, standard hardware units that have many types of functions are made to solve different system tasks by changing the program. The program, not the hardware, varies for each application.

Here is the importance of the microprocessor and its corresponding single-chip microcomputers. They are units that can be told to solve many different tasks by varying the step-by-step sequence they perform. All systems use the same unit. Each system in itself may be produced in small quantity and require only a small number of the standard unit. However, large quantities of the standard unit are required when all of the smaller quantities are added together. Manufacturing the unit in these large quantities results in a low cost unit.

# **Learning Curve**

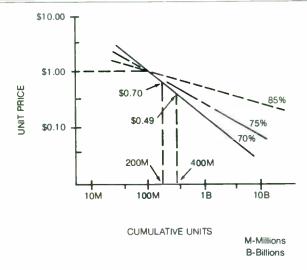

Experience in the manufacture of integrated circuits is very important. When a large quantity of a given unit is going to be manufactured, the proper investment can be made in the automated equipment, in personnel training, in manufacturing process improvements, and in technical support people. These investments produce a learning experience in manufacturing the integrated circuit which reduces its cost. Such learning-experience cost reduction is shown in *Figure 1-27*, and, is called a learning curve.

Figure 1-27. Learning Curve

The basic concept of a learning curve is that, after a product is being manufactured in large quantities, each time the total number of units manufactured doubles, the unit price reduces by a constant percentage. The 70% slope of Figure 1-27 is one that has been typical for the manufacture of SSI and MSI integrated circuits. It says that if the total number of units manufactured was 100 million and the price per package was \$1.00, then when the total number of units manufactured reached 200 million the price had reduced to 70% of \$1.00 or 70 cents. When the total volume reached 400 million then the price reduced to \$0.70x70% or 49 cents.

The same learning experience has been true for the LSI and VLSI circuits with the slope ranging from 75 to 85%. It is this kind of regular reductions in the cost of a microprocessor as it is manufactured in large quantities that will help to lower the price and contribute to continued expansion of the applications.

Needless to say, if an integrated circuit is not manufactured in large quantities, then the resulting cost reduction will not occur. But with microprocessors this will be accomplished in a little different way.

They will be manufactured in large quantity even though they are used in small quantities for any one individual design.

They will be made and sold at low cost and the cost will move down a learning curve as the quantity of units manufactured accumulates. Because of the low cost more systems will be designed which, in turn, will lower the cost. The cycle will continue until the unit is replaced with a new and better design.

# System Design Trends

# A Viable Alternative

Providing subsystems or even full systems within one package has certainly changed the emphasis for the designer to a system orientation rather than one concerned with each individual detailed circuit. In addition, when the system design is being considered, if the system designer wants to use VLSI integrated circuits he has several choices that depend on the number of systems that will be manufactured. If the quantity is large, the two choices that are available are listed below. The one chosen should meet the system objectives in the most cost-effective way:

- Have a special VLSI circuit designed which is dedicated to the specific application. It's likely this will result in the lowest equipment manufacturing cost but it will have limited chance for change without redesigning.

- Use a microprocessor and the different general purpose packages that have been designed to work with it, and develop a program that guides the system to do the task at hand.

When the quantity is small the same choices are available. The first choice would result in development expenses that usually cannot be justified. In addition, the end cost of the units would be higher.

However, the second choice is a very viable alternative. Because standard units are used with a different program, all the cost advantages of a unit manufactured in large quantity are available even for the system manufactured in small quantity.

# System Development Costs

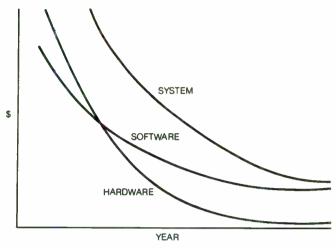

Microprocessor and microcomputer systems are very important because they can be developed at lower total cost due to all the functions that are available within one package. Figure 1-28 is a curve showing how total development costs have changed since the introduction of integrated circuits.

Since fewer packages are used, fewer assemblies are used. This requires fewer connectors, fewer cabinets, less power distribution, and less air conditioning. The end result is that the hardware costs are reduced as shown.

All the programming effort that is used to prepare the step-by-step sequence to get the system to do a particular task is termed "software". The name came about because most software is written or printed material. Because of microprocessors and microcomputers the total development cost has been reduced, even the software costs. Note, however, that the software cost becomes a much larger part of the total development cost.

Figure 1-28. System Development Costs

# A Shift to Software

The percent of total costs for software increases because a different program must be developed for each new application. This is a significant change in the way systems are designed. Now the designer must be concerned about how a program is written to make the step-by-step procedure control the system. No longer is the major effort on the design of the hardware. Now it is the creation and checkout of the software.

This change in design procedure is not easy for many designers. However, it is going to be a continuing trend for the future and it is hoped that the fundamental concepts developed in this book will aid in making the change easier.

## **ADDITIONAL STANDARD UNITS**

The ability to change the things a system can do by changing the order of the things the microprocessor is told to do will extend to the other units that are needed around the microprocessor to perform the sense and act functions. Family units designed to work with similar types of microprocessors will also be made programmable. Thus, they become "standard" units as with the microprocessor, and are manufactured in larger quantity at a lower cost.

The family of units also is an advantage when preparing the software. Because all the family units follow the same instructions, as step-by-step procedures are developed for different applications, the things that are learned and used begin to accumulate to make the next software job easier.

It is difficult to predict the overall impact of microprocessors and microcomputers except to say that it is and will continue to be great. It is hoped that this chapter has given some insight as to why this is so.

# WHAT HAVE WE LEARNED?

- An analog system handles information with signals that vary continuously.

- Digital systems handle information with signals in digital form—a

combination of separate parts called bits that have set values and occur

in codes to represent a particular letter, number, character or symbol.

- Digital electronics has provided the computer controls for many of the products we use.

- The computer is a fast, accurate, and versatile digital electronics system

that can be programmed to perform the sequence of operations we need

for a given application and can be changed to do different tasks by

changing the program.

- Solid-state technology through integrated circuits has made digital

electronics the lowest-cost approach to building complex products

because it is possible to provide a large number of digital operations in a

small area of solid-state material.

- Medium-scale computers have been reduced in cost by 300 times as a result of the digital evolution.

- The central control element of a computer, the processor, is available in integrated circuit form in a device called a microprocessor.

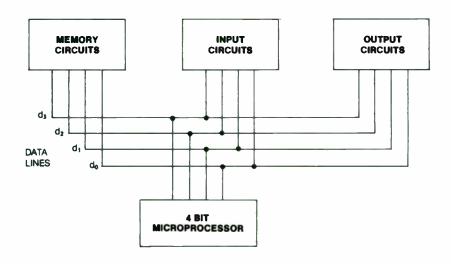

- Connecting memory and input and output circuits to a microprocessor forms a computer.

- A microcomputer is a complete digital system in a small size that is

usually in the smallest range of size and slowest range of speed when

compared to all digital systems.

- Microprocessors and microcomputers are bringing so much problemsolving capability into our hands at such a reasonable cost that more and more people are going to find ways to use them.

- The existence of programmable standard devices such as the microprocessor and other units that surround it, allows all digital system designers to share the benefits of solid-state technology at reasonable costs.

# WHAT'S NEXT?

In this chapter, we have seen some of the characteristics of computers that make them so useful to us. We are now ready to begin looking at the operation of the computer in detail. In the next chapter, we will start by looking at each of the computer functional blocks and how they work together to form a smoothly functioning system that can do almost anything.

### **Quiz for Chapter One**

- 1. Answer the following statements true or false:

- Most of us will never use a microcomputer.

- **b.** Microcomputers are even found in cameras.

- c. Microcomputers and microprocessors are hard to understand.

- d. Microcomputers are enabling computers to be applied to many tasks.

- e. Computers behave much like we do in many ways.

- The microprocessor's main disadvantage is that it is not versatile.

- g. Microprocessors are now found in systems that were originally built with analog electronics.

- h. It is easy to change a computer's behavior or application.

- Match the following human features with their computer counterpart:

Human

Computers

- a. Eyes

- b. Ears

- c. Memory

- **d.** Voice

- e. Muscles

- f. Reasoning

- A. Sensor Input

- **B.** Memory

- C. Control Output

- D. Communication Input

- E. Microprocessor

- F. Communication Output

- 3. Over the years solid-state technology has:

- a. Provided more digital functions in a smaller area of material.

- **b.** Increased the cost per digital function.

- c. Has made it harder to understand and build electronic systems.

- d. None of the above.

- Microprocessors and single-chip microcomputers are important because:

- a. They allow all of us to use the same functional blocks in building our systems so that we can use low-cost units which contain a large number of digital functions.

- b. They allow us to bring the advantages of the computer to all products, large or small.

- c. They can replace calculators.

- d. a and b above

- e. a and c above

- f. None of the above.

- 5. Computers offer the following advantages:

- a. High speed operation

- b. Accurate operation

- c. Versatility

- d. Programmability

- e. All of the above

6. The purpose of a microcomputer system is defined by its program, inputs, and outputs. Show which inputs and outputs would be used to make the following systems:

| e., | -4 |     |

|-----|----|-----|

| 57  | 81 | em. |

- a. Home Computer

- b. Camera

- c. Furnace Controller

- d. Lawn Watering System D. Radio Receiver

- e. Garage Door Opener

#### Inputs

- A. Temperature Sensor 1. Motor

- **B.** Typewriter

- C. Moisture Sensor

- E. Light Sensor

#### **Outputs**

- 2. Water Valves 3. Television Screen

- 4. Gas and Air Flow Valves

- 5. Aperture, Shutter Speed, and LED Indicator Control

- 7. A device is said to be programmable if:

- a. Its behavior or operation can be changed by changing commands or instructions it is given.

- b. It can be adapted to many applications by giving it a suitable program.

- c. Its operation is fixed and unchangeable.

- d. a and b above.

- 8. 100 million VLSI circuits are produced at a cost of \$2.00. If the production is increased to 400 million, what will be the new cost per device (Assume an 80% learning curve slope)?

- a. \$1.00

- **b.** \$1.28

- c. \$1.60

- d. None of the above

- 9. Match the computer subsystems with the system function:

- a. Sense

- A. Outputs

- **b.** Decide

- B. Memory

- c. Act

- C. Inputs

- d. Store D. Processor

- 10. Software for microcomputers:

- a. Is mainly the computer program

- b. Is less expensive to design than the hardware

- c. Can be used only once

- d. None of the above

9a-C, 9b-D, 9c-A, 9d-B; 10-a 26-C, 2f-E, 3-a, 4-d, 5-e, 6a-B,3; 6b-E,5, 6c-A,4; 6d-C,2, 6e-D,1; 7-d, 8-b, 1a-F, 1b-T, 1c-F, 1d-T, 1e-T, 1f-F, 1g-T, 1h-T, 2a-A, 2b-D, 2c-B, 2d-F,

# Basic Concepts in Microcomputer Systems

#### **ABOUT THIS CHAPTER**

As we saw in the last chapter digital systems have the basic functions of sense, remember, decide and act.

In this chapter we will examine how the computer system satisfies these functions and how the functional blocks work together — all the while searching for understanding of the basic concepts.

#### WHAT ARE THE MICROCOMPUTER BUILDING BLOCKS?

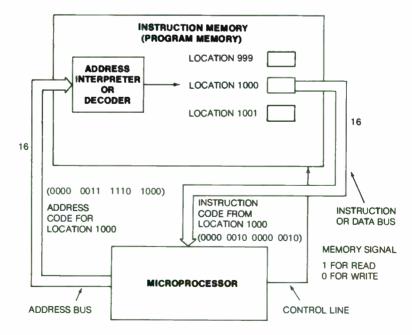

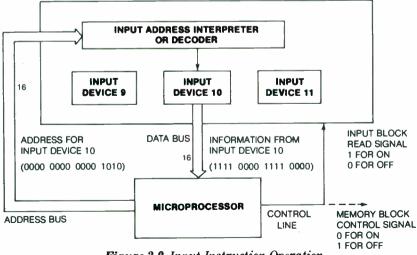

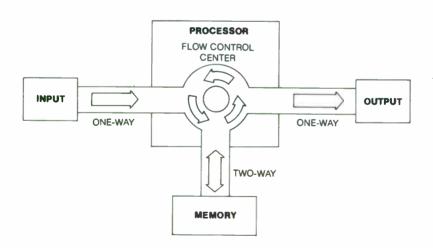

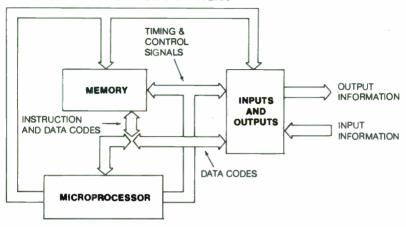

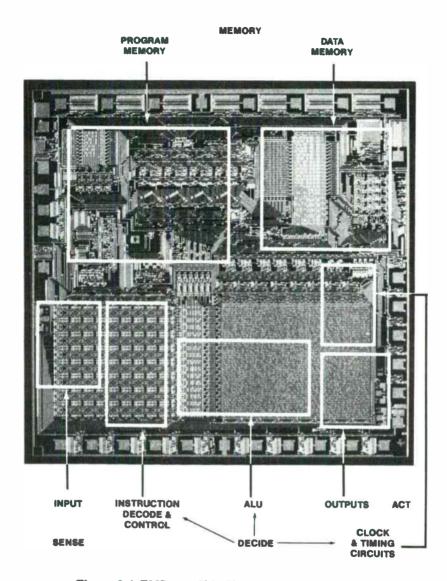

Microcomputer components can be purchased and interconnected to provide a computer system with the functions of sense, remember, decide and act. For the computer system, as shown in Figure 2-1, the sense function is the inputs, the remember function is the memory, the decide function is the processor or control, and the act function is the output. Inputs and outputs, even though they perform different detailed functions, are handled very similarly in the microcomputer system and can be classified as a basic communications function. As a result three basic computer system functions result: Processor or control, memory and communications.

#### Microprocessor — The Central Control Function

The microprocessor tells all the other system components what to do and when to do it. It does all the arithmetic and makes all the decisions for the rest of the system. It is much like the control center of any other system such as the brain of humans, the boss of a company, or the master switching center of a train yard. All of these tell each part of their system what to do and when to do it. As an example, the subconscious part of our brain regulates all of our vital systems in correct order. The reasoning part provides our decision making and other higher intellectual capabilities to help us do what we want when we want.

The boss of a company assigns tasks to all the workers and makes sure that each of them performs his job on time and in cooperation with the other workers in the firm.

The train yard switching center selects and connects boxcars, freighters, flatcars, tank cars, and so on, into cross-country trains by the flick of a lever which controls train yard switches.

Similarly, the microprocessor turns on and turns off all the system components in the proper order and at the proper time to make sure the entire system works in harmony.

All of these systems, as shown in Figure 2-1, are not independent of the outside world. They require inputs from the outside world to sense and react to. They give outputs to the outside world to provide action as a result of the inputs. They sense inputs and act on these inputs to provide outputs. Even the memory of the system may receive inputs or provide outputs to the outside world.

Figure 2-1. The Building Blocks of Computers

#### Memory

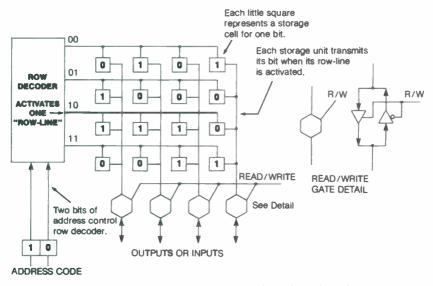

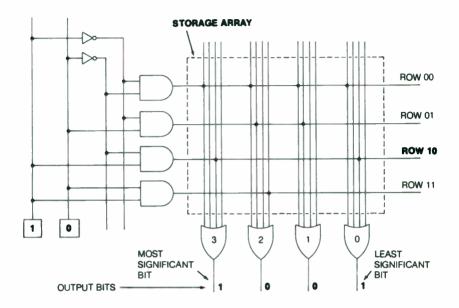

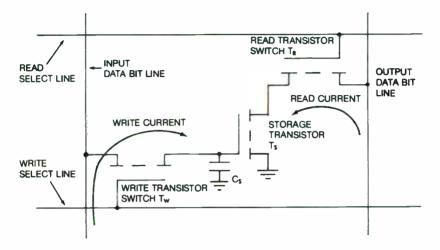

Let's look at memory. The microcomputer memory performs the rather obvious function of remembering or storing information needed by the system, the same function as the human memory. It is also similar to the file systems and note pads that humans use to store information that they want to refer to later but can't keep completely within their brain at all times. Numbers, words or characters that the microcomputer system must use in performing its tasks — its data — is stored in its memory. It stores this information as bits, "1's" and "0's" as shown in Figure 2-2. The arrangement of bits form codes to identify each number or character.

|                | 16-BIT WORDS                    | 8-BIT BYTES     | 4-BIT<br>NIBBLES |  |

|----------------|---------------------------------|-----------------|------------------|--|

| MEMORY WORD #1 | 100000001000000                 | 10000000        | 0000             |  |

| MEMORY WORD #2 | 0000000010000001                | 01100110        | 0 0 0 1          |  |

| MEMORY WORD #3 | 0000000010000010                | 00111100        | 0010             |  |

| MEMORY WORD #4 | 0000000010000011                | 1 1 0 0 0 0 1 1 | 0 0 1 1          |  |

| MEMORY WORD #5 | 0000000010000100                | 11100111        | 0 1 0 0          |  |

| MEMORY WORD #6 | 0 0 0 0 0 0 0 0 1 0 0 0 0 1 0 1 | 0 1 0 1 0 1 0 1 | 0 1 0 1          |  |

Figure 2-2. Information Stored as Groups of Bits

#### BASIC CONCEPTS IN MICROCOMPUTER SYSTEMS

## 2

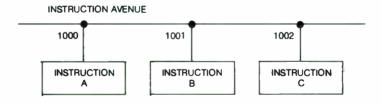

The memory is also used to store or remember the instructions or sequence of operations the processor is to perform. Such a memory is called a program memory. The instructions also are coded with "1's" and "0's". The sequence of instructions, stored in order one word after another as shown in Figure 2-2, is called the computer program.

#### Input and Output

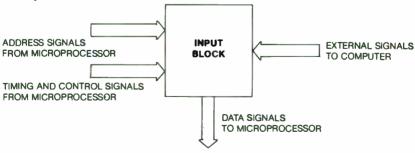

Every system must have input and output blocks to provide the sensing, action, and communications functions for the computer. The sense input elements keep track of the system conditions such as temperature. pressure, light levels, and so on. This is similar to the way our human senses of seeing, hearing, smelling, tasting, and feeling make us aware of the conditions around us. The output action elements enable the microcomputer to turn on or off power units such as motors, relays, lights, and so on, much like our brain can control our muscles to do work for us. The communications inputs allow human operators to send information or instructions to the computer using typewriter keyboards, calculator-like keyboards, position controls, telephones, and so on. These devices are much like our ears and eyes, since we use these organs to receive speech and to read printed characters. The communications outputs allow the computer to send information to human operators through character displays or typewriters. These devices are similar to our speech, writing and printing capabilities used for sending information to others.

#### **HOW DO THESE BUILDING BLOCKS WORK TOGETHER?**

The individual function of each block is evident from its name: memory remembers, inputs and outputs communicate with the outside external world, and the microprocessor processes information and controls the operation of the entire system. How these functions work together to achieve their assigned tasks is not so evident. The way the blocks work together can be seen better by looking at the way we do our jobs. We, as humans, act as a computer in many of our activities. We are given a list of instructions in the form of a recipe and get the cake baked by following the recipe instructions step-by-step. We are given a list of jobs that must be done and get the jobs done by doing each in proper order. We behave exactly like a microprocessor behaves in a microcomputer, following each instruction and doing each job a step at a time.

#### An Example Program

Let's take as an example the situation we have when we are trying to follow the instructions in a recipe. Assume we are trying to make chocolate fudge from a recipe of the type shown in Figure 2-3. This recipe is a list of instructions that we must follow exactly if the fudge is to be successful. The list of instructions has been saved or stored on a piece of paper. Some recipes are saved in the memory of some cook somewhere, but this one is available to us in written form. This is similar to the use of the memory in a computer. In the computer, the list of instructions, the program, is stored in solid-state devices as a pattern of digital bits of information. Just as the written instructions on paper are meaningful to us, the digital form of instructions is meaningful to the processor of the computer. In either case, the program or plan of operation is saved and ready to be executed. In the case of the recipe, we must execute the instructions in the order listed without making any mistakes if we are to produce fudge and not mud. Similarly, the processor must execute the instructions in the order they are listed in the computer memory if the computer is to behave as it was intended. Failure to execute the instructions in the proper order and without error could cause an automatic lawn mowing machine to become a berserk public menace or a furnace control system to become a device that burns down the house.

- 1. Get a mixing bowl.

- 2. Get 5 pounds of granulated sugar.

- 3. Get two 8-ounce cans of evaporated milk.

- 4. Get 12-ounce jar of white corn syrup.

- 5. Get 1 package of pecans.

- Get 1 package of chocolate chips.

- 7. Get 1 stick of butter.

- 8. Get 2-ounce bottle of vanilla extract.

- 9. Measure 21/2 cups of sugar into the mixing bowl.

- 10. Measure % cup evaporated milk into the mixing bowl.

- 11. Measure 1/2 cup white corn syrup into the mixing bowl.

- 12. Measure 2 tablespoons butter into the mixing bowl.

- Get a separate container.

- 14. Measure 1 cup of nuts and 12 ounces of chocolate chips into the separate container and set aside for later use.

- 15. Mix all ingredients except nuts and chips together in the mixing bowl.

- 16. Pour this mixture into a pan and bring to a boil.

- 17. Boil for exactly 5 minutes. Slowly stir mixture as it boils.

- 18. Remove from heat and stir in one teaspoon of vanilla extract.

- 19. Stir in nuts and chips (from Step 14) until chips are melted.

- 20. Pour fudge into buttered pan.

Figure 2-3. Chocolate Fudge Program

#### BASIC CONCEPTS IN MICROCOMPUTER SYSTEMS

## 2

#### **Getting Started**

Since we have the program of instructions stored in some suitable form (on paper or in the computer memory), we must read and interpret (decode) the first instruction in the program. In the case of the recipe we actually read the instruction with our eyes and find out its meaning with our brain. The processor in a computer does the same thing by bringing (transferring) the instruction code (in the form of a group of digital signals or bits) into the processor and using the digital electronic circuits inside of the processor to decide what operations the instruction wants done. In the recipe, we see that once we have gotten together the supply of goods that we need, the first thing we must do is measure 2 1/2 cups of sugar into a mixing bowl. Once we do this, we go down to the next instruction, which is to measure 3/4 cup of evaporated milk into the bowl. These types of operations continue until all of the basic ingredients are combined and the result placed into a pan for cooking. Up to this point, most of our activities have been in the form of inputs and initializing the components of our cooking system. The computer usually goes through these types of operations early in the operation of the machine. It steps through instructions that tell it to receive inputs which are digital code commands or which set up system switch conditions that tell the system where to start, when to stop, the limits of memory, etc. Also, it will save needed numbers in some memory locations and clear others, just as certain quantities of specified ingredients were measured into the 'storage locations' of the mixing bowl and, after everything was combined, poured from the bowl into the cooking pan.

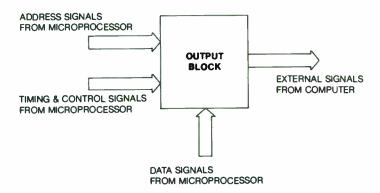

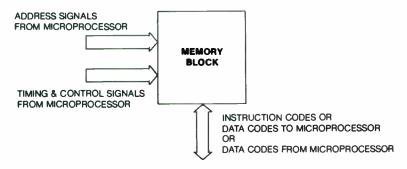

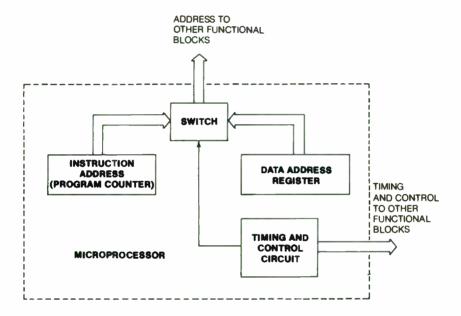

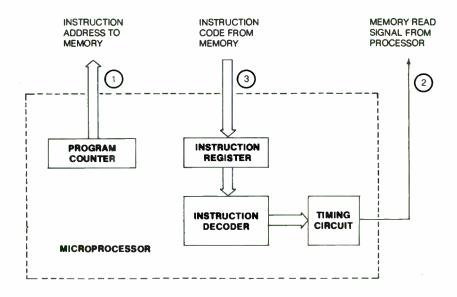

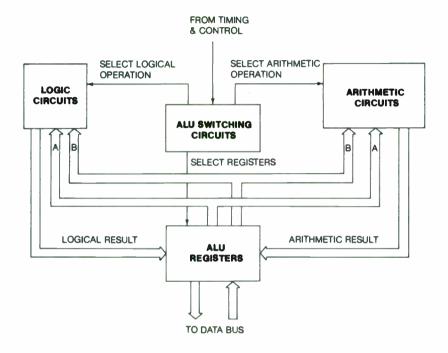

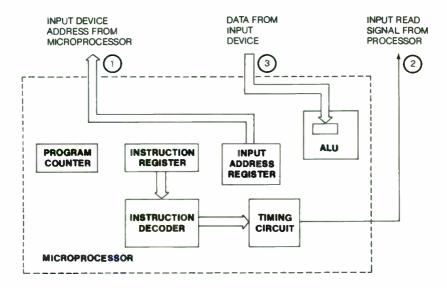

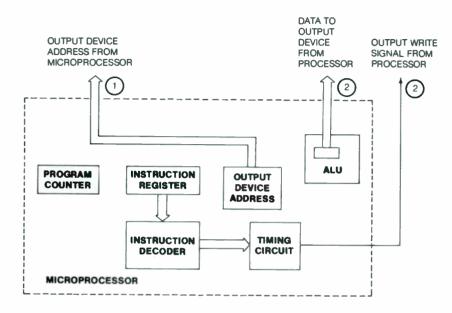

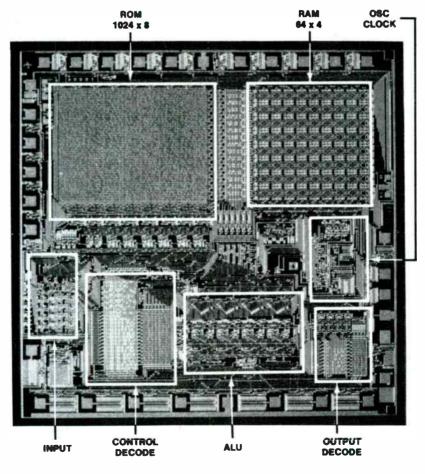

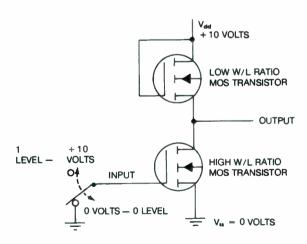

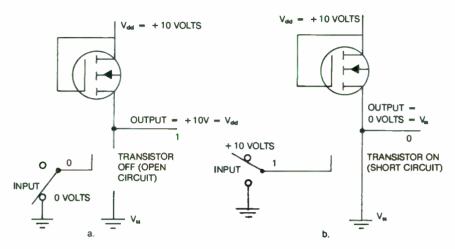

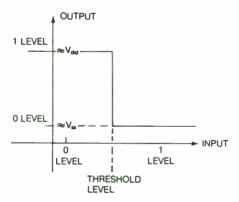

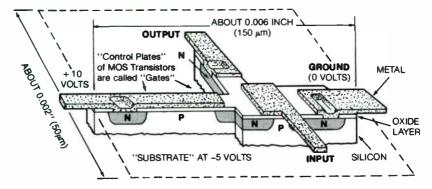

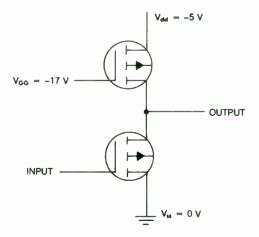

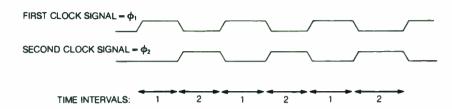

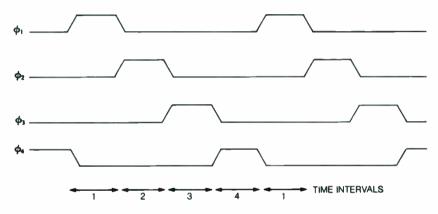

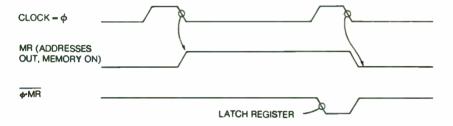

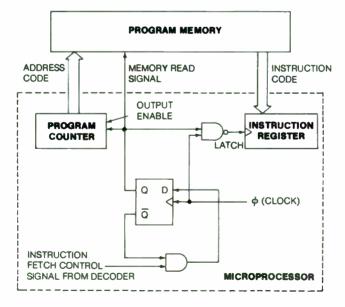

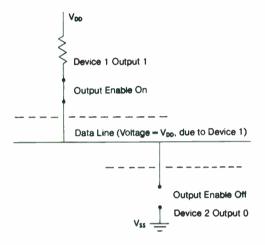

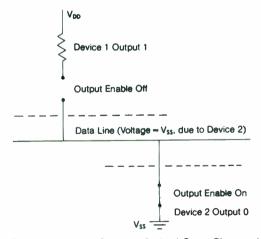

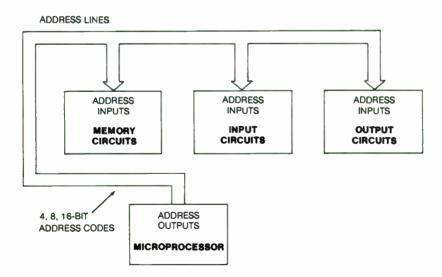

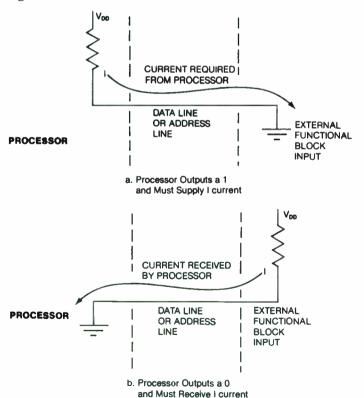

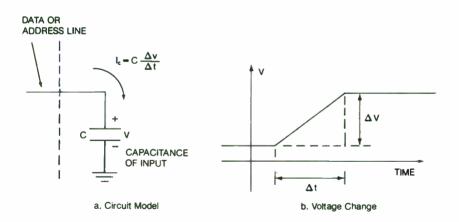

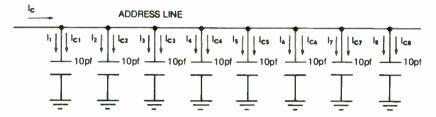

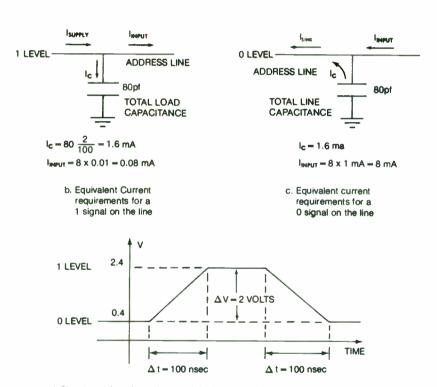

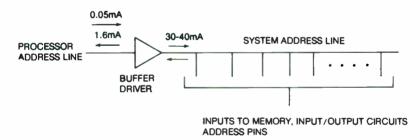

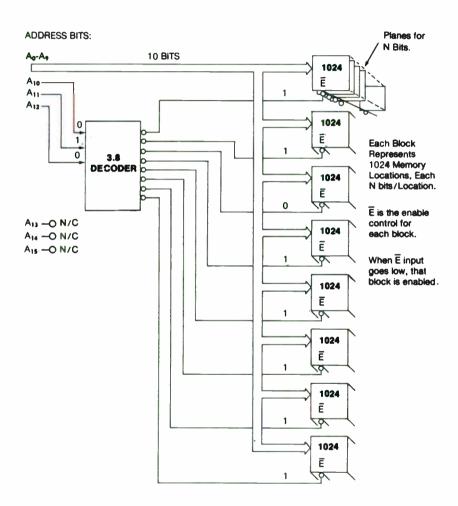

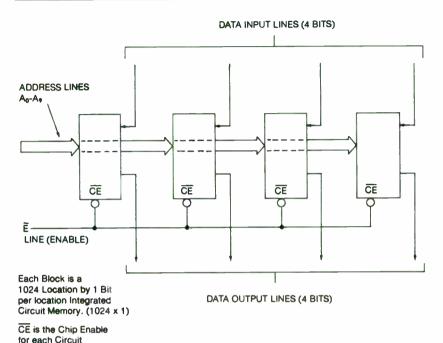

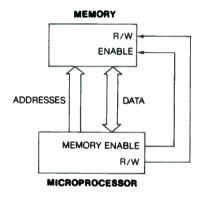

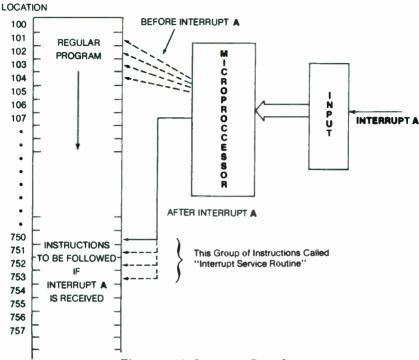

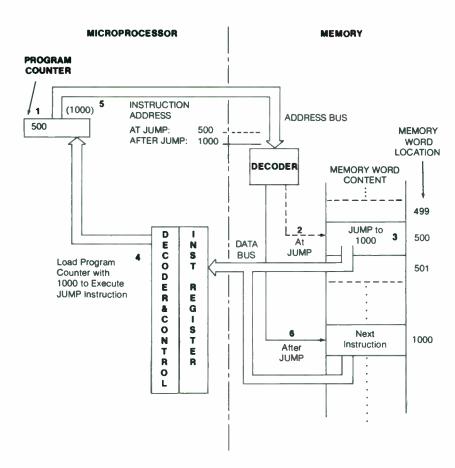

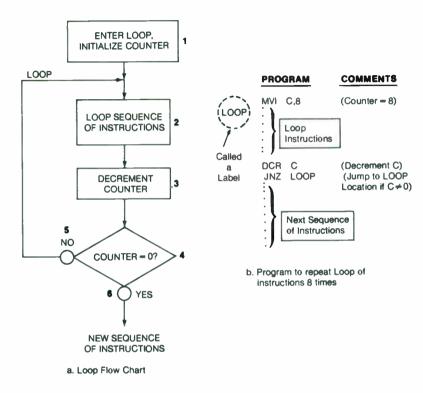

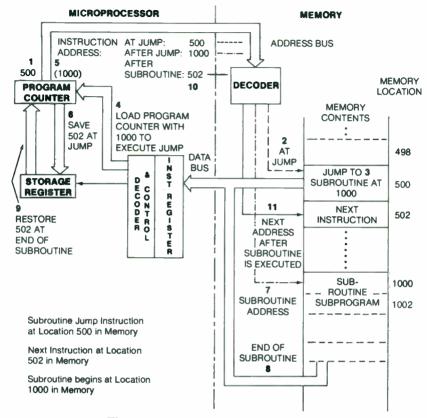

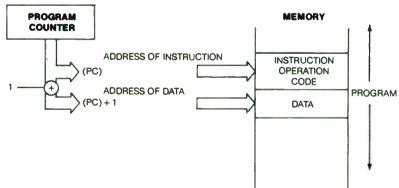

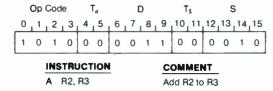

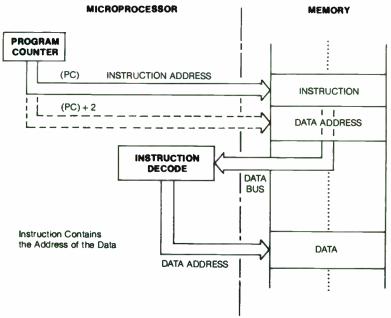

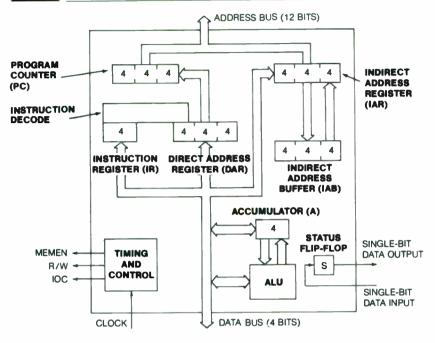

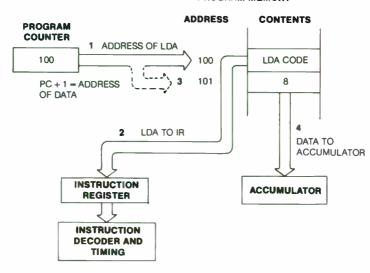

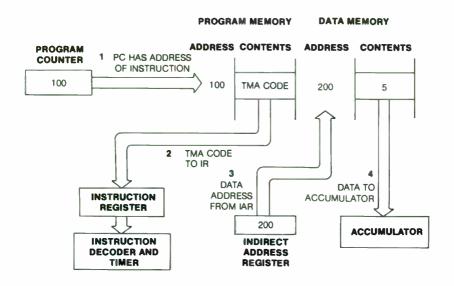

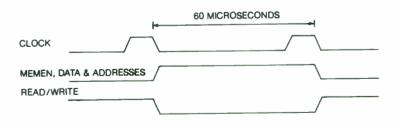

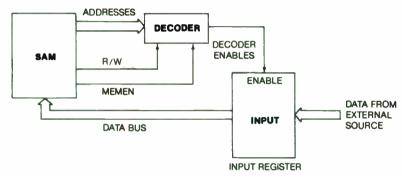

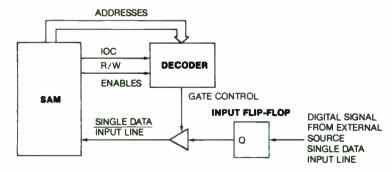

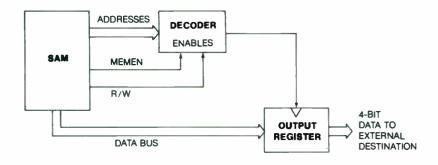

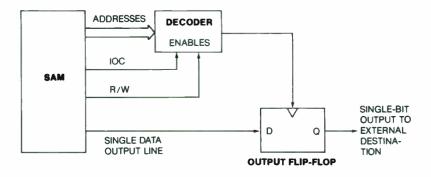

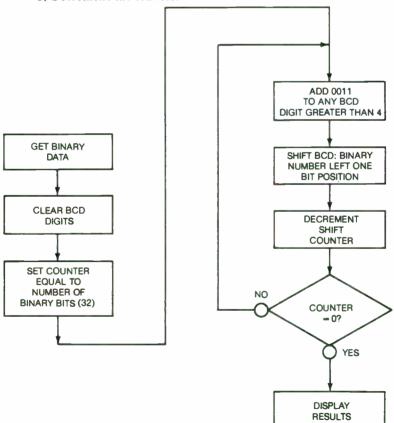

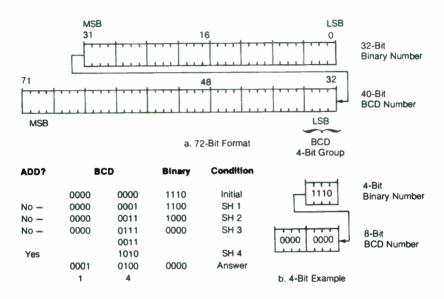

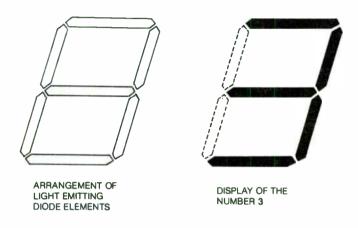

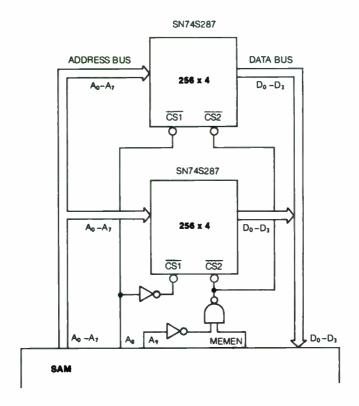

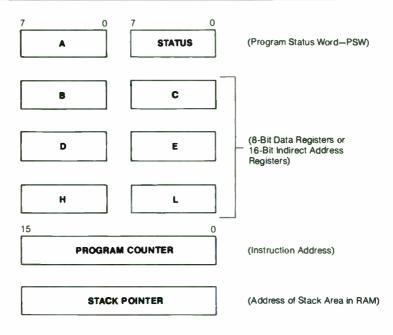

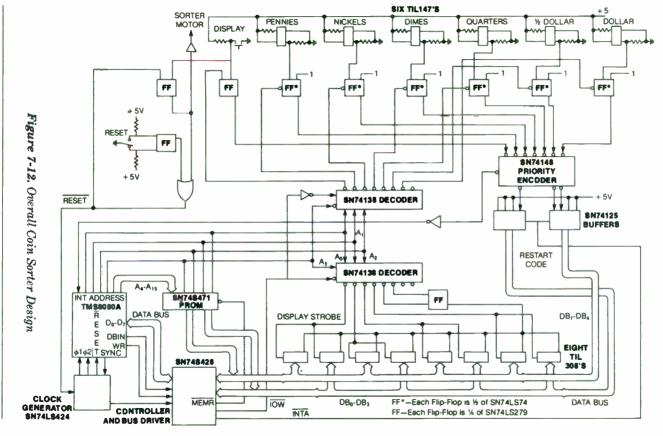

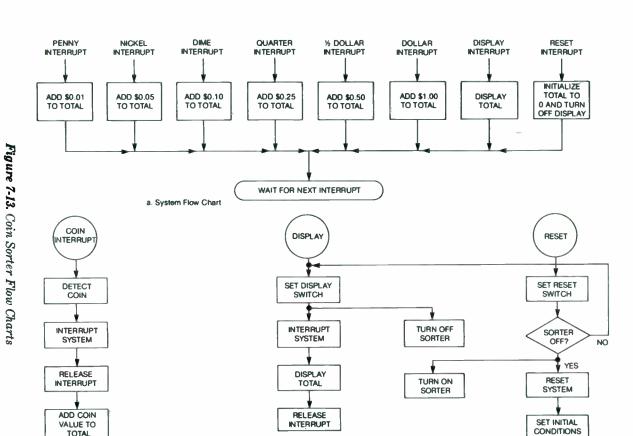

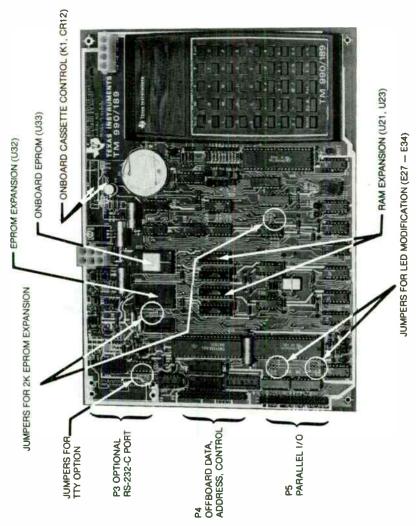

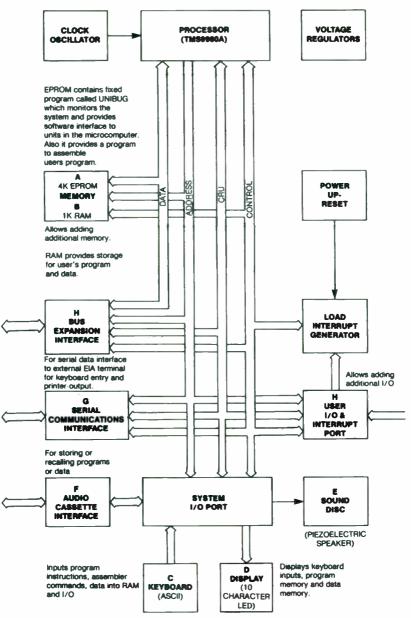

#### Setting Aside Results for Later Use