# Basic Principles of Vacuum Tube Logic Circuits

**v1.0**

# A compilation of excerpts from public domain documents available on the Intertubes

If you know of any excellent documents on the subject that should be included in this compilation, please email me at: wbblair3@yahoo.com

Customer Engineering Manual of Instruction

### Principles of Electronic Operation

THIS CHAPTER will cover the principles and operation of the basic 604 "electronic building blocks" and will show how "freed" electronics is able to do already familiar jobs.

Both G suffix and H suffix circuits are covered in this and following chapters. F suffix circuits are similar to the G, though unit locations may differ. Where the F suffix circuit operation is much different, separate descriptions are included.

All circuits are first covered in general form, and then followed by a detailed description as it applies to specific suffix machines. Each circuit description, while dependent upon the objective introduction, is complete in itself. Thus, in studying the H suffix machine, no reading need be done in the sections labeled "G." It is suggested that only one machine type be studied at one time.

Electrons have long helped IBM machines perform, largely through electro-mechanical effects. Relays, mechanical counters, clutches, and ratchet control mechanisms are all examples of mechanical devices controlled by electron flow. In the 604 unit, IBM released a machine which freed electron actions from mechanical inertia. Electronic building blocks were developed to do the jobs previously done by electro-mechanical means.

Instead of relays, electronic switches and triggers are used; instead of counters, trigger combinations were developed, etc. Only the work involved in reading and punching IBM cards has remained mechanical. The increase in calculating speed made possible by freeing electronics from mechanics can be seen by a typical comparison: a normal wire relay can pick in three milliseconds (three thousandths of a second), and for good design, five milliseconds minimum time must be allowed. Its electronic counterpart, an elementary trigger, will flip (or "pick") in two microseconds (two millionths of a second), and five microseconds allows a good margin of safety. Even with the conservative design of the 604, which allows a ten microsecond flip time, this gives a five-hundred-fold speed gain.

#### BASIC CONCEPTS

THE BASIC CONCEPTS of practical electronics are quite simple. Present theory is that all matter consists of atoms having a central nucleus around which one or more small particles called electrons spin rapidly. An electron which has been pulled away from its nucleus is called a free electron. Electrons each have a negative charge and repel one another. A group of free electrons in an area makes this area negative. Given a chance, this accumulation of electrons will try to flow to any other area that is less "crowded" (that is, less negative). An area which has a shortage of electrons is called positive and has a considerable attraction for free electrons. Because of this, electrons always flow from negative to positive. Any material capable of easily carrying a flow of electrons is called a conductor. Any material through which free electrons have difficulty passing is called an insulator. Those materials in between these extremes may resist the flow of electrons to one degree or another and are called resistors. Some combinations of materials will let electrons flow in one direction, but not in the reverse. These are called semi-conductors (half-way conductors). One other important fact is that it is quite possible for an electron to make its force (or presence) felt through an insulator without itself actually passing through the insulator.

The amount of force with which electrons are trying to move from one place to another is measured in an arbitrarily assigned value called a volt. Free electron unbalance being a relative matter, voltage must always be specified as between two areas. Throughout our circuit descriptions, the voltages given will be with respect to the metal frame of the machine (which is called ground). Any exceptions to this convention will be clearly pointed out. Any point having an excess of free electrons will have a negative potential and be noted as a minus voltage, such as -100 volts. Such voltages can be spoken of as "so many volts below ground." As the converse, any point having a shortage of electrons has a positive potential, and would be noted as a plus voltage (such as  $\pm 150$ ) and spoken of as "volts above ground." Two points, one at  $\pm 100$  volts (with respect to ground) and the other at  $\pm 150$  volts (again with respect to ground) are actually 250 volts apart with respect to each other.

The amount of opposition a circuit presents to the flow of electrons is expressed in an established unit called the ohm. The more resistance a circuit has, the greater its ohmic value. Most of the resistances involved in electronic circuits are in thousands of ohms. As a shorthand notation, the symbol "k" is used to indicate thousands. A 68,000 ohm resistor can thus be written as 68k on diagrams, within text, etc. A convention which has been adopted for the 604 is to leave off the "k" on machine diagrams; all values being understood as in thousands of ohms. 68 on a 604 machine print means 68,000 ohms. A 470 ohm resistor is written as .47. This IBM convention is applied generally to components physically located within pluggable units; external components or components located within the punch or references within the text will be found using the "k" or with the full value written out.

Along the same lines, capacitor values in the 604 are understood to be in micromicrofarads unless a symbol is added to indicate otherwise.

The motion or flow of electrons past a given point in a circuit is measured in an arbitrary unit called the ampere (which represents an actual number of electrons passing a given point in one second). This unit of measurement is somewhat too large for most of our calculating circuits, and as a result the term milliampere (abbreviated, ma) will be used frequently. This is simply one thousandth of an ampere.

With these few facts properly applied, any calculating circuit in the 604 can be explained on a practical level. No attempt will be made to go into electronics in depth, but enough explanation will be given to help explain most conditions encountered in the troubleshooting or learning process.

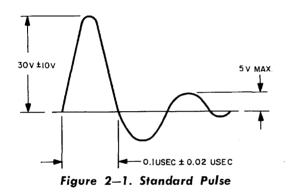

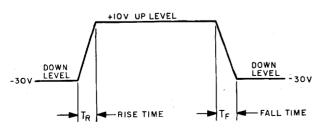

The circuits in the 604 are designed to work from a ten microsecond pulse of fifty or one hundred volts amplitude. This means that the steady state voltage (electron pressure) at a particular point is shifted either upward or downward by fifty or one hundred volts for a ten millionths of a second time period. This change in voltage level can be passed on to other circuits to cause certain actions. Some circuits will produce or use shifts of longer duration. Where these shift durations exceed twenty microseconds in time they are referred to as gates (since they are generally used to "open" a circuit so a ten microsecond pulse or series of pulses can pass through). It is the control and generation of these pulses and gates that constitutes the whole of 604 circuitry.

A pulse or gate that is more positive (or less negative) during its active time than otherwise, is called a "plus pulse or gate" even if the "up level" is still negative with respect to ground. Similarly, a pulse or gate that is negative (or less positive) during its active time, is spoken of as a negative pulse or gate. For example, a point which rests at plus 150 volts and which drops to plus 50 volts for ten microseconds during active time, is said to have a minus 100 volt pulse available even though the signal did not go negative with respect to ground at any time.

#### BASIC ELECTRONIC CIRCUITS

NOT ALL of the basic circuits to be described in this section are used in both the G suffix and H suffix machines. Following the headings for the various circuits, the machine type or types using such circuits will be indicated in parentheses.

#### Power Supply Notation (G and H)

There are five DC supply voltage levels used in the 604 (plus two in the 521 Punch). These five 604 power supplies are numbered in accordance with the Electronic Industries Association coding as follows:

Plus 150 volts is supply number 2.Plus 75 volts is supply number 3.

Minus 100 volts is supply number 5.

Minus 175 volts is supply number 6.

Minus 250 volts is supply number 7.

Whenever a point in a circuit requires one of these potentials, that point on machine wiring diagrams will be shown connected to a small square box identified inside with the proper code number. The diagrams in this manual will also make frequent use of this coding though in addition the DC voltage equivalent will often be written near the box to help develop familiarity with the coding.

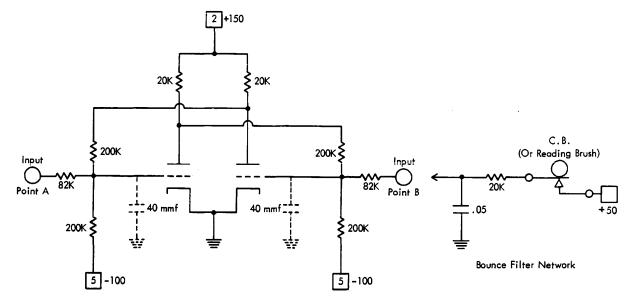

#### The Inverter (IN) Unit (G and H)

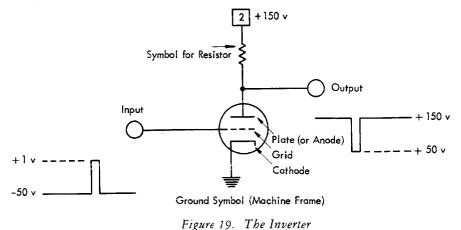

This is the basic electronic circuit from which most others are derived. In its simplest form the circuit con-

1 igure 19. 1 ise inverti

sists of a triode vacuum tube and one resistor arranged as shown in Figure 19. A signal which is applied to the input point goes through the circuit and comes out inverted exactly as indicated by the illustration. Thus the name "Inverter." This inversion is a characteristic of *any* vacuum tube circuit *where the signal goes into a grid and comes off the plate.* However, in the 604 the term "Inverter" is applied only to a particular class of pluggable units using triode tubes. These units are all identified on the handle as "IN" (to designate the general class) followed by a number (to identify the variations within the class). IN-1, IN-2, IN-15, etc., are typical types.

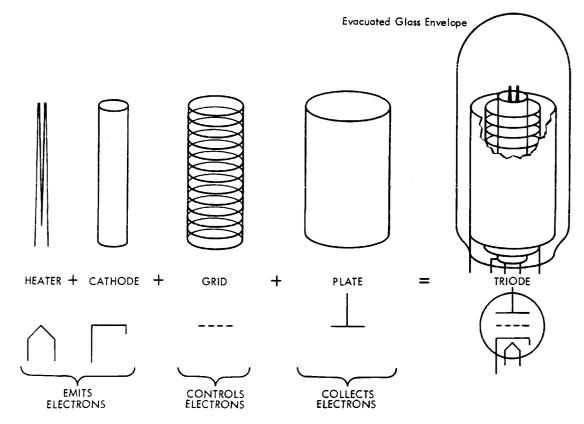

An understanding of this circuit is most important. The heart of it, of course, is the tube itself. This consists of a length of heating wire folded or twisted inside a cylinder called the cathode. Electrons are boiled off the cathode surface when this assembly is heated by

Figure 20. Development of the Triode Tube

passing a current through the heater wire. If a metallic cylinder (called the plate or anode) is placed around the cathode (but separated from it) and this entire assembly sealed in an evacuated envelope, it will be possible to make electrons travel from the cathode to the plate. This is done by making the plate positive with respect to the cathode. As the electrons are boiled off the hot cathode, they tend to move toward a less "crowded" area and thus find the plate very attractive. Such a tube is called a diode (consisting as it does of two basic elements, the heater-cathode combination and the plate). This diode has one very important characteristic that makes it of practical value in circuits actually used in the 604H calculator: electrons are able to travel from the cathode to the plate if the cathode is hot and the plate has a positive potential with respect to the cathode; but electrons cannot travel from the plate to the cathode no matter what the relative voltages are. This is because the plate is not heated and thus does not "boil off" electrons. The diode thus becomes a semi-conductor (a half-way conductor). Its practical use and application will be described later.

The triode tube used in the inverter circuit is a three element tube consisting of a cathode and plate with a grid inserted in the space between them. This grid consists of a coil of fine wire with spacing between each turn. Electrons can still pass between the grid turns and flow to the plate under proper conditions. See Figure 20.

With the cathode heated and a positive voltage applied to the plate, electrons boiled off the cathode will be attracted to the plate, as with the simple diode, except that they will now have to pass between the turns of the grid wires. If a negative, repelling voltage

is applied to the grid with respect to the cathode, the electrons emitted by the cathode will not feel the attraction of the plate as much as they did before. As a result, the flow of electrons from cathode to plate will be greatly reduced. If the grid voltage is made sufficiently negative with respect to the cathode, it will be so repellent to the electrons that none will reach the plate. The negative grid voltage which will completely stop current flow to the plate for any particular tube and plate supply voltage is called the "cutoff" potential. For the triode tubes and voltages used in the 604 this value is ten volts negative or less. Once a tube has been cut off by driving the grid sufficiently negative, driving the grid still more negative has no further effect. From these facts, the action of the basic inverter circuit can be explained.

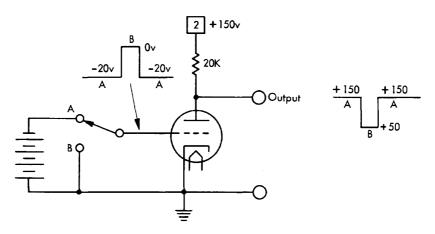

In Figure 21 a resting voltage of minus twenty with respect to the cathode is applied to the grid. Because of this, there is no electron flow through the tube (the tube is cut off). As a result, there is no electron flow through the 20,000 ohm resistor between the plate of the tube and the plus 150 volt supply. The output point is therefore at the same level as the supply voltage, 150 volts positive with respect to ground.

By throwing the switch in Figure 21 from A to B, the potential on the grid of the triode tube with respect to the cathode will be changed from minus twenty volts to zero. Electrons boiling off the cathode will now no longer feel a repelling grid and will instead be strongly attracted to the positive plate. As a result of this, electrons will flow through the tube and through the resistor in its plate circuit, causing a voltage change from one end of the resistor to the other. With the tube type used in the 604, at the supply voltage used (plus

Figure 21. Basic Inverter Circuit

150), and with a 20k plate load resistor, 5 milliamperes of current will flow through the tube and resistor. By Ohm's law ( $E=I \times R$ ) this indicates that a one hundred volt drop occurs across the plate load resistor. Since the +150 volt supply end of the resistor is rigidly held at +150, this 100 volt change must occur at the plate end of the resistor. This leaves +50 volts at the tube plate and at the output point. Returning the switch to the minus twenty grid volt position, A, will again cut off the tube and restore the plate and output point to plus 150 volts.

Two items about this action should be noted. First, during the active portion of this cycle, while the switch was thrown to B, the grid signal was less negative and thus more nearly positive than during its normal state. In other words, a positive (going) signal was applied to the grid. This, however, resulted in a lowering of the positive level on the plate of the tube where the output is taken. A negative (going) signal thus came from the output point when a positive (going) signal was applied to the grid. This is the inversion effect mentioned earlier.

A second point to note is that though only a twenty volt change was applied to the grid circuit of the tube, a one hundred volt change resulted in the output. This action of a triode, its ability to amplify an input signal, is used only indirectly in the 604 calculating circuits. The amplifying ability of a tube changes considerably with the aging of the tube, and any computer making much use of this factor would (unless constantly compensated) be rather unstable with the passage of time. The 604 generally uses tubes either in their full conduction state or cut off completely. While the total amount of full conduction current may vary through the life of the tube, the circuits are designed to work well with any normal variation.

#### PRACTICAL INVERTER CIRCUITS (G AND H)

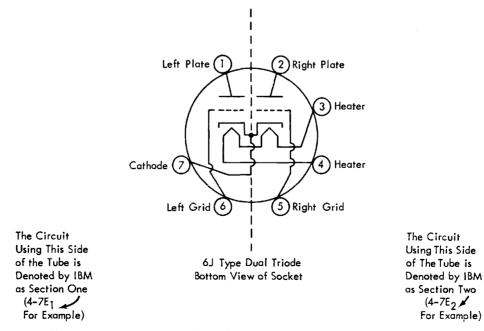

There are twenty-seven types of INverter units used in the various 604 types. They all follow the theory discussed above, but practical considerations have introduced a number of variations. An IN type pluggable unit contains two separate inverter units. The tubes used for 604 inverter service are all dual triode types with characteristics (though not construction) somewhat similar to the commercial 616. These tubes contain two separate triode units sealed within the same evacuated glass envelope. The two cathodes of the separate sections are internally tied together electrically and the heaters connected in series. This allows a seven pin tube base to be used where ten pins would otherwise be required. Such tubes are called the 6J type class by IBM to identify directly interchangeable tubes of various designs and manufacturers.

The 5965 is a heavier duty type of dual triode used by IBM for occasional inverter service and for extensive service in other types of circuits. This tube has a nine pin base which allows separate connections to be made

Figure 22. A 6J Type Dual Triode Pin Connection Diagram (Bottom View)

to each cathode. A tap is also made to the heater wire where it runs between the two tube units; this permits a 12 volt series connection or a 6 volt parallel connection of the two unit heaters. The parallel arrangement used by IBM for circuits using this tube type makes it possible for one section of a 5965 to have an open heater while the second section is heating correctly. This is not true of the 6J type with their internal *series* connection. The basing connections for these and other tubes used in the 604 can be found in the Appendix of this book.

Since two functionally separate triodes are available in one glass bulb, a great saving is made in the number of pluggable units required by the machine through including the components for two separate circuits in one unit basket. This does, however, require an addition to the pluggable unit location code described in Chapter One, Figure 12, in order to positively identify the particular circuit section of such a dual unit. A subscript 1 is added to the right of the location code (such as  $4-7E_1$ ) to identify the circuits used with the left half of the tube as drawn in the manufacturers' tube basing diagrams (Figure 22 and in the Appendix). A subscript 2 is used to indicate the circuits for the right half of the tube (such as  $4-7E_2$ ).

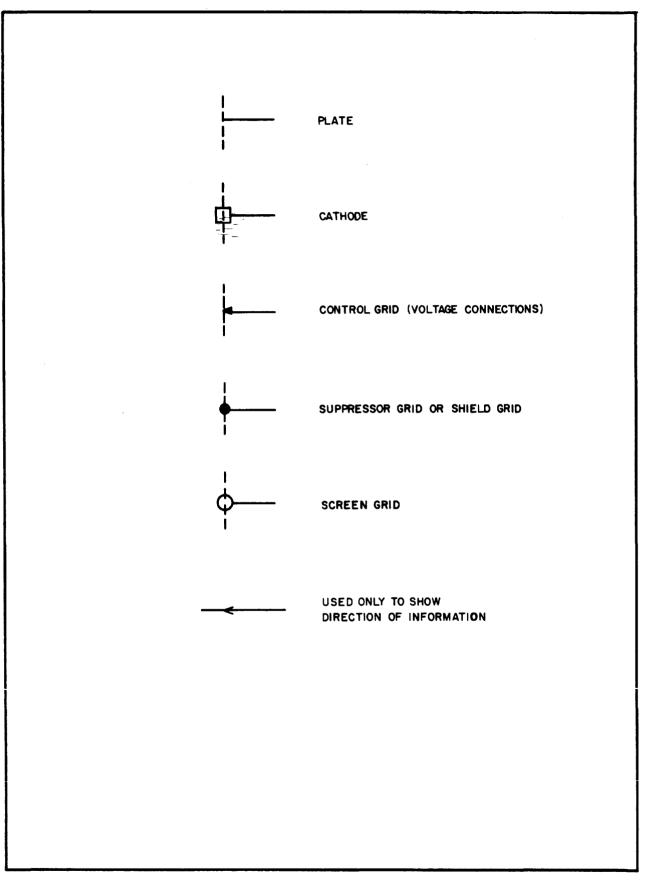

Because almost all vacuum tubes have heaters and their presence is so widely understood, it is common practice to omit the symbol for the heater wire itself when drawing a circuit diagram. This convention will be used throughout this manual. In certain tubes (used in the 604 only in the power supply) the heater itself is used as the electron emitter (cathode). No hollow sleeve cathode is used. In such instances the heater is called a filament and is always drawn on the diagram.

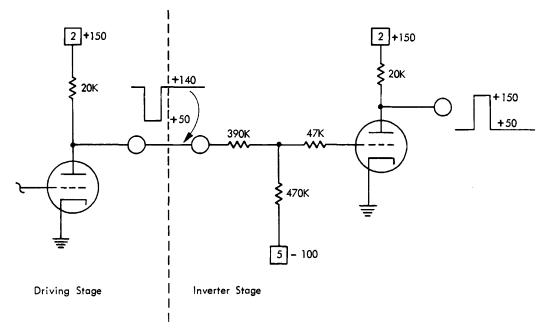

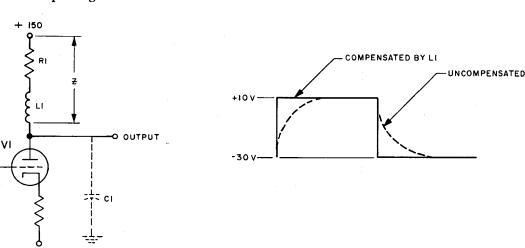

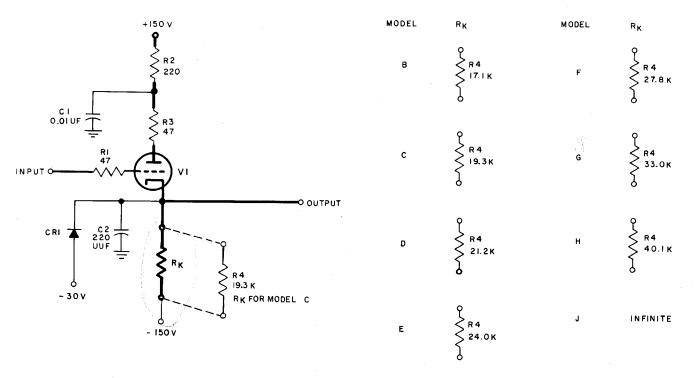

A typical and practical inverter circuit is shown in Figure 23. Three resistors have been added to the grid circuit of the theoretical stage discussed earlier. Inverter units are always driven from some other electronic source such as another inverter unit, power unit, trigger unit, etc. These units generally have a plate output which varies from about +140 volts with the tube cut off, down to +50 volts with the tube conducting. As was discussed earlier, the grid of an inverter must receive about 20 volts negative to reliably cut it off and a zero or positive condition to cause heavy electron flow. In Figure 23, the 390k and 470k resistors connected between the plate of the driving stage and a source of -100 volts acts to convert the driver plate voltage levels into a form usable at the grid of the inverter stage under discussion. Because of the electron flow from the -100 volts up through the 470k and 390k resistors and up through the 20k plate load of the driving stage, the voltage at the plate of the driving stage rests at about +140 volts with the tube cut off rather than the  $\pm 150$  volt level considered earlier. Point C, the connecting point of the three grid circuit resistors, will be found to be at about +30 volts if Ohm's law is applied to the voltage divider network. It would seem that the grid of the inverter

Figure 23. A Practical Inverter Circuit

would also be at plus 30 volts, but such is not the case so long as the cathode of the inverter tube is hot. The inverter tube grid is very close physically to the cathode. Whenever this grid goes positive with respect to the cathode, it draws from the cathode electrons which act to neutralize the expected plus potential. The grid current drawn reflects itself at point C and keeps that point also from reaching the expected +30 volts. The 47k resistor in series with the grid, as well as the high resistances of the other two grid circuit resistors, helps limit the amount of grid current actually drawn. This is important since too much grid current could melt the fine grid wires and destroy the tube. The circuits used within the 604 are so designed that no grid will ever be driven more than about one volt positive at the tube, regardless of the input signal applied to the pluggable unit pins. This potential is enough to make the tube pass the desired electrons from cathode to plate and bring the plate output down to about plus 50 volts. This is the condition of the inverter in Figure 23 when the plate of the driving stage is at its high, plus 140 volt point.

If the input to the driving stage is altered so that tube draws heavy current, the plate of the driving stage will drop to a voltage level near 40 or 50 volts. The resistance coupling network will now cause point C and the grid of the inverter stage to be at about -20 volts, cutting off current flow within the tube, and permitting the inverter plate and output point to rise to  $\pm 140$  to 150 volts (depending on the circuit connected to the plate). It can be seen that by circuits such as this, one tube can be used to control another. This method of coupling between tubes is called straight resistance or DC coupling and permits a direct current condition to be passed and held between tubes. In the example given, as long as the driving tube is conducting, the inverter tube is cut off, and vice versa, regardless of the time involved.

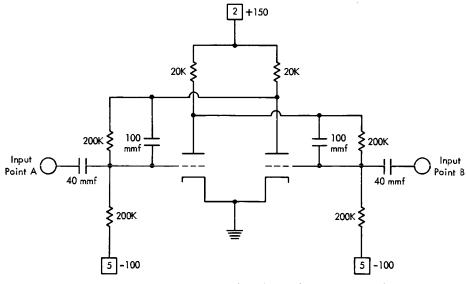

#### INVERTER CIRCUIT VARIATIONS (G AND H)

Certain variations of the basic inverter circuit will be found in a number of the pluggable unit types. These variations will be discussed separately, but they may be used in any combinations within any pluggable unit type. Each half of an IN unit may use different variations and units other than the IN type will use these same principles. A study of the unit diagrams in the Appendix will show the actual circuits used in any 604 pluggable.

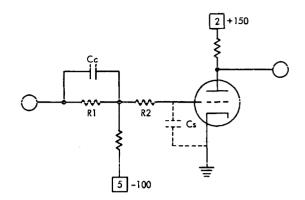

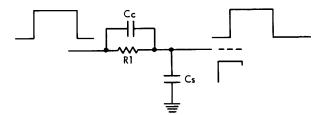

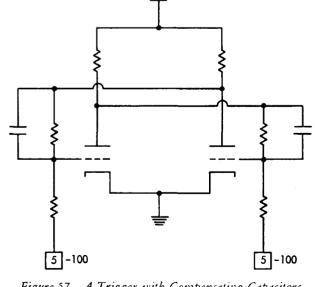

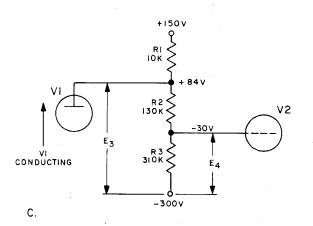

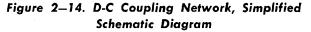

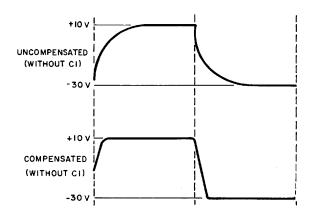

Figure 24. The Compensating Capacitor

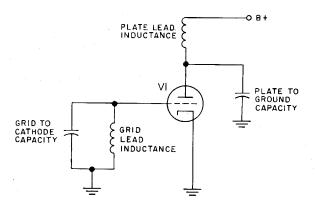

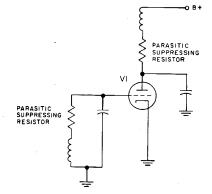

The Compensating Capacitor. An understanding of the need for the compensating capacitor, Cc in Figure 24, will require some discussion of the characteristics of a capacitor. Any two conductors that are insulated from one another form a capacitor, the symbol for which is quite representative of its construction. The closer these two conductors are to one another, and the larger their surface area, the greater their capacitive effect. A large number of free electrons can be trapped on one or the other of these conductors or a large number of electrons can be removed from one of the conductors and not permitted to return. In both of these cases, the capacitor is called "charged" meaning the electron distribution is unbalanced. Putting these electrons on a capacitor or taking them off, takes an amount of time which is directly proportional to the resistance through which the electrons have to pass to get on or off the capacitor. The actual electrical size of the capacitance directly affects the voltage (electron pressure) to which a capacitor will charge through a given resistor in a given amount of time. The practical effect of this is that a capacitor will not instantaneously change the voltage across its conductors (which are generally called plates). While acting as an open circuit for long term steady voltage conditions, the capacitor acts as a temporary short circuit for any changes in the applied voltage.

The grid and cathode of a vacuum tube and the wiring to it, being conductors insulated from one another, constitute "invisible," stray capacitance drawn in as Cs in Figure 24. Before any change in voltage can be produced between the grid and the cathode of the tube, and thus affect the cathode to plate electron flow, this capacitance must have its voltage balance altered. Any signal voltage change applied to this capacitor must come through the resistors R1 and R2. R2 is so

Figure 25. Stray Capacitance

small in comparison with R1 that it may be neglected in this phase of the circuit operation. The relevant parts of the circuit, without the compensating capacitor, are drawn in Figure 25.

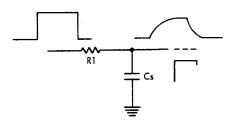

A crisp input signal is rounded over and distorted on the grid of the tube because the stray capacitance, Cs, shorts out and delays the voltage changes. The capacitor cannot rapidly change its charge through the series resistor R1. Reducing the resistance in R1 would reduce this rounding but would also disturb the steady state conditions of the circuit.

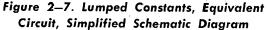

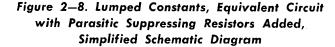

Figure 26. RC Circuit with Compensating Capacitor

Placing the compensating capacitor, Cc, in parallel with resistor R1 changes this action considerably. A capacitor of the proper size, acting like a short circuit to rapid voltage changes, can short these changes around R1 and force the stray capacitance to respond instantly so the voltage on the grid of the tube looks exactly like the applied signal. For steady state conditions no change is noticed by the circuit, the resistors alone providing the needed actions. Any 604 circuit that must have a fast response will be found to use a compensating capacitor.

The Desensitizing Filter Capacitor. The sensitivity of a circuit to short duration spikes, called noise, can be greatly reduced by effectively *increasing* the stray capacitance and eliminating the compensating capacitor. Figure 27 shows an external capacitor, Cf, connected between the grid circuit and ground. This filter or

32

Figure 27. An External Capacitor Used to Desensitize a Circuit

desensitizing capacitor shorts to ground any short, rapid changes, and delays the circuit response to longer duration impulses. Both of these actions can be useful in certain areas.

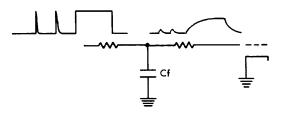

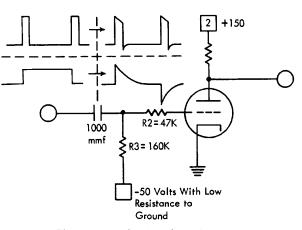

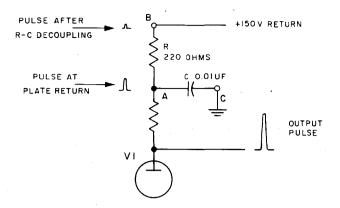

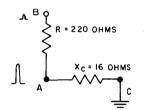

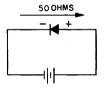

The Coupling Capacitor. Another use for a capacitor is to eliminate the direct voltage coupling between two stages while permitting any voltage changes or signals to pass through. A side result of this is that some signals can be passed through a capacitor coupling network substantially unaltered, while other signals of longer duration are converted into pulses. Both of these effects are applied in 604 circuitry.

Figure 28. The Coupling Capacitor

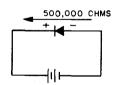

Figure 28 shows the basic capacitor coupling circuit and its effect on typical input signals. The coupling resistor has been removed and its place taken by a capacitor. The effect of this change is always to separate the DC levels of the two circuits. What it does to the signals applied depends on the type of the signal and the value of the capacitor and any resistance in series with its charge path. With the values given in the figure a voltage pulse of ten microseconds will pass through the network with very little change, while a gate of two hundred microseconds is considerably altered. The important relationships are between the time length of the signal and the time constant of the resistance-capacitance network. The time constant can be determined from a simple formula:

#### T = RC

Time Constant (in microseconds) = Resistance (in millions of ohms) times Capacitance (in micromicro-farads).

If the duration of the applied pulse in microseconds is one tenth or less of this RC product, that pulse will be passed substantially unaltered. If the applied pulse is five or more times as long as the RC product, the signal will be peaked into a curved sawtooth-like pulse with a practical width in time of about twice the RC product. In-between relationships will produce intermediate effects.

The circuit being investigated must at times be carefully studied to determine the value to use for the R in the formula. In Figure 28, the value normally used would be the 160k (.16 megohms) of R3. If the signal drives the grid into the positive area where grid current is drawn, however, the 47k resistor can be considered as being in parallel with the 160k resistor. This is because a tube, while drawing grid current, has a low resistance effectively between the grid and the cathode (on the order of one thousand ohms). It is thus possible for a circuit to have one time constant for a positive going signal and a second for a negative going signal.

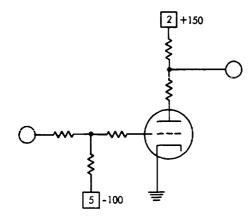

The Tapped Output. In some instances the full one hundred volt change normally produced at the plate of a 604 circuit tube is more than required. Any desired degree of signal output (generally about 2/5, or 40 volts change) can be obtained by taking the output not

Figure 29. The Tapped Output

from the plate, but instead from a tap on the plate resistor or from a connection between two series plate resistors. This is shown in Figure 29. The closer the tap is (resistance-wise) to the plate, the greater will be the output voltage change.

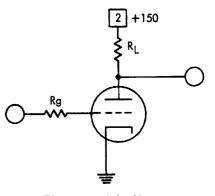

The Slave Unit. Some pluggable units have been designed to work only in parallel with other units, sharing their components, and depending on the presence of these other pluggable units for voltages, etc. These dependent units have very few of their own components and are called slave units. Figure 30 is typical.

Figure 30. The Slave Unit

The plate load resistor,  $R_L$ , and the grid current limiting resistor, Rg, may either or both be missing within the slave unit itself, but when the complete circuit is traced through the units to which a slave is connected, the expected components can be found.

To repeat an earlier statement about all the foregoing circuit arrangements, these principles and variations will be found singly and in combination in all types of units in many circuits throughout the 604.

#### USES OF THE INVERTER

There are seven general uses for inverters within the 604:

- 1. inversion

- 2. level setting

- 3. clipping and shaping

- 4. delay

- 5. isolation

- 6. OR circuit (mixing)

- 7. AND circuit (switching)

As was true with the circuit variations, these uses may be applied singly or in combinations. No other

Figure 31. Signal Inversion

type of unit is applied to so great a variety of different jobs.

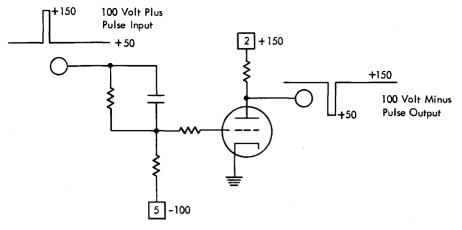

1. Signal Inversion (Figure 31). Particular types of circuits require a particular direction of signal shift to produce the desired action. A trigger may require a negative pulse to cause it to flip at a time when only a positive pulse is available. Running this pulse through an inverter converts it to the desired polarity. Inversion of a negative pulse or gate to a positive signal is also easily accomplished.

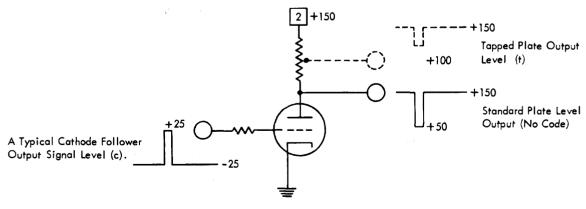

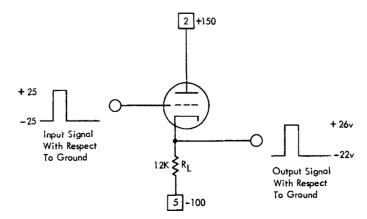

2. Level Setting (Figure 32). A minus 25 volt to plus 25 volt signal, for instance, can be converted to a +150 volt to +50 volt plate output level. In this example not only was the level changed, but the signal was also inverted and amplified in the process. The inversion can be overcome by running the new signal through a second inverter. The amplification can be neutralized by a tapped output. (If a second inverter was used to restore the original signal polarity, the tap would be on the output resistor of the second inverter.) Figure 32 shows a single, inverting level setter with the optional tapped output shown in dotted lines. Also in Figure 32 is introduced the signal level code used in the 604. Signal levels are held to a small number of possible variations which can be identified where necessary by small, parenthetical letters. A "(c)" near a wire indicates a signal level from minus 25 to plus 25, such as is obtained from the output of a Cathode Follower (to be described later). A "(t)" indicates the tapped plate output signal with a normal 50 volt shift from about +150 to +100 volts. An unlabeled line is the standard, full plate level shift of 100 volts. There is also a level used to drive a triode switch and called the triode switch level, identified as "(s)", which runs from 0 to -40 volts. The triode switch uses IN units but will be described in later pages.

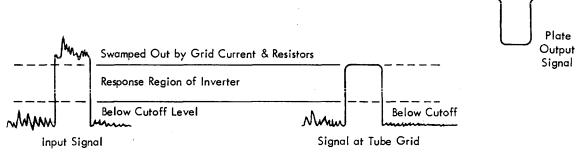

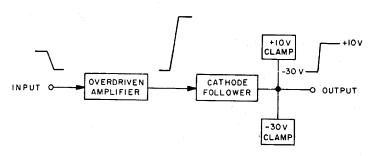

3. Clipping and Shaping (Figures 33 and 34). It takes sharp, flat, noise free signals to insure proper operation of the 604: As pulses are run throughout the machine, they may become distorted and "sloppy." This

Figure 32. Level Setting

Figure 33. Clipping and Shaping

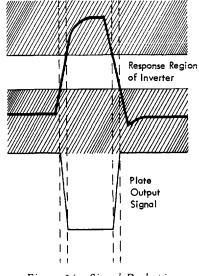

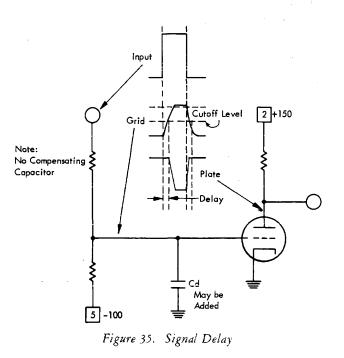

condition can be corrected by an inverter. Signals more negative than the amount needed to cut off electron flow within the tube are not reflected in the output of an inverter. At the other end, signals which try to drive the grid positive with respect to the cathode are effectively swamped by the grid current which results; the plate current levels off at a fixed point. This overdriving of the units is engineered into the 604 and clips off any roughness at the extremes of a signal. This happens almost every time a normal signal is run through a tube unit as shown in Figure 33. A similar effect results when a signal with a sloping leading or trailing edge overdrives an inverter, Figure 34. A high 4. Delay (Figure 35). An inverter unit can be used to introduce a slight amount of delay in the transmission of a pulse from one circuit to another. This delay is generally quite short, less than a microsecond, but can help stabilize an occasional circuit. This delay is a function of the coupling to the inverter unit. The compensating capacitor is left out of the circuit, which puts a slope on the leading edge of the signal. The time it takes for the tube grid to rise from a point below cut off to the point where cathode to plate electron flow begins gives the desired delay. The amount of delay can be increased somewhat by adding a small shunt capacitor, Cd in Figure 35.

Figure 34. Signal Reshaping

degree of improvement results in the rise time and fall time since only a portion of the rise and fall time produces any actively changing plate signal level. This is a very important function of inverters since sloping wave fronts will not properly operate triggers (which are the sole memory devices used in the 604).

5. Isolation. Isolation is a very important use of a tube unit. As previously mentioned, variations on the grid of a tube are reflected in the plate circuit because electrons flowing from the cathode to the plate must

Figure 36. The OR Circuit Mixing Problem

pass through the grid. There is no electron flow from plate to grid, however. Therefore, except for a small capacitative effect between the plate and grid, the grid is electrically independent of the plate. Variations on the plate have practically no effect on the grid or circuits connected to it. Some 604 circuits, such as triggers, can be flipped by stray pulse pick-up (called cross talk or noise) even when applied to their output points. To prevent this effect, the output of a trigger, for instance, will be run through a physically close inverter before a lead of any great length (and therefore liable to stray pickup) is run throughout the machine. A similar "back circuit" elimination is used in the "OR circuit mixing" to be described next.

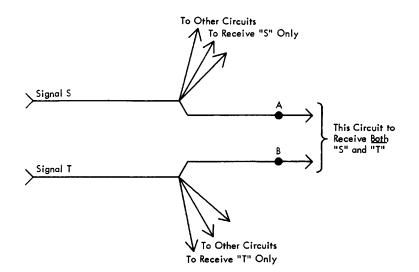

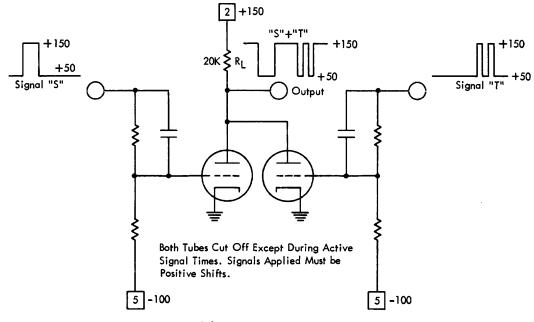

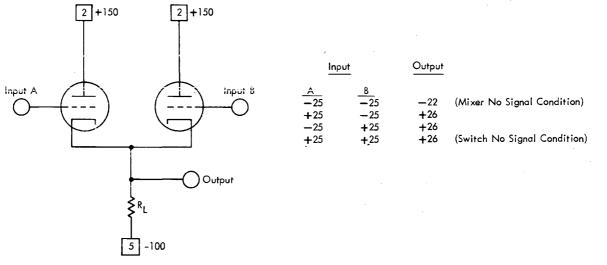

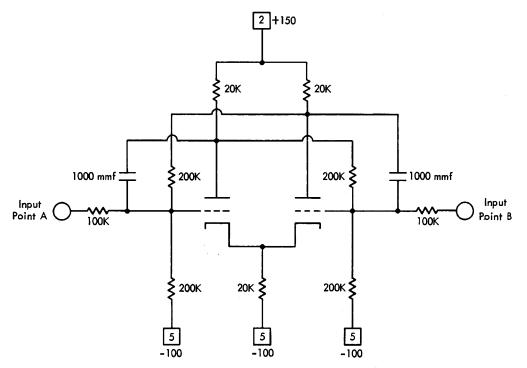

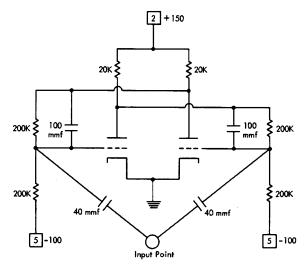

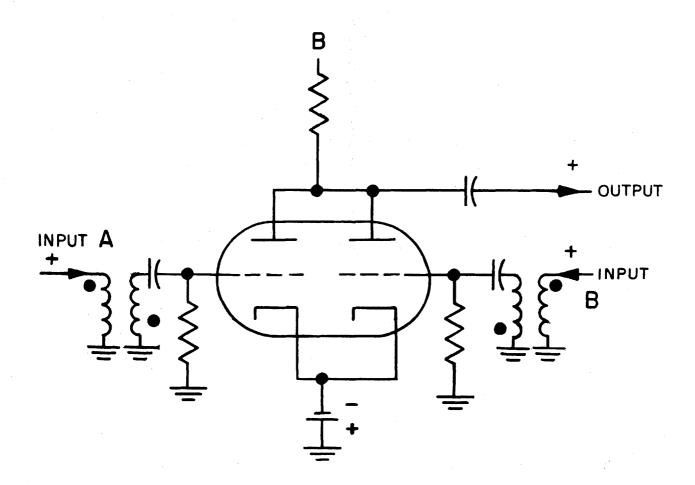

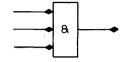

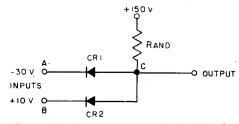

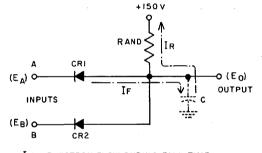

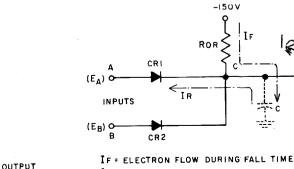

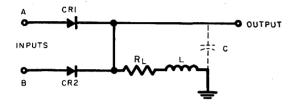

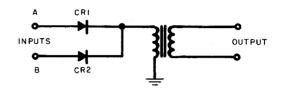

6. The Inverter OR Circuit (Mixing) (Figures 36 and 37). The problem to be solved is represented by Figure 36. Two separate signals, "S" and "T", which do not necessarily occur coincidentally in time, are used to separately control different circuits within the machine. One circuit, however, is to receive and be controlled by BOTH these signals. Merely shorting together points A and B will provide the desired S and

Figure 37. The Inverter OR Circuit (Mixer)

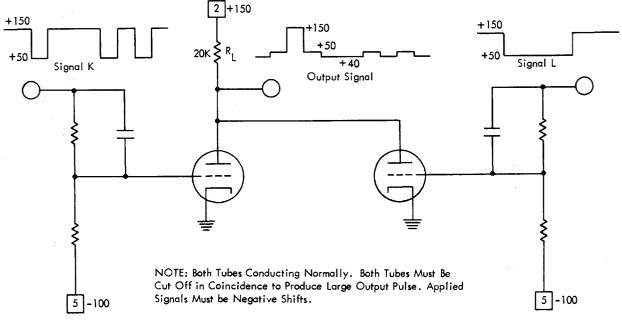

T signals to the desired circuit, but all the separate S circuits will now also receive the T signal and vice versa. A circuit is desired which will create an output whenever one signal OR another signal is applied to it without interaction between the input signals. Figure 37 shows one solution through the use of two inverter circuits with separate inputs but sharing a common plate load resistor. The values of the components and the circuits which feed this mixer (OR circuit) are chosen so both triodes are normally resting below cutoff. When signal S comes in to the left inverter, this inverter conducts and the inverted signal is developed across the plate load resistor, R<sub>L</sub>. When signal T comes in to the right inverter, the right inverter conducts and develops the inverted signal across the same plate load resistor, R<sub>L</sub>. Both input signals thus affect the output, but there is no effect upon signal S by signal T or vice versa, because signals on the plate of a tube are not reflected back to the grid.

Almost any number of tubes can be connected to share the same load resistor (so long as each of the tubes is normally cut off) thus making multiple mixing OR circuits possible. Such combinations are used in the 604.

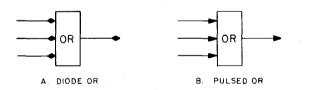

An understanding of the problem solved by an OR circuit mixer is quite important. The solution of the problem is an important application of inverter (IN) units, but other units such as diode types (DS), cathode followers (CF), and pentagrid switches (PS) can solve this same problem. These units will be described later.

By definition, an OR circuit is a mixer which allows two (or more) separate inputs, not necessarily coincident in time, to be combined on a separate output without interaction between the inputs. "This" OR "that" will produce an effect.

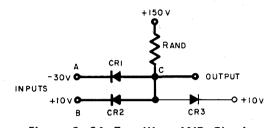

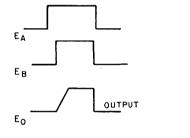

7. The Inverter AND Circuit (Switch) (Figures 38 and 39). The control of electronic pulses (allowing a pulse to reach a circuit at one time but not at another) is one of the primary design elements in the 604. In electrical IBM machines, series strings of relay points perform this control function; all relay points in the string must be closed before the circuit is completed. In the 604, electronic switches allow similar control. The definition of a switch is an electronic circuit which requires two coincident inputs to obtain an output. The logical name "AND circuit" has been applied to such a device because "this" condition AND "that" condition must be true at the same time to secure an effect.

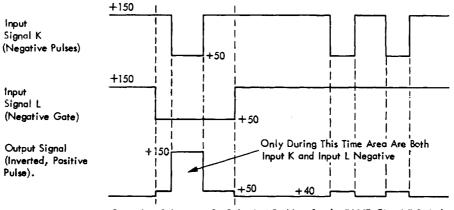

Figure 38 shows the basic electronic problem. It is desired to let only a particular negative pulse from signal "K" get to a circuit and produce an effect. The somewhat wider negative signal (a gate) shown as "L" has a time coincidence with the desired "K" pulse, but not with the undesirable pulses, and can thus be used to make this particular pulse selection possible. Figure 39 shows the Inverter Switch (AND circuit). As with the OR circuit mixer, other types of units which will be described later can also be used to accomplish the same objective.

The circuit of the Inverter Switch is identical to the Inverter Mixer. The only difference is that both sections of the Inverter Switch are driven by a normal no-signal +150 volt level and thus both triodes are conducting during no-signal time (with the Inverter Mixer, both triodes were normally cut off). We have discussed the

Control or Selection of a Pulse is a Problem for the "AND Circuit" Switch. Waveshapes Drawn are Representative of an Inverter Switch.

Figure 38. Control or Selection of a Pulse

Figure 39. The Inverter AND Circuit (Switch)

fact that one inverter triode conducting through a normal 20k plate load will reduce the potential on the plate down to about +50 volts. When a second inverter triode is connected to share the same plate load and is conditioned to conduct, a current sharing action takes place. When the second triode is told to conduct while the first triode is also conducting, only a plus 50 volt potential is available on the second plate to attract electrons. Electrons leaving the second triode cathode are thus only mildly attracted to the plate, but a few do make the trip and further lower the potential on the tied together plates of both the tubes. This reduces somewhat the electron flow in the first tube. The net effect is that the combined plates fall to about 40 volts (a drop of only 10 additional volts), and the total electron flow through the tubes divides about equally. This is the heart of the Inverter Switch action: either tube conducting alone will drop the combined plates to +50 volts, while both tubes conducting together cause only an additional ten volts of drop. This is shown in Figure 38. Such a small (10 volt) change will have no effect on following 604 circuits. When both triodes in coincidence are cut off, the plate output potential rises to +150 volts. It thus takes two coincident negative going input signals to produce any appreciable voltage level change at the output.

Since the circuits of the Inverter Switch and the Inverter Mixer are identical, examination of the preceding circuits must be made to determine the true

38 1BM 604

action. This will be found true of any circuits in which a load resistor is shared by two or more units. It should be noted that the Inverter Switch is more frequently used than the Inverter Mixer.

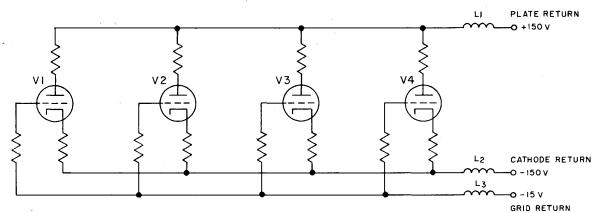

#### Power (PW) Units (G and H)

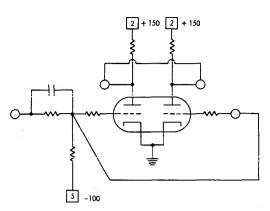

The inverter units previously discussed are designed to work with tubes capable of passing safely a current of about five milliamperes. The basic pulse amplitude of the 604 is 100 volts; and if 5 ma of current is to produce this much voltage drop, a 20k plate load resistor is required. In some instances twenty thousand ohms is more resistance than can be used for successful circuit operation. For instance, in Chapter One, Figure 5, a general layout of the machine was given. A number of entry channels were indicated as running throughout the machine. These channels feed many units in parallel, each loading the circuit to some degree. Further, the long leads of these channels have considerable capacitance between themselves and ground, and other circuits. To prevent severe distortion and delay of the voltage pulses, these conditions demand a low resistance plate load to drain the capacitive charge quickly at the end of the pulse, and a high current tube to charge the capacitance and drive the receiving unit grids sharply at the start of a pulse. A three thousand ohm plate load is indicated, but a 6J type tube could only produce a twenty to thirty volt shift across such a resistor. It is possible to connect 6J type tubes in parallel

Figure 40. A Semi-Power Arrangement Using Two Triodes in Parallel

to increase the current capacity, but this would require an excessive number of units in some cases. It is done occasionally with the two sides of one IN unit where only a moderate power increase is needed. Figure 40 shows such an arrangement. This hook-up is called a semi-power unit usage of an IN unit. Notice that *both* grids and *both* plates are connected together. Other circuits, such as switches or mixers, connect EITHER the grids OR the plates together, but these configurations are *not* for semi-power reasons.

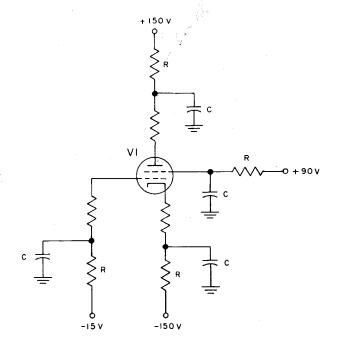

To achieve the power capabilities desired, using only one pluggable unit, a larger and different tube is used in Power Units (coded PW). One type of power unit, the PW-12, uses a 5965, which is a heavy duty dual triode. The two units are effectively in parallel as discussed above under the semi-power unit connection. The use of the larger tube type in this circuit permits a 60 volt signal (from  $\pm 150$  to  $\pm 90$  volts) to be developed across a plate load of less than one thousand ohms.

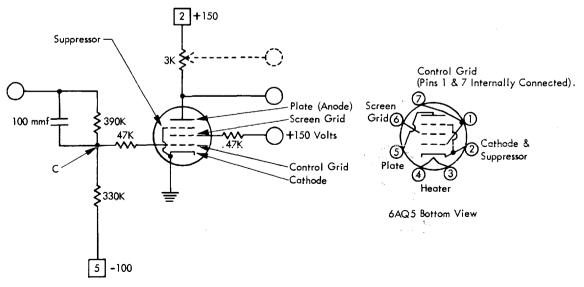

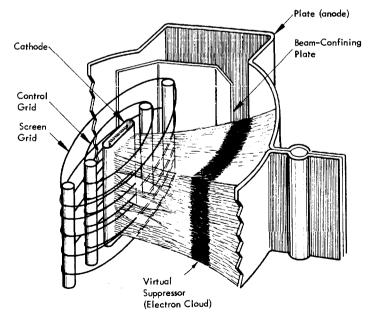

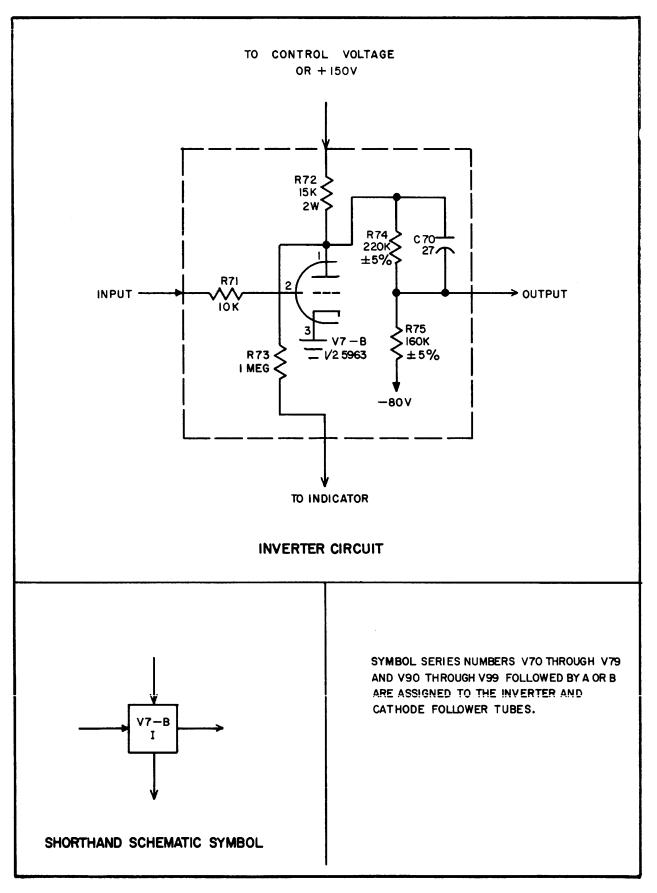

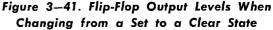

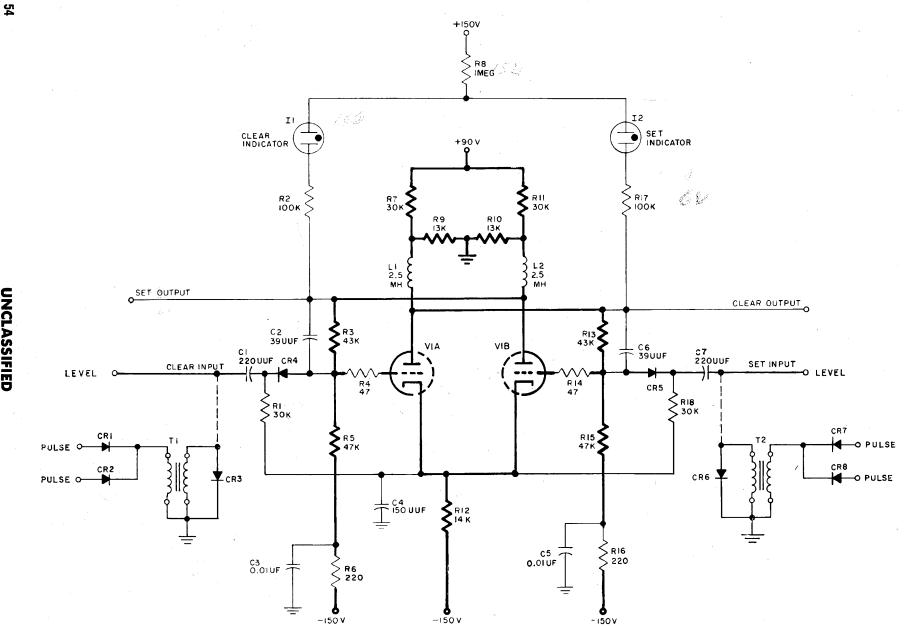

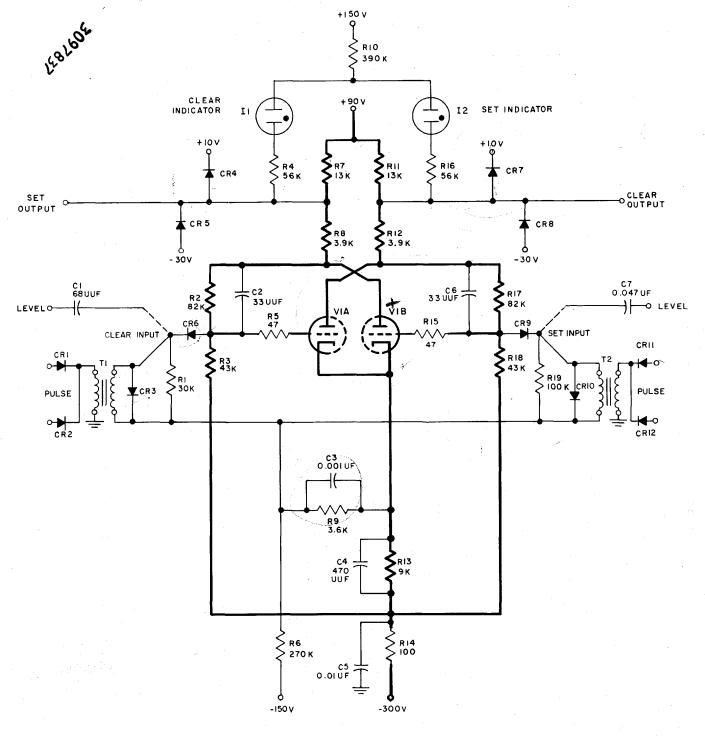

All other PW units in the 604 use a type 6AQ5 beam power tube. The five electronic elements which make up the construction of this tube form the cathode to plate electron flow into a heavy stream or beam. A typical diagram for this power unit, showing the symbol for the tube used, is given in Figure 41.

The larger physical size of the elements within the 6AQ5 tube and the addition of the screen grid between the control grid and the plate both make this tube capable of easily passing the 15 to 30 milliamperes required by certain 604 circuits.

The screen grid in the 6AQ5 overcomes one of the limitations of the triode. As a triode passes electrons to the plate, the plus potential of the plate is somewhat neutralized. The plate potential drops, and it is this drop which constitutes the signal output. However, the lower plate potential does not attract electrons from the cathode with as much force nor in as great a number as would have been true had the plate volage not dropped. In short, the plate potential *must* drop to produce a signal but it should *not* drop if maximum electron flow is to be obtained. These mutually incompatible requirements are resolved by the addition of the screen grid between the grid and the plate.

The screen grid is connected through a 470 ohm limiting resistor to  $\pm$ 150 volts. With such a low value of series resistance, very little voltage variation is

Figure 41. A Power Unit Using a 6AQ5

noticed at the screen regardless of the current drawn by it. Even 10 ma of screen current (which is excessive for a 6AQ5) would lower the screen voltage only 4.7 volts to about +145. The screen potential thus remains quite stable despite the amount of current flow through the tube. Since the screen is located physically nearer to the cathode than is the plate, the screen exercises a greater attractive force for electrons boiled off the cathode than does the plate. In fact, the potential on the plate is practically unfelt at the cathode, due to the screening action of the screen grid. When the control grid permits them to do so, the electrons from the cathode stream toward the attractiveness of the screen grid. The screen grid is made of turns of fine wire with wide spaces between the turns. By the time the electrons get near the screen grid wires, they are traveling so fast that they are unable to turn and actually land on the wires. Instead, most of them pass right by the screen and continue going until they strike the plate. These electrons trying to flow through the 3,000 ohm plate load resistor cause the plate potential to drop and thus develop the output signal, but the lowered plate potential does not reduce the number of electrons striking the plate. The net result is that an output signal level change from +150 to +40 volts is produced across a 3000 ohm plate resistor. This signal is too large for some applications, and as a result some power units use a plate resistor with an adjustable tap to permit any desired signal amplitude to be obtained. This tap must be adjusted any time a tube is replaced in such a unit to insure specified output (generally a fifty volt signal). Figure 41 shows this tapped output in dotted lines.

The suppressor grid shown between the screen grid and the plate of Figure 41 prevents electrons from returning to the screen grid from the plate under certain conditions of operation. With the power tube passing a heavy electron flow, the positive potential on the plate may only be thirty to forty volts due to the voltage drop through the plate load resistor. As the electrons are thrown at the plate by the action of the screen, a chipping effect takes place. Secondary electrons are knocked off the plate and could readily be attracted to the screen grid, since under these conditions the screen still has a plus potential of nearly 150 volts on it while the plate is only at 30 volts or so. Any electron flow from plate to screen would decrease the effective plate current and increase the screen current; both effects are undesirable. This is prevented by the suppressor which is electrically connected to the cathode within the tube and thus presents a repelling, negative barrier to any slow moving electrons released by the plate. The higher velocity electrons traveling from the cathode to the plate are only sightly affected. Having five active elements within its glass envelope, such a tube is called a pentode (penta indicating five). With some types of tube construction the suppressor grid is not physically included, the effect being obtained from a repelling

Figure 42. A Beam Power Pentode

cloud of electrons produced by the beaming of the electrons toward the plate. Figure 42. In this case the beam confining plates are the fifth tube element. They are generally represented by the tube symbol in the same way an actual suppressor grid would be drawn and as indicated by Figure 41.

The pentode tubes used by the 604 require a potential of nearly -20 volts on the control grid to cut off most of the electron flow. This is twice or more than required by the dual triode 6J type. The values of the resistors in the power unit grid circuit are different from those generally found in inverter units in order to produce a voltage swing from -32 to +14 at point C, Figure 41. As with the inverter unit, if the tube cathode is hot, the drawing of grid current will keep the plus level at something less than +1 volt.

In summary, type PW units are high power inverter units using pentode tubes or, in the PW 12, a heavy duty dual triode. The PW units are used when a number of tubes are to be driven in parallel or when a circuit wire must physically run for a considerable distance.

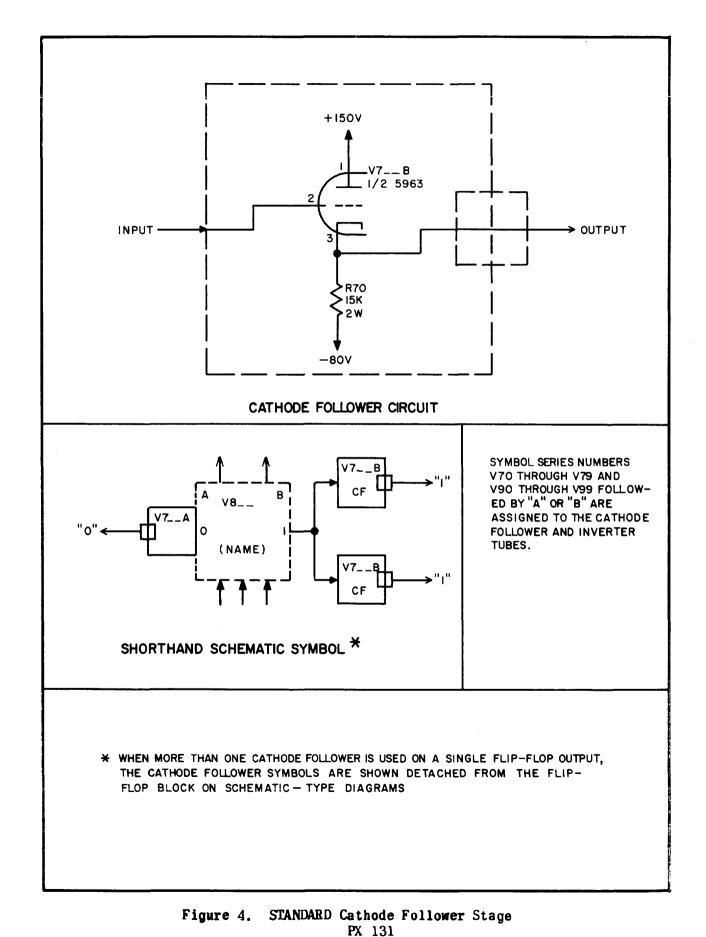

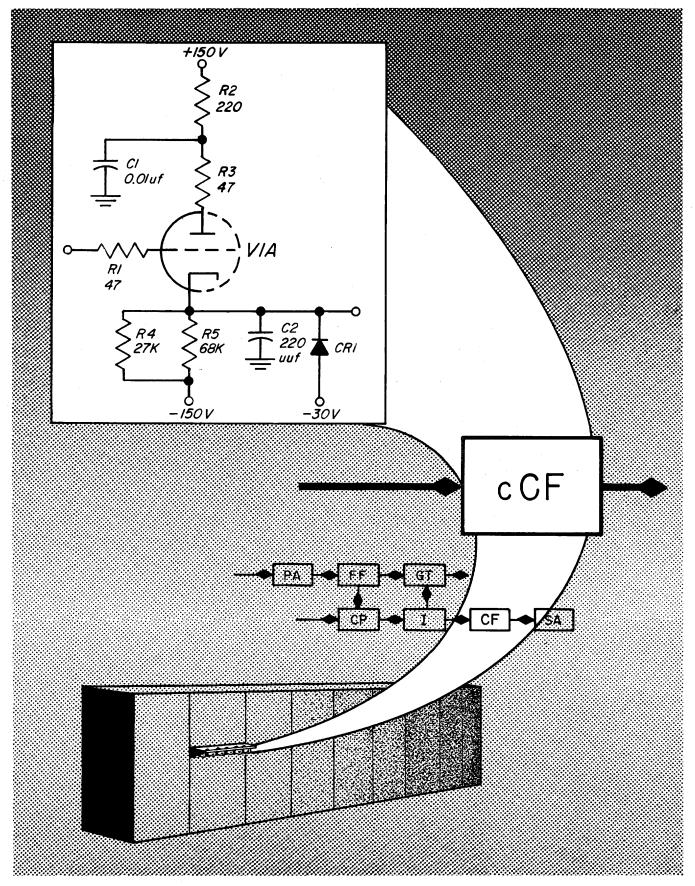

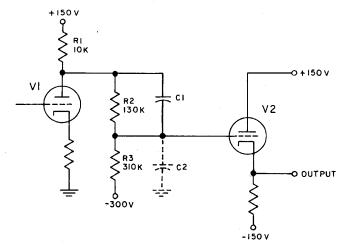

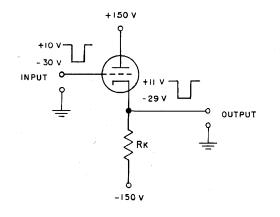

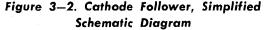

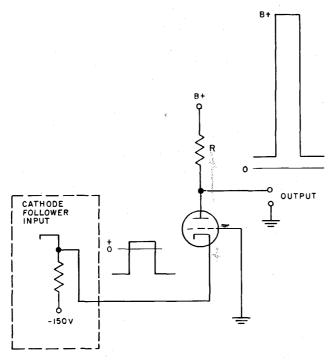

#### Cathode Follower (CF) Units (H suffix only)

The Cathode Follower is a type of circuit which is in certain ways even better than a Power Unit for driving many parallel circuits or long lead length circuits. It is extensively used in the H suffix machine but not at all in the G and earlier.

Throughout this discussion of the 604 electronic circuits, the term "voltage on the grid with respect to the cathode" has been frequently used. It is this difference of potential which controls the electron flow within a tube. The voltage on the plate with respect to the cathode also has an effect on the cathode to plate

electron flow, but a relatively weaker on. In circuits discussed up to now the tubes had their cathodes connected directly to ground and any change in voltage on the grid was totally reflected as a change in grid to cathode potential. In the cathode follower this is not the case. Figure 43 shows that a resistor has been connected between the cathode and a point with a potential 100 volts below ground (that is, 100 volts minus). The plate of the tube is now connected directly to +150volts. In effect, the plate load resistor of the inverter type unit has been shifted down through the tube to the cathode circuit. With this arrangement, any change in electron flow through the tube directly affects the potential on the cathode with respect to ground. It is this change in cathode potential which constitutes the output signal, just as the plate level change in inverters, power units, etc., makes up their output. An important result of this shifting cathode potential is that the grid to cathode potential is changed every time the cathode level shifts, and the cathode potential shifts every time the grid potential is changed. This interacting effect is the heart of cathode follower operations.

Unlike other unit types of the 604, cathode followers are designed so they never cut off, nor are they driven into the grid current region. Electron flow through the tube is always present. As the grid moves toward a more positive potential, the electron flow through the tube increases, more electrons are removed from the cathode, and the cathode becomes less negative (more positive). If the grid is shifted in a negative direction, the electron flow through the tube is reduced; this reduces the electron flow through the load resistor,  $R_{L}$ , and as a result the cathode moves nearer to -100 volts. That is, the cathode also shifts in a negative direction. This means there is no inversion of the signal through

Figure 43. A Basic Cathode Follower Showing the Characteristic Absence of Signal Inversion

a cathode follower. At times this is an advantage, at other times not, but it is an invariable fact in any event.

A type 5965 tube is generally used in 604 cathode follower units. This tube will cut off when the voltage on the grid with respect to the cathode is more than five volts negative, and it will draw grid current whenever the grid goes positive with respect to the cathode. The normal signal applied to the grid itself of a 604 cathode follower is from -25 volts to +25 volts with respect to ground, and yet the statement was made, and is true, that the cathode follower tube is never driven either to cut off nor into the region of grid current flow. The answer to this seeming contradiction lies in the fact that the cathode *follows* the grid, always staying slightly more positive than the grid, and always staying within zero to five volts of the grid potential. This of course means the signal output voltage from the cathode can never be greater than the signal applied to the grid. There is actually a slight signal voltage loss through a cathode follower, but there is a power (current) gain which makes the circuit useful.

The reason for the cathode's staying within a few volts of the grid can be seen by considering the circuit of Figure 43. If the -25 volt signal on the grid of the tube did manage to cut off cathode to plate electron flow, there would be no electron flow through the load resistor, R<sub>L</sub>, and the potential on the cathode would then drop to -100 volts (75 volts more negative than the grid). Put another way, the grid would be 75 volts more *positive* than the cathode. This would demand a heavy electron flow through the tube and would cause the cathode to move in a plus direction. But if the cathode goes more than five volts positive *with respect* to the grid, the tube electron flow will be cut off (since this is the same to the tube as having its grid five volts negative with respect to its cathode). If the electron flow is stopped, we are back to the starting point of our discussion. Neither of these extremes happens, of course. Instead, for any given input signal the cathode instantly shifts to a balance point that will make the grid to cathode voltage remain within the operating range of the tube.

In the cathode follower circuit a change in the cathode potential has as much effect on the electron flow through the tube as a change in grid potential. This introduces the second important point about a cathode follower, the "stiffness" of its output signal. A cathode follower has a low output impedance, which simply means that any stray signal which may happen to be picked up by a circuit connected to the cathode output is effectively swamped or balanced out. This fact made it possible in the 604H suffix to eliminate the shielded cables found in earlier machine to prevent trouble from stray pick-up (cross talk) on the long entry and exit channels that run throughout the machine. Plain wires and cathode followers are used in the H suffix where power units, inverters, and braid shielded cables were formerly needed.

The reason for the output circuit "stiffness" of a cathode follower can be seen by imagining a stray picked up signal that tries to drive the cathode negative. This has the same effect within the tube as making the grid more positive. This increases electron flow through the tube and tries to make the cathode go in a positive direction, instantaneously neutralizing to a very large degree the effect of the initial stray, negative signal applied to the cathode. A stray positive signal produces a similar effect in reverse. We have, in a manner of speaking, provided electronic shielding to the output circuits.

In summary, a cathode follower:

1. Does not invert the input signal.

2. Gives out slightly less signal voltage than is applied to the grid.

3. Gives a gain in signal power through heavier electron flow.

4. Has a stiff (low impedance) output.

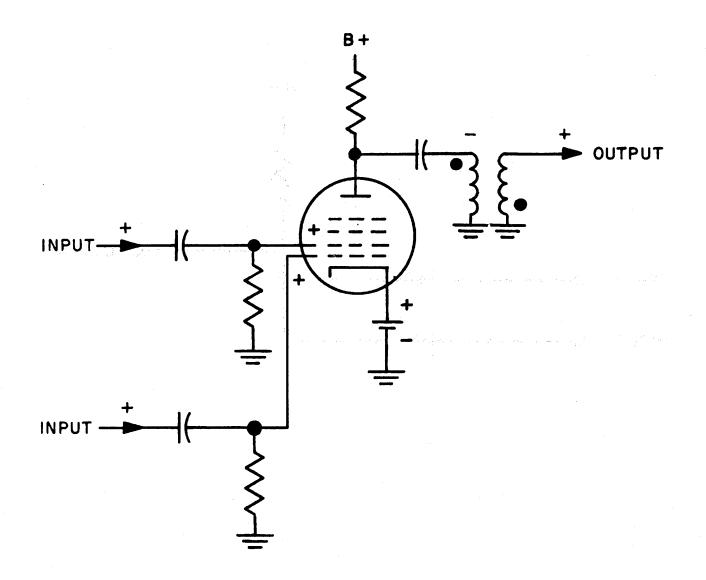

### CATHODE FOLLOWER SWITCHES AND MIXERS (FIGURE 44)

As was true with two inverters sharing a common load resistor, two cathode followers sharing a common load resistor can be used either to combine signals (the OR circuit mixer) or to control pulses (the AND circuit switch). Figure 44 shows the basic circuit for both these logical functions. As was true with the inverter circuits, the polarity of the input signals makes the difference. It is as a switch (AND circuit) that the 604 generally uses this arrangement.

Whichever tube has the more positive signal input to its grid controls the output at the cathodes. If the no signal point of both grids is -25 volts, with respect to ground, the combined cathode output will be near -22 volts. If input A is shifted to +25 volts, the left cathode will rise to about +26 volts and draw the right cathode up with it. With the right cathode at this +26volt level and the right grid still at -25 volts with respect to ground, the right tube is completely cut off

Figure 44. The Cathode Follower Switch Circuit

and no longer acting as a cathode follower. The left tube is thus controlling the output since it has the more positive grid. Returning input A to -25 volts and raising input B to +25 volts produces the same type of action. A plus input on either grid will thus produce an output. There is no interaction between input circuits, and thus the conditions required for an OR circuit mixer have been met.

When used as an AND circuit switch, a resting nosignal condition of +25 volts is on both grids. As long as either grid is positive, there will be no output variation. Only when both grids go minus at the same time

Note: Portion shown shaded (where grid goes plus with respect to cathode) will, if cathode is hot, be swamped due to grid current flow.

Figure 45. The Basic Triode Switch Unit

will the cathode level drop and produce an output signal. This meets the requirements of a switch, a device which requires two coincident inputs to secure an output signal. In this case both the input signals and the resultant output are negative shifts. These actions are summarized in the chart of Figure 44.

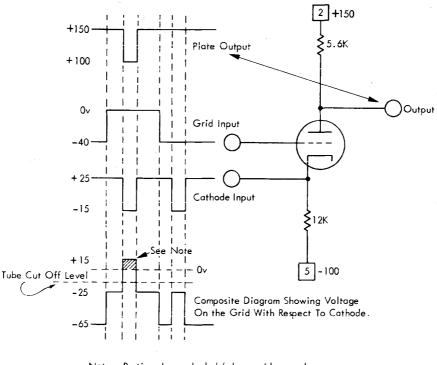

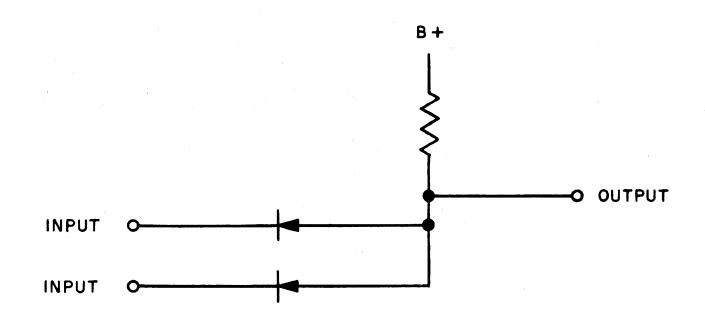

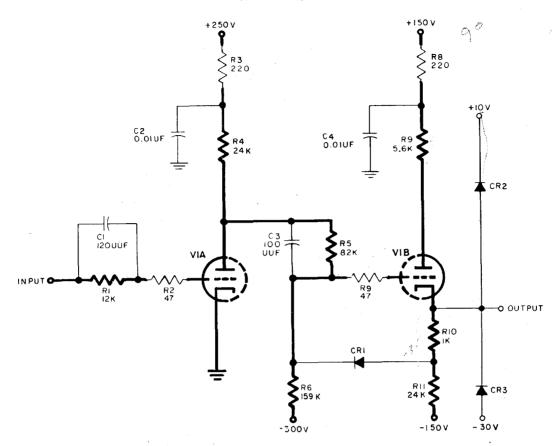

#### The Triode Switch (H suffix only)

The Triode Switch uses an inverter, IN type unit, but involves some of the principles discussed under the cathode follower. A triode switch has a resistor in both the cathode lead and the plate lead. Input signals are applied to the grid and across the cathode resistor, with the output taken from the plate of the tube, as shown in Figure 45.

Once again it must be emphasized that it is the voltage on the grid *with respect to the cathode* that controls the electron flow through a tube. The grid of a triode switch is driven over a range of -40 to 0 volts with respect to ground. The cathode is driven from +25.to -15 volts, again with respect to ground. Translating these values into the important grid to cathode relationship shows that the grid varies from -65 to +15 volts with respect to the cathode. This is shown by the bottom graph on Figure 45. Any time the grid is more than five to ten volts negative with respect to the cathode, the tube current is cut off. As a result, only when the grid is at the zero volt level with respect to ground AND the cathode is at the -15 volt level with respect to ground, can cathode to plate electron flow take place. Only at this time is the tube not cut off. We thus have the requirement of a switch: it takes two coincident inputs to secure an output shift. With the triode switch, one plus shifting signal is used on the grid and one negative shifting signal on the cathode to secure a 50 volt negative shift in plate output during coincident time.

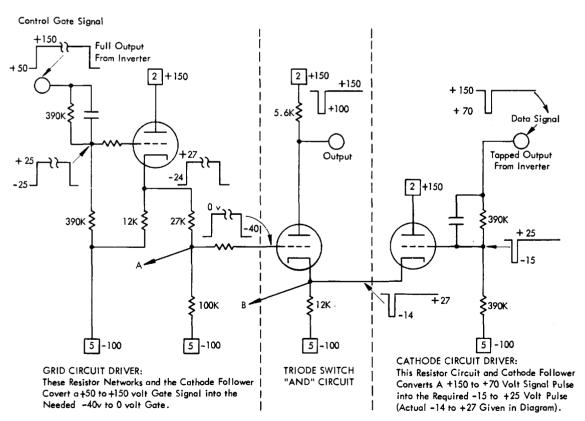

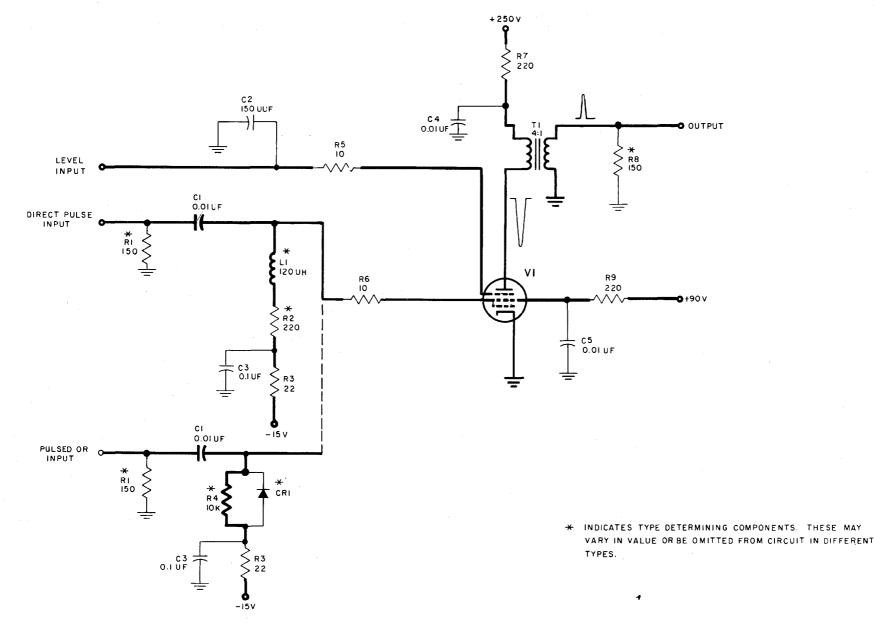

Both inputs to a triode switch generally come from cathode followers. The grid signal level (from -40 to 0) is voltage-wise obtained most easily from a cathode follower, and the cathode signal input (+25 to -15) must be from a stiff, low impedance source ideally supplied by a cathode follower. The particular voltage levels needed are secured from the proper selection of resistor values in the cathode follower driver circuits. A typical diagram is shown in Figure 46.

Figure 46. The Practical Triode Switch and Driver Circuits as Used in the 604H Column Shift Unit

The illustration shows the actual components used in the 604H Column Shift unit which makes the major use of Triode Switches. The Control Gate Input at the upper left of the diagram has its level changed by the resistor net feeding the grid of the cathode follower driver. A resistance network in the cathode circuit converts the Control Gate into the necessary voltage levels for application to the grid of the triode switch.

The Data or Information Signal entering at the upper right of the diagram also has its voltage level changed by a resistance circuit before being applied to the grid of the cathode follower driver. This tube drives the cathode circuit of the triode switch and provides the needed second input at the proper amplitude and level.

The Column Shift Unit of the 604H uses sixty-three triode switches, but this does not mean that individual driver tubes are needed for each switch tube. Figure 46 shows two leads, A and B, which each control five or more separate triode switch tubes. The total number of tubes is thus less than might at first glance be expected, and since two triode switches are available in one pluggable unit, the space required by the 604H Column Shift circuits is comparatively small.

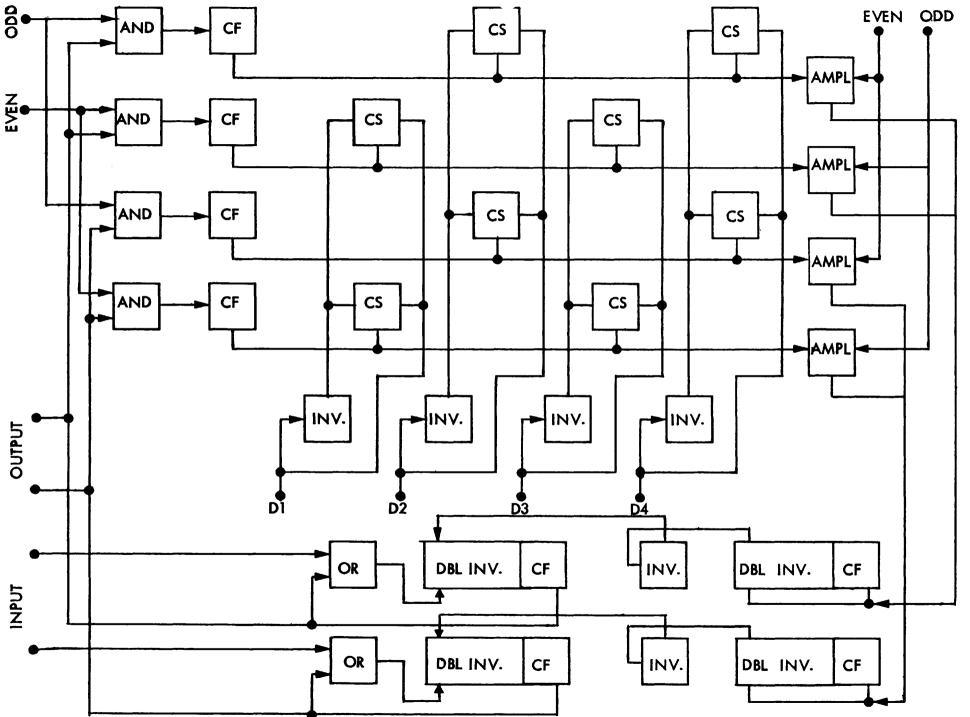

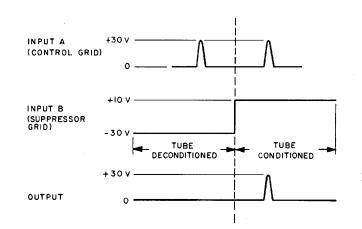

#### The Pentagrid Switch (PS) Unit (G and H)

The Pentagrid Switch unit uses a special, multielement tube in a circuit specifically designed for switching applications. In machines prior to the H suffix, 63 of them were used in the column shift unit alone, as well as for numerous applications in other areas. H suffix machines use fewer of these units, but their application is still extensive.

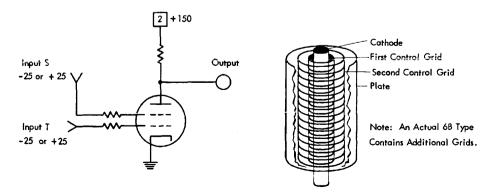

Figure 47 shows the basic elements of a Pentagrid Switch unit. An electron leaving the cathode must pass through two grids, one after the other, before reaching the plate. Either one of these grids, if sufficiently negative, can repel the electrons and cut off the cathode to plate electron flow. Both grids must be at their high, or plus level at the same time to permit electrons to reach the plate and produce a negative output signal shift. It thus takes two coincident conditions to produce an output shift, meeting the requirements of a switch unit. As is true of tube circuits using grid input and plate output, the signal is inverted in passing through the unit.

Pentagrid switch units use the IBM type class 6B tube; the commercial 6BE6 was the basis for its design. Special industrial tubes, such as the 1680 or 5915A, are actually used in the 604. Different type numbers are used from time to time as engineering designs or finds improved performance possibilities. A -6 volt potential on either control grid with respect to the cathode will cut off electron flow to the plate.

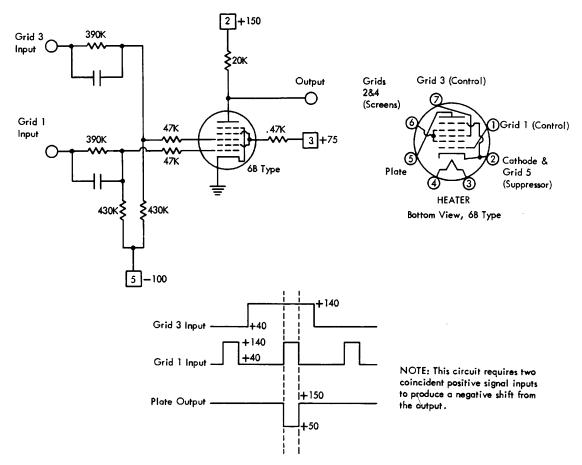

Figure 48 shows an actual PS unit circuit and represents the 6B tube as it really is. There are not just two, but five grids within the tube (thus the name, *pentagrid*), numbered from one to five as they are located in the electron stream from cathode to plate. Grids 1 and 3 are the control grids. Grids 2 and 4, called screen grids, are internally tied together and connected through an external 470 ohm resistor to  $\pm 75$  volts. These two grids accelerate the electrons on their trip from cathode to plate (which of necessity is somewhat longer than that found in triode tubes). They also act as shield screens to reduce interaction and cross talk between the control grids and to make the cathode to plate electron flow relatively independent of plate potential. Grid number five is called the suppressor and is internally connected to the cathode. Its function is to repel back to the plate any slow-moving secondary electrons which are chipped off the plate by the high velocity cathode to plate elec-

Figure 47. The Basic Circuit of the Pentagrid Switch Unit and a Cutaway View of a Simplified Tube for Use in the Circuit

trons, as was discussed under "Power Units." The large number of grids and the resultant close spacing between the elements makes this tube more liable than other types to develop internal shorts. For instance, the spacing between the cathode and the number one control grid is about .015 inch. A small flake of oxide material from the cathode can cause intermittent or permanent shorts between the cathode and this grid. Where a number of these tubes are connected in parallel (as in the G suffix column shift) such shorts can appear to be trouble in units other than the one actually at fault; knowing this can help trouble analysis.

In practice, the signals applied to the input points of the unit shown in Figure 48 vary from a down level of +40 volts to an up level of +140 volts. The resistors in the grid circuits will convert these levels to about -25 to +25 volts at the grids themselves. The drawing of grid current will generally prevent the up level from going much above +1 volt *at the grids*. However, if grid number 1 has cut off electron flow through the tube, there will be no electrons around for grid number three to draw. Under these conditions grid three can go to +25 volts if its input signal is at the high level. If the cut off voltage on the number one grid should now be shifted and permit electrons to flow, the number three grid would have electrons to draw and would drop to the one volt point. The effect of this 24 volt change in grid number three potential can be noticed on some scope pictures, especially where slave units are involved. While this effect is considered in machine design, the high values of the resistors used in the grid circuit prevent most of this shift from being reflected back to the input point and driving tube.

#### VARIATIONS IN PENTAGRID SWITCH UNIT CIRCUITS

There are thirty different types of PS units used in the 604 series of machines. The basic variations to be found in the plate circuit or in the grid circuits of PS units are the same as those discussed under Inverter Units:

1. The compensating capacitor to prevent signal distortion.

Figure 48. A Practical Pentagrid Switch Circuit Showing All Five Grids and the Base Connections for IBM 6B Class of Tubes

2. The grid to ground shunt capacitor to desensitize that input and swamp out noise.

3. The coupling capacitor to separate the AC component from the DC and to convert long duration gates into short peaked pulses.

4. The tapped output to reduce the amount of output signal shift taken from the plate circuit.

5. The slave unit to work in conjunction with other units to save components.

There is one unique variation for the PS unit; connecting the two control grids together produces a unit having the ability to amplify rather greatly any variations in input level. Very small changes on the grid (s) produce large changes in the output level. This principle will be found used in the regulating portion of the reset circuits to be described later.

In several instances in the 604, the PS unit will be found used as an OR circuit mixer. In these cases the normal resting point of the input signals will be at the up level ( $\pm$ 150 volts). The tube will normally be in conduction. Dropping the signal level to one grid OR the other will shut off cathode to plate electron flow and produce a positive output shift from the plate. Such usage is rare, but will be found (in the Column Shift Control circuits, for instance).

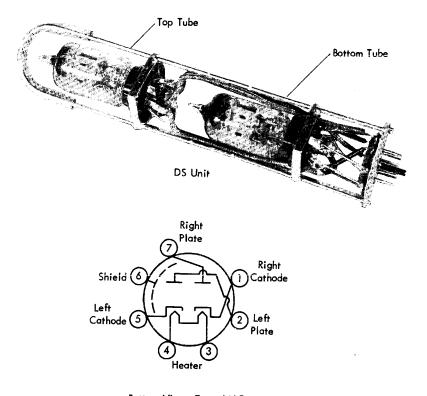

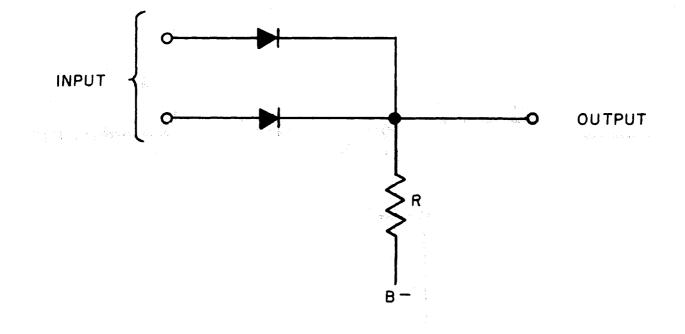

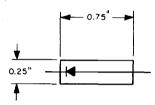

#### The Diode Switch (DS) Unit (H suffix only)

The simplest and smallest per circuit AND/OR device used in the 604 is the DS unit using two 6AL5 dual diode tubes mounted in one pluggable unit. Figure 49 shows the small physical size of these tubes and the small number of components needed. There are four tube sections within such a pluggable unit. To permit specific identification, this makes necessary the addition to the panel location code of the letter "T" for top tube and "B" for bottom tube. When used with the already discussed subscript 1 for the left tube section and 2 for the right, this will provide the needed exactness. 3-8EB<sub>1</sub> would indicate a diode section in panel 3, row 8, column E, bottom tube, left half.

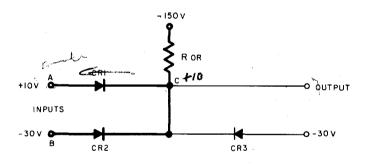

A diode will permit electrons to flow only from its cathode to its plate. This electron flow will only take place within the diode if the plate is more positive than the cathode. The Diode Switch (which can also be used as a mixer) makes use of this fact. When the diode is

Bottom View, Type 6AL5 Figure 49. A Diode Switch Pluggable Unit and the Base Diagram for Type 6AL5 Tubes

passing electrons to the more positive plate, the tube acts much like a short circuit (the actual conducting resistance of a 6AL5 is in the range of 200 to 1,000 ohms, depending on voltage conditions). The tube acts like and is an open circuit when the plate is more negative than the cathode.

A cathode follower signal shift from -25 to +25volts is generally used to drive a DS unit, though inverters, pentagrid switches, or power units can also provide the needed drive. There is no amplification of any kind in a diode, and as a result it will load (draw electrons) from any circuit feeding it. Because of the sensitivity of trigger units to loading, they are not generally connected directly to Diode Switches. The operation of triggers will be covered later.

The input signals to a DS unit can be applied either to the cathodes or the plates; these options will be discussed separately.

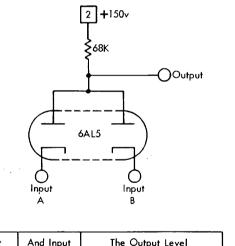

#### CATHODE INPUT

With the circuit of Figure 50, the two plates share a common 68k load resistor which runs to the +150

Г

volt supply. Input signals are applied to the separate cathodes. Whenever a cathode is more negative than its plate, that diode will act as a very low resistance and draw the plate down to within a volt or so of the cathode level. The plate of the second diode (sharing the same load resistor) will also be pulled to the same lowered level. If this makes the second plate more negative than its associated cathode, electron flow through the second diode will be stopped. Whichever cathode is most negative will therefore control the output level and stop electron flow in the other diode (or diodes if more than two are sharing the same load resistor). If the cathodes of the diodes have the exact same potential, there will be a sharing of electron flow and the plates will approach closely the cathode level. The chart in Figure 50 shows all the conditions possible when cathode level signals are used to feed such a circuit. While OR circuit usage is possible, within the 604 this circuit is used exclusively as an AND switch. The resting point for both cathodes is at -25 volts; both input signals must shift to the +25 volt level to permit the output point to rise (two coincident inputs to get an output signal).

| If Input<br>A is: | And Input<br>B is: | The Output Level<br>Will Be About:                       |                                    |

|-------------------|--------------------|----------------------------------------------------------|------------------------------------|

| + 25 v            | + 25 v             | + 25.5v (Both Tubes Share)<br>- 24v (Left Tube Conducts) |                                    |

| - 25 v            | + 25 v             |                                                          |                                    |

| + 25v             | — 25v              | -24v (Right Tube Conducts)                               |                                    |

| - 25 v            | - 25 v             | — 24.5v (Both Tubes Share)                               | AND Circuit Starting<br>Conditions |

NOTE: The output level will be about equal to the voltage at the most negative (or least positive) cathode. This circuit is used in the 604H as an AND circuit switch.

Figure 50. A Diode Switch with Cathode Input

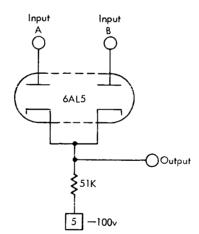

#### PLATE INPUT

With the plate input arrangement, the cathodes are connected to share a common, 51k load resistor which returns to the -100 volt supply. This introduces a form of cathode follower action. The cathodes will try to rise to the most positive plate. If one of the plates is more positive than the other, this plate will draw both cathodes up to within about a volt of itself. The second cathode will thus be more positive than its associated plate and the electron flow through this second section will cease. If both plates are at the same potential, each tube will pass a share of the total electrons. This arrangement is used in the 604 as an OR circuit mixer by placing the diode plates at a no-signal level of -25volts. The cathode output will rest at a slightly more negative potential (near -25.5 volts). If one of the plates should be raised to +25 volts, the cathode line will be pulled up also. One input OR another input will thus produce an output. Since electron flow through the non-active diode(s) ceases, there is no interaction be tween inputs. One application in the 604 H True-Compliment Trigger Control circuit has five plate input diodes sharing a common load resistor, making it a five channel mixer. The chart of Figure 51 shows the possible voltage output conditions when cathode level inputs are applied to the plates.

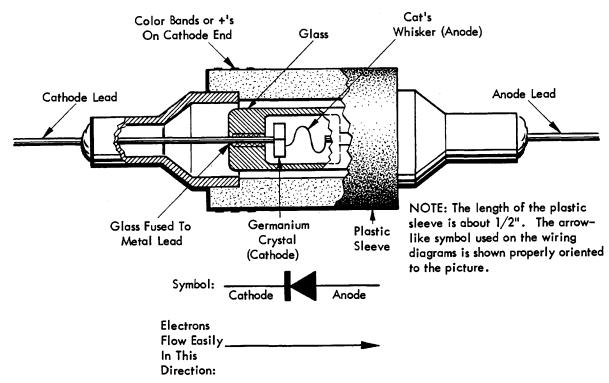

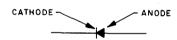

#### Germanium Crystal Diodes and Selenium Rectifiers (G and H)

Germanium crystal diodes and selenium rectifiers act much-like the tube diodes in that they permit electrons to flow readily in one direction but not in the other. These semi-conductors have a very low forward resistance, but unlike vacuum tube diodes they do leak electrons in the back direction. This limits their use in certain applications. Crystal diodes are very small, have very little stray shunt capacitance, and require no cathode heating. They can readily be used in switching circuits, but the greater cost and the ease with which they can be destroyed by even momentary overload has limited their use in the 604 to a few applications where space is a factor.

The construction of a typical germanium diode and the diagram symbol for it is shown in Figure 52. Electrons flow readily from the germanium block to the metal "cat's whisker", but with great difficulty in

| If Input<br>A is: | lf Input<br>B is: | The Output Level<br>Will Be About: |                      |

|-------------------|-------------------|------------------------------------|----------------------|

| — 25 v            | -25 v             | -25.5 v(Both Tubes Share )         | -OR Circuit Starting |

| <u>-25 v</u>      | +25 v             | +24 v (Right Tube Conducts)        | Conditions           |

| + 25 v            | -25 v             | +24 v (Left Tube Conducts)         |                      |

| +25 v             | +25 v             | +24.5 v (Both Tubes Share)         |                      |

NOTE: The most positive plate will set the output level. This circuit is used in the 604H as an OR circuit mixer.

Figure 51. A Diode Unit with Plate Input

Figure 52. An Enlarged Diagram of a Germanium Diode Showing Construction

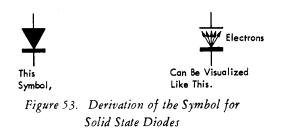

the reverse direction. The germanium thus acts like the cathode and the "cat's whisker" like the plate or anode. Since the internal construction of a germanium diode is most often not visible, an identifying band of color (or a plus symbol) will be printed on the *cathode end* of the case. Some diodes will instead have the diode symbol imprinted on the case. Note particularly that (except for leakage) electron flow through the diode is *opposite* to the direction of the arrow symbol. This can possibly be remembered more easily by visualizing the arrow symbol to be as drawn in Figure 53.

Typical germanium diodes will have forward resistances of from 50 to 500 ohms and back resistances of from 100,000 to 1,000,000 ohms. These values vary with the diode, the current, the temperature and the applied voltage. Forward current ratings of small diodes range near 25 to 50 milliamperes, and the maximum

voltage across the diode in the reverse direction must be limited to 50 volts or less (100 volts with some types). Diodes are easily ruined by excessive heat. For this reason field replacement within units (where soldering is required) is not advised. Replace the complete unit.

Selenium rectifiers have the same symbol and general action as crystal diodes. They are physically larger (being made up of stacks of steel plates coated with alloys and selenium), have higher internal shunt capacitance, and have a higher resistance to the passage of electrons in the forward direction. They are used in the 604-521 as power rectifiers, arc suppressors, and polarity traps, due to their availability in higher current and reverse voltage breakdown ratings. They are less susceptible to burnout from momentary current overload, which makes them useful in circuits with high transient conditions. Some of the smaller selenium rectifier diodes, such as are used in the wiring of the 604 electronic tube gate panels, are encased in small cardboard tubes. The cathode end is identified the same as germanium diodes.

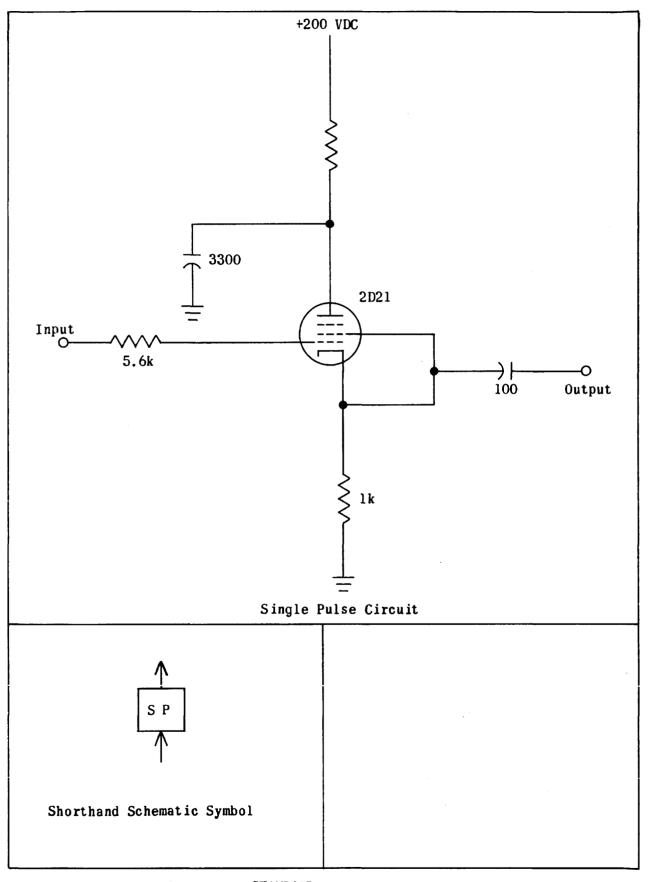

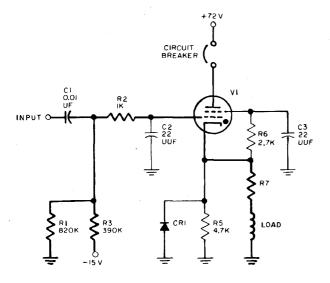

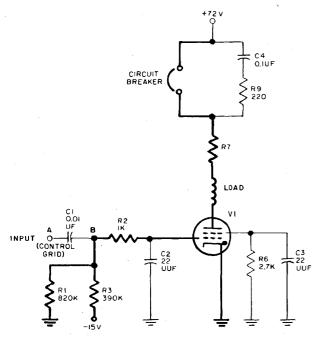

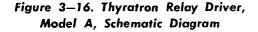

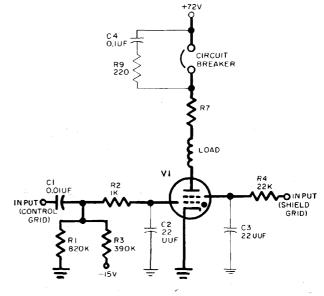

#### Thyratron (TH) Units (G and H)

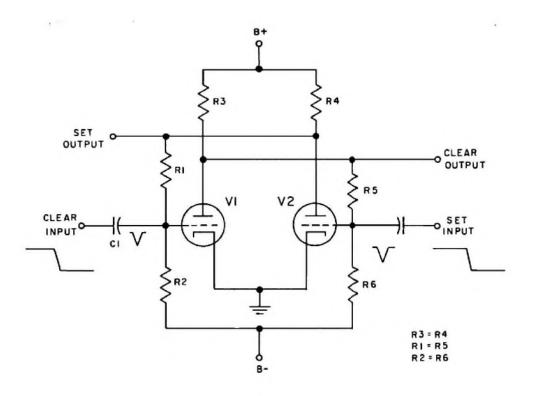

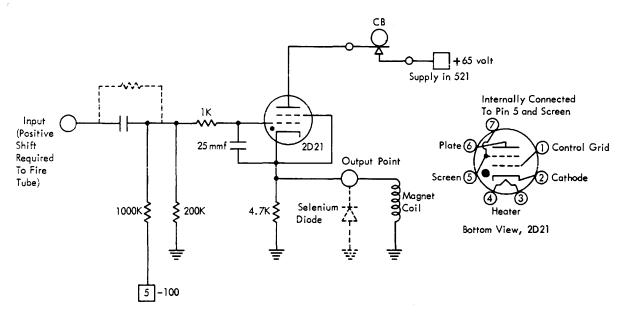

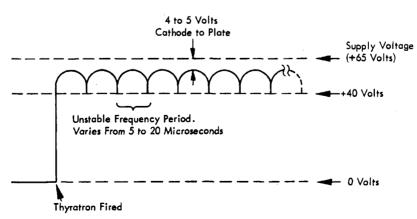

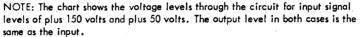

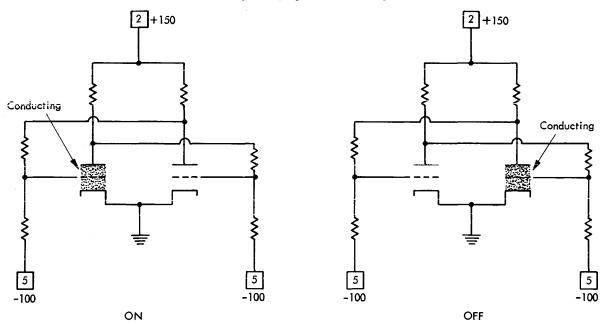

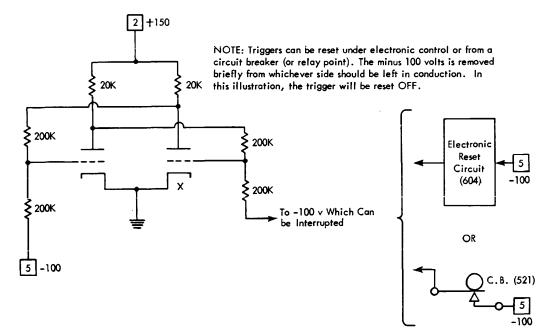

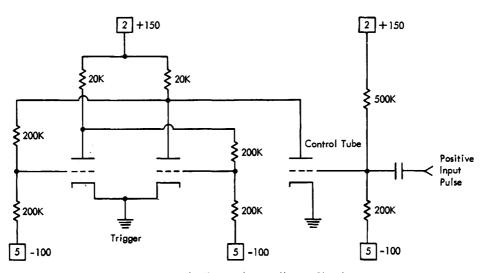

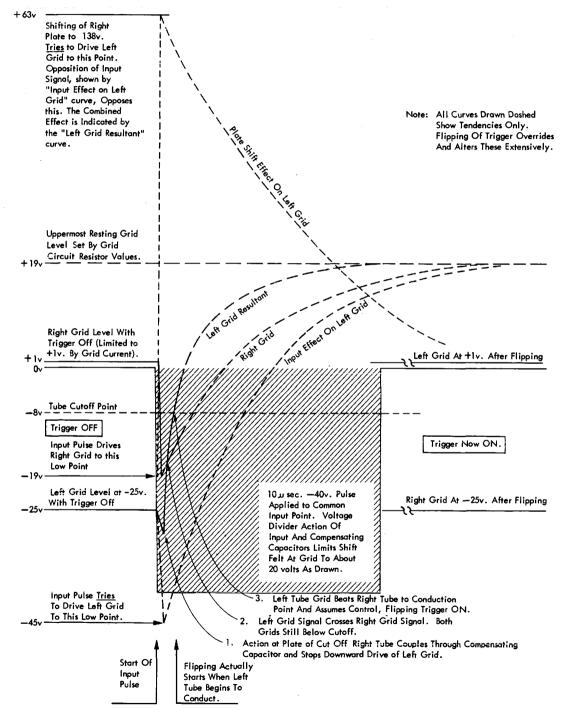

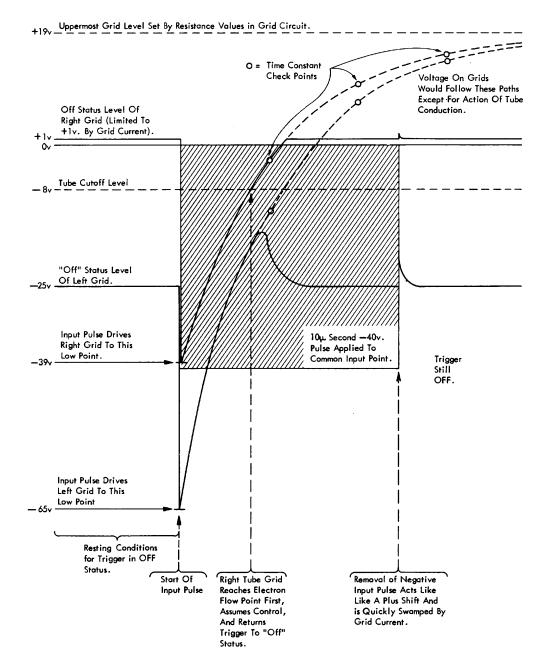

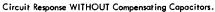

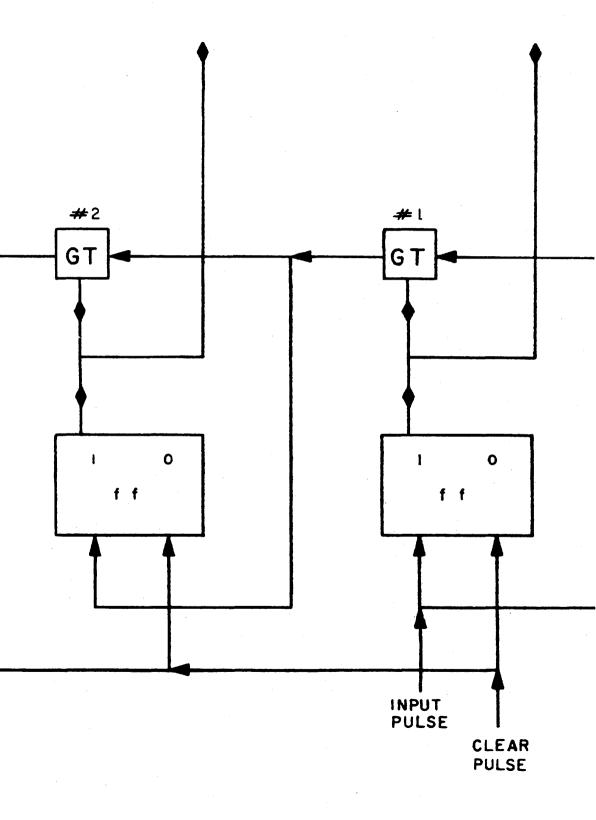

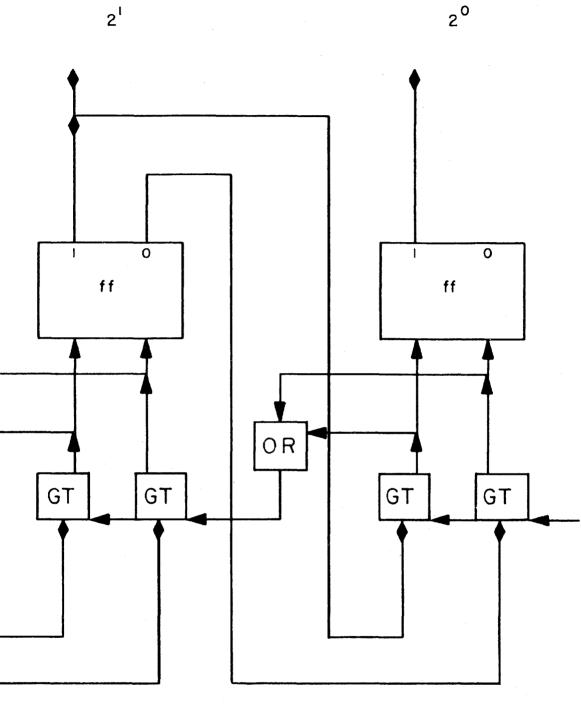

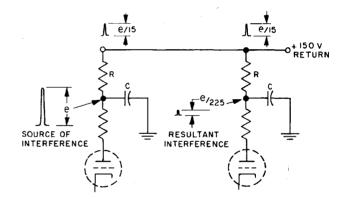

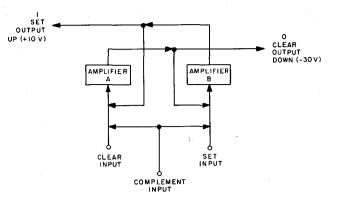

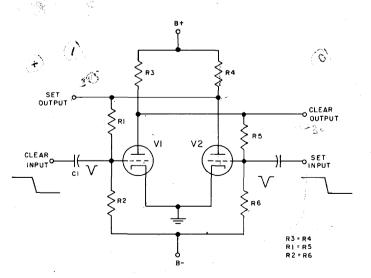

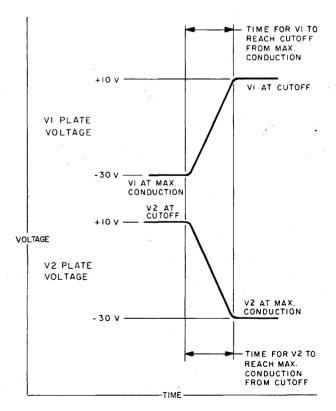

Filling the glass envelope of an electron tube with a gas such as argon increases the current carrying capabilities of the tube from two to ten times. Such a tube is called a thyratron and is an excellent high current, low voltage control device. It also has certain other characteristics which make it very useful whenever a relay or a punch magnet coil must be energized under electronic control, as when punching out calculated answers. The industrial type 2D21 tube is used in all thyratron units of the 604. This tube, about the physical size of the 6AQ5, is capable of passing the 80 milliamperes required by the usual relay coil and up to the 400 milliamperes required for brief periods when energizing a punch magnet coil. Figure 54 shows a typical circuit and the basing diagram for the 2D21. Notice the dot within the tube diagram which indicates a gas filled envelope.