## AN INTRODUCTION TO Z80 MACHINE CODE

by R.A. & J.W. PENFOLD

BERNARD BABANI (publishing) LTD THE GRAMPIANS SHEPHERDS BUSH ROAD LONDON W6 7NF ENGLAND

## AN INTRODUCTION TO Z80 MACHINE CODE

#### ALSO BY THE SAME AUTHORS

- No.BP129 An Introduction to Programming the ORIC-1

- No.BP133 An Introduction to Programming the DRAGON 32

- No.BP139 An Introduction to Programming the BBC Model B Micro

- No.BP142 An Introduction to Programming the ACORN ELECTRON

- No.BP143 An Introduction to Programming the ATARI 600/800 XL

- No.BP147 An Introduction to 6502 Machine Code

- No.BP150 An Introduction to Programming the Sinclair QL

- No.BP153 An Introduction to Programming the AMSTRAD CPC464

- No.BP154 An Introduction to MSX BASIC

- No.BP156 An Introduction to QL Machine Code

- No.BP158 An Introduction to Programming the Commodore 16/Plus 4

#### PLEASE NOTE

Although every care has been taken with the production of this book to ensure that any projects, designs, modifications and/or programs etc. contained herein, operate in a correct and safe manner and also that any components specified are normally available in Great Britain, the Publishers do not accept responsibility in any way for the failure, including fault in design, of any project, design, modification or program to work correctly or to cause damage to any other equipment that it may be connected to or used in conjunction with, or in respect of any other damage or injury that may be so caused, nor do the Publishers accept responsibility in any way for the failure to obtain specified components.

Notice is also given that if equipment that is still under warranty is modified in any way or used or connected with home-built equipment then that warranty may be void.

All the programs in this book have been written and tested by the authors using models of the relevant micros that were available at the time of writing in Great Britain. Details of the graphics modes may vary with versions of these machines for other countries.

#### © 1984 BERNARD BABANI (publishing) LTD

First Published – November 1984 Reprinted – June 1986 Reprinted – January 1988 Reprinted – January 1990

British Library Cataloguing in Publication Data

Penfold, R.A.

An introduction to Z80 machine code (BP.152)

1. Microcomputers — Programming

2. Machine codes (Electronic computers)

I. Title II. Penfold, J.W.

001.64'24 QA76.6

ISBN 0 85934 127 5

Printed and bound in Great Britain by Cox & Wyman Ltd, Reading

## PREFACE

Home computers are equipped with built-in software that enables them to be easily programmed to do quite complex tasks. The price that is paid for this programming ease is a relatively slow running speed, far lower than the speed at which the computer is really capable of running. Machine code programming entails direct programming of the microprocessor without using a built-in high level computer language such as BASIC. This gives a vast increase in running speed, but is something that can only really be undertaken by someone who has a reasonable understanding of the microprocessor and some of the other hardware in the computer.

Machine code programming is not as difficult as one might think, and once a few simple concepts have been grasped it is actually quite straightforward (although admittedly never as quick and easy as using a high level language). This book takes the reader through the basics of microprocessors and machine code programming, and no previous knowledge of these is assumed. The microprocessor dealt with here is the Z80 which is not one of the most simple types, but is generally acknowledged as one of the most powerful 8 bit devices, and is by no means excessively difficult for beginners. The Z80, or in most cases now the faster version the Z80A, are used in many home computers, including several of the most popular machines such as the Sinclair ZX81 and ZX Spectrum, the Memotech MTX500 and MTX512 machines, and the Amstrad CPC 464. A few simple demonstration programs that can be run on these computers are included in this book.

#### R.A. & J.W. Penfold

## CONTENTS

### Page

| Chapter 1:           |    |

|----------------------|----|

| THE MICROPROCESSOR   | 1  |

| Assembly Language    | 3  |

| The Processor        | 5  |

| Binary               | 9  |

| Signed Binary        | 13 |

| Twos Complement      | 15 |

| Overflow Flag        | 17 |

| Binary Coded Decimal | 18 |

| Hexadecimal          | 20 |

| System Operation     | 22 |

| The Stack            | 26 |

| Flags                | 29 |

| Z80A Pinouts         | 31 |

| Mode 0               | 34 |

| Mode 1               | 34 |

| Mode 2               | 34 |

| Chapter 2:           |    |

| ADDRESSING MODES     | 37 |

| Implied Adressing    | 37 |

| Immediate Addressing | 38 |

| Absolute Addressing  | 38 |

| Zero Page            | 39 |

| Relative Addressing  | 39 |

| Indirect Addressing  | 40 |

| Indexed Addressing   | 40 |

| Chapter 3:<br>THE INSTRUCTION SET 41 |

|--------------------------------------|

| Chapter 4:                           |

| STORING AND EXECUTION 102            |

| Execution 103                        |

| Chapter 5:                           |

| EXAMPLE PROGRAMS 105                 |

| Add105                               |

| And 106                              |

| Loop107                              |

| Take                                 |

| Machine Specific Listings            |

| for Memotech 109                     |

| Machine Specific Listings            |

| for ZX81112                          |

| Machine Specific Listings            |

| for ZX Spectrum 115                  |

| Machine Specific Listings            |

| for Amstrad CPC 464 117              |

| Chapter 6:                           |

| INPUT/OUTPUT 121                     |

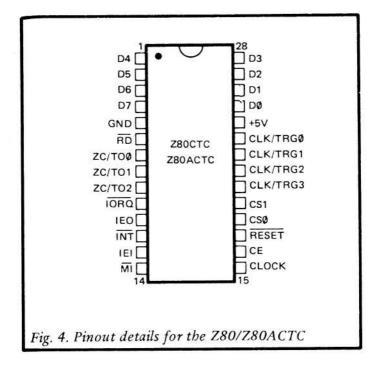

| The Z80 CTC                          |

| Control Register 124                 |

# Chapter 1 THE MICROPROCESSOR

All home-computers are equipped to operate using a high level computer language such as BASIC or FORTH, and these languages are designed to make program design as quick and easy as possible. With most high level languages the programmer uses words that are virtually plain English, and the computer's built-in software then converts these into machine code routines that the microprocessor at the heart of the computer can interpret and act upon. Writing programs direct in machine code is, on the face of it, rather pointless, as it is somewhat harder and a considerably slower process than using BASIC or another high level language to achieve the same ends.

The advantage of machine code programs is the speed with which they run. The speed of a machine code program is, in fact, only limited by the operating speed of the computer's microprocessor, and a computer can perform no faster than when it is running a machine code program. High level languages such as BASIC are inevitably much slower due to the way in which each instruction has to first be interpreted (converted into machine code) before it can be executed. In other words, the program is stored in memory in its BASIC form, and it is only when the program is run that each instruction is converted into machine code and executed. The program is effectively brought to halt during the interpreting process, which accounts for more time than the running of the interpreted machine code. The difference in speed is probably much greater than most people realise, and machine code is typically something approaching one thousand times faster than an equivalent BASIC program.

Action games written in BASIC are often a little sluggish due to this lack of operating speed, especially when a lot starts to happen at once, but a machine code equivalent normally appears to operate instantly no matter how much simultaneous action takes place. With some scientific and business progams BASIC is too slow to be of any use at all, and the use of machine code is mandatory. However, the speed of machine code is its only advantage, and apart (perhaps) from the fun of it, there is no point in using machine code where a program written in a high level language would be fast enough.

There are alternatives to machine code and high level interpreted languages such as BASIC, and we will consider these briefly before moving on to a description of the microprocessor itself. Some high level languages are compiled rather than interpreted. The difference is that with a compiled language the interpreting process is carried out before the program is run. The program may then run using the compiled machine code, or using a sort of pseudo machine code which requires a minimal amount of interpreting. In either case programs should run at high speed, and should be far easier to write than equivalent machine code programs. A compiled language may seem like the ideal solution (and many people would argue that it is), but languages of this type are generally much more difficult to use than interpreted languages when writing and debugging programs, and languages such as BASIC are probably much better for beginners to programming. A mixture of BASIC and machine code (with the latter only being used where high operating speed is essential) can therefore be a more practical solution in many cases.

Incidentally, you may come across the terms source code and object code occassionally. The former is the program in its high level language form, and the latter is the machine code or pseudo machine code produced after interpretation or compilation.

### Assembly Language

The terms machine code and assembly language seem to cause a certain amount of confusion, and there seems to he a general belief that they are different terms for the same thing. In fact they are very similar, but there is an important difference. When machine code programming 8 bit microprocessor the instructions for the an microprocessor are in the form of numbers from 0 to 255 (or in some cases, two numbers of this type). This is not a very convenient way of doing things, and it inevitably involves almost constantly looking up instructions to find their code numbers. Assembly language uses a program in the computer to take three or four letter codes and convert these into the corresponding machine code instruction numbers. Most assemblers also provide the programmer with some further assistance, but not much when compared to a high level language such as BASIC. The main function of the assembler is simply to take the three or four letter mnemonics and convert them to the appropriate numbers. An assembler is really the most basic of compilers, but as far as the programmer is concerned there is no real difference between assembly language and machine code, and if you can program in one you can also program using the other.

Of course, the main advantage of using an assembler is that the mnemonics are chosen to closely relate to the instructions that they represent. For example, the Return From Subroutine instruction has RET as its mnemonic which is obviously much easier to remember than the machine code number of 169. If you intend to do a lot of machine code programming an assembler could reasonably be considered essential, since using anything other than a few short machine code routines is generally rather awkward and inconvenient with most home-computers which are designed primarily for BASIC programming. A few computers (the Memotech MTX500 and MTX512 for instance) have built-in assemblers, but assembler programs are readily available for most other Z80A based computers. The facilities offered vary somewhat from one assembler to another, but most give at least some aid with debugging, although they are nothing like as sophisticated as the best BASIC languages in this respect.

One final point to bear in mind is that a high level language like BASIC varies only slightly from one computer to another, and once you have mastered BASIC it is usually not too difficult to write programs for any computer equipped with this language. Problems can arise with the sound and graphics facilities which vary from one machine to another, giving inevitable variations in the sound and graphics commands. However, the language is fundamentally the same for all the computers that use it. Machine code programming is identical for any computers that use the Z80A microprocessor as the central processor. Although there are again differences in the sound and graphics facilities available on various machines, these do not affect the instructions that are available to the programmer (although to produce the desired effect it might be necessary to use a different routine for each machine because of differences in the supporting hardware for the microprocessor). The situation is very different when dealing with a computer that uses a different microprocessor such as the 6502. Apart from the differences in the sound and graphics facilities, the microprocessor will have different machine code numbers for each instruction, and possibly even different mnemonics. For instance, the Z80A Return Subroutine instruction, as mentioned earlier, has RET as its mnemonic, and 169 is the instruction number. The equivalents for the 6502 microprocessor are RTS and 60. Furthermore, the instruction sets of various microprocessors are substantially different, as are the registers they contain and the way in which they handle certain tasks. Obviously all microprocessors work on the same basic principle, but rewriting a machine code program to run on a different microprocessor is not usually just a

matter of coverting the mnemonics or code numbers, and changing from programming one type to programming an alternative device usually involves a fairly substantial amount of work.

#### The Processor

Although a microprocessor is an extremely complex device, usually containing the equivalent of tens of thousands of components, as far as the programmer is concerned it can be regarded as a fairly simple set of electrical circuits known as registers which will perform certain functions if fed with the appropriae instruction numbers. The registers consist of one or more circuits known as flip/flops, and these can produce an output voltage that is either virtually zero, or one that is typically about 5 volts. From the software point of view the voltages are not important, and we can think in terms of low or logic 0 if the output of a flip/flop is near zero volts, and high or logic 1 if it is at about 5 volts. A circuit with an output that can represent just 0 or 1 may not seem to be very useful, and in isolation such a circuit is not of tremendous value, but as we shall see later, a number of flip/flops together can represent large numbers, and can be used to perform complex calculations etc.

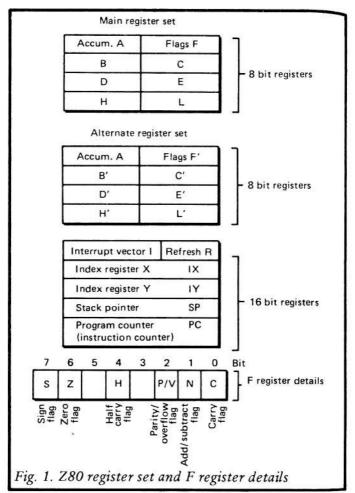

The registers of the Z80A are shown in diagramatic form in Figure 1, and the ones of main interest to the programmer are the accumulator (A register), the flag (F register), the six general purpose registers (the B, C, D, E, H, and L registers), and the IX plus IY index registers. The A, F, B, C, D, E, H, and L registers are in fact all duplicated in the alternative register set, but only one set at a time can be used (with instructions being included to enable the programmer to switch from one set to the other as desired). These are 8 bit registers apart from the IY and IY index registers which are 16 bit types. However, as

indicated in Figure 1, the B-C, D-E, and H-L registers are paired together, and can operate effectively as 16 bit registers. In other words, they have two sets of eight flip/flops and can handle numbers up to 16 bits long. The accumulator and flag registers also operate together, but.

as we shall see later. not in the same way as the other register pairs. Incidentally, a group of 8 bits is usually called a byte. although strictly speaking a byte does not have to be 8 bits long, and can be any length. The point about a byte is that it is not just a collection of unrelated signals or bits, but the bits operate together to represent a number, alphanumeric character, or whatever.

The accumulator is very much at the centre of things. and any data processed by the microprocessor has to be handled by this register and the complex circuit associated with it. With the Z80A some of the other registers can actually be used when processing data, but they are then acting as a sort of pseudo accumulator. The circuit associated with the accumulator is called the arithmetic logic unit, or ALU, but this is something that can be ignored by the programmer. If you feed an instruction to the microprocessor the ALU will almost certainly be involved in the execution of that instruction, but this is something that is all handled internally by the microprocessor itself, and the programmer does not get directly involved with the ALU. At this stage we will not consider in detail the type of data processing that the accumulator can provide, but it includes such things as addition and subtraction.

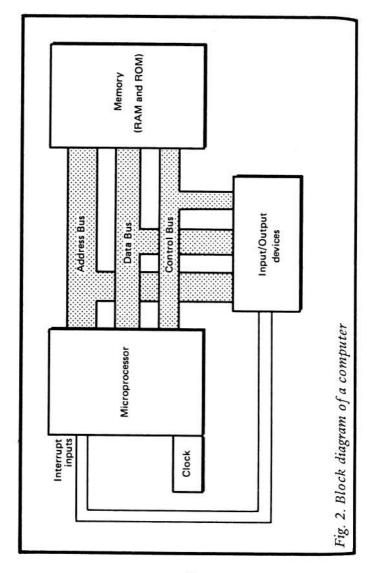

The IX and IY registers are index registers. Their purpose is to act as pointers to tell the microprocessor where to find data or instructions. In order to understand their function, or the function of practically any part of the microprocessor for that matter, it is necessary to understand, amongst other things, the basic make-up of a computer. Figure 2 shows in block diagram form the general arrangement used in a Z80A based computer. The memory is a bank of 8 bit registers which are used to store both program instructions and data. The number of registers in the memory block varies from one computer to another, but the Z80A can operate with a maximum of 65536. The address bus is 16 bits wide, and these sixteen bits are produced by the program counter (see Figure 1).

It is the program counter, via the address bus, that selects the particular memory register that is connected to the microprocessor. The data bus is used to transfer data between the microprocessor and the memory block. An important point to note here is that the data bus is bidirectional, and is used by the microprocessor to take data and instructions from memory, and to place data in memory. There are not separate input and output busses on a microprocessor — the data bus is used for both types of operation.

The control bus is used to make sure that all the elements of the system are operating in unison, and that if (say) the microprocessor sends data to a particular register in memory, that register is ready to receive the data and is not trying to output data to the microprocessor. All the lines in the control bus operate automatically, are not directly controlled by the programmer, and are not something we need concern ourselves with here.

#### Binary

The 16 bit program counter can place 65536 different output combinations onto the address bus, and it is this that limits the Z80A to 65536 memory registers. Each memory register occupies an address, which is merely a number from 0 to 65535, and each of the 65536 output combinations of the program counter corresponds to one of these addresses. Therefore, by placing each bit of the program counter at the appropriate state, the microprocessor can read the contents of any memory register, or can write data to that register, depending on the type of instruction it is executing. In order to undertake machine code or assembly language programming it is essential to understand the way in which the bits of the address bus (and the data bus) are used to represent a number.

The numbering system we normally use is commonly called the decimal system and is, of course, based on the

number 10. There are ten single digit numbers from 0 to 9. This system of numbering is not very convenient for an electronic circuit in that it is difficult to devise a practical system where an output has ten different voltage levels so that any single digit decimal number can be represented. It is much easier to use simple flip/flops which have just two output levels, and can only represent 0 or 1. However, this bars such circuits from operating directly in the decimal numbering system. Instead, the binary system of numbering is utilized.

This system is based on the number 2 rather than 10, and the highest single digit number is 1 rather than 9. If we take a decimal number such as 238, the 8 represents eight units (10 to the power of 0), the 3 represents three tens (10 to the power of 1), and the two represents 2 hundreds (10 to the power of 2 or 10 squared). Things are similar with a binary number such as 1101. Working from right to left again, the 1 represents the number of units (2 to the power of 0), the 0 represents the number of twos (2 to the power of 1), the next 1 represents the number of fours (2 to the power of 2), and the final 1 represents the number of eights (2 to the power of 3). 1101 in binary is therefore equivalent to 13 in decimal (1 + 0 + 4 + 8 = 13).

The table following shows the number represented by each digit of a 16 bit number when it is set high. Of course, a bit always represents zero when it is set low,

| Bit |  |  |  |             | 8<br>256    |

|-----|--|--|--|-------------|-------------|

|     |  |  |  | 14<br>16384 | 15<br>32768 |

Using 16 bits any integer from 0 to 65535 can be represented in binary fashion, or using 8 bits any integer from 0 to 255 can be represented, and this exposes the main weakness of the binary numbering system. Numbers of modest magnitude are many binary digits in length, but despite this drawback the ease with which electronic circuits can handle binary numbers makes this system the only practical one at the present time.

Addition of two binary numbers is a straightforward business which is really more simple than decimal addition. A simple example is shown following:—

| First number  | 11110000  |

|---------------|-----------|

| Second number | 01010101  |

| Answer        | 101000101 |

As with decimal addition, start with the units column and gradually work towards the final column on the left. In this case there is 1 and 0 in the units column, giving a total of 1 in the units column of the answer. In the next column two 0s give 0 in the answer, and the next two columns are equally straightforward. In the fifth one there are two 1s to be added, giving a total of 2. Of course, in binary the figure 2 does not exist, and this should really be thought of as 10 (one 2 and no units), and it is treated in the same way as ten in decimal addition. The 0 is placed in the answer and the 1 is carried forward to the next column of figures. The sixth column again gives a total of 10, and again the 0 is placed in the answer and the 1 is carried forward. In the seventh column this gives a total of 3 in decimal, but in this binary calculation it must be thought of as the binary number 11 (one 2 and one unit). Therefore, 1 is placed in the answer and 1 is carried forward. In the eighth column this gives an answer of 10. and as there are no further columns to be added, both digits are placed in the answer.

Adding two 8 bit binary numbers together produces a slight complication in that, as in this case, the answer is some 9 bits long. When the accumulator is used to add two 8 bit numbers it cannot accommodate the extra bit when there is a final carry-forward, but the 1 in column nine is not simply lost (which would obviously give an incorrect

answer and would be unacceptable) Instead, the carry forward is taken to one bit of the microprocessor's status register. Not surprisingly, this is called the carry or C bit. The main use of the status register bits or flags is in conditional instructions (i.e. if the carry bit is set high do this, if it is not do that). Anyone who has done some BASIC programming should be familiar with conditional instructions in the form of BASIC IF...THEN or IF...THEN...ELSE and similar instructions. Note that there are eight flags in the status register, but only five of these are actually used.

Of course, the fact that the accumulator can only handle 8 bit numbers giving a maximum equivalent to 255 in decimal, is not to say that 8 bit computers and microprocessors can not deal in numbers of a higher magnitude. Very large numbers can be accommodated by using two or more bytes together. The usual way of doing this is to have (say) two bytes used together with one byte providing the lower 8 bits of the number, and the other providing the upper 8 bits. These are generally called the low byte and high byte respectively. Two other terms that are often used are least significant bit or LSB, and most significant bit or MSB. These simply refer to the lowest and highest bits respectively (e.g. bits 0 and 7 of 8 bit number).

When adding together two 16 bit numbers the basic way in which it is done is to first add the two low bytes, to give the low byte of the answer. Then the two high bytes are added together with the carry (if any) to give the high byte of the answer, plus a possible 17th bit in the carry flag.

When machine code programming using a homecomputer the hardware between the programmer and the microprocessor can help to make things very much easier. but it can also be a hinderance. Few home-computers allow numbers to be entered in binary form, or normally display data in this form, although a few computers do allow data to be entered in binary form (such as the

sinclair ZX Spectrum using the BASIC BIN instruction). Thus, although the microprocessor would handle a calculation such as 10 plus 20 in binary form, using a home-computer and numbers would be entered in decimal. and the answer would be displayed in decimal. For simple data processing this is very convenient, but when it comes to multibyte numbers and certain other types of data processing it is rather inconvenient. A large number such as 2050 is processed by the microprocessor as two 8 bit numbers, which are entered into the computer as two decimal numbers in the range 0 to 255. In the case of the number 2050, in decimal the high byte is 4, and the low byte is 2, which bears little resemblence to the decimal number 2050 or its binary equivalent. The point to remember here is that bits 0 to 7 of the high byte represent the 512s, 1024s, 2048s, etc., through to the 32768s. However, as far as the number entered into the computer is concerned, when set high bits 0 to 7 only represent 1, 2, 4. etc.

When using machine code you must be aware of the way in which the microprocessor deals with data on a bit by bit basis if you are to fully master the situation, and a reasonable understanding of binary is essential.

#### Signed Binary

The binary system described so far, which is often called direct binary, is inadequae in many practical applications in that it is unable to handle negative numbers. One way around the problem is to use signed binary numbers where the first bit is used to denote whether the number is positive or negative. The convention has the first bit as a 0 for positive numbers and as a 1 for negative numbers. With this system the normal number range of 0 to 255 is replaced with a range of -127 (1111111) to +127(01111111). The problem is solved only at the expense of reduced maximum magnitude for a given number of bits. Note though, that where two or more bytes are used  $t_0$  form a multibyte number, only the most significant bit of the high byte needs to be used to indicate whether the number is positive or negative, and it is not necessary  $t_0$  use the most significant bit of each byte in the number  $t_0$  do this.

Obviously a certain amount of care needs to be excercised when dealing with binary numbers and you must know whether a number is in signed or unsigned binary. For example, 10000001 could be 129 (unsigned) or -1 (signed). In this basic form the signed binary system has practical limitations in that it can represent binary numbers without any difficulty, but calculations fail to give the right result, which makes the system of little practical value unless it is modified to correct this anomaly. It is not used with the Z80A microprocessor in the basic form described above.

To illustraste the problem, consider the calculation:-

| 16           | 00010000 |

|--------------|----------|

| -5           | 10000101 |

| Answer (-21) | 10010101 |

Adding 16 and -5 should obviously give an answer of 11 not -21.

An alternative and related method of handling negative numbers is the ones complement system. Here a negative number is the complement of the positive equivalent. For instance, +16 in binary is 00010000, and -16 is therefore 11101111. In other words, the ones are simply changed to zeros and the zeros are changed to ones. This gives better results when used in calculations, as demonstrated by the foillowing example.

| 16 | 00010000 |  |

|----|----------|--|

| -5 | 11111010 |  |

This answer may seem to be less use than the one obtained using ordinary signed binary, and the margin of error is certainly greater, but this depends on how the answer is interpreted. The first point to note is that the positive number starts with a zero and the negative number starts with a 1. Provided that sufficient digits are under starts with a 1. Provided that sufficient digits are used this will always be the case, and in this respect the system is not much different to ordinary signed binary. The answer is completely wrong of course, but if the carry is ignored the answer is much closer to the right result. It then becomes 10 rather than 11. So what happens if we try another example and again ignore the carry in the answer?

| 32          | 00100000  |

|-------------|-----------|

| -4          | 11111011  |

| Answer (27) | 100011011 |

As before, the answer is wrong, but is one less than the right answer (which is of course 28 in this case).

#### **Twos Complement**

Clearly this system can be made to operate properly, and it is just a matter of finding some way of correcting the answer. The method used with simple microprocessors such as the Z80 is the twos complement system. This differs from the ones complement system in that once the complement of a number has been produced one is added to it. Therefore, rather than -5 being represented as 11111010, it becomes 11111011. If we now apply this to one of the examples given earlier we obtain the following result

| 16          | 00010000  |

|-------------|-----------|

| -5          | 11111011  |

| Answer (11) | 100001011 |

This time, provided we ignore the carry in the carry flag, we have the correct answer of 11. This is a convenient way of handling subtraction (for the microprocessor anyway) since subtraction can be handled by the same circuit that handles addition. To handle a sum such as 45 - 25 the figure of 25 is converted into (twos complement) -25, and then added to 45. In other words, rather than calculating the sum in the form 45 - 25 the microprocessor calculates it as 45 + (-25), and either way the answer is 20.

The table following shows some sample numbers in twos complement form, and should help to clarify the system for you. Note that, like ordinary signed binary, the first digit is used to indicate whether the number is positive or negative.

| Number | Positive | Negative |

|--------|----------|----------|

| 0      | 00000000 | 00000000 |

| 1      | 00000001 | 11111111 |

| 2      | 00000010 | 11111110 |

| 3      | 00000011 | 11111101 |

| 4      | 00000100 | 11111100 |

| 32     | 00100000 | 11100000 |

| 126    | 01111110 | 10000010 |

| 127    | 01111111 | 10000001 |

| 128    | 01000000 | 10000000 |

Note that with 8 bit twos complement numbers the range is from +127 to -128.

So far we have only considered calculations where the answer is a positive quantity, but the twos complement system works properly if the answer is negative. The following example demonstrates this point:-

| 16           | 00010000 |

|--------------|----------|

| -31          |          |

|              | 11100001 |

| Answer (-15) | 11110001 |

The system also functions correctly when two negative numbers are added together, as demonstrated by this example:-

| -4           | 11111100 |

|--------------|----------|

| -8           | 11111000 |

| Answer (-12) | 11110100 |

#### **Overflow** Flag

When using the twos complement system there is a slight problem in that a number can be accidentally turned into a negative quantity. The simple calculation shown below demonstrates this point:-

| 64           | 01000000 |

|--------------|----------|

| 127          | 01111111 |

| Answer (-65) | 10111111 |

If taken as an ordinary 8 bit direct binary number this does give the right answer, but in the twos complement system the carry forward from bit 6 to bit 7 has changed the sign and magnitude of the number so that an answer of -65 instead of 191 is obtained.

This is termed an overflow, and it is handled by microprocessors such as the Z80 by a flag called (appropriately) the overflow flag. In the diagram of Figure 1 this is given its abbreviated name, the V flag. This flag is actually a dual purpose type, and also acts as the parity flag. This will be described in more detail later Like the carry flag, there are special instructions connected with the overflow flag, and these can be used to prevent erroneous results from being produced, or to give warning that an error has occured. These flags are normally at 0 and are set by an overflow or a carry forward. They are automatically controlled by some of the microprocessor's instructions, and this helps to streamline things so that he system operates rapidly and uses as little memory as possible. Most microprocessors have instructions specifically for setting or resetting certain flags, but the Z80A has very few instructions of this type, and is designed to operate in a way that renders them unnecessary.

At this stage it is probably best not to go into any more detail about binary calculations and the way they are handled by microprocessors. It is a complicated subject, and it is probably clarified most easily by trying out a few programs which demonstrate the techniques involved. Some simple practical examples that can be run on some popular Z80A based home-computers are given later in this book. Even if you can only understand direct binary, provided you also understand the main principles of microprocessors you should be able to run and understand some simple machine code routines.

#### **Binary Coded Decimal**

The Z80A can use another form of binary known as binary coded decimal, or BCD. This is perhaps less frequently used than the twos complement binary system described above, and it has the disadvantages of being relatively slow and uneconomic on memory. However, it can be used to give a high degree of precision, and it can be advantagous in certain applications. It is certainly worthwhile considering this system briefly here.

With BCD four binary bits (often termed a nibble) are used to represent each decimal digit. The system operates in the following manner:—

| Decimal Number<br>0 | Bit Code<br>0000 |

|---------------------|------------------|

| 1                   | 0001             |

| 2                   | 0010             |

| 3                   | 0011             |

| 4                   | 0100             |

| 5                   | 0101             |

| 6                   | 0110             |

| 7                   | 0111             |

| 8                   | 1000             |

| 9                   | 1001             |

The binary number is in fact just the normal binary representation of the number concerned, and it is only for numbers of more than 9 that the system is different. The binary codes from 1010 to 1111 are unused, and all two digit decimal numbers require 8 bit binary codes. For instance, the decimal number 64 would be represented by the 8 bit BCD code 01100100. The first four bits (0110) represent the 6, and the second four bits (0100) represent the four. Each byte can therefore represent any two bit number from 0 to 99, which compares to a range of 0 to 255 for a straightforward 8 bit binary number. This helps to contribute to the relative inefficiency of the BCD

system. Of course, when a nibble is incremented by 1 from 1001 (9 in decimal) it does not go to 1010 (which is an illegal code in BCD). but cycles back to 0000. A carry forward of 1 should then be taken to the next BCD nibble

With this system there is no difficulty in handling large numbers, and it is just a matter of using several bytes to accomodate the required number of digits. Negative numbers and decimal points can also be handled with ease by this system, but this requires an additional byte or bytes. This information is usually carried in the high byte or bytes.

#### Hexadecimal

While on the subject of numbering systems it would perhaps be worthwhile dealing with another system which you will inevitably come across quite frequently, and this is the hexadecimal system. There is in fact yet another system known as octal which, as its name suggests, is based on the number 8. Octal seems to have fallen from favour in recent years, and as it is something you are not likely to encounter these days we will not consider this system here.

A problem with binary numbers is that they tend to have many digits with each digit being either 0 or 1, which makes them rather difficult to deal with in many circumstances. For instance, trying to remember more than just a very few Z80A instruction codes in their 8 bit binary form would probably be beyond most peoples' ability. On the other hand, binary numbers give a graphic representation of the state of each bit in the registers of the microprocessor, and this is something that is often important. Decimal numbers are easier to use in that they are much shorter and are in a familiar form. Converting a decimal number into an equivalent binary one is not a very quick or easy process, especially where large numbers are concerned, and this is inconvenient when it is necessary to visualise things on a bit by bit basis. The hexadecimal system gives the best of both worlds in that it requires just a few digits to represent fairly large numbers, and is in fact slightly better than the decimal system in this respect. On the other hand, it is easy to convert hexadecimal to binary, and it is easy to use when operating at bit level. The hexadecimal system is based on the number 16, and there are sixteen single digit numbers. Obviously the numbers we normally use in the decimal system are inadequate for hexadecimal as there are six too few of them, but this problem is overcome by augmenting them with the first six letters of the alphabet. It is from this that the system derives its name. The table given below helps to explain the way in which the hexadecimal system operates.

| Decimal | Hexadecimal | Binary |

|---------|-------------|--------|

| 0       | 0           | 0000   |

| 1       | 1           | 0001   |

| 2       | 2           | 0010   |

| 3       | 3           | 0011   |

| 4       | 4           | 0100   |

| 5       | 5           | 0101   |

| 6       | 6           | 0110   |

| 7       | 7           | 0111   |

| 8       | 8           | 1000   |

| 9       | 9           | 1001   |

| 10      | А           | 1010   |

| 11      | В           | 1011   |

| 12      | С           | 1100   |

| 13      | D           | 1101   |

|         |             |        |

Continued

| Decimal | Hexadecimal | Binary   |

|---------|-------------|----------|

| 14      | E           | 1110     |

| 15      | F           | 1111     |

| 16      | 10          | 00010000 |

| 17      | 11          | 00010001 |

| 163     | A3          | 10100011 |

What makes hexadecimal so convenient is the way in which multidigit numbers can be so easily converted into binary form. The reason for this is that each hexadecimal digit represents four binary bits. Take the hexadecimal number A3 in the above table for instance. The digit A represents 1010 in binary, and the digit three converts to 0011. A3 therefore represents 10100011 in binary. You may find that you can memorise the four bit binary number represented by each of the sixteen hexadecimal digits, but a little mental arithmetic is all that is needed to make the conversion if you can not.

The digits in a hexadecimal number represent, working from right to left, the number of units, 16s, 256s, 4096s, 65536s, and 1048576s. You are unlikely to use hexadecimal numbers of more than six digits in length.

#### System Operation

If we now return to the block diagrams of Figures 1 and 2, you should begin to get the idea of how data is moved around the system and processed. At switch-on the microprocessor has several of the registers set to zero, including the program counter. The start-up procedure is not normally of interest to the machine code programmer, since few people design their own systems. It is far more likely that you will be using a home-computer where all this is taken care of by the computer's operating system.

The program you write will normally go into a section of memory occupied by random access memory (RAM). This is memory where the microprocessor can set its contents at any desired 8 bit binary number, and then read back that number at a later time. The contents of RAM can be changed an unlimited number of times, but reading the contents of RAM does not destroy the data there or affect it in any way. However, when the computer is switched off the contents of RAM are lost. Software such as the computer's operating system and BASIC interpretter are usually in read only memory (ROM) which retains its contents after the computer has been switched off (although the BASIC interpreter or other language has to be loaded from tape or disc on a few machines). The contents of ROM are fixed, and writing to ROM does not alter its contents. ROM is not an area of memory that is normally used by the programmer, the exception being when there are useful routines there that can be utilized.

The block marked input/output in Figure 2 includes such things as the keyboard and the chip which produces the television picture. Many microprocessors use memory mapped input/output. In other words, the microprocessor reads data from or writes data to input/output devices just as if they were RAM, and they are addressed in exactly the same way. This has the advantage of making programming more straightforward in that using a common set of instructions for memory and input/output operations gives fewer instructions to contend with. A drawback of this system is that some of the 64k (a k is 1024 bytes incidentally) memory address range is occupied by the input/output devices. The Z80A uses the alternative system of having separate input/output and memory maps, but the 16 bit address bus is in fact used for both memory and input/output devices. The difference is in the control bus signals generated by the microprocessor. which select either a memory device or an input/output device depending on the type of instruction used. This leaves the full 64k address range free for memory, and gives more than adequate address space for input/output circuits.

With the aid of the computer's operating system and either the BASIC interpreter or an assembler, the machine code program is placed in a suitable section of memory, and the program is run by directing the microprocessor to the appropriate address. The machine code program then operates by fetching an instruction from the start address of the program, and then shuffling data around its registers and the memory as it goes through the set of instructions. This may seem a rather vague description of things, but if you can grasp the basic concept of instructions and data being taken from memory, or possibly input output devices, with the data being processed in some way by the microprocessor before being sent back to a memory location or an output device, then you should not find it difficult to understand a few simple machine code programs and then gradually progress to more complex ones. If you can not see how the system operates overall, individual machine code instructions could, to say the least, be rather difficult to understand, and even simple programs would certainly be impossible to follow.

A simple example of how the system operates should now be quite easy for you to understand. We will assume that the program must take a number from some memory location, then add this to a number taken from a second address, and then finally place the answer at a third address. There is more than one way of going about this, and the differences occur due to the various addressing modes that the Z80A can use. In other words, we can place the numbers at any addresses we like, and by using the appropriate addressing mode (or modes) and instructions the program can be made to obtain the numbers from the correct addresses. Addressing modes is a fairly complex subject which is fully discussed in a later chapter of this book, and it will not be considered in detail here. For the sake of this example we will use the most simple addressing mode, which is immediate addressing. with this system the first instruction would be to load a byte into the accumulator from memory (i.e. the first number), and with immediate addressing the byte of data is at the address which follows the instruction. After receiving an immediate instruction the program counter automatically increments by one and moves the program on to the byte of data that is to be processed. The next instruction would be to add the second number to the number currently in the accumulator, and this would again be a matter of having the instruction followed by the number at the next address. Next, the instruction to store the accumulator at the next address would be used, and then finally the return from subroutine instruction would be given. This last instruction simply ends the program and returns control of the computer to the operating system.

This program only uses seven bytes including the one where the answer is stored. Before the program was run these would be as follows:—

| Byte 1 | Load immediate instruction code         |

|--------|-----------------------------------------|

| Byte 2 | First number                            |

| Byte 3 | Add immediate instruction code          |

| Byte 4 | Second number                           |

| Byte 5 | Store accumulator immediate instruction |

| Byte 6 | Any 8 bit number                        |

| Byte 7 | Return from subroutine instruction      |

After the program was run things would be little different, and the only change would be that byte 6 would have been changed from a random number to the sum of the first and second numbers. In this simple example we are ignoring any carry forward indicated by the carry flag. It is only fair to point out that the program could not be run in this form on the Z80A as it does not have the necessary store accumulator immediate instruction. However, it could achieve much the same sort of thing using an alternative form of this instruction, and this gives us an opportunity to briefly consider the use of the IX and IY index registers. With the immediate instructions the program counter automatically increments by one after the microprocessor has finished the instruction. This method of doing things is very fast, straightforward, and requires little memory, but it is in many ways limiting.

The IX and IY registers can be loaded with numbers which can then be used to control the program counter in some way so that the program jumps to the required address. In our simple example this indexed addressing is an unnecessarily complicated way of doing things, and they are principally used when working with a block of memory, but it nevertheless illustrates the use of an index register, and should give you the basic idea of how they are used.

Something that will probably have become apparent is that it takes a large number of machine code instructions to achieve quite simple tasks. When programming in a language such as BASIC each instruction is converted into a number of machine code instructions by the interpreter. This is one of the factors which makes writing machine code programs a relatively slow affair.

#### The Stack

There are a number of registers in the Z80A (and shown in Figure 1) which we have not yet considered, and we will take a look at the function of these now. The one labelled SP is the stack pointer, and this is a sixteen bit register which is used to hold an address. The stack is a set of registers which can be used for temporary data storage, and with some microprocessors the stack is an internal part of the microprocessor. This is often termed a hardware stack. This is in many ways the most elegant solution to the problem, and it has the advantage of high speed. It has the disadvantage of giving only a relatively small number of registers, and does of course add complexity to the microprocessor.

The Z80A, in common with most of the more simple and general purpose microprocessors, uses the alternative of a software stack. This is just an area of memory which is reserved for use as the stack, and the system must, of course, provide RAM at the relevant range of addresses. The stack pointer (the SP register) points to an address in this block of RAM, and with the Z80A the use of a 16 bit stack pointer enables the stack to be placed at any desired section of memory.

The stack uses the last in — first out or LIFO system. In other words, each time data is placed onto the stack the SP register is incremented by 1, and each time data is taken from the stack the pointer is decremented by 1. This is often looked on as being analagous to a stack of plates, with plates being loaded one on top of the other, building a pile from the bottom upwards, and then removing plates from the top of the pile and working downwards. The address in the stack pointer is the address of the last byte to be placed on the stack (the highest address in use in other words).

Apart from use as a convenient temporary data store, the stack is also used when subroutines and interrupts are implemented. We will not consider these in detail here, but in both cases the microprocessor breaks out of its normal operating routine, and branches off into another routine. With an interrupt the signal which indicates to the microprocessor that it must break out of its normal routine is provided by a hardware device via one of the Z80A's three interrupt inputs. A typical application where interrupts are used is the timer that is a feature of many home-computers. Here a counter circuit generates an interrupt (sav) every 10 milliseconds, and a software routine is used to increment by one the number stored at a set of memory locations. With suitable manipulation the number in these RAM locations can be converted into suitable data for a minutes and seconds display, or even for a real-time clock. The number can be set to any desired figure so that the clock can be set at the required time. If the timer is to achieve a reasonable degree of accuracy it is important that the microprocessor carries out the software routine at each request without waiting to complete other tasks first. It is for this type of application that interrupts are ideal.

The problem with the use of interrupts is that the microprocessor has to be able to break back into its main routine again after it has finished the interrupt routine. To facilitate this, things such as the contents of the accumulator, the IX register, and the IY register are stored on the stack when the interrupt is generated, and then retrieved again when the interrupt routine has been completed. Things are much the same when a subroutine is called, and a subroutine could be regarded as a sort of soltware generated interrupt. When writing programs for home-computers it is unlikely that you will need to deal with interrupts, and they are principally used as part of the computer's operating system and in a few specialised addon hardware applications, although you might possibly need to handle them when dealing with the computers input/output devices. Because the computer is continually generating its own interrupts there will almost certainly be restrictions on user generated interrupts, and they may not be usable at all. This is not to say that you can simply ignore interrupts, as in some cases they might affect the operation of your program by producing small but important delays, but in most applications they will not be of any consequence.

#### Flags

As we have already seen, the Z80A has status flags apart from the carry and overflow types, and one of these is the zero flag (the Z register of Figure 1). This is used in certain conditional instructions, and comparison instructions. The zero flag is set at 1 when the result of an operation or data transfer is zero, and in other cases it is set at 0. With comparison instructions it is set to 1 when a match is found, and to 0 if no match is achieved.

There are other uses of this flag which is also used in conjunction with bit and certain input output instructions. This is covered in the section dealing with the Z80A instruction set.

The N register of Figure 1 can be a little confusing to anyone who is familiar with certain microprocessors other than the Z80A, since this is the name often given to the negative flag. In this case it is used by the Z80A during some BCD operations, and it cannot be tested by the programmer using conditional instructions. It is therefore only of academic importance to the programmer.

The S flag is the sign flag and this simply reflects the state of the most significant bit of a byte that is being transferred. Remember that with the twos complement system this bit indicates the sign of a number (0 for positive and 1 for negative).

The H flag is the half carry of auxiliary carry flag. This is used to indicate a carry from bit 3 to bit 4, and is needed during BCD operations.

As mentioned earlier, the overflow flag is also used as the parity flag (the P/V register of Figure 1). Parity is mainly used when dealing with text of some kind, and the various characters (upper and lower case letters, figures, punctuation marks, etc.) are then normally encoded using the ASCII (American Standard Code for Information Exchange) code. In fact most home-computers use slight variations on this code, and one or two use totally different codes (the manual for your computer should give a table of the codes it uses). The principle is the same though, with bit codes being used to represent the various characters. The ASCII code uses only seven bits, since this provides up to 128 different characters which is more than adequate to provide a full range of characters. This leaves the most significant bit unused, and free for use in parity checking.

This is very simple in principle, and there are two types or parity: odd and even. With even parity there is always an even number of 1s in the byte, with the parity bit (which is bit 7 in this case) being set to 1 as and when necessary to ensure that the required even number of 1s are present. Odd parity is basically the same, but the parity bit is used to ensure that there is an odd number of 1s in each byte.

The purpose of parity checking is to search for errors, particularly when data is sent to some peripheral device such as a disc drive, and then recovered later. If the data is corrupted and a bit changes state, an odd number of bits will be changed to an even number, or vice versa. However, parity checking is not perfectly reliable, and if two or more bits of a byte are corrupted it is quite possible that a parity check will fail to indicate the error. Parity checking is not used a great deal in practice.

An unusual feature of the Z80A is the R or Refresh register which can be used in conjunction with dynamic RAM devices to ensure correct operation. With most microprocessors this register is provided by external hardware. This is not a register which you are likely to use and a detailed description of its use goes well beyond the scope of this book.

The I register is the interrupt page register, and this is only used in one of the Z80A's interrupt modes. In this mode the I register is used to provide the high byte of the address where the interrupt routine starts, while the low byte must be provided by the device which generated the interrupt.

When dealing with the microprocessors it is common

to find references to pages of memory. For example, you will often come across references to zero page. Pages of memory are simply blocks of 256 bytes, with zero page at addresses from 0 to 255, page 1 at 256 to 511, page 2 at 512 to 767, and so on. The 64k address range of the Z80A gives 256 pages in all.

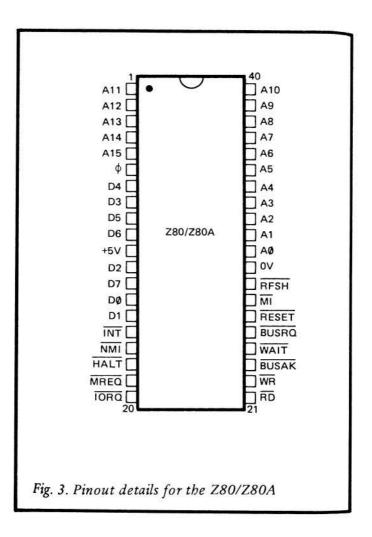

# **Z80A** Pinouts

The Z80A is contained in a 40 pin DIL plastic package. and it has the pinout configuration shown in Figure 3. The pinouts of the device are really only of academic importance as far as the programmer is concerned, but a brief description of these will be given here as you might find it helpful in understanding how the overall system operates.

The pins marked A0 to A15 are the 16 bit address bus, and similarly, D0 to D7 are the 8 bit data bus. BUSRQ is taken low to set both the address and data busses at a high impedance state. In other words they will simply assume whatever logic level some external device dictates, and will not act as inputs or outputs. The point of this is to give an external circuit (a second processor perhaps) direct memory access or DMA. The microprocessor completes whatever part of an instruction it is performing before responding to a BUSRO signal, and it then takes BUSAK low to indicate that it has set the data and address busses in the high impedance state. There are two flip/flops in the Z80A (FF1 and FF2) which are set by signals received at the two interrupt inputs of the device, so that interrupts received while the device is disabled are not just ignored. When BUSRQ is returned to its normal (high) state the microprocessor carries on where it left off. It is really a very simple form of interrupt input.

One of the other interrupt inputs is NMI, the Non Maskable interrupt input, and taking this low generates an

interrupt, but the current instruction is completed first and the microprocessor would simply crash if it was not As its name implies, this type of interrupt can not be blocked by the programmer, and the Z80A will respond immediately to this type of interrupt. The only exception is if the a signal on the BUSRQ line has disabled the Z80A. The NMI interrupt bit is then automatically set be the processor, and the interrupt is serviced as soon as the Z80A is enabled again. The processor automatically stores the contents of the program counter on the stack and further interrupts are ignored until the current one has been completed. This is obviously essential, since the microprocessor can only handle interrupts one at a time The program counter is then loaded with the hexadecimal number 0066, which is where the start of the interrupt routine must be placed, or alternatively data and instructions to direct the microprocessor to the interrunt routine could be placed at this start address.

This type of interrupt offers very high operating speed, but it is in certain ways a very simple and rather limited form of interrupt.

An important point to bear in mind regarding interrupts is that the microprocessor only saves (on the stack) and restores the contents of the program counter. If any other registers, such as the IX or IY index registers, will have their contents altered by the interrupt routine, it is up to the programmer to provide a routine to save these on the stack and then restore them again at the end of the interrupt routine. The programmer is also responsible for resetting the interrupt bit of the device which generated the interrupt once the interrupt has been serviced.

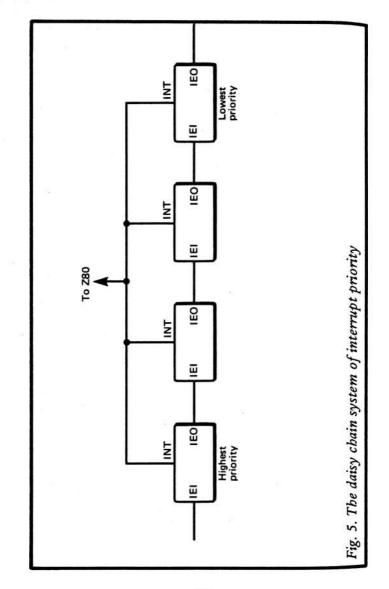

The third interrupt input of the Z80A is the ordinary interrupt (INT) input. This can be masked by the programmer and is the lowest priority interrupt input. There are instructions which give three interrupt modes using INT, and these modes will be briefly described here.

## Mode 0

This is the normal interrupt mode which is obtained when the device is reset or by using the appropriate  $(IM_{0})$ instruction. It is the interrupt mode used on the  $808_0$ microprocessor incidentally. In principle it is very simple, with the microprocessor waiting for the device which provided the interrupt to provide the next instruction (usually CALL or RST which automatically preserve the program counter on the stack).

## Mode 1

This is very similar to using the NMI interrupt, and is a vectored interrupt. In this case the microprocessor automatically sotres the program counter on the stack and then sets the program counter to hexadecimal address 0038. This is where the interrupt routine or directions to the routine should be placed in memory.

## Mode 2

This is a powerful but quite complex interrupt mode. The basic scheme of things is to have the Interrupt register loaded with the high byte of an address, and the device which supplied the interrupt supplies the seven most significant bits of the low byte (bit 0 is always 0). This does not provide the start address of the interrupt routine. but instead directs the microprocessor to the correct entry in a table of up to 128 interrupt routine start addresses. This is a fast arrangement with the microprocessor being rapidly directed to the right routine, even though there may be many devices generating interrupts, and many interrupt routines. With most microprocessors, when an interrupt is received an interrupt routine has to be included which checks the interrupt flag in each interrupt generating

device until a flag that is set is found, and the source is identified. Interrupt mode 2 of the Z80A is more efficient if a large number of interrupt generating devices are used since it does not waste time polling devices that have not generated the interrupt. It is difficult to implement though unless the special Z80/Z80A peripheral devices are used in the computer.

With this mode the program counter is automatically stored on the stack.

The Reset input is taken low briefly at switch-on, and this starts the microprocesor in its initialisation sequence. It can also be used to take the computer back to this sequence at any time, such as after the computer has crashed. Many Z80A based computers have a Reset or break switch in some form or other, which simply pulls the Reset pin low when the switch is operated. As part of the inialisation process the program counter, together with the I and R registers, is set at zero and interrupts are disabled. The start-up routine therefore commences at address 0000 (but this is the start address of the computer's operating system, and not user supplied machine code routines).

The RD and WR pins are the read and write lines. The RD pin is placed low by the microprocessor when it reads a memory or input output device, and the WR line is placed low when it is writing data to an input/output or memory device. Of course, only one device at a time must output data onto the data bus, and normally only one device at a time must receive data from the microprocessor. Correct decoding of the address bus ensures that only one device is activated at any one time. The MREO and IORO lines are placed low to select a memory device or an input/output device respectively. The address on A0 to A15 is valid when MREO is low. but only A0 to A7 are valid when IORQ is low. In other words, the input/output address range is only from 0 to 255, but some 256 addresses is more than adequate in practice

The pins marked  $\phi$  is the clock input. The clock circuit of many microprocessors is built-in, but this is not the case with the Z80A. The purpose of the clock circuit is to simply provide a series of electrical pulses to the microprocessor, and it is these that move the component through the complex sequence of events that make up each instruction. The standard Z80 will operate with clock frequencies of up to 2.5 megahertz (i.e. 2.5 million pulses per second), and it is normally used with a clock frequency at something in the region of 2.5MHz so that it carries out instructions at something approaching the highest rate possible. The more popular Z80A operates at clock frequencies of up to 4MHz, and can therefore perform a given task correspondingly faster. When using the Z80/Z80A (or any microprocessor) in an application where high operating speed is important it must be remembered that each instruction takes several clock cycles, and that a clock frequency of 4 megahertz does not equate with 4 million instructions per second. The number of cycles taken to execute an instruction varies from one instruction to another, but for the Z80/Z80A it is typically about eight clock cycles.

The purpose of the WAIT input is to enable the microprocessor to be slowed down to a rate that can be matched by a slow memory device. The HALT output indicates that a HALT instruction has been performed, and the microprocessor then performs continuous NOP (no operation) instructions until an interrupt is received. MI is an output, which goes low, together with IORQ, when an interrupt has been received. This can be used to acknowledge receipt of an interrupt from an input/output device.

# Chapter 2 ADDRESSING MODES

Addressing is the means by which the processor determines, from the instruction, the location of the data, or operand, on which the instruction will operate. The Z80 uses 7 address modes, and in general does not allow combinations of modes. However, where an instruction refers to two operands, it may be possible to use a different address mode for each. Thus an instruction may use absolute addressing for one operand, and indexed addressing for the other.

Many instructions can use more than one addressing mode. Though the mnemonic used is the same for all modes, the way in which the rest of the instruction is written in assembly language is different. The assembler will determine the correct opcode to use from the special symbols or syntax used to indicate some modes (e.g. enclosing items in brackets). When hand-assembling, care must be taken to select the correct opcode, and to provide the correct number of bytes after the opcode. These may vary with a given instruction depending on the address mode in use.

Full use of the available address modes is important to good programming, and it is important to understand them thoroughly.

## 1. Implied Addressing

This mode of addressing is used only by instructions which operate on one or more of the Z80's internal registers without requiring external data.

All these instructions are a single byte long.

Zilog make a distinction between implied addressing, which is limited to instructions which do not have a specific field to point to an internal register, and register addressing, for instructions which do.

Examples of instructions using implied or register addressing are ADC A,s; ADD A,r; AND s; CP s; LD r,r'; OR s; SBC A,s; SUB s; XOR s.

## 2. Immediate Addressing

In this mode, the operand is included in the program, immediately after the opcode. As the Z80 has both 8-bit and 16-bit registers, there are two types of immediate addressing, for 8-bit and 16-bit operands. The second, and possibly third, byte of the instruction contains the opcode, followed by the literal, which may be one or two bytes. Thus the total length of some instructions using this mode is 5 bytes.

Examples of instructions using this mode are ADD A,n (two bytes); LD dd,nn (three bytes); LD r,n (two bytes).

When the operand is two bytes long, this mode is referred to as immediate extended.

It is by this mode that constant data is included in a program.

#### 3. Absolute Addressing

In absolute addressing, the location of the operand in memory is specified in the instruction. Two bytes are used, so any position in the available 64k may be specified. This is the means by which variable data may be accessed by the program.

These instructions are three bytes long.

This mode is also called extended addressing, by contrast with short addressing using an 8-bit address.

Examples of instructions using this mode are LD A,(nn), which means load the accumulator with the contents of memory location nn and JP nn, which means jump to memory location nn.

# 4. Zero Page

In zero-page addressing, an 8-bit address is provided, this being an address in the first page of memory (i.e. the high byte is assumed to be zero). However, this mode is not used in the Z80, with the exception of the RST instruction. This is a single-byte instruction, the effective address being contained in bits 5. 4, and 3. It can thus point to 8 addresses in zero page, eight bytes apart. This instruction is mostly used in interrupt handling.

## 5. Relative Addressing

With the Z80, this addressing mode is used only with jump relative instructions.

In relative addressing, the byte following the instruction contains a displacement, which is regarded as a signed number between -128 and 127. If the program branches, this displacement is added to the contents of the program counter, causing a jump forwards or backwards. Note that the displacement is the number of memory locations, not the number of instructions.

With most assemblers, you specify the address of the memory location to which the program is to branch, and the assembler calculates the displacement for you.

All instructions using this mode are two bytes long.

Something to bear in mind if timing is critical is that the time taken by a conditional jump relative instruction depends on whether or not the condition is met. If it is met, the instruction will take 12 T-states to execute, as a new address has to be loaded into the program counter. If it is not met, the instruction only takes 7 T-states.

#### 6. Indirect Addressing

In indirect addressing, two bytes following the opcode contain a memory address. The contents of this address, and the byte that follows it, give a further address, which is where the data is to be found.

In fact, very few microprocessors allow indirect addressing, and the Z80 does not allow it in this form. It does, however, allow register indirect addressing, where each of the 16-bit register pairs BC, DE, and HL, may be used as a memory address.

When the registers are used to point to two-byte data, the address in the registers is the address of the low byte, the high byte being at the next higher address in memory.

## 7. Indexed Addressing

In indexed addressing, the address specified in the instruction is modified by the contents of one of the index registers IX and IY. The contents of the register are added to the address to give the final address from which the data is retrieved.

This is most commonly used to access successive elements of a table.

Instructions using indexed addressing include ADD, CP, INC, RLC and SET.

For historical reasons, all instructions using indexed addressing have opcodes two bytes long.

# Chapter 3 THE INSTRUCTION SET

The following list is the full set of Z80 Z80A instructions. including all the variations on each instruction where appropriate. They are listed in alphabetical order, and in addition to the mnemonics the code numbers (in hexadecimal) are also given. Details of any changes to the status flags produced by each instruction are also detailed. Note that a number of Z80 Z80A instructions are two or even three bytes long, plus an additional byte or bytes in some cases (a two byte address following an absolute instruction for example). The number of clock cycles (sometimes called T-states) taken to execute each instruction is included, and provided the clock frequency of the system you are using is known, the execution time for each instruction can be calculated from this. For example, with a clock frequency of 4MHz (4 million cycles per second), an instruction which requires 8 clock cycles obviously lasts 2 millionths of a second (2 microseconds). Do not confuse clock cycles and machine cycles. Instructions are broken down into a sequence of steps by the microprocessor, and each group of steps is called a machine cycle. The most simple of instructions take one machine cycle, but most take more than this. A machine cycle lasts at least three clock cycles incidentally.

## ADC A,s

Adds the operand (together with the carry flag) to the accumulator. The result is placed in the accumulator. There are several versions of this instructions:—

| CE           |

|--------------|

| 8F           |

| 88           |

| 89           |

| 8A           |

| 8 <b>B</b>   |

| 8C           |

| 8D           |

| 8E           |

| DD 8E offset |

| FD 8E offset |

|              |

The N flag is set to zero, other flags are altered depending on the result of the operation.

Clock cycles, immediate and indirect = 7, implicit = 4, indexed = 19.

## ADC HL,ss

Adds the contents of the HL register pair to a second register pair (ss). The carry flag is then added and the result is place in HL.

| BC | ED 4A |

|----|-------|

| DE | ED 5A |

| HL | ED 6A |

| SP | ED 7A |

The N flag is set to zero, H is set if there is a carry from bit 11, the other flags are altered depending on the result of the operation.

15 clock cycles.

# ADD A,(HL)

Adds the contents of the accumulator to the indirectly addressed (HL) memory location. Result is placed in accumulator.

Code number 86

The N flag is set to zero, the other flags are altered depending on the result of the operation.

7 clock cycles.

#### ADD A, (IX+d)

Adds the accumulator to the memory location addressed by IX and offset d. The result is placed in the accumulator.

Code numbers DD 86 offset

The N flag is set to zero, the other flags are altered depending on the result of the operation.

19 clock cycles.

#### ADD A,(IY+d)

Adds the accumulator to the contents of the memory location addressed by IY and offset d. The result is placed in the accumulator.

Code numbers FD 86 offset

The N flag is set to zero, the other flags are altered depending on the result of the operation.

19 clock cycles.

## ADD A,n

Adds the contents of the memory location following the

instruction to the accumulator, where the result is stored

Code number C6

The N flag is set to zero, the other flags are altered depending on the result of the operation.

7 clock cycles.

## ADD A,r

Adds the contents of the specified register (r) to the accumulator, where the result is stored.

| Α | 87 |

|---|----|

| В | 80 |

| С | 81 |

| D | 82 |

| E | 83 |

| н | 84 |

| L | 85 |

The N flags is set to zero, the other flags are altered depending on the result of the opertion.

4 clock cycles.

#### ADD HL,ss

Adds the contents of a specified pair of registers to the HL pair. The result is placed in HL.

| BC | 09 |

|----|----|

| DE | 19 |

| HL | 29 |

| SP | 39 |

The N flag is set to zero, C flag is reset unless there is a

carry from bit 15, and the H bit is set by a carry from bit 11.

11 clock cycles.

# ADD IX,rr

The contents of the specified pair of registers is added to IX, where the result is stored.

| BC | DD 09 |

|----|-------|

| DE | DD 19 |

| IX | DD 29 |

| SP | DD 39 |

The N flag is set to zero, C flag is set by a carry from bit 15, and the H bit is set by a carry from bit 11.

15 clock cycles.

#### ADD IY,rr

The contents of a specified pair of registers are added to the IY register, where the result is stored.

| BC | FD 09 |

|----|-------|

| DE | FD 19 |

| IY | FD 29 |

| SP | FD 39 |

The N flag is set to zero, the C flag is set by a carry from bit 15, and the H bit is set by a carry from bit 11.

15 clock cycles.

## AND s

The accumulator is logically "ANDed" with the specified data, and the result is placed in the accumulator.

Logical ANDing requires some further explanation. The two bytes are compared on a bit by bit basis, and a 1 is placed in a bit of the answer only if there is a 1 in that bit of both the ANDed numbers.

For example:

| Byte 1 | 11110000 |

|--------|----------|

| Byte 2 | 01010101 |

| Answer | 01010000 |

There are several addressing modes available with this instruction.

| Immediate     | E6           |

|---------------|--------------|

| Implicit (A)  | A7           |

| Implicit (B)  | A0           |

| Implicit (C)  | A1           |

| Implicit (D)  | A2           |

| Implicit (E)  | A3           |

| Implicit (H)  | A4           |

| Implicit (L)  | A5           |

| Indirect (HL) | A6           |

| Indexed (IX)  | DD A6 offset |

| Indexed (IY)  | FD A6 offset |

The C and N flags are set to zero, the H flag is set to 1, the S, Z, and P/V bits are altered depending on the result of the operation.

Clock cycles, immediate and indirect = 7, implicit = 4, indexed = 19.

#### BIT b,(HL)

A memory location is specified using the HL registers,

and then a specified bit of that memory location is tested and the Z flag is set accordingly.

| Bit 0 | CB 46 |

|-------|-------|

| Bit 1 | CB 4E |

| Bit 2 | CB 56 |

| Bit 3 | CB 5E |

| Bit 4 | CB 66 |

| Bit 5 | CB 6E |

| Bit 6 | CB 76 |

| Bit 7 | CB 7E |

The H flag is set to 1, the N flag is set to zero, the S and **P/V** flags are altered randomly.

12 clock cycles.

#### BIT b,(IX+d)

This is the (IX) indexed version of the previous instruction.

Code numbers DD CB offset BIT