### Set 29: Analogue multipliers—1

### Quarter-squares multiplier

#### Description

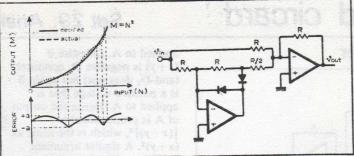

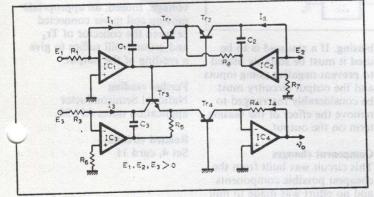

Quarter square multipliers are found frequently in analogue/hybrid computers in which their high accuracy (0.05% of half scale) is required and their limited bandwidth (less than 10kHz) is no disadvantage.

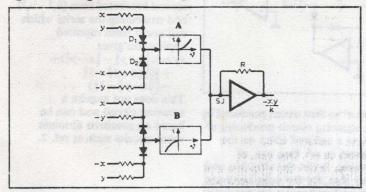

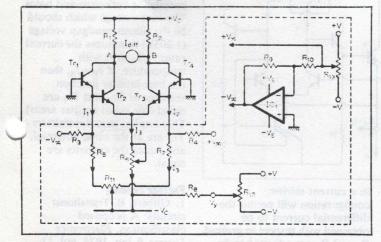

ley implement the relationship  $xy = \frac{1}{4}[(x+y)^2 - (x-y)^2]$  i.e. multiplication based on a square law device—this is

usually a diode function generator permanently set to provide a square law action. Such generators are usually single quadrant devices, e.g. A (above) requires a positive input and this necessitates the use of an absolute value circuit prior to it. If, for instance, (x+y) is positive then  $D_1$  conducts (and  $D_2$  does not) and a positive voltage is

applied to A. Likewise if (x+y) is negative  $D_2$  conducts (and  $D_1$  does not) but again it is a positive voltage that is applied to A. Hence the output of A is proportional to  $|(x+y)|^2$ , which is the same as  $(x+y)^2$ . A similar argument applies to the other absolute value circuit, B; being a 3rd quadrant device, it produces a current proportional to  $-(x-y)^2$ .

The constant k appearing in the output expression depends on R and on the output characteristics of A and B. Generally, if the maximum value of X and Y is say P volts, then k is set to P. If an absolute value circuit does not precede the squaring section then a total of four squaring sections are necessary. Despite the apparent increased complexity this is still sometimes done to avoid errors due to the diodes  $D_1$  and  $D_2$

## wireless world circard

### Set 29: Analogue multipliers—2

### V-f converter multiplier

#### Circuit description

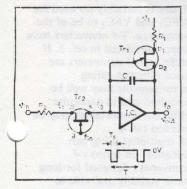

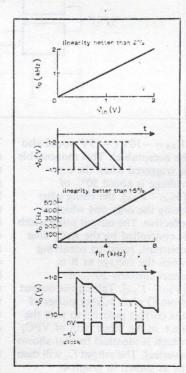

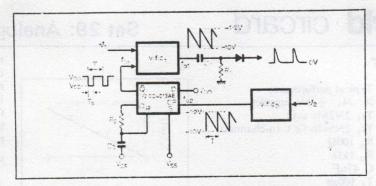

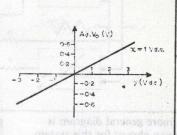

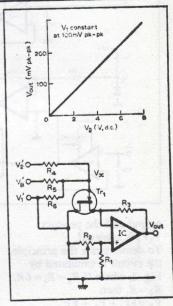

The circuit is a modification of the v-f converter described in ref. 1. The f.e.t.  $Tr_2$  is the only addition. Graph 1 was obtained with f.e.t. permanently conducting, i.e.  $V_{gs} = 0$  ( $f_{in} = 0$ ), and shows  $f_0$  to be proportional to  $v_{in}$ . This graph was obtained with  $v_1$  set to 3.3V which setting gave an  $f_0$  of 2kHz with  $v_{in} = 2V$ . Control of

Typical performance IC 741,  $\pm 15V$  supplies  $Tr_1$  2N2646 u.j.t.  $Tr_2$  2N5486 f.e.t. (n-channel)  $R_1$  100 $\Omega$   $R_2$  1k $\Omega$

C 47nF T<sub>s</sub> 100μs Pulse height -5V

the relationship between fo and vin depends on the u.j.t. breakdown voltage and this is variable from device to device. The v-f conversion can be described as a conversion first from vin to i1 and secondly from i1 to fo. The greater i1 the more rapidly does the capacitor charge and the more rapidly is the breakdown condition of the u.j.t. met. The downwards ramp of graph 2 shows this charging. On breakdown the u.i.t. shorts the capacitor so the output voltage

rises towards zero until the u.j.t. assumes its normal non-conducting role.

If now pulses are fed to the f.e.t. gate as shown, i<sub>1</sub> will become a train of current pulses i<sub>2</sub>. f<sub>0</sub> then depends on i<sub>2</sub>.

$f_0 = k i_2 = k i_1 \cdot \frac{T_s}{T} = k \frac{v_{\text{in}}}{R_2} T_s \cdot f_{\text{in}}$  $= k_1 v_{\text{in}} f_{\text{in}}$

Graph 3 shows that  $f_0$  is indeed proportional to  $f_{in}$ , the proportionality between  $f_0$  and  $v_{in}$  being shown in graph 1. The multiplying action is thus experimentally verified. If  $f_{in}$  is derived from another v-f converter we have  $f_{in} = k_2 v'_{in}$  and then  $f_0 = k'' v_{in} \cdot v'_{in}$  so that  $f_0$  is proportional to the product of two voltages.

Component changes. The value of  $R_2$  quoted i.e.  $1k\Omega$  is the absolute minimum usable.  $R_2$  should be much larger than the f.e.t. "on" resistance ( $\approx 200\Omega$ ). Max.  $R_2 \approx 100k\Omega$ ;

and to provide further functions.

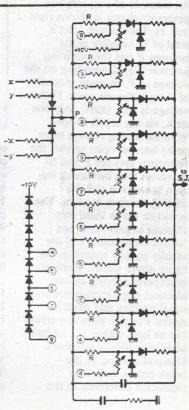

An example of a square law generator circuit is shown right (ref. 1). The current i has a total of 10 possible paths between P and the summing junction (SJ). Depending on the voltage at P, however, not all of these paths are open. If the voltage is very small, only one path, via the top R is open. With increasing voltage more paths become open so that the resistance between P and SJ decreases thus increasing the gain between P and the amplifier output in steps. The points at which these step changes in gain occur are termed breakpoints and are usually equally spaced as the figure above shows. Uniform breakpoint spacing allows identical slope increments and equal positive and negative errors. For this situation errors can be kept within x% of half scale with  $10/\sqrt{x}$  segments. Unequal spacing of the break-points makes no significant difference to the

overall accuracy although it is common to have one or two extra breakpoints near zero for improved accuracy. The use of the diode string to provide some of the biasing functions provides temperature compensation as well. The capacitors shown increase the frequency response.

#### Related circuits

If bandwidth is not essential but increased accuracy is, then use can be made of the relationship  $m^2 = \frac{1}{4}(1 + 2u + u^2)$ where u=2|m|-1. The right hand side of this equation is not totally dependent on u2 so that errors produced by a squaring circuit producing u2 have a reduced effect on the errors in m2. One can, of course, invert the situation and say that, for the same accuracy, fewer breakpoints are necessary and a less expensive squarer is produced. A "card" mechanising the right hand side of the equation is simply inserted as the A card in the circuit overleaf and with minor modifications a B card is produced. If we now examine

and apply the above equation © 1976 IPC Business Press Ltd

for m we obtain  $xy = \frac{1}{4} \left[ 2(u_1 - u_2) + (u_1^2 - u_2^2) \right]$  $=\frac{1}{2}(|x+y|-|x-y|)+$  $\frac{1}{4}(u_1^2-u_2^2)$ Reapplying the formula on the second bracketed term  $(u_1^8 - u_2^8)$ and truncating the series which will result from repeated application gives  $xy \approx \frac{1}{4}(|x+y| - |x-y| + \frac{1}{4}(|x+y| - 1|$ -||x-y|-1|This does not require a

squaring circuit and can be based on precision absolute value circuits such as ref. 2.

References 1. Whigham, R. H. Fast 10-V quarter-square multiplier. Simulation 1965. 2. Set 4, card 3. Korn and Korn. Electronic Analog and Hybrid Computers, 2nd edition, McGraw-Hill.

beyond this op-amp input currents become considerable. The value of C is related to that for R2 as the ramp slope is  $1/R_2C$ . With C=4.7nF (and  $T_s = 10 \mu s$ ) we achieved a maximum fo of 10kHz. Higher values of fo are difficult to achieve because of chargestorage effects in the u.j.t. affecting the discharge time. Pulse height must be sufficient to cause pinch-off of f.e.t. but not so high as to cause breakdown. -1 to -10V with this device was satisfactory.

#### Circuit modifications

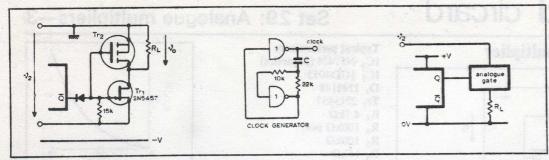

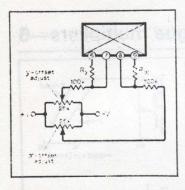

The circuit above shows a complete circuit whose output frequency, foi, is proportional to the product of the voltages v<sub>1</sub> and v<sub>2</sub>. The second voltage to frequency converter, VFC2, is assumed to be identical to that shown in the main diagram overleaf with the omission of the f.e.t. gate; it will therefore produce an output as shown in graph 2. This output is fed to the c.m.o.s. monostable shown (ref. 2) in which  $V_{\rm DD} = 0V$  and

$V_{\rm SS} = -10 \text{V} (-15 \text{V} \text{ would also})$ be acceptable). This monostable is triggered when the c.p. voltage is about 50% of  $[V_{\rm DD} - V_{\rm SS}]$ , the rising edge being the only one which is effective. The output pulse width is controlled by the R2C2 time constant, resetting occurring when the voltage at R is approximately 50% of  $[V_{\rm DD} - V_{\rm SS}]$ . Taking the output from Q gives trigger pulses of the correct polarity to gate the f.e.t. in the input path of VFC1 which is identical to that shown overleaf. The output for will then be as shown in graph 4.

The network comprising C1, R1 and D<sub>1</sub> is simply a differentiating network to produce a somewhat more normal type of pulse train. Note that fin is equal to for and that for must be less than fin. In fact consideration of the operation of the system overleaf shows that fin should be of the order of ten times the desired for. Hence VFC2 must operate at a much higher frequency than VFC1 and consequently the input resistors and feedback capacitors will be different. Voltages v1 and v2 also affect the frequencies of operation. As the maximum frequency

attainable from a unijunction type of v-f converter is of the order of 10kHz it may be necessary to use different types for a particular application. There is certainly no need for VFC<sub>1</sub> and VFC<sub>2</sub> to be of the same type. V-f converters have been considered in ref. 3. If different v-f converters are used different gating arrangements may well be required and in particular different monostables may be needed ref. 4. A multiplier using two identical (in form) v-f

converters designed for long term stability and able to accommodate floating inputs is described in detail in ref. 5.

#### Related circuits

Set 21, V-f converters, card 1 Set 19, Monostables, card 8 Set 21, V-f converters Set 19, Monostables Versatile integrator-multiplier, E. Ljung and S. Berglund, Electronic Engineering, Aug. 1974, pp. 38-40.

### Set 29: Analogue multipliers—3

### Delta-sigma modulator/multiplier

Circuit description

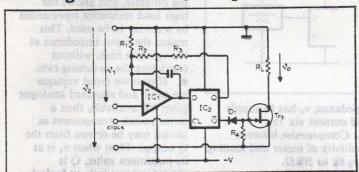

If an output waveform has a constant pulse height and width but the pulse-rate is proportional to an input voltage, then the mean value of the output is also proportional to that voltage. If the pulse height is made proportional to

econd voltage the mean tput becomes proportional to the product of the two voltages. A delta-sigma modulator converts a pulse-train into one with a smaller number of pulses, using an integrator to control the voltage on the D input of a flip-flop. As the mean voltage at the inverting and non-inverting inputs are the same and the mean current in the capacitor is zero, the fraction of the time for which Q is high is controlled by the input voltage v<sub>1</sub>. The circuit configuration has a negative

Typical performance IC<sub>1</sub> N574N (Signetics) IC<sub>2</sub>  $\frac{1}{2}$ CD4013 D<sub>1</sub> 1N4148 Tr<sub>1</sub> 2N5457 R<sub>1</sub> 4.7k $\Omega$  R<sub>2</sub> 100k $\Omega$  pot. R<sub>3</sub> 100k $\Omega$  R<sub>4</sub> 15k $\Omega$  R<sub>L</sub> 15k $\Omega$  Supply -10V v<sub>1</sub>, v<sub>2</sub>  $0 \rightarrow -1$ V v<sub>0</sub>  $0 \rightarrow -1$ V

$|v_0| = v_1 v_2$

input voltage and supply because it was desired to use the simplest arrangement, and certain op-amps (e.g. Signetics 741) have an input commonmode range that includes the positive supply rail. The circuit can be adapted for any other op-amp by providing a separate positive bias. With dual supplies the system may equally be used with positive inputs and outputs if the

flip-flop is powered from the positive rail.

The  $\bar{Q}$  output is used to gate a junction f.e.t. on and off. With  $\bar{Q}$  high (zero volts), the diode is non-conducting and  $R_4$  establishes zero gate-source bias. With  $\bar{Q}$  low (-V) the f.e.t. is off. This is true provided the second input voltage  $v_2$  is small so that the reverse gate-source voltage is in excess of the pinch-off voltage. The load receives voltage pulses of duration equal to the inter pulse period and just less than  $v_2$  in

# wireless world circard

## Set 29: Analogue multipliers—4

### Log-antilog multiplier

Components

IC<sub>1-4</sub> 741 (e.g. RC4136 quad package)

Tr<sub>1</sub> to Tr<sub>4</sub> 1/5 CA3086

R<sub>1</sub>, R<sub>2</sub>, R<sub>3</sub>, R<sub>6</sub>, R<sub>7</sub> 100k $\Omega$ R<sub>4</sub> 10k $\Omega$ , R<sub>5</sub> 2.2k $\Omega$ C<sub>1</sub> 300pF, C<sub>2</sub> 200pF

C<sub>3</sub> 22pF

All passive components  $\pm 5\%$

Supply voltage ±7.5V

Performance

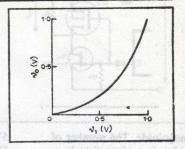

It can be shown (see text) that  $v_0 = E_1 E_3 R_2 R_4 / E_2 R_1 R_3$ . With the resistor values chosen, assuming perfect components,  $v_0 = E_1 E_3 / 10 E_2$  and so the circuit can be used as a squarer  $(E_1 = E_3 \text{ and } E_2 \text{ constant})$ , as a multiplier  $(E_2 \text{ constant } E_1 \text{ and } E_3 \text{ variable})$ , as a divider

$(E_9)$  as divisor  $E_1$  or  $E_3$  as dividend, the other fixed) or as a device for obtaining the reciprocal of  $E_2$  ( $E_1$  and  $E_3$ fixed). Results as a squarer are shown in graph 1 from which it will be noted that E2 was set at 0.92 rather than 1V to achieve the slope of 45° (making up for component inaccuracy) and that the maximum vo obtainable is less than 4V. Saturation of the transistors occurs at higher voltages. Graph 2 shows similar linearity for operation as a multiplier, multiplying the variable  $E_1$  by the constant  $E_5$ . Identical results were obtained when the roles of  $E_1$  and  $E_3$ were reversed. Similar linearity was obtained with the device operated as an arithmetic inverter (reciprocal).

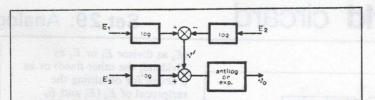

Circuit description

Analysis of the circuit is as follows:

$$I_1 = E_1/R_1$$

and  $V_{be_1} = \frac{kT}{q} \log_e i_1$

$i_2 = E_2/R_2$  and  $V_{be_2} = \frac{kT}{q} \log_e i_2$

$V' = V_{be_2} - V_{be_1} = \frac{kT}{q} \log_e \frac{E_2R_1}{E_1R_2}$

$V_{be_4} = -V' + V_{be_3} = \frac{kT}{q} \log_e \frac{E_1E_3R_2}{E_2R_1R_3}$  (1)

as  $V_{be_3} = \frac{kT}{q} \log_e i_3$  and  $i_3 = E_3/R_3$

magnitude. The number of pulses in a given time is proportional to  $v_1$ . Hence the mean load voltage is  $\propto v_1v_2$ . This can be read directly on a moving-coil meter, or filtered and fed to a d.v.m.

Component changes

IC<sub>1</sub>: Any op-amp if supply requirements observed. Output is always close to the flip-flop threshold voltage i.e. does not approach either supply line. Supplies can be single-ended negative or positive depending on op-amp. Must be large enough to gate f.e.t. 6 to 15V. Tr<sub>1</sub>: Any n-channel junction f.e.t. with pinch-off below, say,

5V. Low on-resistance preferred. D<sub>1</sub>: General purpose switching diode.

IC<sub>2</sub>: Any c.m.o.s. D-type flip-flop (set and reset grounded).

$R_1$ ,  $R_2$ ,  $R_3$ : Ratio sets 'gain' i.e. usual potential divider relationship defines ratio of mean output at Q to  $v_1$ . Total resistance 10k to 10M $\Omega$ . Suggested ratios 5: 1 to 20: 1.  $R_4$ : If too high, results in slow switching of f.e.t. from off-on state with reduced overall accuracy. If too low, additional current places unwanted extra load on  $v_2$  source.  $v_1$ ,  $v_2$ : Typically  $0 \rightarrow -1V$ .  $v_1$  feeds into very high

© 1976 IPC Business Press Ltd

impedance,  $v_2$  has to supply load current via  $Tr_1$ .  $R_L$ : Compromise between sensitivity of meter and loading of  $v_2$  5k to 50k $\Omega$ .

Circuit modifications

• To improve switching times without adding an extra i.c., it is possible to use a p.m.o.s. transistor from a CD4007 package. If the remainder of the package is connected as in the circuit shown, a clock generator results. Frequencies from 10kHz to > 100kHz have been tested with this system. In general clock rates of several MHz are feasible but would

make heavy demands on the analogue switches. The p.m.o.s. device prevents charge storage across the load resistance in the off-state, and allows the high load resistance represented by a d.v.m. to be used. This makes the input impedance at the v<sub>2</sub> input high, without restricting the switching rate.

• If positive input voltages are used, and standard analogue gates are available, then a series switch arrangement as shown may be driven from the Q output. Then when  $v_1$  is at its maximum value, Q is almost permanently at logic 1 and  $v_2$  is gated through to the load for almost 100% of the time. A shunt gate driven from Q completes the configuration for higher switching speeds or where  $R_L$  is to be raised.

In principle this can be interpreted as a combined V<sub>1</sub>-f and V<sub>2</sub>-amplitude converter system.

Related circuits Set 15, card 9

But  $\log_{e_4} = qV_{\text{be}_4}/kT$  and  $I_4 = V_0/R_4$  Combining this last pair of equations with equation 1 gives

$V_0 = \frac{E_1}{E_2} E_3 \cdot \frac{R_4}{R_3} \cdot \frac{R_2}{R_1}$

A functional block diagram following from these equations is shown, right. The antilog function is performed by Tr<sub>4</sub> and IC<sub>4</sub>. Principally it is Tr<sub>4</sub> which performs the antilog function in converting its base-emitter voltage to a current: IC<sub>4</sub> and R<sub>4</sub> convert this current to a voltage, viz. V<sub>0</sub>.

The above analysis concerned d.c. conditions only, so all capacitors were ignored. Likewise R<sub>5</sub> and R<sub>8</sub> were ignored. The function of all of these components is to stabilize the loops in which they are contained. To see this, consider the simplest case viz. IC<sub>3</sub> and its associated circuitry. The loop gain of this circuit is the open-loop gain of IC<sub>3</sub> together with the gain of Tr<sub>3</sub> which is in common base mode and has a voltage gain given

approximately by gm×the load on Tr3. The load on Tr3 is R3 (by superposition the E<sub>3</sub> input end of R<sub>3</sub> is at ground). This voltage gain gmR3 is large and the overall loop gain is, therefore, considerably enhanced and instability is a considerable problem. The inclusion of R5 reduces the feedback path gain as only a portion of the i.c. output voltage is applied to the base-emitter junction. For high frequency effects C3 completely shorts out this feedback path amplifier, again improving stability. Note that gm depends on the operating conditions i.e., in this case, on E<sub>3</sub> so that the problem is complex indeed. Note that all the input voltages must be positive to maintain correct transistor

biasing. If a sinusoid is to be used it must be suitably biased to prevent negative going inputs and the output circuitry must be considerably rearranged to remove the effect of the biasing term on the output.

Component changes

This circuit was built from the cheapest possible components and no effort was made to null the i.cs. Considerable improvement in accuracy is obtainable if the resistors R<sub>1</sub>R<sub>2</sub>R<sub>3</sub> and R<sub>4</sub> are chosen to a much tighter tolerance. Nulling of i.cs will improve performance as will the use of i.cs with facility for feedforward compensation e.g. LM301 etc. The use of i.cs with very low input currents e.g. LM108 or f.e.t. input i.cs such as CA3130

will improve the lower end of the input range. These comments do not apply strictly to IC<sub>4</sub> which simply converts the current through Tr<sub>4</sub> to a voltage. Indeed, an appropriate moving coil meter connected between the collector of Tr<sub>4</sub> and ground will suffice to give a reading of the output.

Further reading National Semiconductor application notes AN-30.

Related circuits Set 4, card 11

© 1976 IPC Business Press Ltd

### Set 29: Analogue multipliers—5

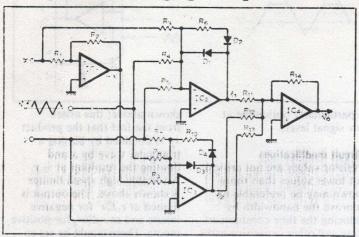

### Triangle-wave averaging multiplier

Components

R<sub>1</sub> to R<sub>14</sub> 120kΩ IC, 741 D<sub>1</sub> PS101 pplies -- 15V

Performance

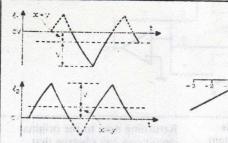

With v set at 4V and the

frequency of the triangular waveform set at 1kHz graphs 1 and 2 were obtained. Linearity shown in graph 2 is better than 1%. Note that x and y are direct voltages and vo is the average voltage at the output of IC4. vo is, of course, the

inverted sum of e1, e2 and y. With x and y both at 1V and varying the frequency of the triangular wave the output accuracy was maintained within 1% up to 6kHz. The device is a 4-quadrant multiplier.

Description

The block comprising IC2, R3, R<sub>4</sub>, R<sub>5</sub>, R<sub>6</sub>, D<sub>1</sub> and D<sub>2</sub> is a precision half-wave rectifier producing a negative output equal in magnitude to the sum of the input voltages when that

sum is positive. The block producing e2 can likewise be described. The sum of e, e, and y produces the output and at first sight the multiplier appears related to time-division (a.m./p.w.m.) multipliers. Analysis shows however that this multiplier is more closely related to the quartersquare multiplier, the reason being that the height of e2 is closely related to the base of hatched triangle in graph 1 so that the area of the triangle becomes a square function.

## wireless world circard

### Set 29: Analogue multipliers-

### Four-quadrant multiplier—characteristics

Pin designation

2 multiplier outputs x input 4 common

5 y input 6 and 7 y gain

8 and 9 x gain

10 negative supply

11 op-amp output

12 compensation

non-inverting op-amp input

inverting op-amp input

15 high-frequency output

16 positive supply

#### Description

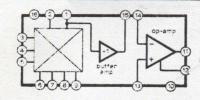

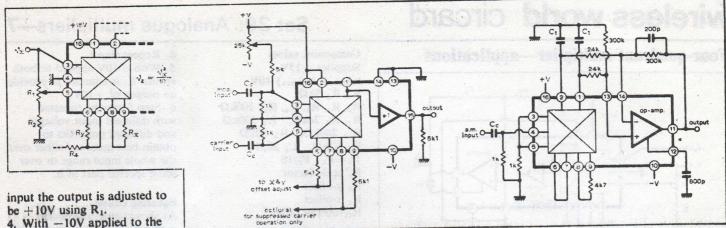

The XR-2208/2308 is an op-amp combining a fourquadrant analogue multiplier, a high-frequency buffer amplifier and a differential-input op-amp on the same monolithic integrated circuit. The package is suitable for arithmetic operations and communication

signal processing, maximum versatility being achieved by internally separating the amplifier and the multiplierbuffer section; suitable interconnections being made externally with passive components. The op-amp can be used as a post-detection amplifier in coherent detector

applications or as a preamplifier for low-level input signals. The output from the buffer amplifier can be used for high-frequency signal processing, the multiplierbuffer section having a smallsignal 3dB bandwidth of 8MHz and a transconductance bandwidth of 100MHz. The package can be operated from symmetrical supply rails in the range  $\pm 4.5$  to  $\pm 16$ V. Very good power supply rejection and temperature stability are achieved by internally-regulating current and voltage levels. The multiplier inputs x and y are applied to pins 3 and 5 respectively, with pin 4 common-normally the reference or ground terminal. However, in some applications x and y inputs are strapped together and pin 4 used as an input terminal. The d.c. bias currents at pins 3 and 5 are

typically 3µA and at pin 4 typically 6µA. The differential output voltage (vo) between pins 1 and 2 is often connected directly to the op-amp (pins 13 and 14), the final output (vz) being obtained from pin 11.

$$v_0 \approx \frac{25}{R_X \cdot R_Y} v_X \cdot v_Y$$

where all voltages are in volts and the gain control resistances

A more general diagram is shown above: for this system it can be shown that the average value of  $V_0$  is:

$$-\frac{R}{R} \text{ (average of } e_1 + \text{ average of } e_2 + by)$$

$$= -\frac{R'}{R} \left[ \frac{-1}{4cV} (cV + ax + by)^2 - \frac{1}{4cV} (cV + ax + by)^2 + by \right]$$

If  $R' = \alpha R$ , then this expression simplifies to

$$V_{\text{onv}} = \alpha xy \frac{ab}{cV}$$

Comparing this with the circuit overleaf we see that we have x-a-b-1 and cV-4.

Returning now to the original circuit one can observe that the somewhat restricted input range is due to the fact that at no point should the bias voltage exceed the peak of the triangular wave. Clearly the input signal size can be increased by increasing the carrier magnitude and also by introducing factors a and b, reducing the effective input. The effect of these changes can be then cancelled by setting  $R' = z \ c V/ab$ .

The circuit is sensitive to d.c. components in the carrier and also to the carrier magnitude. The effect of a d.c. component

is particularly noticeable at low signal levels.

Circuit modifications

Resistor values are not critical but lower values than those shown may be preferable to improve the bandwidth by reducing the time constants of stray and other capacitive paths. Resistor R' may be replaced by a filter to remove the a.c. components of V<sub>0</sub>. The d.c. impedance of such a filter should still equal R'. The system bandwidth can be increased by using a faster version of half-wave rectifiers<sup>1</sup>.

• An alternative scheme is

from the fact that the product xy is obtained by biasing a triangular wave by x and limiting the resultant at  $\pm y$ . A suitable high speed limiter is shown above. The output is limited at  $r_1E/r'$  for negative inputs and at  $r_2E/r'_2$  for positive inputs. These would be set to  $\pm y$  respectively. Note that  $r_1r_2 \ll R$  for good limiting.

References

1. Set 22, card 3

2. Korn & Korn, Electronic Analog and Hybrid Computers, 2nd edition McGraw-Hill.

( $R_X$  and  $R_Y$ ) for the x and y sections of the multiplier are in  $k\Omega$ . Conversion gain of the multiplier is

$$K_{\rm M} \approx \frac{25}{R_{\rm X} \cdot R_{\rm Y}} (V^{-1})$$

resistors R<sub>X</sub> and R<sub>Y</sub> being connected as below; where the arrangement for adjusting the x and y offsets at pins 7 and 8 is also shown:

The operational amplifier is internally protected against short-circuit load conditions and can sink or source a current of 10mA into a resistive load. This amplifier can be compensated for unconditional

stability by connecting a capacitor (C<sub>C</sub>) of 20pF across pins 11 and 12. For higher voltage gains than unity, C<sub>C</sub> is reduced to increase small-signal bandwidth and to improve slew-rate.

The unity-gain buffer amplifier if brought into use by connecting a resistor from pin 15 to ground and provides a low-impedance output for the multiplier section when the latter is used at high frequencies, in order to minimize capacitive loading of the multiplier output proper. The buffer output is not short-circuit protected and typically has a direct voltage of  $V^+$  -4.5 volts. The maximum direct current extracted from pin 15 should not exceed 10mA. NOTE: When only the multiplier section or op-amp section is being used the input terminals of the unused section must be connected to ground. The maximum peak x or y input signal that can be used for a given supply voltage without significant improvement

of the linearity of the multiplier is shown below.

#### Further reading

XR-2208/2308 Operational multiplier data sheet, EXAR, 1972.

XR-2208 Operational Multiplier, New Electronics, 1 April 1975, pp. 27-31.

Related circuits Set 29, card 7

© 1976 IPC Business Press Ltd

© 1976 IPC Business Press Ltd

### Set 29: Analogue multipliers—7

### Four-quadrant multiplier—applications

#### 4-quadrant multiplierapplications

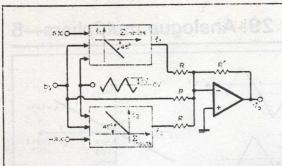

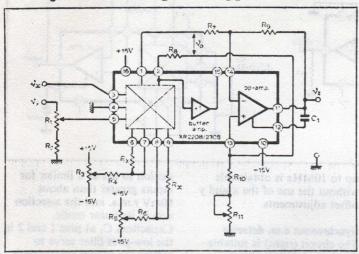

In most multiplication applications the operational amplifier and multiplier sections are interconnected as shown left providing a

single-ended output signal and having a wide dynamic range. With the values shown below, the linear output swing is typically 10V for maximum input signals of 10V with a scale factor K=0.1.

#### Component values

Supplies ±15V Vx(max); Vy(max) 10V  $R_1, R_2 5k\Omega$  $R_3$ ,  $R_4$ ,  $R_5$ ,  $R_6$ ,  $R_{11}$  100k $\Omega$  $R_7$ ,  $R_8$  24k $\Omega$ ,  $R_9$  300k $\Omega$   $R_{10}$  240k $\Omega$ ,  $R_x$  30k $\Omega$  $R_y$  62k $\Omega$ ,  $C_1$  20pF  $V_z = V_x \cdot V_y/10$ R, scale factor R<sub>3</sub> y-offset R<sub>5</sub> x-offset R<sub>11</sub> output offset

#### Setting-up procedure

1. With 0V applied to both inputs and the output offset is adjusted to be 0V with R11. 2. With a 20V pk-pk, 50Hz signal applied to the x-input and 0V to the y-input, R3 is adjusted to provide minimum output voltage.

3. With a 20V pk-pk 50Hz signal applied to the y-input and 0V to the x-input, R5 is adjusted to provide minimum output voltage.

4. Repeat step 1.

5. With +10V applied to both inputs, R<sub>1</sub> is adjusted to provide an output of +10V.

6. Step 5 may be repeated with different input voltages and different polarities to obtain best accuracy either over the whole input range or over some specific part of it.

#### Squaring circuit

As shown over, the circuit used for squaring is essentially that used for multiplication except that the input signal is applied simultaneously to the x and v input terminals and only one input offset adjustment is required.

Adjustment procedure is: 1. With 0V applied to the input the output offset is adjusted to be 0V using R11. 2. With +1V applied to the

input R<sub>3</sub> is adjusted to make vo 0.1V.

3. With +10V applied to the

## wireless world circard

### Translinear multiplier

#### Circuit description

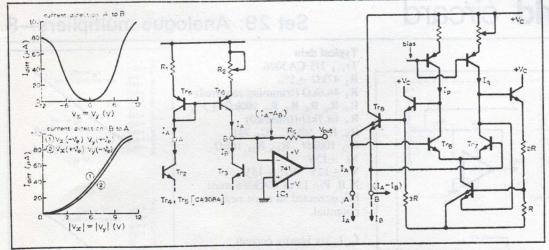

The circuit currents above are related to a defined current unit I, by the following:  $I_1 = (1+X)I/2 I_2 = (1-X)I/2$  $I_3 = (1 + Y)I$ where X and Y are controlled variables, and Idir between

Tr<sub>2</sub> and Tr<sub>3</sub> collectors is XY I. The circuit operates in the current domain and depends for its temperature independence on the proportionality of bipolar transistor gm (transconductance) to the collector current. Currents I1,

### Set 29: Analogue multipliers-

#### Typical data

Tr<sub>1-4</sub> 1/5 CA3086  $R_1 47k\Omega \pm 5\%$ R<sub>2</sub> 46.6kΩ (trimming required) R<sub>3</sub>, R<sub>4</sub>, R<sub>5</sub>, R<sub>7</sub>, R<sub>8</sub> 100kΩ ±5%  $R_6$  68.7k $\Omega$  (trimmed) R<sub>9</sub>, R<sub>10</sub> 50kΩ IC<sub>1</sub> 741  $R_{11}$  100k $\Omega$   $R_{12}$ ,  $R_{13}$  10k $\Omega$  $V_c \pm 15V$ V: ±12V Vs: ±15V N.B. Pin 13 of CA3086 must be connected to most negative potential.

sources, and the above network comprising Vx, Vy, resistors R3 to R<sub>7</sub> is an attempt to simulate such a condition e.g. I, is approximately equal to  $-V_{\rm e}/(R_7 + R_{11}/2) \approx 100 \mu \rm A plus$ steps of 1V. These calculations

I2, I3 are ideally current

a multiple of 100µA defined by  $V_x/R_4$  where  $V_x$  is increased in assume that the base-emitter junction voltages are negligible. To obtain a balanced condition where  $I_{\text{diff}} = 0$  if either  $V_x$  or

V<sub>y</sub> is zero demands trimming of resistor R6 and R2 to allow for the 1.2V potential at the emitters of Tr2, Tr3. Linearity of Idiff is shown in accompanying graphs. Note, that if  $V_x = +8V$ , this is equivalent to eight units of

be +10V using R<sub>1</sub>.

4. With -10V applied to the input check that the output is +10V, if this is not so repeat steps 1 to 3.

A.m. generator

The circuit (middle) is that recommended for generating double sideband signals or for suppressed-carrier a.m. generation. Modulation and carrier are applied to the x and y inputs respectively with a carrier level of 1V (r.m.s.). The level of the carrier appearing at the output is adjusted by

means of the 25kΩ up to 10MH without the d.c. level at pin 3. In suppressed-carrier applications, the carrier level at the output can be further reduced by means of the x and y offset adjustment controls. The buffer amplifier provides a unity gain low-impedance output, but if not required pin 15 should be open circuited to reduce power dissipation. Carrier suppression of 40dB up to 1MHz and 30dB

© 1976 IPC Business Press Ltd

up to 10MHz is obtainable without the use of the x and y offset adjustments.

Synchronous a.m. detector

The circuit (right) is suitable

for demodulation of a.m.

signals with carrier frequencies

up to 100MHz, with an input

signal of at least 25mV r.m.s.

The a.m. input is applied to

the common terminal of the

multiplier, the y-gain terminals

are strapped allowing this

section to act as a limiter for inputs greater than about 50mV r.m.s. and the x-section acts in its linear mode.

Capacitors C<sub>1</sub> at pins 1 and 2 in the low-pass filter serve to reduce the carrier feedthrough to the output.

Further reading XR-2208/2308 Operational multiplier data sheet, EXAR, 1972.

Related circuits Set 29, card 6

current, and if  $V_y = +2V$ , two units of current. Resulting product is 16.

Parameter changes

If X = Y, the output function is a squared function of those variables. Graphs of the resulting current variation are given above. For each graph, the effect of Y being negative causes a slight deviation from the true square law. Possibly

due to inexact compensation for V<sub>BE</sub> drops with network employed.

Component changes

Circuit is supply sensitive, especially at the low levels of current I. At  $V_c = \pm 15$ V, a 20% reduction of  $V_c$  provides a -3% error for  $I_{diff} = 81 \mu A$ , but at  $9\mu A$ , +30% error.

Circuit modifications

• Use of transistors Tr4, Tr5

in a current mirror configuration will permit the differential current to be obtained with respect to ground.  $R_1$  and  $R_2$  are adjusted to be similar to obtain equal collector currents in  $Tr_4$ ,  $Tr_5$ . This current is converted to an equivalent voltage by driving into  $IC_1$ , such that  $V_{\text{out}} = -(I_AI_B)R_S$ .

A more sophisticated technique<sup>2</sup>, with a wide

frequency response, is shown extreme right. Transistor Transis which has a double emitter, could be derived from a monolithic package by paralleling collectors and bases. The bias voltage which should be the silicon bandgap voltage (1.205V) minimizes the current ratio Ip/Iq drift with temperature. If  $I_p = I_q$ , then the base-emitter junction voltages of Tr, and Tr, are equal (for equal emitter areas). This implies that the emitters o' Tr<sub>8</sub> are at the same potential, and hence the currents are equal.

Further reading

1. Gilbert, B. Translinear circuits: A proposed classification, *Electronics Letters*, 9 Jan. 1975. vol. 11, no. 1.

2. Gilbert, B. Wideband negative current mirror, Electronics Letters, 20 March, 1975. vol. 11, no. 6.

3. Korn & Korn. Electronic analogue and hybrid computers McGraw Hill 1972.

© 1976 IPC Business Press Ltd

## Set 29: Analogue multipliers—9

### Hall-effect multiplier

Hall-effect multiplier

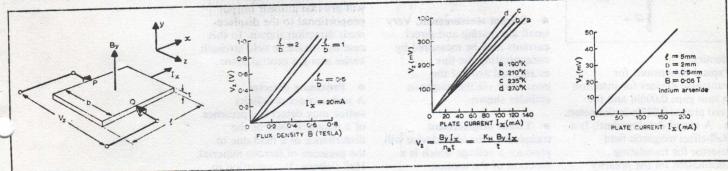

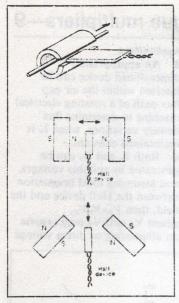

In a practical Hall plate, point electrodes between which the Hall voltage is developed are connected midway between the end-electrodes. Materials used for the plate are high mobility bulk semiconductors, with low conductivity: indium arsenide, germanium, indium antimonide.

#### Background

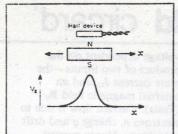

The device produces an output

voltage dependent on the product of two inputs—the plate current  $I_x$ , and an external magnetic field  $B_y$  (Tesla). Current flow is due to electrons n, charge q and drift velocity  $v_x$ . Hence current density

$J_x = I_x/bt = nqv_x$ . Deflecting force on electrons in

direction Z due to  $\mathbf{B}_y$  is  $F_z = \mathbf{B}_y q v_x$ .

At equilibrium, this just balances the field force due to electron deflection, i.e.  $qE_z$ ,

$B_yqv_x=qE_z$  and  $E_z=B_yv_x=B_yI_x/btnq$ The Hall voltage is  $V_z=E_zb$  $V_z=B_yI_x/mqt=K_HB_yI_x/t$  $K_H$  is known as the Hall coefficient and should be as large as possible for maximum output. Conductivity is  $\sigma=qn\mu_n$  where  $\mu_n$  is electron mobility  $K_H=1/qn=\mu_n/\sigma$

$K_{\rm H} = 1/qn = \mu_{\rm h}/\sigma$ High mobility, low-conductivity optimizes device Hall voltage for specific thickness t.

### Applications

An appropriately dimensioned device can be inserted within the air gap flux-path of a rotating electrical machine to determine flux density variations, when I<sub>x</sub> is maintained constant.

• Both  $I_x$  and  $B_y$  can be generated by suitable voltages, and assuming fixed orientation between the Hall device and the field, then  $V_z \alpha V_x V_y$ , where  $V_x$  and  $V_y$  may assume an alternating or direct voltage

# wireless world circard

## Set 29: Analogue multipliers—10

F.e.t. analogue multiplier

Circuit description

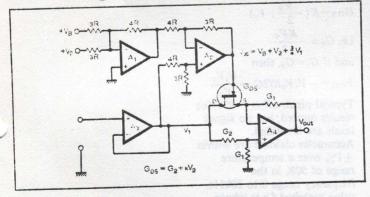

The conductance  $G_{DS}$  of the junction field-effect transistor depends on the voltage  $V_x$ . To linearize the f.e.t. in its pre-pinch-off region  $V_x$  must comprise one half of the sum of the separate drain and source voltages with respect to ground. In this case, that is equivalent to  $\frac{1}{2}(V_1 + V_1/2)$ . The

total gate-voltage is then a fixed bias voltage  $V_B$ , a signal voltage  $V_2$  and the required  $\frac{3}{4}V_1$  is obtained via  $A_3$  and  $A_2$ . With then the equivalence of conductances  $G_1$ , the output voltage  $V_{\rm out}$  is linearly proportional to the product of signals  $V_1$  and  $V_2$ , when  $G_{\rm DS}$  is equal to  $G_2$  plus an incremental value proportional

Typical data (simulation) IC SN741  $Tr_1$  2N5457  $R_1$ ,  $R_3$  330 $\Omega$ ,  $R_2$  1k $\Omega$   $R_4$ ,  $R_5$  22k $\Omega$ ,  $R_6$  6.8k $\Omega$  frequency 1KHz  $V_1$  maintained at 100mV pk-pk to achieve the best linearity. Linearity obtained is demonstrated on the graph.

to  $V_2$ . Equating the potentials at the inverting and non-inverting inputs of amplifier  $A_4$  and using the parallel generator concept then  $\frac{V_1(G_2+KV_2)+V_{\text{out}}G_1}{G_1+G_2+KV_2} = \frac{V_1G_2}{G_1+G_2}$

$$\frac{G_1+G_2+kV_x}{G_1+G_2} = \frac{G_1+G_2}{G_1+G_2}$$

This gives

$V_{\text{out}} = -\frac{KV_1V_2}{G_1 + G_2}$ The drain current drain-source

voltage relationship is  $I_{\rm D} \propto (V_{\rm G} - V_{\rm p} - \frac{V_{\rm D} + V_{\rm S}}{2}) V_{\rm DS}$

If  $V_G$  does comprise  $V_B$ ,  $V_2$  and  $(V_D + V_S)/2$ , then  $G_{DS} = I_D/V_{DS} \propto (V_B - V_P + V_2)$  for pre-pinch-off.

If the constant of proportionality  $K_1=K$ , and is such a value that  $K_1(V_B-V_p)=G_3$ , then a linearised relationship between the

Typical dimensions for transverse devices for insertion in thin gaps 0.006in and for axial probes 0.063in in diameter. A recent development<sup>1</sup>, is a Hall-effect magnetic field detector for translating

information on the polarity

and field strength of a magnetic into a differential output current using integrated circuit technology (Mullard TCA450A). This device offers a high level of sensitivity, low offset flux and is self-balancing. Typical supply voltage 4-16V. Magnetic sensitivity 0.4V/Tesla. Offset flux density  $\pm 7.5 \times 10^{-3}$ Tesla.

Possible applications include isolated current sensing and control in high current situations, conversion of magnetic quantities into proportional currents, detection of positional movements of a rotating shaft.

- Current measurement. Very small alternating and direct currents may be measured by concentrating the flux established around the conductor via the magnetic cylinder shown.

- Linear displacement transducer. The Hall device will produce a voltage which is a function of the motion

between the device and a stationary magnetic field. Displacement laterally between the magnets will produce an output voltage when the device is moved from the mid-position. An alternative arrangement will provide a linear output proportional to the displacement direction shown. In this case the magnetic field strength varies along a central plane.

**Proximity detector** A non-contact proximity switch may detect the presence of a magnetic field or the disturbance of a field due to the presence of ferrous material. Hall voltage, Vz, variation in © 1976 IPC Business Press Ltd

relation to relative position of magnetic and Hall device would be as shown.

#### References

Chasmer, R. P., Cohen, E., Holmes, D. P. Design and performance of a Hall-effect multiplier, Proc. IEE 106 Part B. Supplement 16, 1959. Newsome, J. P. Application of the Hall effect. Electronics & Power, April 1966.

1. Mullard News Bulletin, 1975.

output and the product  $V_1V_2$  is achieved. To demonstrate the principle, the circuit is simulated by Fig. 2, where if  $R_4 = R_5 = 6R$ ,  $R_6 = R$ , then  $V_{\rm x} = \frac{3}{4}V_1 + V_2' + V_{\rm B}'.$ To obtain the best linearity, these values of resistors need to be chosen empirically. This is most easily performed using an oscilloscope with an X-Y facility, where the input V<sub>1</sub>

and output for V2 zero volts are applied X-Y inputs respectively. Any non-linearity or offset can then be minimized by varying the resistors. A more practical circuit (see reference) includes temperature compensation by making G2 another voltage dependent conductance, using a matched field-effect transistor (above). For maximum signal amplitudes, f.e.ts with a high

pinch-off should provide a wider working range. Also if the gate bias VB is arranged to be one half the pinch-off value, then

$$G_{\rm DS} = K(-\frac{V_{\rm p}}{2} + V_{\rm p})$$

i.e.

$$G_2 = -\frac{KV_p}{2}$$

and if  $G_1 = G_2$ , then

and if

$$G_1 = G_2$$

, then

$$V_{\text{out}} = -V_1 V_2 K/2G_2 = \frac{V_1 V_2}{V_p}$$

Typical pinch-off is -10V for results quoted, but no signal levels are identified. Accuracies claimed are within ±1% over a temperature range of 50K in the frequency range 0 to 20kHz, using matched f.e.ts whose conductances are within ±5%.

#### Reference

Miller, A. Temperature compensated analogue multiplier, Electronics Letters 9 Sept. 1971, vol. 17, no. 18.

Related circuits Set 22, card 7